Изобретение относится к микроэлектронике и может быть использовано при проектировании и изготовлении запоминающих устройств с резервированием.

Целью изобретения является упрощение устройства.

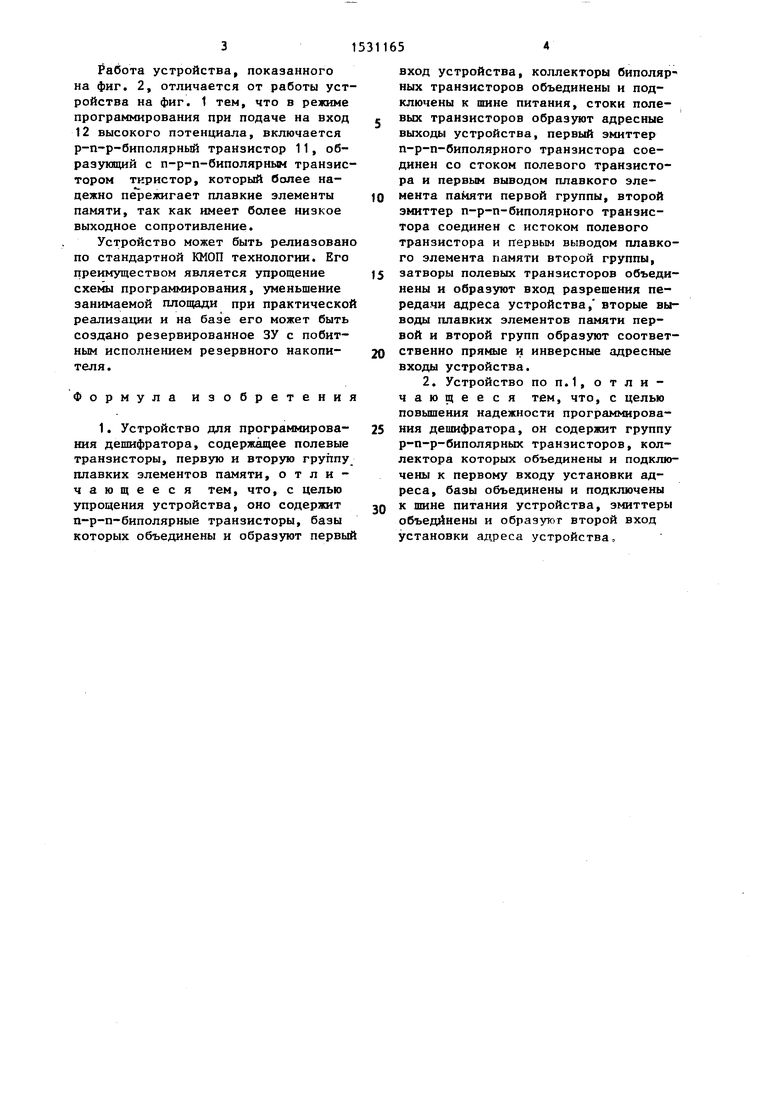

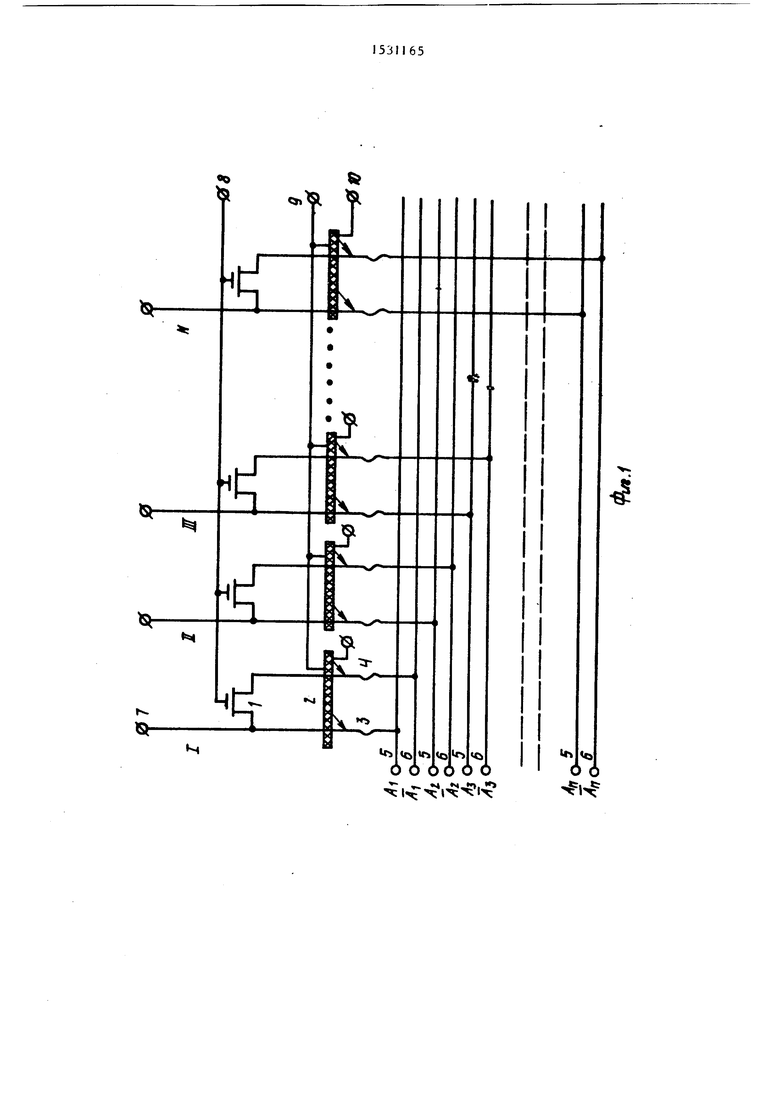

На фиг. 1 приведена электрическая схема устройства для программирования дешифратора; на фиг. 2 - то же, с дополнительным р-п-р-биполярным транзистором.

Устройство (фиг, 1 и 2) содержит полевой МДП-транзистор 1, двухэмит- терный п-р-п-биполярный транзистор 2, плавкий элемент 3 памяти первой группы, элемент 4 памяти второй группы, прямой адресный вход 5, инверсный адресный вход 6, адресный выход 7, вход 8 разрешения передачи адреса, первый вход 9 установки адреса, пшну 10 питания, р-п-р-биполярный транзистор 11 и второй вход 12 установки адреса.

Устройство для программирования дешифратора в режиме резервирования работает следующим образом.

При наличии на адресных входах 3 н 6 кодов адреса строки и столбца дефектной ячейки памяти в виде логических О и 1 на вход 9 подается высокий потенциал (логическая 1), в результате чего включаются п-р-п-биполярные транзисторы и через их эмиттеры., находящиеся под воздействием низкого потенциала, начинает протекать ток, которьш пережигает соответствующие плавкие элементы памяти. На входе 8 в режиме програ1 1н 1ровлния поддерживается потенциал, выключающий полевые транзисторы 1

В режиме записи и считывания информации на вход 9 подается низкий потенгр ал, в результате закрыты все п-р-п-биполярные транзисторы 2 независимо от потенциалов на адресных входах. На вход 8 подается потен1;иал, открывающий транзисторы 1, в результате чего на адресных выходах 7 появляются сигналы, определяемые состоянием главких элементов памяти и кодом адресны:: входов.

g

(Л

с:

ел

00

05 ел

Работа устройства, показанного на фиг. 2, отличается от работы устройства на фиг. 1 тем, что в режиме программирования при подаче на вход 12 высокого потенциала, включается р-п-р-биполярный транзистор 11, образующий с п-р-п-биполярным транзистором тиристор, который бсшее надежно пережигает плавкие элементы памяти, так как имеет более низкое выходное сопротивление.

Устройство может быть релиазовано по стандартной КМОП технологии. Его преимуществом является упрощение схемы программирования, уменьшение занимаемой площади при практической реализации и на базе его может быть создаио резервированное ЗУ с побитным исполнением резервного накопителя.

Формула изобретения

1. Устройство для программирования дешифратора, содержащее полевые транзисторы, первую и вторую группу плавких элементов памяти, отличающееся тем, что, с целью упрощения устройства, оно содержит п-р-п-биполярные транзисторы, базы которых объединены и образуют первый

вход устройства, коллекторы биполярных транзисторов объединены и подключены к шине питания, стоки полевых транзисторов образуют адресные выходы устройства, первый эмиттер п-р-п-биполярного транзистора соединен со стоком полевого транзистора и первым выводом плавкого элемента пайяти первой группы, второй эмиттер п-р-п-биполярного транзистора соединен с истоком полевого транзистора и первым выводом плавкого элемента памяти второй группы,

затворы полевых транзисторов объединены и образуют вход разрешения передачи адреса устройства, вторые выводы плавких элементов памяти первой и второй групп образуют соответственно прямые и инверсные адресные входы устройства.

2. Устройство по П.1, отличающееся тем, что, с целью повышения надежности программирования дешифратора, он содержит группу р-п-р-биполярных транзисторов, коллектора которых объединены и подключены к первому входу установки адреса, базы объединены и подключены

к шине питания устройства, эмиттеры объединены и образуют второй вход установки адреса устройства.

5S

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Дешифратор | 1988 |

|

SU1596393A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Программируемое постоянное запоминающее устройство | 1981 |

|

SU999111A1 |

| Адресный формирователь | 1988 |

|

SU1596389A1 |

| Дешифратор | 1986 |

|

SU1399817A1 |

| Дешифратор | 1988 |

|

SU1594605A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

Изобретение относится к микроэлектронике и может быть использовано при проектировании и изготовлении запоминающих устройств с резервированием. Цель изобретения - упрощение устройства для программирования дешифратора. Поставленная цель достигается тем, что устройство содержит N-P-N-биполярные транзисторы для пережигания плавких элементов памяти. В режимах записи и считывания информации используются полевые транзисторы. 1 з.п.ф-лы, 2 ил.

| Патент № 4441170, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1989-12-23—Публикация

1987-12-28—Подача