Изобретение относится к вычислительной технике и может быть использовано в самосинхронных схемах для вычисления систем логических функций большого числа переменных, представленных в дизъюнктивной нормальной форме (ДНФ).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций, где m - число вычисляемых логических функций, счетчик, дешифратор, причем информационные входы D-триггеров из групп D-триггеров подключены к соответствующим разрядам входов данных, входы сброса всех D-триггеров всех групп D-триггеров и вход сброса счетчика объединены и подключены ко входу сброса устройства, выход счетчика подключен ко входу дешифратора, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы D-триггеров, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы D-триггеров, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы D-триггеров, выходы группы m блоков вычисления функций являются выходами устройства, каждый блок вычисления функций содержит k групп n-1 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , где k=intlog2(n), (n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, где k=intlog2(n), (n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к четвертым входам следующей четной группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены к четвертым входам следующей четной группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам блоков значений функций, причем нечетные входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам блоков значений функций, причем нечетные входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к третьим входам соответствующих элементов второй группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены к третьим входам соответствующих элементов второй группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , выходы четных элементов первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены ко вторым входам второй группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены ко вторым входам второй группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, выходы предпоследней группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , содержат два элемента 2⋅2НЕ-И-ИЛИ, реализующих функцию

, содержат два элемента 2⋅2НЕ-И-ИЛИ, реализующих функцию  , и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-гo блок а конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-ы блок значений конъюнкций содержит k групп n-1 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-гo блок а конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-ы блок значений конъюнкций содержит k групп n-1 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , где k=intlog2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, где k=intlog2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , подключены к нечетным входам второй группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию С

, подключены к нечетным входам второй группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию С  , выходы четных элементов нечетной группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов нечетной группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , 25.k подключены к четным входам четной группы 25.k+1 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, 25.k подключены к четным входам четной группы 25.k+1 элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию

, выходы предпоследней группы элементов 2⋅2НЕ-И-ИЛИ, реализующих функцию  , содержат два элемента 2⋅2НЕ-И-ИЛИ, реализующих функцию

, содержат два элемента 2⋅2НЕ-И-ИЛИ, реализующих функцию  , и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций (патент РФ №2503993 от 10.01.2014, кл. G06F 7/57).

, и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций (патент РФ №2503993 от 10.01.2014, кл. G06F 7/57).

Недостатком известного устройства являются высокие аппаратурные затраты на реализацию систем логических функций вследствие использования стандартных логических базисов и совершенных дизъюнктивных нормальных форм (СДНФ) логических функций, в связи с чем невозможно использовать известное устройство для вычисления заданных в ДНФ систем логических функций в самосинхронных схемах.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее первую группу D-триггеров количеством k2n, где n - количество переменных, k - количество вычисляемых конъюнкций, в каждой из k подгрупп 2n триггеров, k≤2n, вторую группу D-триггеров количеством km, где m - количество вычисляемых логических функций, группу k блоков конъюнкций 3, группу m блоков вычисления функций, счетчик, дешифратор, входы задания переменных, входы настройки, вход сброса, вход программирования, причем последний выход дешифратора является выходом готовности устройства, входы настройки подключены к информационным входам первой второй групп D-триггеров, входы сброса которых подключены ко входу сброса счетчика и ко входу сброса устройства, выходы группы m блоков вычисления функций являются выходами устройства, входы задания переменных подключены ко входам задания переменных блоков группы k блоков конъюнкций, первые k выходов дешифратора подключены ко входам синхронизации соответствующих из k подгрупп D-триггеров первой группы D-триггеров, вторые k+m выходов дешифратора подключены ко входам синхронизации соответствующих из m подгрупп D-триггеров второй группы D-триггеров,

каждый блок конъюнкций содержит первую, вторую, третью и четвертую группы инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, шину «Ноль вольт», шину питания,

причем входы инверторов первой группы подключены к соответствующим из п входов задания переменных, выходы инверторов первой группы подключены ко входам соответствующих инверторов второй группы и истокам соответствующих нечетных транзисторов первой группы передающих транзисторов, выходы инверторов второй группы инверторов подключены к истокам соответствующих четных транзисторов первой группы передающих транзисторов, затворы транзисторов первой группы передающих транзисторов подключены к соответствующим из 2n входам настройки блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов и подключен ко входу к соответствующего инвертора третьей группы инверторов, выход которого подключен к затвору соответствующего из n транзистора второй группы транзисторов и ко входу соответствующего инвертора из четвертой группы инверторов, выходы которых подключены к затворам соответствующих из n транзисторов третьей группы передающих транзисторов, истоки которых объединены и подключены к шине «Ноль вольт», стоки транзисторов третьей группы передающих транзисторов также объединены и подключены ко входу инвертора блока конъюнкции, к которому также подключен сток последнего n-го транзистора второй группы транзисторов, исток каждого транзистора которой подключен к стоку предыдущего транзистора, а исток первого транзистора второй группы транзисторов подключен к шине питания, выход инвертора блока конъюнкции является выходом блока конъюнкции,

каждый блок из группы m блоков вычисления функций содержит группу k передающих транзисторов программирования функций, инвертор блока дизъюнкции, причем затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока дизъюнкции, а истоки - к соответствующим из k разрядам входов конъюнкций блока дизъюнкции, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока дизъюнкции, выход которого является выходом блока дизъюнкции (Патент РФ №2544750 от 20.03.2015, кл. G06F 7/57). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения - содержит группу k блоков конъюнкций, группу m блоков вычисления функций, n входов задания переменных, k групп входов настройки конъюнкций, входы задания переменных подключены к первой подгруппе второй группы входов блоков группы k блоков конъюнкций, выходы группы m блоков вычисления функций являются выходами значений функций устройства, каждый блок конъюнкций содержит группу инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов, где i=1…n, выход инвертора блока конъюнкции является выходом блока конъюнкции 1.j, где j=1…k, каждый блок из группы m блоков вычисления функций содержит группу k передающих транзисторов программирования функций, инвертор блока вычисления функций, затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока вычисления функций, истоки - к выходам соответствующих из k разрядам входов конъюнкций блока вычисления функций, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока вычисления функций, выход которого является выходом блока вычисления функций.

Недостатком известного устройства, принятого за прототип, является невозможность его использования для вычисления заданных в ДНФ систем логических функций в самосинхронных схемах (ССС).

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию систем логических функций в синхронных схемах и не имеют средств индикации завершения переходных процессов. Входные переменные поступают на входные инверторы, на выходе которых образуются инверсии входных сигналов. Это приводит к тому, что, даже введя двойственный канал для вычисления двойственной логической функции, не будет возможности реализации фазы гашения, так как спейсер (например, нулевой) не может быть создан - отсутствуют средства приведения выходов основного и двойственного каналов в одинаковое состояние.

Для реализации спейсера в фазе гашения необходимы дополнительные средства приведения выходов основного и двойственного каналов в одинаковое состояние, отсутствующие в прототипе. Все это вызывает невозможность фиксации завершения переходного процесса, что является ключевым в самосинхронных схемах.

Задачей изобретения является обеспечение возможности индицирования завершения переходного процесса для использования устройства в самосинхронных схемах с парафазными переменными и нулевым спейсером при реализации систем логических функций, заданных в ДНФ.

Поставленная задача была решена за счет того, что в известное устройство, содержащее группу k блоков конъюнкций, группу m блоков вычисления функций, n входов задания переменных, k групп входов настройки конъюнкций,

причем входы задания переменных подключены к первой подгруппе второй группы входов блоков группы k блоков конъюнкций, выходы группы m блоков вычисления функций являются выходами значений функций устройства, каждый блок конъюнкций содержит группу инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов, где i=1…n,

выход инвертора блока конъюнкции является выходом блока конъюнкции 1.j, где j=1…k,

каждый блок из группы m блоков вычисления функций содержит

группу k передающих транзисторов программирования функций, инвертор блока вычисления функций,

причем затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока вычисления функций,

а истоки - к выходам соответствующих из k разрядам входов конъюнкций блока вычисления функций, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока вычисления функций, выход которого является выходом блока вычисления функций,

дополнительно введены группы k двойственных блоков конъюнкций, группа m двойственных блоков вычисления функций, группа k индикаторов вычисления конъюнкций, группа m индикаторов вычисления функций, n входов задания инверсий переменных, входы настройки функций, входы настройки двойственных блоков конъюнкций, входы настройки двойственных блоков функций, выходы двойственных блоков функций,

выходы индикации вычисления конъюнкций, выходы индикации вычисления функций, две группы k входов шины питания, группу k входов шины «Ноль вольт»,

причем j-e входы настройки конъюнкций группы входов настройки конъюнкций подключены к первой группе входов соответствующих j-x блоков конъюнкций группы k блоков конъюнкций,

n входов задания инверсий переменных подключены ко второй подгруппе входов второй группы входов k блоков конъюнкций и группы k двойственных блоков конъюнкций,

n входов задания переменных подключены к первой подгруппе входов второй группы входов блоков конъюнкций группы k блоков конъюнкций и к первой подгруппе входов второй группы входов двойственных блоков конъюнкций,

первые входы j-x блоков конъюнкций подключены к j-м входам первой группы шин питания,

вторые входы j-x блоков конъюнкций подключены к j-м входам группы шин «Ноль вольт» и к первым входам j-x двойственных блоков конъюнкций группы k двойственных блоков конъюнкций,

вторые входы, которых подключены к j-м входам второй группы шины питания,

выходы блоков конъюнкций подключены к первым входам индикаторов группы k индикаторов вычисления конъюнкций, ко вторым входам которых подключены выходы двойственных блоков конъюнкций группы k двойственных блоков конъюнкций, выходы индикаторов группы k индикаторов вычисления конъюнкций являются выходами индикации вычисления конъюнкций,

выходы блоков конъюнкций группы k блоков конъюнкций подключены к соответствующим входам первой группы входов блоков вычисления функций группы m блоков вычисления функций, вторая группа входов которых подключена ко входам настройки функций

выходы двойственных блоков конъюнкций группы k блоков конъюнкций подключены к соответствующим входам первой группы входов двойственных блоков вычисления функций группы m двойственных блоков вычисления функций, вторая группа входов которых подключена ко входам настройки двойственных блоков функций,

выходы блоков вычисления функций группы m блоков вычисления функций подключены к первым входам индикаторов группа m индикаторов вычисления функций,

выходы двойственных блоков вычисления функций группы m двойственных блоков вычисления функций подключены ко вторым входам индикаторов группы m индикаторов вычисления функций и являются выходами двойственных блоков функций,

в каждый блок конъюнкций введена группа 2n транзисторов инверсной проводимости и шина «Ноль вольт»,

причем входы нечетных инверторов группы подключены к соответствующим нечетным входам входов настройки конъюнкций,

входы четных инверторов группы подключены к соответствующим четным входам входов настройки конъюнкций,

нечетные входы настройки конъюнкций подключены к затворам соответствующих нечетных передающих транзисторов второй группы передающих транзисторов, где i=1…n, n - количество переменных,

четные входы настройки конъюнкций подключены к затворам соответствующих четных передающих транзисторов второй группы передающих транзисторов, где i=1…n,

истоки нечетного и четного транзисторов второй группы передающих транзисторов объединены и подключены к первому входу блока вычисления конъюнкций, где j=1…k, k - количество конъюнкций,

сток каждого нечетного транзистора второй группы передающих транзисторов подключен к истоку нечетного транзистора первой группы передающих транзисторов и к стоку нечетного транзистора третьей группы передающих транзисторов,

сток каждого четного транзистора второй группы передающих транзисторов подключен к истоку четного транзистора, где i=1…n, первой группы передающих транзисторов и к стоку четного транзистора третьей группы передающих транзисторов,

истоки нечетных и четных транзисторов третьей группы передающих транзисторов объединены и подключены ко второму входу блока вычисления конъюнкций 1.j, где j=1…k,

к затворам нечетных и четных транзисторов третьей группы передающих транзисторов подключены выходы соответствующих нечетных и четных инверторов группы инверторов, входы которых подключены к соответствующим нечетным и четным входам настройки конъюнкций,

объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов второй группы передающих транзисторов,

объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов второй группы передающих транзисторов,

остальные транзисторы групп соединены аналогично: объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов первой группы передающих транзисторов,

объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены ко входу инвертора блока конъюнкции, исток первого транзистора в группе 2n транзисторов инверсной проводимости подключен к шине «Ноль вольт», сток первого транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку второго транзистора в группе 2n транзисторов инверсной проводимости, сток второго транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку третьего транзистора в группе 2n транзисторов инверсной проводимости, остальные транзисторы соединены аналогично, сток 2n-1 второго транзистора в группе 2n транзисторов инверсной проводимостиподключен к истоку 2n-го транзистора в группе 2n транзисторов инверсной проводимости, сток которого подключен ко входу инвертора блока конъюнкции,

двойственные блоки конъюнкций группы k двойственных блоков конъюнкций аналогичны блокам конъюнкций группы k блоков конъюнкций,

каждый блок из группы m двойственных блоков вычисления функций содержит группу k передающих транзисторов инверсной проводимости программирования функций, инвертор двойственного блока вычисления функций,

причем затворы транзисторов группы k передающих транзисторов инверсной проводимости программирования функций подключены к соответствующим из k разрядам входов настройки двойственного блока вычисления функций, а истоки - к выходам соответствующих из k разрядам входов конъюнкций двойственного блока вычисления функций, стоки транзисторов группы k передающих транзисторов инверсной проводимости программирования функций объединены и подключены ко входу инвертора двойственного блока вычисления функций, выход которого является выходом двойственного блока вычисления функций.

Признаки заявляемого технического решения, отличительные от прототипа - содержит группы k двойственных блоков конъюнкций, группу m двойственных блоков вычисления функций, группу k индикаторов вычисления конъюнкций, группу m индикаторов вычисления функций, n входов задания инверсий переменных, входы настройки функций, входы настройки двойственных блоков конъюнкций, входы настройки двойственных блоков функций, выходы двойственных блоков функций,

выходы индикации вычисления конъюнкций, выходы индикации вычисления функций, две группы k входов шины питания, группу k входов шины «Ноль вольт»,

причем j-e входы настройки конъюнкций группы входов настройки конъюнкций подключены к первой группе входов соответствующих j-x блоков конъюнкций группы k блоков конъюнкций,

n входов задания инверсий переменных подключены ко второй подгруппе входов второй группы входов k блоков конъюнкций и группы k двойственных блоков конъюнкций,

n входов задания переменных подключены к первой подгруппе входов второй группы входов блоков конъюнкций группы k блоков конъюнкций и к первой подгруппе входов второй группы входов двойственных блоков конъюнкций,

первые входы j-x блоков конъюнкций подключены к j-м входам первой группы шин питания,

вторые входы j-x блоков конъюнкций подключены к j-м входам группы шин «Ноль вольт» и к первым входам j-x двойственных блоков конъюнкций группы k двойственных блоков конъюнкций,

вторые входы, которых подключены к j-м входам второй группы шины питания,

выходы блоков конъюнкций подключены к первым входам индикаторов группы k индикаторов вычисления конъюнкций, ко вторым входам которых подключены выходы двойственных блоков конъюнкций группы k двойственных блоков конъюнкций, выходы индикаторов группы k индикаторов вычисления конъюнкций являются выходами индикации вычисления конъюнкций,

выходы блоков конъюнкций группы k блоков конъюнкций подключены к соответствующим входам первой группы входов блоков вычисления функций группы m блоков вычисления функций, вторая группа входов которых подключена ко входам настройки функций

выходы двойственных блоков конъюнкций группы k блоков конъюнкций подключены к соответствующим входам первой группы входов двойственных блоков вычисления функций группы m двойственных блоков вычисления функций, вторая группа входов которых подключена ко входам настройки двойственных блоков функций,

выходы блоков вычисления функций группы m блоков вычисления функций подключены к первым входам индикаторов группа m индикаторов вычисления функций,

выходы двойственных блоков вычисления функций группы m двойственных блоков вычисления функций подключены ко вторым входам индикаторов группы m индикаторов вычисления функций и являются выходами двойственных блоков функций,

в каждый блок конъюнкций введена группа 2n транзисторов инверсной проводимости и шина «Ноль вольт»,

причем входы нечетных инверторов группы подключены к соответствующим нечетным входам входов настройки конъюнкций,

входы четных инверторов группы подключены к соответствующим четным входам входов настройки конъюнкций,

нечетные входы настройки конъюнкций подключены к затворам соответствующих нечетных передающих транзисторов второй группы передающих транзисторов, где i=1…n, n - количество переменных,

четные входы настройки конъюнкций подключены к затворам соответствующих четных передающих транзисторов второй группы передающих транзисторов, где i=1…n,

истоки нечетного и четного транзисторов второй группы передающих транзисторов объединены и подключены к первому входу блока вычисления конъюнкций, где j=1…k, k - количество конъюнкций,

сток каждого нечетного транзистора второй группы передающих транзисторов подключен к истоку нечетного транзистора первой группы передающих транзисторов и к стоку нечетного транзистора третьей группы передающих транзисторов,

сток каждого четного транзистора второй группы передающих транзисторов подключен к истоку четного транзистора, где i=1…n, первой группы передающих транзисторов и к стоку четного транзистора третьей группы передающих транзисторов,

истоки нечетных и четных транзисторов третьей группы передающих транзисторов объединены и подключены ко второму входу блока вычисления конъюнкций 1.j, где j=1…k,

к затворам нечетных и четных транзисторов третьей группы передающих транзисторов подключены выходы соответствующих нечетных и четных инверторов группы инверторов, входы которых подключены к соответствующим нечетным и четным входам настройки конъюнкций,

объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов второй группы передающих транзисторов,

объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов второй группы передающих транзисторов,

остальные транзисторы групп соединены аналогично: объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов первой группы передающих транзисторов,

объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены ко входу инвертора блока конъюнкции, исток первого транзистора в группе 2n транзисторов инверсной проводимости подключен к шине «Ноль вольт», сток первого транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку второго транзистора в группе 2n транзисторов инверсной проводимости, сток второго транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку третьего транзистора в группе 2n транзисторов инверсной проводимости, остальные транзисторы соединены аналогично, сток 2n-1 второго транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку 2n-го транзистора в группе 2n транзисторов инверсной проводимости, сток которого подключен ко входу инвертора блока конъюнкции,

двойственные блоки конъюнкций группы k двойственных блоков конъюнкций аналогичны блокам конъюнкций группы k блоков конъюнкций,

каждый блок из группы m двойственных блоков вычисления функций содержит группу k передающих транзисторов инверсной проводимости программирования функций, инвертор двойственного блока вычисления функций,

причем затворы транзисторов группы k передающих транзисторов инверсной проводимости программирования функций подключены к соответствующим из k разрядам входов настройки двойственного блока вычисления функций, а истоки - к выходам соответствующих из k разрядам входов конъюнкций двойственного блока вычисления функций, стоки транзисторов группы k передающих транзисторов инверсной проводимости программирования функций объединены и подключены ко входу инвертора двойственного блока вычисления функций, выход которого является выходом двойственного блока вычисления функций.

Отличительные признаки в сочетании с известными позволяют обеспечить возможность индицирования завершения переходного процесса для использования устройства в самосинхронных схемах с парафазными переменными и нулевым спейсером при реализации систем логических функций, заданных в ДНФ.

Введение двойственных блоков конъюнкций и соответствующих связей позволяет формировать парафазные сигналы значений конъюнкций, необходимые для функционирования самосинхронной схемы.

Введение двойственных блоков вычисления функций и соответствующих связей позволяет формировать парафазные сигналы значений функций, необходимые для функционирования самосинхронной схемы.

Введение группы k индикаторов вычисления конъюнкций и соответствующих связей позволяет фиксировать рабочую фазу вычисления конъюнкции (когда значения, вычисленные соответствующими блоками конъюнкций и двойственными блоками конъюнкций инверсны) и фазу гашения или спейсера (когда значения, вычисленные соответствующими блоками конъюнкций и двойственными блоками конъюнкций одинаковы).

Введение группы m индикаторов вычисления функций и соответствующих связей позволяет фиксировать рабочую фазу вычисления функции (когда значения, вычисленные соответствующими блоками вычисления функций и двойственными блоками вычисления функций инверсны) и фазу гашения или спейсера (когда значения, вычисленные соответствующими блоками вычисления функций и двойственными блоками вычисления функций одинаковы).

Введение n входов задания инверсий переменных позволяет реализовать фазу гашения (спейсера) в том случае, когда на n входов задания инверсий переменных и на n входов задания переменных подаются одинаковые нулевые значения. В рабочей фазе на n входов задания инверсий переменных и на n входов задания переменных подаются взаимно инверсные сигналы.

Введение входов настройки двойственных блоков конъюнкций позволяет настраивать двойственные блоки конъюнкций на реализацию заданной конъюнкции.

Введение входов настройки двойственных блоков функций позволяет настраивать двойственные блоки функций на реализацию заданной дизъюнкции значений, формируемых двойственными блоками конъюнкций.

Введение выходов индикации вычисления конъюнкций позволяет внешнему оборудованию (внешним гистерезисным триггерам) фиксировать завершение переходного процесса в блоках конъюнкций и в двойственных блоках конъюнкций.

Введение выходов индикации вычисления функций позволяет внешнему оборудованию (внешним гистерезисным триггерам) фиксировать завершение переходного процесса в блоках функций и в двойственных блоках функций.

Введение выходов двойственных блоков функций позволяет передавать парафазные сигналы значений функций внешнему самосинхронному оборудованию.

Введение двух групп k входов шины питания и группы k входов шины «Ноль вольт» позволяет реализовать парафазное вычисление конъюнкций в блоках конъюнкций и в двойственных блоках конъюнкций.

Введение в каждый блок конъюнкций, аналогичных двойственным блокам конъюнкций, группы 2n транзисторов инверсной проводимости и шины «Ноль вольт» позволяет реализовать фазу гашения блоков конъюнкций и двойственных блоков конъюнкций при нулевых значениях входов переменных и входов инверсий переменных.

Введение в каждый блок из группы m двойственных блоков вычисления функций группы k передающих транзисторов инверсной проводимости программирования функций и инвертора двойственного блока вычисления функций позволяет вычислять двойственное значение функций для получения парафазных сигналов значений функций на выходах блоков функций и двойственных блоков функций.

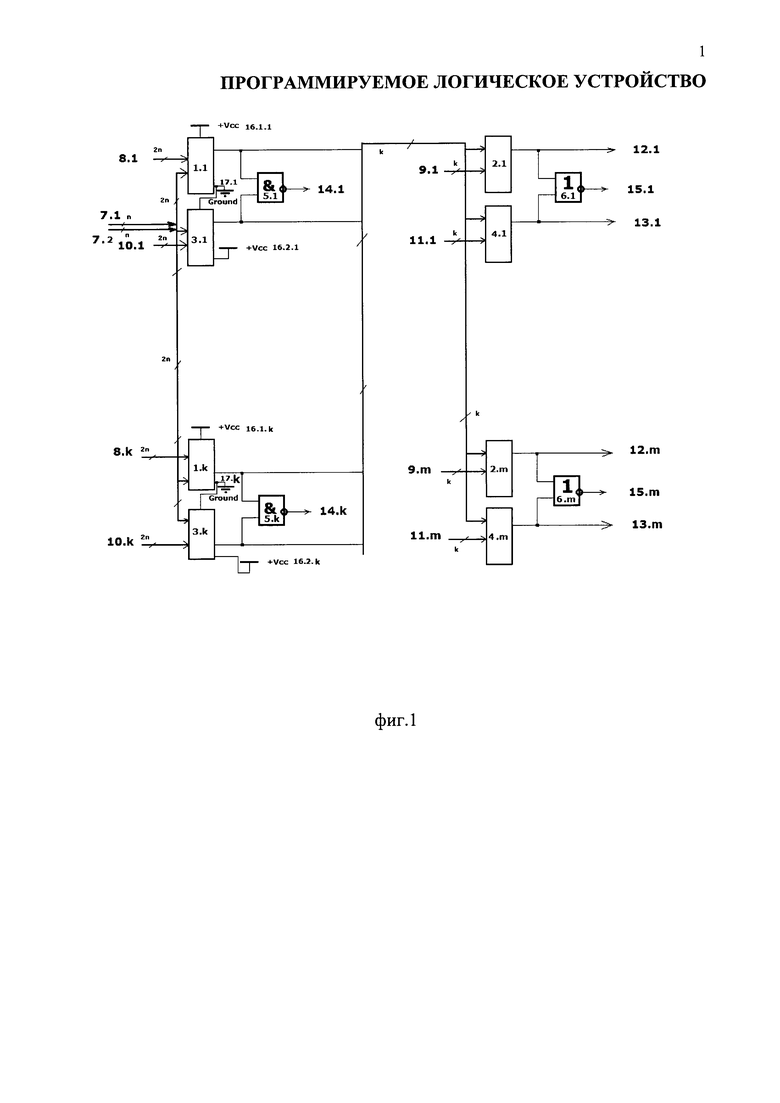

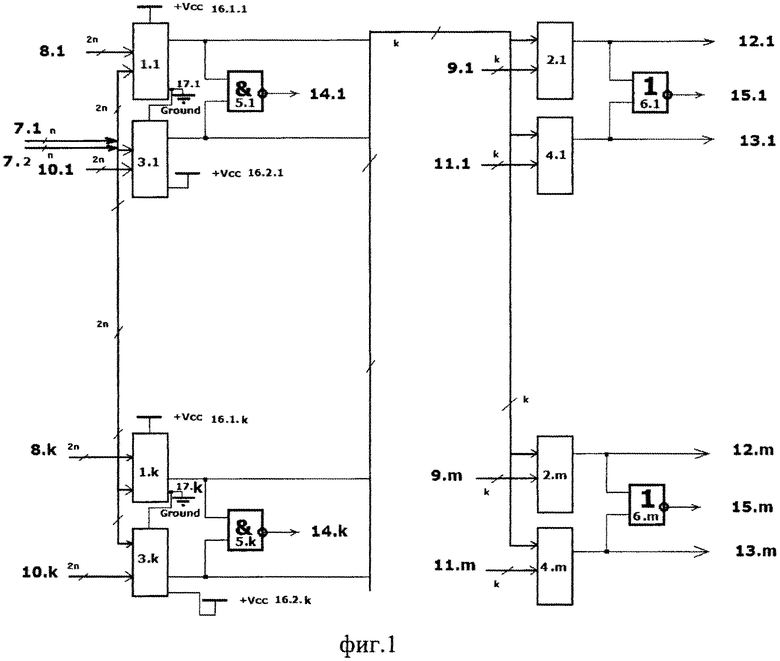

На фиг. 1 изображена схема электрическая структурная программируемого логического устройства.

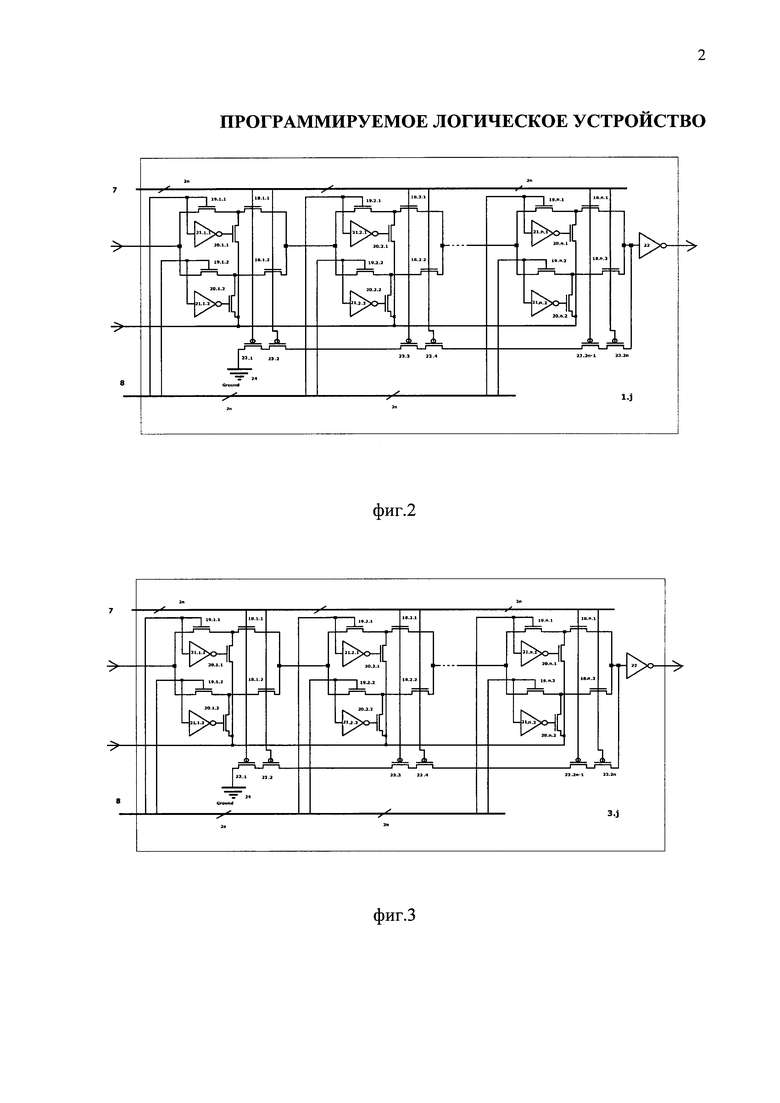

На фиг. 2 - схема электрическая функциональная j-го блока конъюнкций.

На фиг. 3 - схема электрическая функциональная j-го двойственного блока конъюнкций.

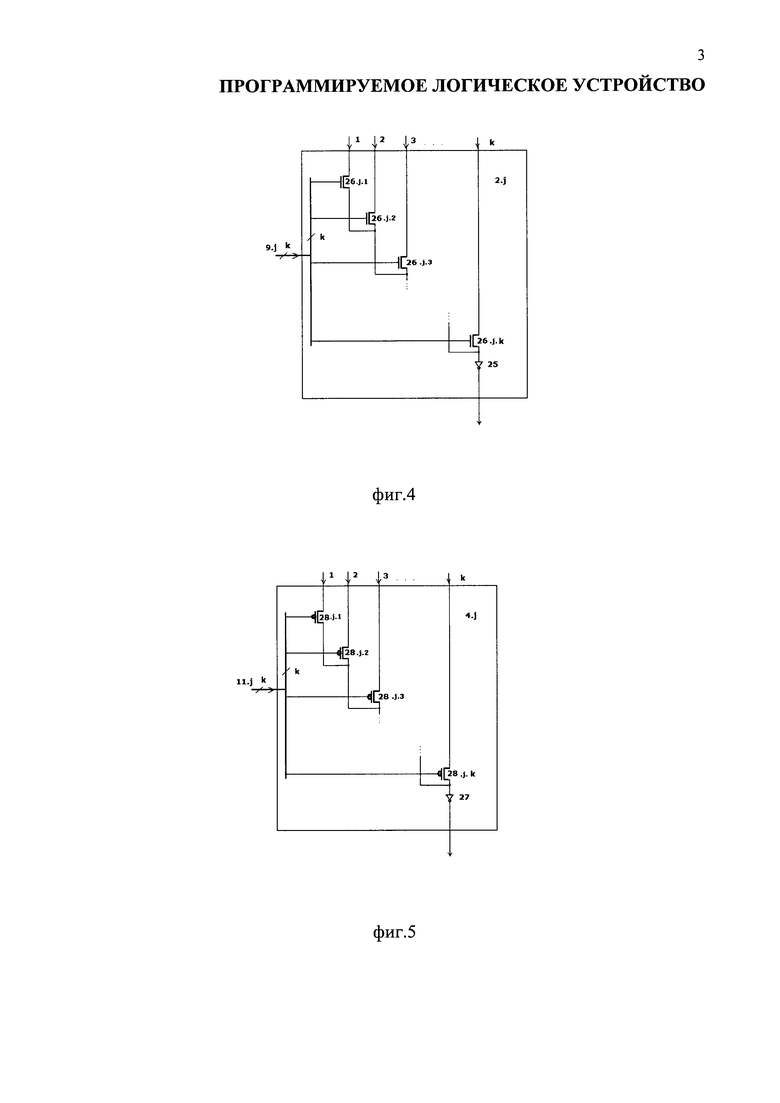

На фиг. 4 - схема электрическая функциональная j-го блока вычисления функций.

На фиг. 5 - схема электрическая функциональная j-гo двойственного блока вычисления функций.

Программируемое логическое устройство содержит (фиг. 1) группу k блоков конъюнкций 1, группу m блоков вычисления функций 2,

k групп двойственных блоков конъюнкций 3, группу m двойственных блоков вычисления функций 4, группу k индикаторов вычисления конъюнкций 5, группу m индикаторов вычисления функций 6, n входов задания переменных 7.1, n входов задания инверсий переменных 7.2, k групп входов настройки конъюнкций 8, входы настройки функций 9, входы настройки двойственных блоков конъюнкций 10, входы настройки двойственных блоков функций 11, выходы значений функций устройства 12, выходы двойственных блоков функций 13, выходы индикации вычисления конъюнкций 14 (фиг. 1), выходы индикации вычисления функций 15, две группы k входов шины питания 16.1, 16.2, группу k входов шины «Ноль вольт» 17.

Каждый блок конъюнкций (фиг. 2) содержит первую 18, вторую 19 и третью 20 группы передающих транзисторов, группу инверторов 21, инвертор блока конъюнкции 22, группу 2n транзисторов инверсной проводимости 23 и шина «Ноль вольт» 24.

Каждый двойственный блок конъюнкций (фиг. 3) аналогичен блоку конъюнкций (фиг. 2).

Каждый блок из группы m блоков вычисления функций 2 (фиг. 4) содержит инвертор блока вычисления функций 25, группу k передающих транзисторов 26 программирования функций,

Каждый блок из группы m двойственных блоков вычисления функций 4 (фиг. 5) содержит инвертор двойственного блока вычисления функций 27, группу k передающих транзисторов инверсной проводимости 28 программирования функций,

Входы задания переменных 7.1 (фиг. 1) подключены к первой подгруппе второй группы входов блоков группы k блоков конъюнкций 1, выходы группы m блоков вычисления функций 2 являются выходами значений функций устройства 12.

Сток каждого нечетного транзистора первой группы передающих транзисторов 18.i.1 (фиг. 2) объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов 18.i.2, где i=1…n, n - количество входов.

Выход инвертора блока конъюнкции 22 (фиг. 2) является выходом блока конъюнкции 1.j, где j=1…k, k - число реализуемых конъюнкций от n переменных.

Затворы транзисторов группы k передающих транзисторов программирования функций 26 (фиг. 4) подключены к соответствующим из k разрядам входов настройки 9 блока вычисления функций 2, а истоки - к выходам соответствующих из k разрядам входов конъюнкций блока вычисления функций 2. Стоки транзисторов группы k передающих транзисторов 26 программирования функций объединены и подключены ко входу инвертора блока вычисления функций 25, выход которого является выходом блока вычисления функций 2.

j-e входы настройки конъюнкций 8.j (фиг. 1) группы входов настройки конъюнкций 8 подключены к первой группе входов соответствующих j-x блоков конъюнкций 1.j группы k блоков конъюнкций 1.

n входов задания инверсий переменных 7.2 (фиг. 1) подключены ко второй подгруппе входов второй группы входов k блоков конъюнкций 1 и группы k двойственных блоков конъюнкций 3, n входов задания переменных 7.1 подключены к первой подгруппе входов второй группы входов блоков конъюнкций 1 группы k блоков конъюнкций 1 и к первой подгруппе входов второй группы входов двойственных блоков конъюнкций 3.

Первые входы j-x блоков конъюнкций 1.j (фиг. 1) подключены к j-м входам первой группы шин питания 16.1, вторые входы j-x блоков конъюнкций 1.j подключены к j-м входам группы шин «Ноль вольт» 17.j и к первым входам j-x двойственных блоков конъюнкций 3.j группы k двойственных блоков конъюнкций 3, вторые входы, которых подключены к j-м входам второй группы шины питания 16.j.

Выходы блоков конъюнкций 1.j (фиг. 1) подключены к первым входам индикаторов 5.j группы k индикаторов вычисления конъюнкций 5, ко вторым входам которых подключены выходы двойственных блоков конъюнкций 3.j группы k двойственных блоков конъюнкций 3, выходы индикаторов группы k индикаторов вычисления конъюнкций являются выходами 14.j индикации вычисления конъюнкций 14.

Выходы блоков конъюнкций группы k блоков конъюнкций 1 (фиг. 1) подключены к соответствующим входам первой группы входов блоков вычисления функций группы m блоков вычисления функций 2, вторая группа входов которых подключена ко входам настройки функций 9.

Выходы двойственных блоков конъюнкций группы k блоков конъюнкций 3 (фиг. 1) подключены к соответствующим входам первой группы входов двойственных блоков вычисления функций группы m двойственных блоков вычисления функций 4, вторая группа входов которых подключена ко входам настройки двойственных блоков функций 11.

Выходы блоков вычисления функций 2.i (фиг. 1) группы m блоков вычисления функций 2 подключены к первым входам индикаторов 6.i группа m индикаторов вычисления функций 6.

Выходы двойственных блоков вычисления функций 4.i (фиг. 1) группы m двойственных блоков вычисления функций 4 подключены ко вторым входам индикаторов 6.i группы m индикаторов вычисления функций 6 и являются выходами двойственных блоков функций 13.i.

Входы нечетных инверторов группы 21.i.1 (фиг. 2) подключены к соответствующим нечетным входам входов настройки конъюнкций 8.i.1, входы четных инверторов группы 21.i.2 подключены к соответствующим четным входам входов настройки конъюнкций 8.i.2.

Нечетные входы настройки конъюнкций 8.i.1 (фиг. 2) подключены к затворам соответствующих нечетных передающих транзисторов 19.i.1 второй группы передающих транзисторов 19, где i=1…n, n - количество переменных, четные входы настройки конъюнкций 8.i.2 подключены к затворам соответствующих четных передающих транзисторов 19.i.2 второй группы передающих транзисторов 19, где i=1…n.

Истоки нечетного 19.1.1 и четного транзисторов 19.1.2 (фиг. 2) второй группы передающих транзисторов 19 объединены и подключены к первому входу блока вычисления конъюнкций 1.j, где j=1…k, k - количество конъюнкций.

Сток каждого нечетного транзистора 19.i.1 (фиг. 2) второй группы передающих транзисторов 19 подключен к истоку нечетного транзистора 18.i.1 первой группы передающих транзисторов 18 и к стоку нечетного транзистора 20.i.1 третьей группы передающих транзисторов 20.

Сток каждого четного транзистора 19.i.2 (фиг. 2) второй группы передающих транзисторов 19 подключен к истоку четного транзистора 18.i.2, где i=1…n, первой группы передающих транзисторов 18 и к стоку четного транзистора 20.i.2 третьей группы передающих транзисторов 20, истоки нечетных 20.i.1 и четных 20.i.2 транзисторов третьей группы передающих транзисторов 20 объединены и подключены ко второму входу блока вычисления конъюнкций 1.j, где j=1…k.

К затворам нечетных 20.i.1 и четных 20.i.2 (фиг. 2) транзисторов третьей группы передающих транзисторов 20 подключены выходы соответствующих нечетных 21.i.1 и четных 21.i.2 инверторов группы инверторов 21, входы которых подключены к соответствующим нечетным 8.i.1 и четным 8.i.2 входам настройки конъюнкций 8.

Объединенные стоки нечетных 18.1.1 и четных 18.1.2 (фиг. 2) транзисторов первой группы передающих транзисторов 18 подключены к объединенным истокам нечетных 19.2.1 и четных 19.2.2 транзисторов второй группы передающих транзисторов 19.

Объединенные стоки нечетных 18.2.1 и четных 18.2.2 (фиг. 2) транзисторов первой группы передающих транзисторов 18 подключены к объединенным истокам нечетных 19.3.1 и четных 19.3.2 транзисторов второй группы передающих транзисторов 19.

Остальные транзисторы групп 18 и 19 (фиг. 2) соединены аналогично: объединенные стоки нечетных 18.i.1 и четных 18.i.2 транзисторов первой группы передающих транзисторов 18 подключены к объединенным истокам нечетных 18.i + 1.1 и четных 18.i + 1.2 транзисторов первой группы передающих транзисторов 18, i=1…n-1, объединенные стоки нечетных 18.n.1 и четных 18.n.2 транзисторов первой группы передающих транзисторов 18 подключены ко входу инвертора блока конъюнкции 22.

Исток первого транзистора 23.1 (Фиг. 2) в группе 2n транзисторов инверсной проводимости 23 подключен к шине «Ноль вольт» 24, сток первого транзистора 23.1 в группе 2n транзисторов инверсной проводимости 23 подключен к истоку второго транзистора 23.2 в группе 2n транзисторов инверсной проводимости 23, сток второго транзистора 23.2 в группе 2n транзисторов инверсной проводимости 23 подключен к истоку третьего транзистора 23.3 в группе 2n транзисторов инверсной проводимости 23.

Остальные транзисторы соединены аналогично, сток 2n-1 второго транзистора 23.2n-1 в группе 2n транзисторов инверсной проводимости 23 подключен к истоку 2n-го транзистора 23.2n в группе 2n транзисторов инверсной проводимости 23, сток которого подключен ко входу инвертора блока конъюнкции 22.

Затворы транзисторов группы k передающих транзисторов инверсной проводимости программирования функций 28 (фиг. 5) подключены к соответствующим из k разрядам входов настройки 11 двойственного блока вычисления функций 4, а истоки - к выходам соответствующих из k разрядам входов конъюнкций двойственного блока вычисления функций 4 (фиг. 5).

Стоки транзисторов группы k передающих транзисторов инверсной проводимости 28 программирования функций объединены и подключены ко входу инвертора двойственного блока вычисления функций 27, выход которого является выходом двойственного блока вычисления функций 4.

Программируемое логическое устройство работает в следующих режимах: 1) программирования (или запись); 2) вычисления при отсутствии отказов; 3) вычисления при наличии отказов; 4) тестирование.

1. В режиме программирования (или настройки) устройство работает следующим образом.

В этом режиме на k групп входов настройки конъюнкций 8 (фиг. 1) и m групп входов настройки функций 9 с помощью внешнего оборудования подаются сигналы настройки конъюнкций и функций. Эти сигналы не изменяются в режиме вычислений.

В результате в k блоках конъюнкций 1 (фиг. 2) и в k двойственных блоках конъюнкций (фиг. 3) на затворах транзисторов второй группы передающих транзисторов 18 с соответствующих входов настройки конъюнкций 8 устанавливается информация, кодирующая вхождение i-x переменных с инверсией (нечетные транзисторы 19.i.1) или без инверсии (четные транзисторы 19.i.2) в требуемые конъюнкции, либо кодирующая несущественность i-ой переменной (активируются затворы и нечетных и четных соответствующих транзисторов 19).

В то же время настроечная информация 8 обеспечивает управление группой инверторов 21 так, что, если затвор 19.i.1 (19.i.2) неактивирован, то через соответствующий инвертор 21.i.1 (21.i.2) активируется затвор передающего транзистора третьей группы передающих транзисторов 20.i.1 (20.i.2). Это необходимо для передачи значений на первом входе блока конъюнкций (двойственных блоков конъюнкций) при «правильном» значении i-ой переменной и сигнала со второго входа при «не правильном» значении i-ой переменной через транзисторы первой группы передающих транзисторов 18.i.1 (18.i.2).

В m блоках вычисления функций 2 (фиг. 4) на затворах транзисторов программирования функций 26 с соответствующих входов соответствующей группы входов настройки 9 устанавливается информация, кодирующая вхождение или не вхождение j-ой конъюнкции из k конъюнкций в данную из m функций.

В m двойственных блоках вычисления функций 4 (фиг. 5) на затворах транзисторов группы k передающих транзисторов инверсной проводимости 28 программирования функций с соответствующих входов соответствующей группы входов настройки двойственных блоков функций 11 устанавливается информация, кодирующая вхождение или не вхождение j-ой конъюнкции из k конъюнкций в данную из m функций.

Пример конкретного выполнения

Пусть, например, требуется вычислить систему из двух логических функций:

f1 = x1x2∨x2x3∨x1x3,

f1 = x1x3∨(not x1)(not x2).

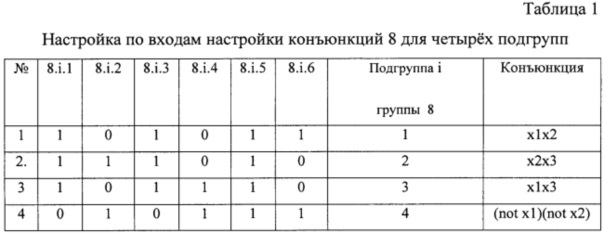

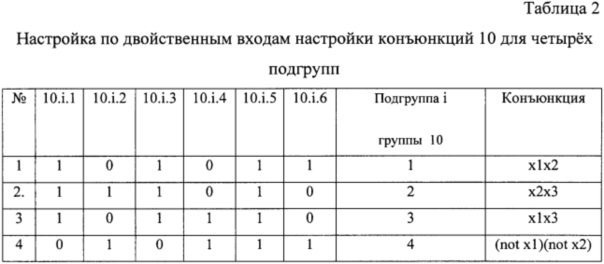

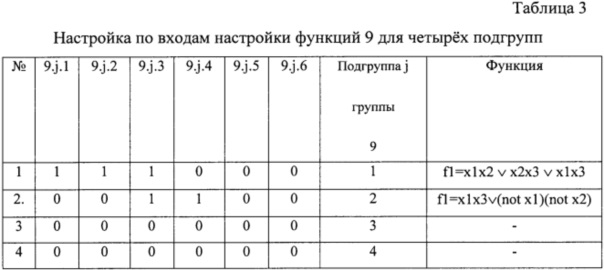

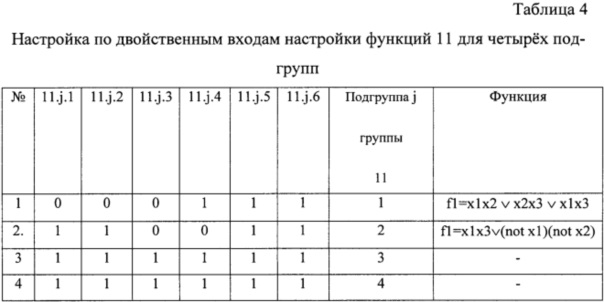

Тогда требуется настройка, определяемая табл.1-4:

2. В режиме вычислений устройство работает следующим образом.

В режиме вычислений информация с n входов задания переменных 7.1, n входов задания инверсий переменных 7.2 (фиг. 1) поступает на k блоков конъюнкций 1 и k двойственных блоков конъюнкций 3 в результате чего на их выходах формируется парафазный код значения k конъюнкций, а на выходах индикации вычисления конъюнкций 14 формируется сигнал логической единицы, фиксирующий завершение рабочей фазы, что воспринимается внешним по отношению к устройству оборудованием. Парафазные коды k конъюнкций поступают в m блоков вычисления функций 2 и m двойственных блоков вычисления функций 4, в результате чего на их выходах образуются парафазные значения функций, а на выходах индикации вычисления функций 15 формируется сигнал завершения рабочей фазы.

Эти сигналы также воспринимаются внешним оборудованием и когда все k выходов индикации вычисления конъюнкций 14 и все m выходов индикации вычисления функций 15 перейдут в состояние логической единицы, внешнее оборудование (гистерезисный триггер) зафиксирует факт завершения рабочей фазы в устройстве. Это приведет к переходу в фазу гашения (спейсера), когда на все n входов задания переменных 7.1 и n входов задания инверсий переменных 7.2 будут поданы нулевые сигналы (нулевой спейсер), что вызовет формирование сигналов логической единицы на выходах k блоков конъюнкций 1 и k двойственных блоков конъюнкций 3. Вследствие этого на выходах индикации вычисления конъюнкций 14 формируется сигнал логического нуля, фиксирующий завершение фазы гашения (спейсера). Кроме того, формирование сигналов логической единицы на выходах k блоков конъюнкций 1 и k двойственных блоков конъюнкций 3 приведет к формированию логических нулей на выходах m блоков вычисления функций 2 и m двойственных блоков вычисления функций 4, что вызовет логический ноль на выходах индикации вычисления функций 15, свидетельствующий о завершении фазы гашения (спейсера).

В режиме вычислений информация с n входов задания переменных 7.1, n входов задания инверсий переменных 7.2 управляет затворами передающих транзисторов первой группы передающих транзисторов 18 (фиг. 2).

При «правильном», то есть запрограммированном, заданном значении всех переменных значение на первом входе блока конъюнкций 1.j (двойственных блоков конъюнкций 3.j) передается на выход инвертора блока конъюнкций (двойственного блока конъюнкций) 22 через пары передающих транзисторов 19 и 18 одинаковой четности. Так, что на выходе блока конъюнкции 1 будет логический ноль, а на выходе двойственного блока конъюнкций 3 - логическая единица, свидетельствующие о том, что запрограммированная конъюнкция равна единице (истинна). Если запрограммированная конъюнкция равна нулю (ложна), то активированы транзисторы групп 18 и 19 различной четности хотя бы в одной паре. В результате за счет транзисторов группы 20, управляемых инверторами 21 на выходе инвертора 22 блока конъюнкции 1 будет логическая единица - инвертированное значение со второго входа блока конъюнкции 1, а на выходе инвертора 22 двойственного блока конъюнкции 3 будет логический ноль - инвертированное значение со второго входа блока конъюнкции 3.

В фазе гашения (спейсера) за счет группы 2n транзисторов инверсной проводимости 23 и шина «Ноль вольт» 24 и на выходе инвертора 22 блока конъюнкции 1 и на выходе инвертора 22 двойственного блока конъюнкции 3 будет логическая единица, что свидетельствует о завершении фазу гашения (спейсера).

В рабочей фазе в блоки группы m блоков вычисления функций 2 поступает информация о значениях запрограммированных конъюнкций с выходов блоков конъюнкций 1. В результате через транзисторы группу k передающих транзисторов 26 программирования функций, активированные по затворам настройкой 9, на вход инвертора блока вычисления функций 25 поступает хотя бы один ноль, если хотя бы одна конъюнкция соответствующей функции равна единице. Поэтому на выходе соответствующего блока вычисления функций 2 формируется логическая единица. Иначе на выходе соответствующего блока вычисления функций 2 формируется логический ноль.

В рабочей фазе в блоки группы m двойственных блоков вычисления функций 4 поступает информация о значениях запрограммированных конъюнкций с выходов двойственных блоков конъюнкций 3. В результате через транзисторы группы k инверсной проводимости 28 программирования функций, активированные по затворам настройкой 11, на вход инвертора двойственного блока вычисления функций 27 поступает хотя бы одна единица, если хотя бы одна конъюнкция соответствующей функции равна единице. Поэтому на выходе соответствующего двойственного блока вычисления функций 4 формируется логический ноль. Иначе на выходе соответствующего двойственного блока вычисления функций 4 формируется логическая единица.

Этим обеспечивается парафазное значение результата вычисления функции на выходах 12 и 13.

В фазе гашения (спейсера) в блоки группы m блоков вычисления функций 2 поступают логические единицы с выходов всех блоков конъюнкций 1. В результате через транзисторы группу k передающих транзисторов 26 программирования функций, активированные по затворам настройкой 9, на вход инвертора блока вычисления функций 25 поступает хотя бы одна единица (в функцию входит хотя бы одна конъюнкция).

Поэтому на выходе соответствующего блока вычисления функций 2 формируется логический ноль.

В фазе гашения (спейсера) в блоки группы m двойственных блоков вычисления функций 4 поступают логические единицы с выходов всех двойственных блоков конъюнкций 3. В результате через транзисторы группу k передающих транзисторов инверсной проводимости 28 программирования функций, активированные по затворам настройкой 11, на вход инвертора двойственного блока вычисления функций 27 поступает хотя бы одна единица (в функцию входит хотя бы одна конъюнкция).

Поэтому на выходе соответствующего двойственного блока вычисления функций 4 также формируется логический ноль.

Этим обеспечивается одинаковое значение результатов вычислений функции на выходах 12 и 13, что фиксирует завершение фазы гашения.

При необходимости возможна перенастройка устройства для вычисления других логических функций и т.д.

Устройство также может работать без фазы гашения, в синхронных схемах. При этом синхронизируется подача входного вектора на входы 7, например, путем записи входного вектора по синхроимпульсу на внешний по отношению к устройству регистр (триггеры), а результаты вычислений на выходах 12, 13 записываются по другому синхроимпульсу на другой внешний по отношению к устройству регистр (триггеры). Результаты на выходах 14, 15 могут быть оценены внешними по отношению к устройству средствами с целью контроля функционирования устройства.

Таким образом, в отличие от прототипа, устройство может быть использовано в самосинхронных схемах, работа которых, после настройки на требуемую логическую функцию, состоит их фазы гашения и рабочей фазы.

Такая работа в составе самосинхронных схем характеризуется большим быстродействием, чем у синхронных схем, так как они работают по реальным задержкам сигналов, и возможностью работы на сверхнизких напряжениях питания, что позволяет использовать устройство в энергоэффективных приложениях.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Программируемое логическое устройство | 2023 |

|

RU2826302C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2547229C1 |

Изобретение относится к вычислительной технике и может быть использовано в самосинхронных схемах для вычисления систем логических функций большого числа переменных, представленных в дизъюнктивной нормальной форме (ДНФ). Технический результат изобретения заключается в обеспечении возможности индицирования завершения переходного процесса для использования устройства в самосинхронных схемах с парафазными переменными и нулевым спейсером при реализации систем логических функций, заданных в ДНФ. Технический результат достигается за счет программируемого логического устройства, содержащего группы k двойственных блоков конъюнкций, группы m двойственных блоков вычисления функций, группы k индикаторов вычисления конъюнкций и группы m индикаторов вычисления функций. 5 ил., 4 табл.

Программируемое логическое устройство, содержащее группу k блоков конъюнкций, группу m блоков вычисления функций, n входов задания переменных, k групп входов настройки конъюнкций, причем входы задания переменных подключены к первой подгруппе второй группы входов блоков группы k блоков конъюнкций, выходы группы m блоков вычисления функций являются выходами значений функций устройства, каждый блок конъюнкций содержит группу инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов, где i=1…n, выход инвертора блока конъюнкции является выходом блока конъюнкции 1.j, где j=1…k, каждый блок из группы m блоков вычисления функций содержит группу k передающих транзисторов программирования функций, инвертор блока вычисления функций, причем затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока вычисления функций, а истоки - к выходам соответствующих из k разрядам входов конъюнкций блока вычисления функций, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока вычисления функций, выход которого является выходом блока вычисления функций, отличающееся тем, что в него дополнительно введены группы k двойственных блоков конъюнкций, группа m двойственных блоков вычисления функций, группа k индикаторов вычисления конъюнкций, группа m индикаторов вычисления функций, n входов задания инверсий переменных, входы настройки функций, входы настройки двойственных блоков конъюнкций, входы настройки двойственных блоков функций, выходы двойственных блоков функций, выходы индикации вычисления конъюнкций, выходы индикации вычисления функций, две группы k входов шины питания, группу k входов шины «Ноль вольт», причем j-e входы настройки конъюнкций группы входов настройки конъюнкций подключены к первой группе входов соответствующих j-x блоков конъюнкций группы k блоков конъюнкций, n входов задания инверсий переменных подключены ко второй подгруппе входов второй группы входов k блоков конъюнкций и группы k двойственных блоков конъюнкций, n входов задания переменных подключены к первой подгруппе входов второй группы входов блоков конъюнкций группы k блоков конъюнкций и к первой подгруппе входов второй группы входов двойственных блоков конъюнкций, первые входы j-x блоков конъюнкций подключены к j-м входам первой группы шин питания, вторые входы j-x блоков конъюнкций подключены к j-м входам группы шин «Ноль вольт» и к первым входам j-x двойственных блоков конъюнкций группы k двойственных блоков конъюнкций, вторые входы которых подключены к j-м входам второй группы шины питания, выходы блоков конъюнкций подключены к первым входам индикаторов группы k индикаторов вычисления конъюнкций, ко вторым входам которых подключены выходы двойственных блоков конъюнкций группы k двойственных блоков конъюнкций, выходы индикаторов группы k индикаторов вычисления конъюнкций являются выходами индикации вычисления конъюнкций, выходы блоков конъюнкций группы k блоков конъюнкций подключены к соответствующим входам первой группы входов блоков вычисления функций группы m блоков вычисления функций, вторая группа входов которых подключена ко входам настройки функций, выходы двойственных блоков конъюнкций группы k блоков конъюнкций подключены к соответствующим входам первой группы входов двойственных блоков вычисления функций группы m двойственных блоков вычисления функций, вторая группа входов которых подключена ко входам настройки двойственных блоков функций, выходы блоков вычисления функций группы m блоков вычисления функций подключены к первым входам индикаторов группы m индикаторов вычисления функций, выходы двойственных блоков вычисления функций группы m двойственных блоков вычисления функций подключены ко вторым входам индикаторов группы m индикаторов вычисления функций и являются выходами двойственных блоков функций, в каждый блок конъюнкций введена группа 2 n транзисторов инверсной проводимости и шина «Ноль вольт», причем входы нечетных инверторов группы подключены к соответствующим нечетным входам входов настройки конъюнкций, входы четных инверторов группы подключены к соответствующим четным входам входов настройки конъюнкций, нечетные входы настройки конъюнкций подключены к затворам соответствующих нечетных передающих транзисторов второй группы передающих транзисторов, где i=1…n, n - количество переменных, четные входы настройки конъюнкций подключены к затворам соответствующих четных передающих транзисторов второй группы передающих транзисторов, где i=1…n, истоки нечетного и четного транзисторов второй группы передающих транзисторов объединены и подключены к первому входу блока вычисления конъюнкций, где j=1…k, k - количество конъюнкций, сток каждого нечетного транзистора второй группы передающих транзисторов подключен к истоку нечетного транзистора первой группы передающих транзисторов и к стоку нечетного транзистора третьей группы передающих транзисторов, сток каждого четного транзистора второй группы передающих транзисторов подключен к истоку четного транзистора, где i=1…n, первой группы передающих транзисторов и к стоку четного транзистора третьей группы передающих транзисторов, истоки нечетных и четных транзисторов третьей группы передающих транзисторов объединены и подключены ко второму входу блока вычисления конъюнкций 1.j, где j=1…k, к затворам нечетных и четных транзисторов третьей группы передающих транзисторов подключены выходы соответствующих нечетных и четных инверторов группы инверторов, входы которых подключены к соответствующим нечетным и четным входам настройки конъюнкций, объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов второй группы передающих транзисторов, объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов второй группы передающих транзисторов, остальные транзисторы групп соединены аналогично: объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены к объединенным истокам нечетных и четных транзисторов первой группы передающих транзисторов, объединенные стоки нечетных и четных транзисторов первой группы передающих транзисторов подключены ко входу инвертора блока конъюнкции, исток первого транзистора в группе 2n транзисторов инверсной проводимости подключен к шине «Ноль вольт», сток первого транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку второго транзистора в группе 2n транзисторов инверсной проводимости, сток второго транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку третьего транзистора в группе 2n транзисторов инверсной проводимости, остальные транзисторы соединены аналогично, сток 2n-1 второго транзистора в группе 2n транзисторов инверсной проводимости подключен к истоку 2n-го транзистора в группе 2n транзисторов инверсной проводимости, сток которого подключен ко входу инвертора блока конъюнкции, двойственные блоки конъюнкций группы k двойственных блоков конъюнкций аналогичны блокам конъюнкций группы k блоков конъюнкций, каждый блок из группы m двойственных блоков вычисления функций содержит группу k передающих транзисторов инверсной проводимости программирования функций, инвертор двойственного блока вычисления функций, причем затворы транзисторов группы k передающих транзисторов инверсной проводимости программирования функций подключены к соответствующим из k разрядам входов настройки двойственного блока вычисления функций, а истоки - к выходам соответствующих из k разрядам входов конъюнкций двойственного блока вычисления функций, стоки транзисторов группы k передающих транзисторов инверсной проводимости программирования функций объединены и подключены ко входу инвертора двойственного блока вычисления функций, выход которого является выходом двойственного блока вычисления функций.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| ПРОГРАММНО-ЛОГИЧЕСКОЕ ВРЕМЕННОЕ УСТРОЙСТВО | 2001 |

|

RU2199146C1 |

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2018-05-07—Публикация

2017-10-02—Подача