Область техники данного изобретения относится к конструкции ячейки памяти. Более конкретно, данное изобретение относится к конструкции ячейки памяти с вертикально расположенными друг над другом пересечениями.

Статическое запоминающее устройство с произвольной выборкой (СЗУПВ) часто применяют в устройствах на интегральных схемах. Например, матрицы ячеек СЗУПВ используют в качестве кэш-памяти для высокоскоростных микропроцессоров. Одно из применений СЗУПВ - в Уровне 2 (У2) кэш-памяти для процессора "Пентиум-Про", который изготавливает "Интел Корп.", Санта-Клара, Калифорния.

Матрица ячеек СЗУПВ обычно состоит из нескольких одинаковых ячеек СЗУПВ для каждого разряда памяти. Например, для осуществления кэш-памяти 256К У2 в процессоре Пентиум-Про требуются миллионы ячеек СЗУПВ. С увеличением размера матрицы СЗУПВ остается неиспользуемым ценное пространство и повышается производственная себестоимость. Поэтому нужно свести по возможности к минимуму размер одной ячейки СЗУПВ, чтобы размер матрицы СЗУПВ не был слишком крупным, чтобы не оставалось неиспользованное пространство и себестоимость ее изготовления не повышалась.

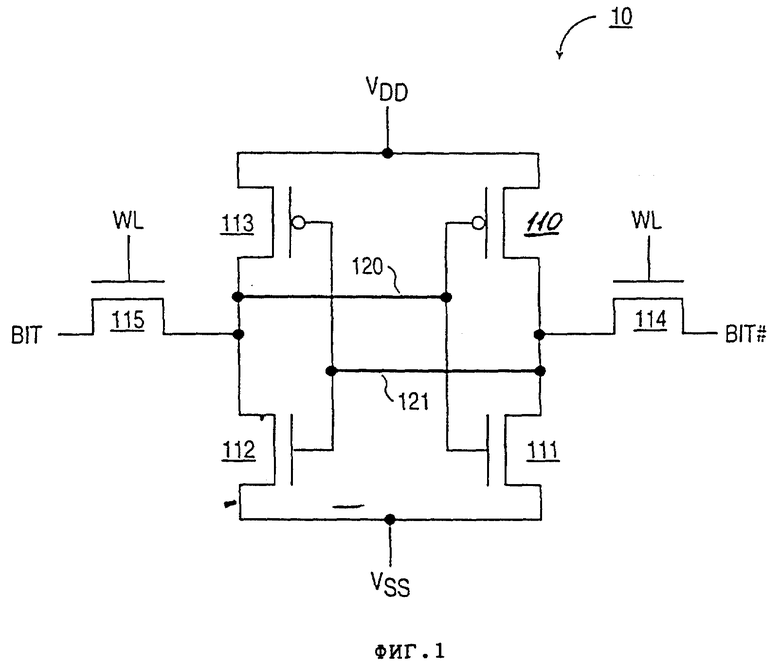

Один из примеров конструкции СЗУПВ изображен на фиг.1. 6-транзисторная ячейка СЗУПВ 10 содержит два инвертора с комплементарной структурой металл-оксид-полупроводник (КМОП). Первый инвертор состоит из транзисторов 110 и 111. Второй инвертор состоит из транзисторов 112 и 113. Два проходных транзистора 114 и 115 используют для выбора ячейки СЗУПВ для операций считывания и записи.

Для осуществления записи в ячейку 10 соответствующие данные записи (ДАННЫЕ) помещают на разрядную шину (РАЗРЯД), а их дополнения (ДАННЫЕ#) помещают на шину (РАЗРЯД#). Затем числовую шину (ЧШ) утверждают на затворе транзисторов 114 и 115, а ДАННЫЕ записывают в ячейку 10. Для считывания ячейки РАЗРЯД и РАЗРЯД# предварительно заряжают. После этого ЧШ утверждают, и с помощью транзисторов 112 и 111, соответственно, разряжают либо РАЗРЯД, либо РАЗРЯД#. Или же для устранения необходимости предварительного заряда к шинам РАЗРЯД и РАЗРЯД# могут прилагать статическое повышение напряжения (не изображено).

Согласно другому варианту, известному из уровня техники, ячейки СЗУПВ конструируют аналогично ячейке 10 - за тем исключением, что МОП-транзисторы с каналом р-типа 110 и 113 заменяют другими хорошо известными устройствами повышения напряжения, такими как работающий в режиме обеднения транзистор, работающий в режиме обогащения транзистор, или резистор. Также из уровня техники известна ячейка СЗУПВ, которая содержит один транзистор, а не два транзистора, который управляет сигналами РАЗРЯД и ЧШ. Кроме этого аналогичная ячейка СЗУПВ, известная из уровня техники, содержит два порта, или две числовые шины, для управления пересылкой данных к ячейке или от ячейки.

Эти конструкции ячейки СЗУПВ, известные из уровня техники, аналогичны в том отношении, что для них требуется использование пересекающихся соединений, таких как пересекающиеся соединения 120 и 121 в ячейке памяти 10. Пересекающееся соединение 120 соединяет вход первого инвертора, который содержит транзисторы 110 и 111, с выходом второго инвертора, который содержит транзисторы 112 и 113. Кроме этого пересекающееся соединение 121 соединяет вход второго инвертора, содержащего транзисторы 112 и 113, с выходом первого инвертора, который содержит транзисторы 110 и 111.

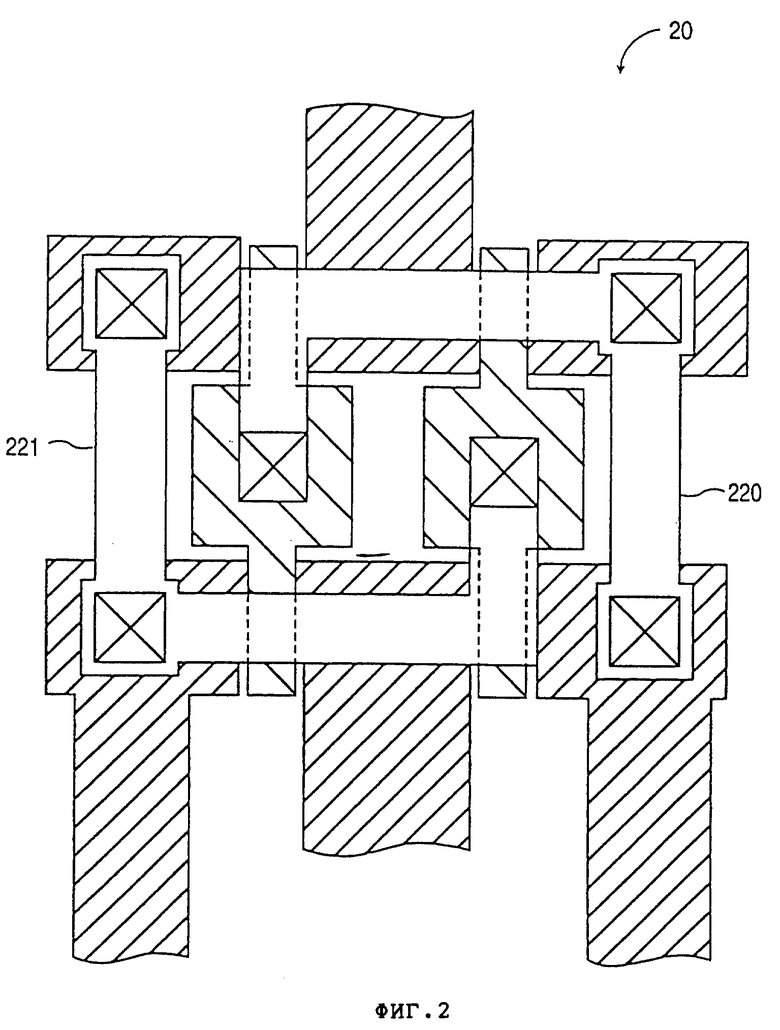

Типичные схемы "элемент-слой" СЗУПВ, известные из уровня техники, выполняют оба пересечения в одинаковом материале, используя одинаковый маскирующий слой. Поэтому схема ячейки СЗУПВ может быть подобна ячейке 20 на фиг. 2. Пересечения 220 и 221 выполняют в первом металлическом слое схемы. Недостаток этой схемы 20 ячейки заключается в том, что пересечения 220 и 221 должны располагаться рядом друг с другом, тем самым увеличивая размер ячейки СЗУПВ.

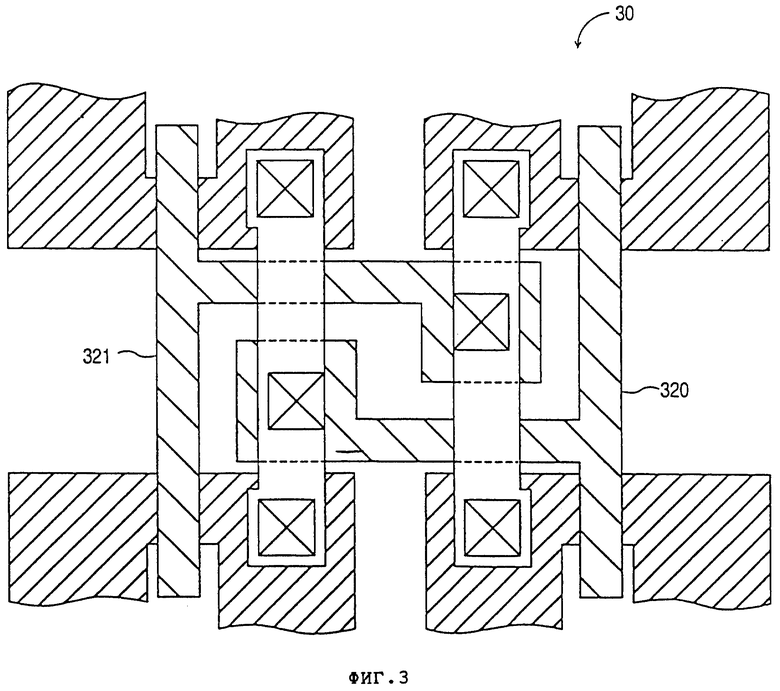

Фиг. 3 изображает еще одну схему "элемент-слой" СЗУПВ, известную из уровня техники, в которой два пересечения осуществляются в слое затвора, который обычно выполняют из поликремния. В этом случае также, поскольку пересечения 320 и 321 выполняют на одном и том же слое устройства, их нужно размещать рядом друг с другом.

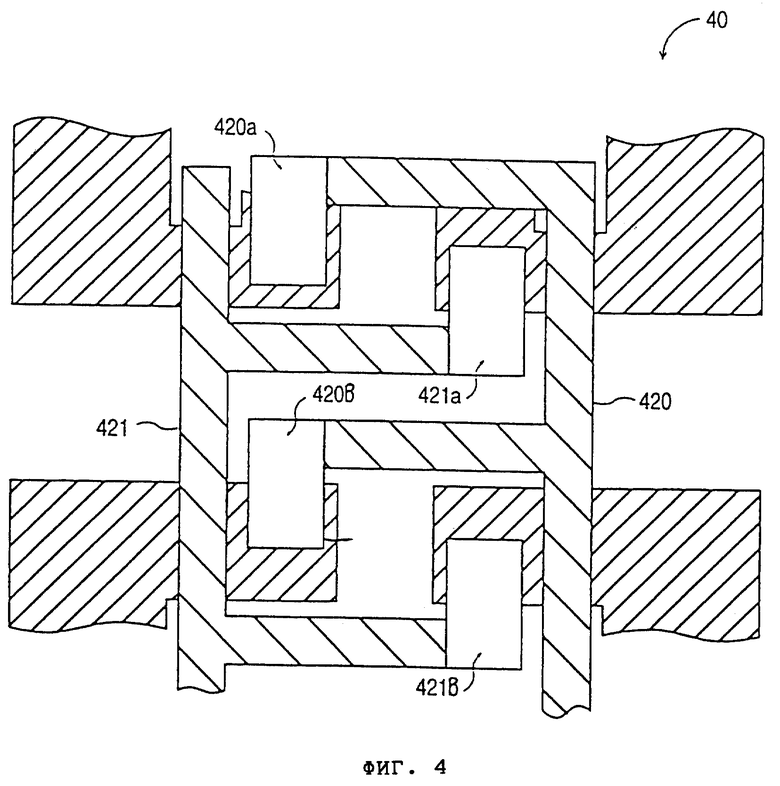

Фиг. 4 иллюстрирует третью схему "элемент-слой" ячейки 40 СЗУПВ, известной из уровня техники, в которой используют слой затвора наряду со слоем местного межсоединения. Пересечения 420 и 421 в основном выполняют в слое затвора, а соединение слоя затвора с истоком или стоком транзистора выполняют слоями местного межсоединения 420а-в и 421а-в. Слой местного межсоединения отличается от типичного металлического слоя первого или второго уровня тем, что местное межсоединение осаждают непосредственно сверху открытых поликремниевых и диффузионных участков транзисторного элемента. Даже в случае использования слоя местного межсоединения пересечения 420 и 421 надо размещать рядом Друг с другом, тем самым увеличивая величину площади, необходимой для ячейки СЗУПВ.

Из вышеизложенного описания схем ячейки СЗУПВ, известной из уровня техники, можно сделать вывод о том, что необходимо обеспечить такую схему ячейки СЗУПВ, в которой размер ячейки можно будет свести к минимуму.

Помимо этого, для снижения производственной себестоимости желательно обеспечить ячейку СЗУПВ минимального размера, которую можно сконструировать с помощью имеющихся технологических материалов, параметров и правил конструирования. Поэтому для осуществления нужной конструкции ячейки СЗУПВ надо исключить изменения в технологической обработке полупроводника.

Сущность изобретения

Ниже следует описание полупроводниковой ячейки памяти с вертикально расположенными друг над другом пересечениями. Ячейка памяти содержит первый транзисторный инвертор, имеющий первый вход и первый выход, и второй инвертор, имеющий второй вход и второй выход. Первый и второй транзисторы связаны с первым и вторым пересекающимися соединениями. Первое пересекающееся соединение соединяет первый вход со вторым выходом. Второе пересекающееся соединение соединяет второй вход с первым выходом. Два пересекающихся соединения содержат разные проводящие слои в процессе изготовления полупроводника. Два пересекающихся соединения поэтому вертикально компонуют одно сверху другого для уменьшения площади схемы ячейки памяти.

Краткое описание чертежей

Данное изобретение иллюстрируется как пример, но не как ограничение, прилагаемыми чертежами, на которых

Фиг. 1 изображает шеститранзисторную ячейку СЗУПВ, известную из уровня техники.

Фиг. 2 - схема известной из уровня техники ячейки СЗУПВ с металлическими пересечениями.

Фиг. 3 - схема известной из уровня техники ячейки СЗУПВ с пересечениями межсоединения "затвор-уровень".

Фиг. 4 - схема известной из уровня техники ячейки СЗУПВ с пересечениями межсоединения "затвор-уровень" и пересечениями местного межсоединения.

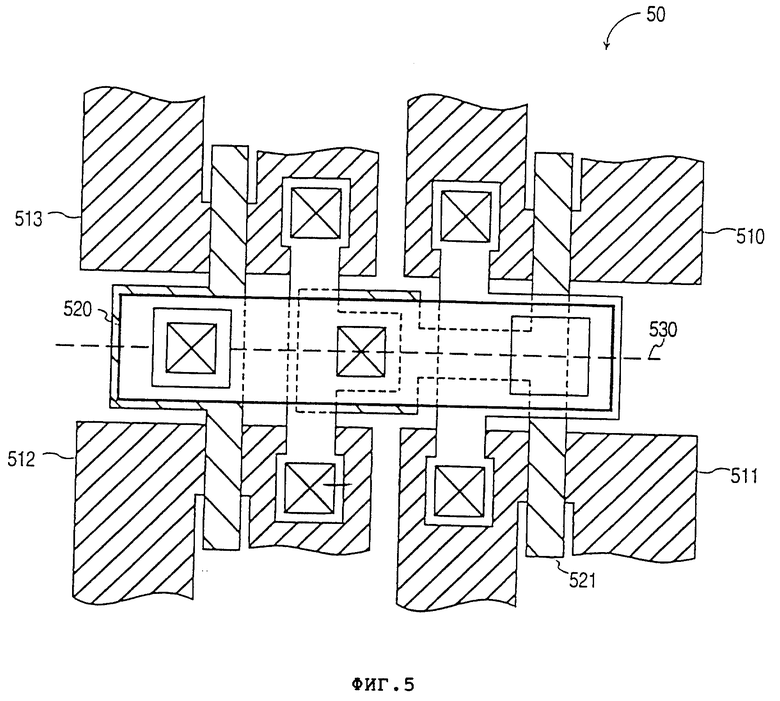

Фиг. 5 - конструкция схемы одного из вариантов осуществления данного изобретения.

Фиг. 6 - поперечное сечение конструкции схемы фиг. 3.

Фиг. 7 - конструкция схемы второго варианта осуществления данного изобретения.

Фиг. 8 - поперечное сечение конструкции схемы фиг. 7.

Подробное описание

Далее следует описание конструкции ячейки памяти с вертикально расположенными друг над другом пересечениями. В данном описании для обеспечения полного понимания излагаются такие многочисленные конкретные подробности, как материалы, параметры процесса и технология интегральной схемы. Но для специалиста в данной области будет очевидно, что для осуществления данного изобретения нет необходимости в применении этих конкретных подробностей. В других случаях, чтобы не перегружать описание данного изобретения, хорошо известные технологические способы или материалы не описываются подробно.

Одно из осуществлений ячейки памяти согласно данному изобретению содержит конструкцию 6-транзисторной ячейки СЗУПВ с вертикально расположенными друг над другом пересечениями в схеме ячейки. Другими словами, основная часть одного пересекающегося соединения расположена сверху другого пересекающегося соединения в схеме ячейки СЗУПВ.

Как вариант, ячейка памяти может содержать больше или меньше 6-ти транзисторов в зависимости от конкретной конструкции, и может содержать другие хорошо известные логические элементы, а не инверторы. Помимо этого ячейка памяти может содержать ячейку динамического запоминающего устройства с произвольной выборкой (ДЗУПВ). Важно только то, что в ячейке памяти используют пересечения, и что пересечения в некоторой степени перекрывают друг друга вертикально.

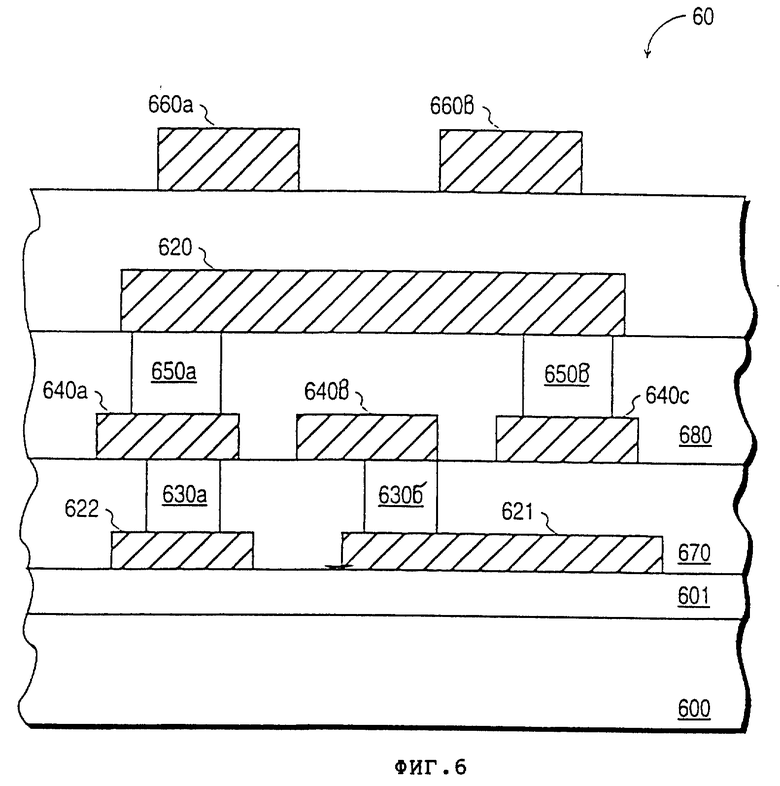

Фиг. 5 иллюстрирует первый вариант осуществления данного изобретения. Ячейка памяти 50 содержит МОП-транзисторы с каналом p-типа 510 и 513 и МОП- транзисторы n-типа 511 и 512. Пересечение 520 выполняют в металлическом слое межсоединения, а пересечение 521 выполняют в слое затвора. Эта компоновка нагляднее изображена в поперечном сечении на фиг. 6 по линии 530 ячейки памяти 50.

Фиг.6 изображает различные слои ячейки памяти 50. В соответствии с изображением фиг. 6 часть пересечения 620 располагается над пересечением 621, т. е. они являются "вертикально уложенными". Это вертикальное расположение друг над другом возможно осуществить, т.к. пересечение 620 выполнено во втором металлическом слое межсоединения, а пересечение 621 выполнено в слое затвора. Способы получения ячейки памяти 50 в соответствии с данным изобретением изложены подробнее ниже.

Следует отметить, что транзисторные элементы 510-513 на фиг. 6 не изображены. Способы конструирования и изготовления МОП-транзисторов хорошо известны в уровне техники и подробно здесь описываться не будут.

Первый слой 600 фиг. 6 содержит полупроводниковую подложку. Для осуществления данного изобретения подложка содержит кремний (Si). Либо подложка может содержать другие хорошо известные полупроводниковые материалы, такие как арсенид галлия (GaAs).

Сверху элементов 510- 513 и полупроводниковой подложки 600 находится защитный диэлектрический слой 601. В одном из вариантов осуществления диэлектрический слой 601 содержит диоксид кремния (SiO2) и сформирован на подложке 600 с помощью одного из нескольких хорошо известных процессов химического осаждения из паровой фазы (ХОПФ). Либо диэлектрический слой 601 можно формировать способом термического выращивания.

Сверху диэлектрического слоя 601 находится пересечение 621, содержащее слой затвора. В слое затвора находится межсоединение 622, которое соединяет затворы транзисторов 512 и 513. В одном из вариантов осуществления пересечение 621 содержит поликремний, который может быть легированным или нелегированным. Либо пересечение 621 содержит другой материал, соответствующий для применения в качестве контакта затвора транзистора. В другом варианте осуществления пересечение 621 также содержит слой силицида титана (TiSi2), или другой металл или силицид металла, имеющие низкое сопротивление слоя.

Пересечение 621 формируют сначала осаждением материала затвора (т.е. поликремния) согласно методу осаждения поликремния, такому как один из некоторых хорошо известных методов ХОПФ. После этого слой фоторезиста, или другой соответствующий маскирующий материал, центрифугируют на поликремнии. Фоторезист экспонируют и проявляют для определения таких элементов, как пересечение 621. Поликремний протравливают, чтобы создать нужные элементы, и затем фоторезист удаляют.

Слой диэлектрика 670 формируют сверху пересечения 621. Для одного из вариантов осуществления слой диэлектрика 670 содержит борофосфоросиликатное стекло (БФСС). Либо диэлектрический слой 670 может содержать слой фосфоросиликатного стекла (ФСС). Кроме этого диэлектрический слой 670 может содержать слой диффузионного барьера, такого как нитрид кремния (Si3N4). Для одного из вариантов осуществления диэлектрический слой 670 формируют процессом ХОПФ. Либо диэлектрический слой 670 формируют термическим выращиванием, методами ионного распыления или осаждения центрифугированием на стекле.

Маскирующий материал (т.е. фоторезист) центрифугируют на диэлектрик и по шаблону создают отверстия для контактов 630а и 630б. Диэлектрик затем протравливают согласно хорошо известному методу травления, такому как реактивное ионное травление (РИТ).

Контакты 630а и 630б затем наполняют проводящим материалом. Для одного из вариантов осуществления проводящий материал содержит вольфрам (W), осаждаемый процессом ХОПФ. Либо проводящий материал может содержать другой хорошо известный контактный материал, такой как алюминий. Помимо этого проводящий материал может быть осажден другими методами осаждения, такими как распыление или испарение. Проводящий материал может также содержать один или несколько слоев титана (Ti) или нитрида титана (TiN) для улучшения адгезии контактного материала и для обеспечения диффузионного барьера.

Для одного из вариантов осуществления данного изобретения подложку полируют химическо-механической полирующей системой для создания ровной поверхности вольфрама или диэлектрика перед выполнением последующих этапов.

Первый металлический слой межсоединения затем осаждают на подложку. Первый металлический слой межсоединения содержит металлические токопроводящие дорожки 640а, 640в и 640с. Токопроводящая дорожка 640а соединяет пересечение 620 со слоем затвора 622, который является входом транзисторов 512 и 513. Токопроводящая дорожка 640в соединяет пересечение 621 с выходом транзисторов 512 и 513. Металлическая токопроводящая дорожка 640с соединяет пересечение 620 с выходом транзисторов 510 и 511. Для одного из вариантов осуществления первый металлический слой межсоединения содержит алюминий (A1). Либо металлический слой межсоединения содержит сплав алюминия и меди (Cu). В качестве еще одного варианта первый металлический слой содержат один или несколько слоев титана (Ti) или нитрида титана (TiN). Нужно отметить, что для первого металлического слоя межсоединения, оставаясь в рамках данного изобретения, можно использовать другие проводящие материалы, имеющие нужные свойства (напр. , низкое удельное сопротивление, удобная формируемость и протравливаемость, устойчивость к механическому напряжению и обработке).

Первый металлический слой межсоединения формируют одним из нескольких хорошо известных методов осаждения, включая, но не ограничиваясь только ХОПФ, испарение или распыление. После этого металлические шины 640-а-с определяют наложением слоя маскирующего материала (напр., фоторезиста), созданием рисунка и его проявлением, и выполнением травления металла согласно хорошо известным методам травления металла. Например, можно использовать методы реактивного плазменного травления или реактивного ионного травления. После травления фоторезист удаляют.

Затем сверху первого металлического слоя межсоединения формируют диэлектрический слой, разделяющий уровни (ДСРУ) 680. В одном из вариантов осуществления слой ДСРУ 680 содержит диоксид кремния (SiO2) и формируется по методу ХОПФ. На слое диэлектрика 680 затем формируют рисунок и его протравливают в соответствии с изложенным выше, чтобы сформировать отверстия для сквозных отверстий 650а и 650б. В одном из вариантов осуществления слой ДСРУ 680 затем выравнивают методом химико-механической полировки. Сквозное отверстие 650а используют для соединения пересечения 620 с металлической токопроводящей дорожкой 640а, тем самым соединяя пересечение 620 с металлической токопроводящей дорожкой 640а, и тем самым соединяя пересечение 620 со входом инвертора, содержащего транзисторы 512 и 513. Сквозное отверстие 6506 соединяет пересечение 620 с металлической токопроводящей дорожкой 640с, тем самым соединяя пересечение 620 с выходом инвертора, содержащего транзисторы 510 и 511.

Сквозные отверстия 650а и 650в наполняют проводящим материалом, таким как вольфрам (W). Либо сквозные отверстия дополнительно наполняют одним или несколькими слоями титана (Ti) или нитрида титана (TiM).Необходимо отметить, что для наполнения сквозных отверстий 650а и 650в, оставаясь в рамках данного изобретения, можно использовать другие соответствующие проводящие материалы, такие как алюминий (Al).

Проводящий материал осаждают с помощью хорошо известного метода осаждения металла, такого как ХОПФ, испарение или распыление. Для одного из вариантов осуществления в целях выравнивания проводящего материала перед выполнением последующих этапов применяют химико- механический метод полировки.

Затем в материале межсоединения второго уровня формируют пересечение 620. Материал межсоединения второго уровня формируют аналогично материалу межсоединения первого уровня. В одном из вариантов осуществления пересечение 620 содержит алюминий (Al). Либо пересечение 620 также содержат один или несколько слоев титана (Ti) или нитрида титана (TiN). Нужно отметить, что для второго металлического слоя межсоединения, оставаясь в рамках данного изобретения, можно использовать один из нескольких хорошо известных проводящих материалов. В еще одном варианте осуществления второй металлический слой межсоединения содержит более толстый слой металла, чем первый металлический слой межсоединения, в целях снижения сопротивления второго металлического слоя.

Слой диэлектрика формируют сверху второго металлического слоя межсоединения в соответствии с указанными выше способами осаждения диэлектрика. Третий металлический слой межсоединения можно по желанию осадить сверху диэлектрика согласно изображению контактов 660а и 660в на фиг. 6.

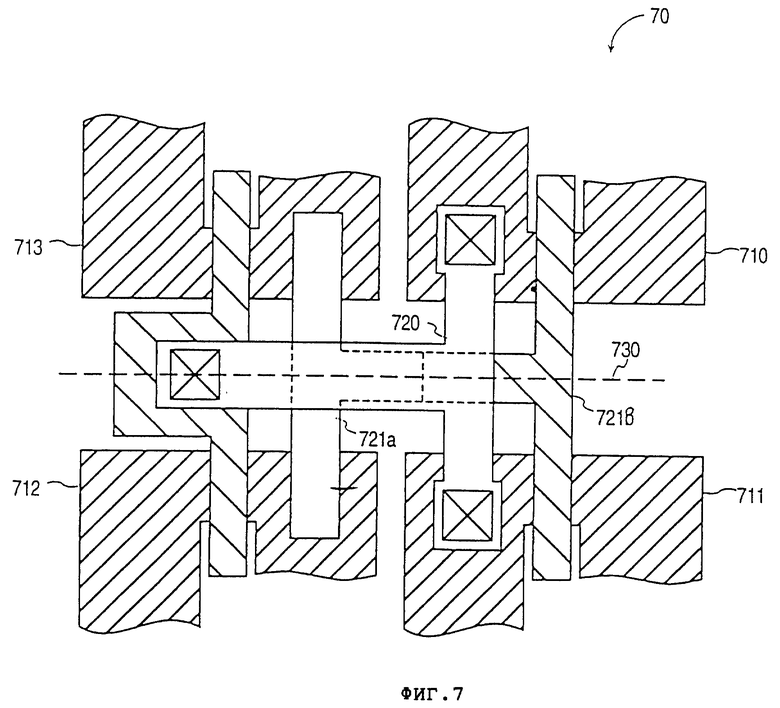

Фиг. 7 изображает другой вариант осуществления данного изобретения. Фиг. 7 - конструкция схемы шеститранзисторной ячейки СЗУПВ, аналогичной ячейке 50 фиг. 5. Ячейка памяти 70 отличается от ячейки памяти 50 тем, что пересечение 720 выполнено в первом металлическом слое межсоединения, а пересечение 721 выполнено в двух межсоединениях, причем первое межсоединение содержит слой затвора, а второе межсоединение содержит слой местного межсоединения. Межсоединение 721а пересечения 721 соединяет выход инвертора, содержащего транзисторы 712 и 713, с межсоединением 721в пересечения 721. Межсоединение 721в пересечения 721 завершает соединение со входом инвертора, содержащего транзисторы 710 и 711.

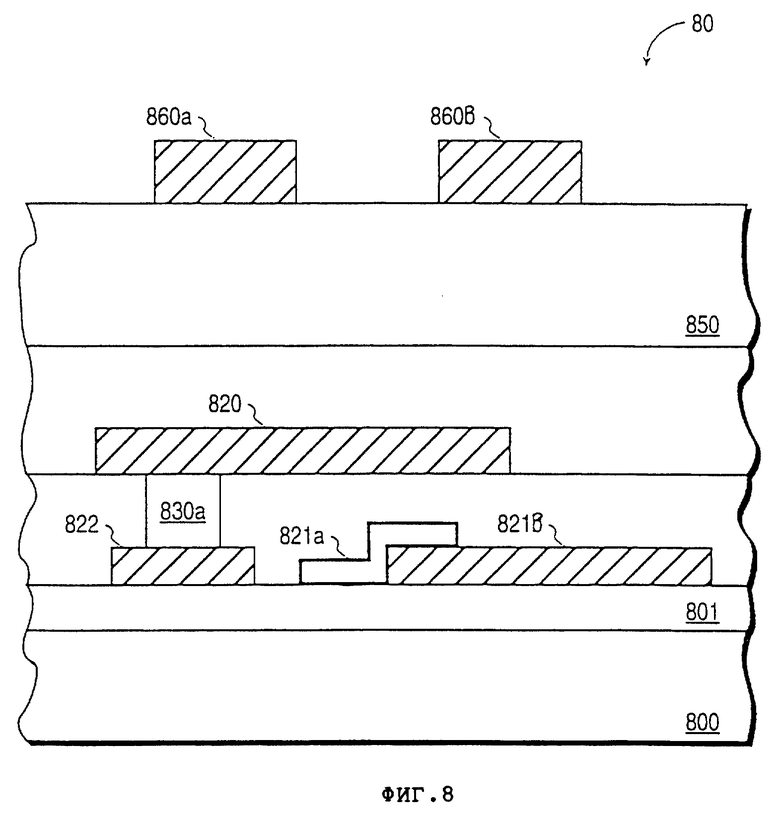

Фиг. 8 изображает поперечное сечение ячейки памяти фиг. 7 по линии 730. Подложка 800 и слой диэлектрика 801 аналогичны подложке 600 и слою диэлектрика 601, и поэтому их формируют согласно методам, описываемым подробно выше со ссылкой на фиг. 6.

Пересечение 820 содержит первый металлический слой межсоединения. Пересечение 821 содержит два межсоединения 821а и 821в. Межсоединение 821а содержит слой местного межсоединения, описываемый подробнее ниже. Межсоединение 821в формируют слоем затвора, аналогичным пересечению 621 фиг. 6. Межсоединение 821в поэтому выполняют согласно методам, которые описаны выше со ссылкой на пересечение 621 фиг. 6.

Межсоединение 821а выполняют в слое местного межсоединения. Слой местного межсоединения состоит из проводящего материала, который находится непосредственно сверху слоя затвора, такого как межсоединение 721в, и также сверху диффузионных областей, таких как исток и сток транзисторов 713 и 712. В одном из вариантов осуществления слой местного межсоединения содержит титан (Ti). Либо слой местного межсоединения содержит нитрид титана (TiN) или вольфрам (W). Слой местного межсоединения может содержать один из многих хорошо известных проводящих материалов, подходящих для применения в качестве межсоединений устройства. Слой местного межсоединения формируют осаждением проводящего материала согласно известному методу осаждения, такому как ЗОПФ, испарение или распыление. На проводящем материале затем создают рисунок (т. е. с помощью описанных выше этапов фоторезиста или травления), чтобы создать межсоединение 821в.

Межсоединение 822 формируют из материала затвора и применяют для соединения затворов транзисторов 713 и 714. Для одного из вариантов осуществления межсоединение 822 содержит поликремний, и его формируют в соответствии с методами, описываемыми вместе с пересечением 621 и межсоединением 622 фиг. 6.

Слой диэлектрического материала осаждают сверху пересечений 821а, 821в и 822. После этого формируют контакт 830а для соединения пересечения 820 со входом инвертора, содержащего транзисторы 712 и 713. Пересечение 820 содержит первый металлический слой межсоединения, который осаждают и протравливают согласно описываемым выше методам со ссылкой на первый металлический слой межсоединения фиг. 6. Пересечение 820 соединяет вход инвертора, содержащего транзисторы 713 и 712, с выходом инвертора, содержащего транзисторы 710 и 711. Еще один слой диэлектрика осаждают сверху пересечения 820, и после этого может быть сформирован металлический слой межсоединения второго уровня (не изображен). Затем по желанию можно чередовать слои диэлектрика и металла. В соответствии с изображением фиг. 8 два межсоединения 860а и 860в содержат третий слой металлического межсоединения, который можно использовать для связи с другими схемами (не изображены).

В изложенном выше подробном описании описана конструкция ячейки памяти с вертикально расположенными друг над другом пересечениями. Конструкция памяти согласно данному изобретению описывается со ссылкой на конкретные материалы, технологические методы и варианты конструкции схемы. Следует отметить, что в рамках данного изобретения можно произвести разнообразные замены и модификации.

Например, одно пересечение можно выполнить в первом металлическом слое межсоединения, а другое - во втором металлическом слое межсоединения. Многие варианты конструкции зависят от конкретного технологического процесса создания ячейки памяти. Описание и чертежи, соответственно, следует рассматривать скорее как иллюстрацию, а не ограничение.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАЩИТНОЕ КОЛЬЦО ДЛЯ СНИЖЕНИЯ ТЕМНОВОГО ТОКА | 1998 |

|

RU2178600C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444891A1 |

| ТЕХНОЛОГИЯ СОЗДАНИЯ СОЕДИНЕНИЙ СКВОЗЬ МАТРИЦУ ЯЧЕЕК ПАМЯТИ В ЭНЕРГОНЕЗАВИСИМОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 2015 |

|

RU2661992C2 |

| СОХРАНЕНИЕ ПЕРЕРАСПРЕДЕЛЯЮЩИХ ТОКОПРОВОДЯЩИХ ДОРОЖЕК, ИМЕЮЩИХ МЕЛКИЙ ШАГ | 2013 |

|

RU2631911C2 |

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2029393C1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2642960C2 |

| СПОСОБЫ ФОРМИРОВАНИЯ ПРОТИВООТРАЖАЮЩИХ СТРУКТУР ДЛЯ ДАТЧИКОВ ИЗОБРАЖЕНИЯ НА ОСНОВЕ КМОП-ТЕХНОЛОГИИ | 2009 |

|

RU2492554C2 |

Изобретение относится к вычислительной цифровой технике, конкретно к конструкции ячейки памяти с вертикально расположенными друг над другом пересечениями. Ячейка памяти согласно изобретению содержит первый транзисторный инвертор, имеющий первый вход и первый выход, и второй инвертор, имеющий второй вход и второй выход. Первый и второй транзисторы связаны с первым и вторым пересекающимися соединениями. Первое пересекающееся соединение соединяет первый вход со вторым выходом. Второе пересекающееся соединение соединяет второй вход с первым выходом. Два пересекающихся соединения содержат разные проводящие слои в процессе изготовления полупроводника. Данное изобретение выполняет пересечения в разных материалах на разных слоях устройства. Поэтому пересечения могут размещаться вертикально друг над другом, тем самым сокращая площадь ячейки памяти. Технический результат: снижение себестоимости за счет уменьшения размера элемента, повышение надежности ячейки памяти в запоминающих устройствах. 3 с. и 22 з.п.ф-лы, 8 ил.

| EP 0698287 A1, 28.02.1996 | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| US 5485420 A, 16.01.1996 | |||

| US 5491654 A, 13.02.1996 | |||

| СПОСОБ ИЗМЕНЕНИЯ ПРОВОДИМОСТИ КАНАЛА ИСТОК - СТОК ПОЛЕВОГО ТРАНЗИСТОРА | 1991 |

|

RU2007785C1 |

| US 5065215 A, 12.11.1991 | |||

| Устройство для расчаливания стрелы самоходного крана | 1971 |

|

SU491581A2 |

Авторы

Даты

2000-09-10—Публикация

1997-03-20—Подача