(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения кодов | 1990 |

|

SU1758643A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

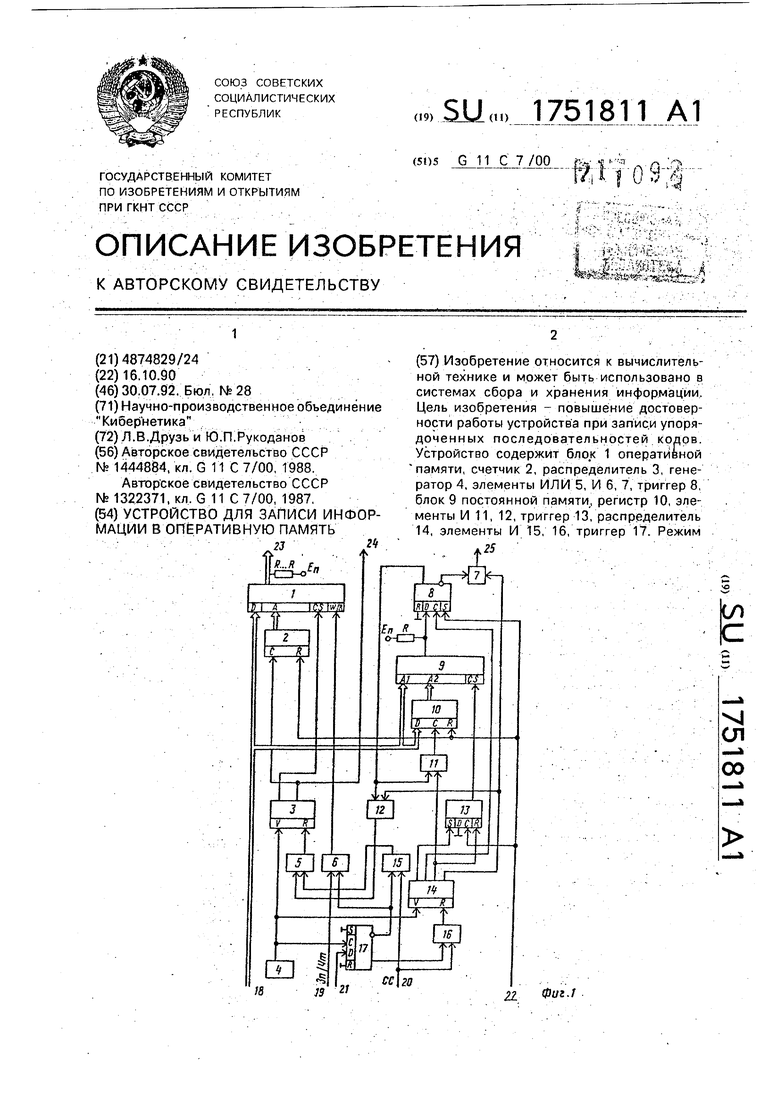

Изобретение относится к вычислительной технике и может быть использовано в системах сбора и хранения информации Цель изобретения - повышение достоверности работы устройства при записи упорядоченных последовательностей кодов Устройство содержит блок 1 оперативной памяти, счетчик 2, распределитель 3, генератор 4, элементы ИЛИ 5, И 6, 7, триггер 8 блок 9 постоянной памяти, регистр 10, элементы И 11, 12, триггер 13, распределитель 14, элементы И 15, 16, триггер 17. Режим л. 25

vi ел

00

контроля устанавливает триггер 17, управляющий элементами И 6, 15, 16, Байты информации последовательности поступают в блок 1, регистр 10 и адресные входы блока 9. В регистре 10 хранится код предыдущего байта информации и подается на другие входы адреса блока 9. Блок 9 запрограммирован таким образом, что в ячейки, адресуемые кодами предыдущих и последующих байтов последовательности, записаны сигналы Лог,1. Сигналы сопровождения информации включают распределитель 14, который организует циклы обращения к блоку 9. При правильной очередности кодов последовательности из блока 9 считывается

Изобретение относится к вычислительной технике и может быть использовано в системах сб,ора и хранения информации.

Известно буферное запоминающее устройство, содержащее регистр, блок памяти, триггеры, счетчики, генератор импульсов, распределитель, элементы И.

Однако в известром устройстве в режиме записи информации не обеспечивается контроль принимаемой информации, что снижает достоверность работы устройства.

Наиболее близким к предлагаемому является устройство для записи информации в оперативную память, содержащее генератор импульсов, распределитель, регистры, счетчики, элементы И, ИЛИ, триггер, блок памяти, формирователь импульсов, блок ввода Недостаток этого устройства заключается в том, что при записи в оперативную память упорядочения последовательностей кодов, например, формализованных массивов, наборов микрокоманд для выполнения стандартных операций и т.п. не обеспечивается контроль очередности этих кодов, что снижает достоверность хранимой в памяти информации, а последующее считывание неправильных последовательностей из памяти приводит к срыву технологических процессов.

Целью изобретения является повышение достоверности при записи упорядоченной последоеательности кодов.

Поставленная цель достигается тем, что в устройство для записи информации в оперативную память, содержащее блок оперативной памяти, адресные входы которого соединены с выходами счетчика, регистр, первый распределитель, тактовый вход которого соединен с выходом генератора импульсов, первый триггер, первый и второй элементы И, элемент ИЛИ, введены блок постоянной памяти, второй распределисигнал Лог.1, триггер 8 устанавливается в единичное состояние, запускается распределитель 3, организующий цикл записи инфор- мации в блок 1 оперативной памяти. Адресация ячеек блока 1 обеспечивается счетчиком 2, При нарушении очередности кодов упорядоченной последовательности из блока 9 считываются сигналы Лог.О, которые устанавливают триггер 8 в нулевое положение, и через элемент И 7 выдается сигнал ошибки. В режимах считывания информации и записи произвольных массивов в блок 1 оперативной памяти включается распределитель 3. 3 ил , 1 табл.

тель, второй и третий триггеры, с третьего по шестой элементы И, причем информационные входы устройства соединены с информационными входами блока оперативной

памяти, первыми адресными входами блока постоянной памяти и информационными входами регистра, выходы которого соединены с вторыми адресными входами блока постоянной памяти, выход которого соединен с информационным входом первого триггера, инверсный выход которого соединен с первым входом первого элемента И, прямой выход - с первыми входами второго и третьего элементов И, выход третьего элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с входом сброса первого распределителя, первый вход которого соединен с входом выборки блока оперативной памяти, второй выход - с тактовым входом

счетчика и выходом запроса информации устройства, вход установки режима запись/чтение которого соединен с первым входом четвертого элемента И, выход которого соединен с управляющим входом запись-чтение блока оперативной памяти, выходы которого соединены с информационными выходами устройства, вход сигнала сопровождения информации которого соединён с первыми входами пятого и шестого

элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами второго триггера, инверсный выход которого соединен с вторым входом четвертого элемента И, выход пятого элемента И соединен с вторым входом элемента ИЛИ, вход установки режима контроля устройства соединен с информационным входом второго триггера, тактовый вход которого соединен с выходом генератора импульсов и тактовым входом второго распределителя, вход сброса которого соединен с выходом шестого элемента И, первый и втретий выходы второго распределителя соединены соответственно с единичным входом и входом сброса третьего триггера, выход которого соединен с входом выборки блока постоянной памяти, второй выход второго распределителя соединен с тактовым входом первого триггера, третий выход - с вторым входом второго элемента И, выход которого соединен с тактовым входом регистра, вход сброса которого объединен с входом сброса счетчика, с тактовым входом третьего триггера, с единичным входом первого триггера и входом начальной установки устройства, выход сигнала ошибки которого соединен с выходом первого элемента И, второй вход которого объединен с вторым входом третьего элемента И и четвертым выходом второго распределителя, а вход сброса первого триггера и информационный вход третьего триггера подключены к общей шине питания.

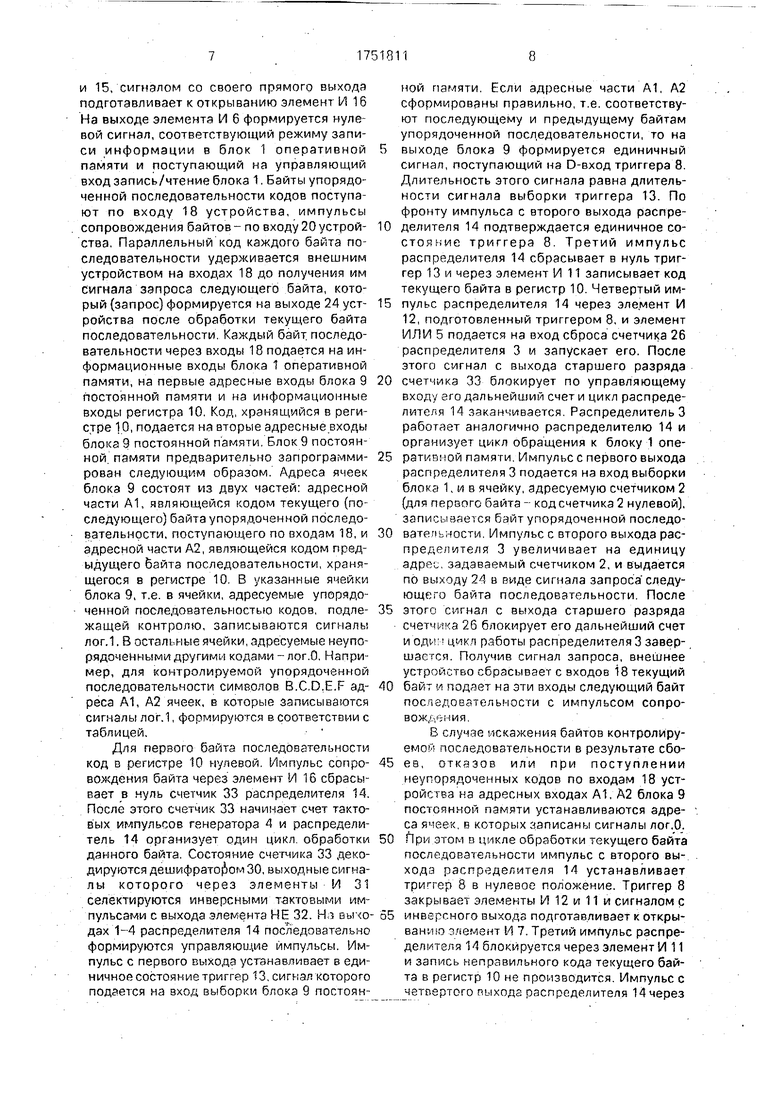

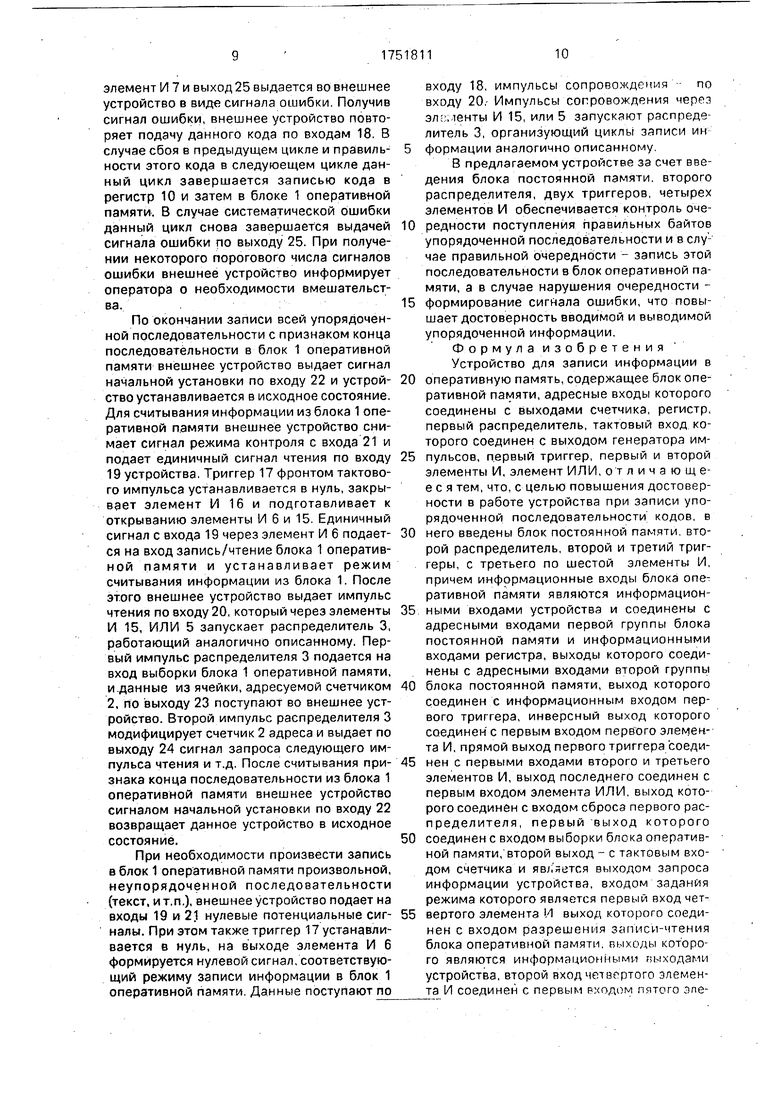

На фиг,1 изображена функциональная схема устройства; на фиг.2 и 3 - схемы распределителей.

Устройство содержит блок 1 оперативной памяти, счетчик 2, первый распределитель 3, генератор 4 импульсов, элемент ИЛИ 5, четвертый элемент И 6, первый элемент И 7, первый триггер 8, блок 9 постоянной памяти, регистр 10, второй элемент И 11, третий элемент И 12, третий тригер 13, второй распределитель 14, пятый элемент И 15, шестой элемент И 16, второй триггер 17, информационный вход 18, вход 19 установки режима запись-чтение, вход 20 сигнала сопровождения информации, вход 21 установки режима контроля, вход 22 начальной установки, информационный выход 23, выход 24 запроса информации, выход 25 сигнала ошибки.

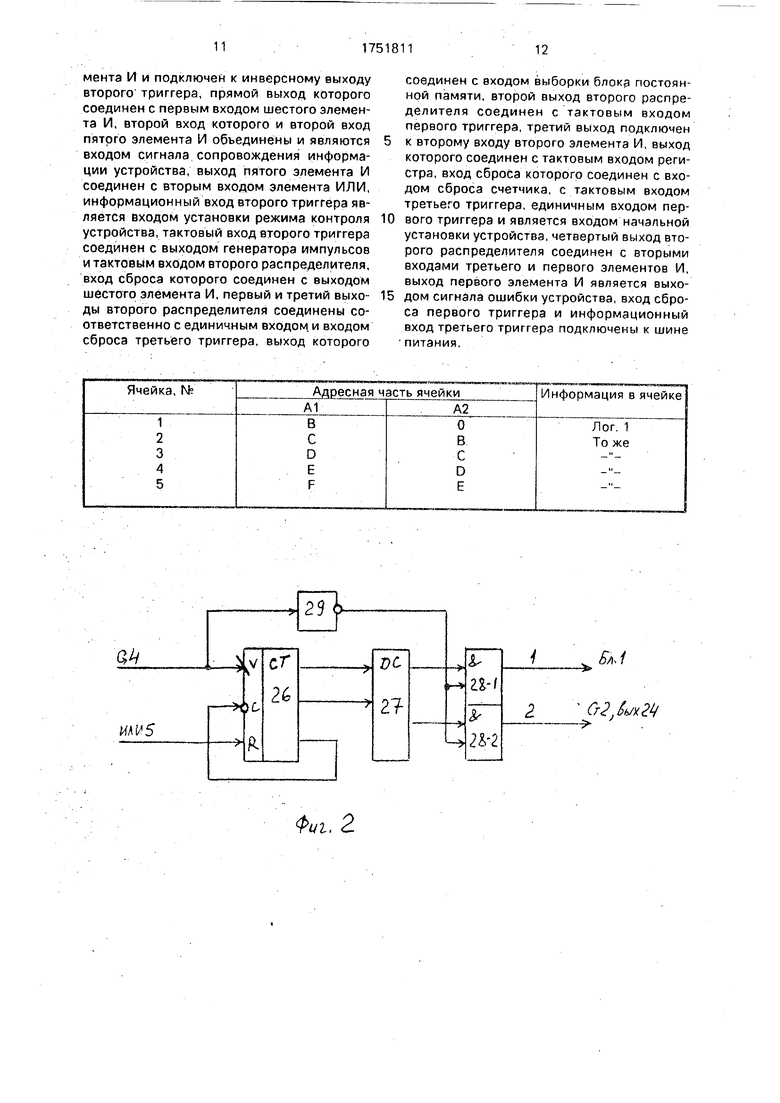

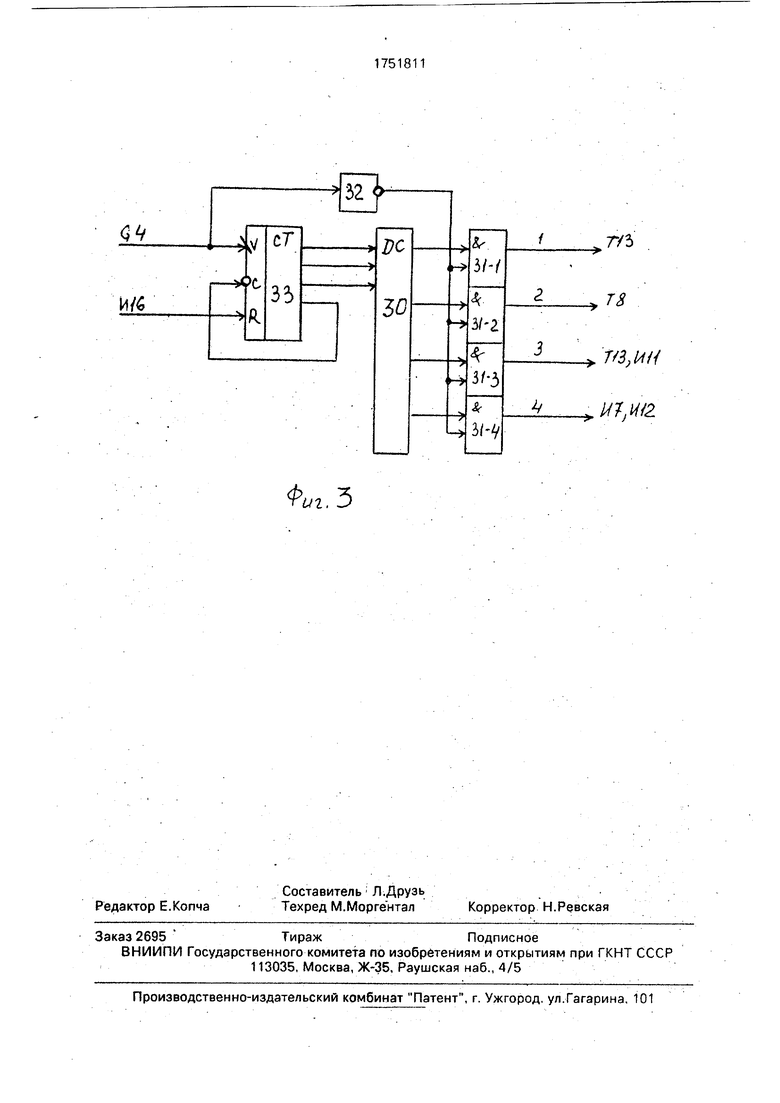

Распределитель 3 (фиг,2) содержит счетчик 26, дешифратор 27, элементы И 28 и НЕ 29. Распределитель 14 (фиг.З) содержит дешифратор 30, элементы И 31, НЕ 32, счетчик 33. Блок 1 оперативной памяти может быть выполнен, например, на микросхемах типа 541РУ1, блок 9 постоянной памяти - на микросхеме 556РТ7, стальные блоки устройства - на микросхемах 564-й серии. Выходы блоков 1 и 9 памяти связаны с шинами источника питания через согласующие резисторы.

Входы 20 соединены с входами блока 1 памяти, адресными входами блока 9 памяти и регистром 10, подключенным выходами к другим адресным входам блока 9 памяти. Выход генератора 4 соединен с распределителями 3 и 14и триггером 17. Входы 19 и 20 соединены соответственно с элементами И

6, 15 и 16. вход 21 - с триггером 17. вход 22 - с входами сброса счетчика 2, регистра 10, та -говым входом триггера 13 и единичным входом триггера 8. Выходы триггера 17 сое- 5 динены с эпементами И 16, 15 и 6. Выходы элементов И 12 и 15 соединены с элементом ИЛИ 5, выходом подключенным к входу сброса распределителя 3. Выход элемента И 6 соединен с входом управления блока 1

10 памяти, вход выборки которого соединен с первым выходом распределителя 3, второй выход которого соединен с входом счетчика 2 и выходом 24 устройства. Выход элемента И 16 соединен с входом сброса распредели5 теля 14, первый и третий выходы которого соединены с установочными входами триггера 13 и элементом И 11, второй выход - с триггером 8, четвертый выход - с элементами И 7 и 12. Выход триггера 13 соединен с

0 входом выборки блока 9 памяти, выход которого соединен с триггером 8. Прямой и инверсный выходы триггеры 8 соединены соответственно с элементами И 7, 11 и 12, Выходы блока 1 памяти соединены с выхо5 дами 23, выход элемента И 7 - с выходом 25 устройства.

Устройство работает следующим образом.

После включения питания запускается

0 генератор 4 импульсов, с выхода которого тактовые импульсы непрерывно подаются на счетный вход счетчиков 26 и 33 распределителей 3 и 14. При отсутствии сигналов на входах сброса счетчиков 26 и 33 послед5 ние заполняются тактовыми импульсами до появления сигналов на выходах их старших разрядов, которые по управляющим входам блокируют дальнейший счет импульсов в этих счетчиках. Счетчики 26 и 33 фиксируют0 ся в указанном положении, на выходах распределителей 3 и 14 формируются нулевые сигналы. Для установки исходного состояния устройства по входу 22 подается импульсный сигнал, который устанавливает в

5 нуль счетчик 2, регистр 10, триггер 13 и в единичное состояние триггер 8. Последний сигналом со своего инверсного выхода закрывает элемент 14 7, сигналом со своего прямого выхода подготавливает к открыва0 нию элементы И 11 и 12. Для приема и записи упорядоченной последовательности кодов по входу 21 подается единичный потенциальный сигнал, который поступает на D-вход триггера 17. По фронту тактового

5 импульса генератора 4 триггер 17 устанавливается в единичное состояние и в дальнейшем сохраняет это состояние до момента снятия сигнала режима контроля с входа 21. Триггер 17 сигналом со своего инверсного выхода закрывает элементы И 6

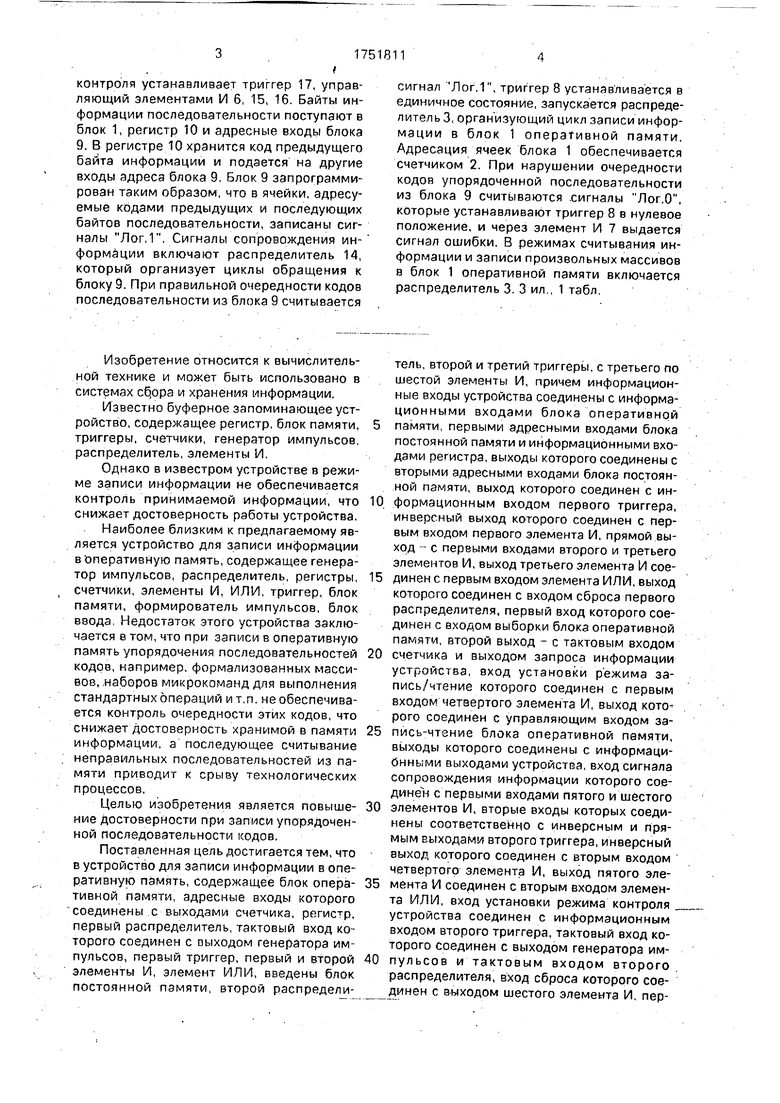

и 15, сигналом со своего прямого выходя подготавливает к открыванию элемент И 16 На выходе элемента И 6 формируется нулевой сигнал, соответствующий режиму записи информации в блок 1 оперативной памяти и поступающий на управляющий вход запись/чтение блока 1. Байты упорядоченной последовательности кодов поступают по входу 18 устройства, импульсы сопровождения байтов - по входу 20 устройства, Параллельный код каждого байта последовательности удерживается внешним устройством на входах 18 до получения им сигнала запроса следующего байта, который (запрос) формируется на выходе 24 устройства после обработки текущего байта последовательности. Каждый байт последовательности через входы 18 подается на информационные входы блока I оперативной памяти, на первые адресные входы блока 9 постоянной памяти и на информационные входы регистра 10. Код, хранящийся в регистре 10, подается ня вторые адресные входы блока 9 постоянной памяти, Блок 9 постоянной памяти предварительно запрограммирован следующим образом. Адреса ячеек блока 9 состоят из двух частей: адресной части А1, являющейся кодом текущего (последующего) байта упорядоченной последовательности, поступающего по входам 18, и адресной части А2, являющейся кодом предыдущего байта последовательности, хранящегося в регистре 10. В указанные ячейки блока 9, т.е. в ячейки, адресуемые упорядоченной последовательностью кодов, подлежащей контролю, записываются сигналы лог.1. В остальные ячейки, адресуемые неупорядоченными другими кодами - лог.О, Например, для контролируемой упорядоченной последовательности символов B.C.D.E.F адреса А1, А2 ячеек, в которые записываются сигналы лог.1, формируются в соответствии с таблицей.

Для первого байта последовательности код в регистре 10 нулевой. Импульс сопровождения байта через элемент И 16 сбрасывает в нуль счетчик 33 распределителя 14. После этого счетчик 33 начинает счет тактовых импульсов генератора 4 и распределитель 14 организует один цикл обработки данного байта. Состояние счетчика 33 декодируются дешифратором 30, выходные сигналы которого через элементы И 31 селектируются инверсными тактовыми импульсами с выхода элемента НЕ 32. выходах 1-4 распределителя 14 последовательно формируются управляющие импульсы. Импульс с первого выхода устанавливает в единичное состояние триггер 13, сигнал которого подается на вход выборки блока 9 постоянной памяти. Если адресные части А1, А2 сформированы правильно, т.е. соответствуют последующему и предыдущему байтам упорядоченной последовательности, то на

выходе блока 9 формируется единичный сигнал, поступающий на D-вход триггера 8. Длительность этого сигнала равна длительности сигнала выборки триггера 13. По фронту импульса с второго выхода распре0 делителя 14 подтверждается единичное состояние триггера 8. Третий импульс распределителя 14 сбрасывает в нуль триггер 13 и через элемент И 11 записывает код текущего байта в регистр 10. Четвертый им5 пульс распределителя 14 через элемент И 12, подготовленный триггером 8, и элемент ИЛИ 5 подается на вход сброса счетчика 26 распределителя 3 и запускает его. После этого сигнал с выхода старшего разряда

0 счетчика 33 блокирует по управляющему входу его дальнейший счет и цикл распределителя 14 заканчивается. Распределитель 3 работает аналогично распределителю 14 и организует цикл обращения к блоку 1 опе5 ратив:юй памяти. Импульс с первого выхода распределителя 3 подается на вход выборки блока 1, и в ячейку, адресуемую счетчиком 2 (для первого байта - код счетчика 2 нулевой), записывается байт упорядоченной последо0 ватепь;-|ости. Импульс с второго выхода распределителя 3 увеличивает на единицу адрес, задаваемый счетчиком 2, и выдается по выходу 24 в виде сигнала запроса следующего байта последовательности. После

5 этого сигнал с выхода старшего разряда счетпика 26 блокирует его дальнейший счет иод цикт работы распределителя 3 завершается. Получив сигнал запроса, внешнее устройство сбрасывает с входов 18 текущий

0 байт / подает на эти входы следующий байт последовательности с импульсом СОПрО- ВОЖг - ИИЯ

В случае искажения байтов контролируемо последовательности в результате сбо5 ев, откчэов или при поступлении неупорядоченных кодов по входам 18 устройства на адресных входах А1, А2 блока 9 постоянной памяти устанавливаются адреса , в которых записаны сигналы лог.О.

0 При этом в цикле обработки текущего байта последовательности импульс с второго выхода распределителя 14 устанавливает триггер 8 в нулевое положение. Триггер 8 закрывает элементы И 12 и 11 и сигналом с

5 инверсного выхода подготавливает к открыванию с емент И 7, Третий импульс распределителя 14 блокируется через элемент И 11 и запись неправильного кода текущего байта в регистр 10 не производится. Импульс с Четвертого пыхода распределителя 14 через

элемент И 7 и выход 25 выдается во внешнее устройство в виде сигнала ошибки. Получив сигнал ошибки, внешнее устройство повторяет подачу данного кода по входам 18. В случае сбоя в предыдущем цикле и правильности этого кода в следуюещем цикле данный цикл завершается записью кода в регистр 10 и затем в блоке 1 оперативной памяти. В случае систематической ошибки данный цикл снова завершается выдачей сигнала ошибки по выходу 25. При получении некоторого порогового числа сигналов ошибки внешнее устройство информирует оператора о необходимости вмешательства.

По окончании записи всей упорядоченной последовательности с признаком конца последовательности в блок 1 оперативной памяти внешнее устройство выдает сигнал начальной установки по входу 22 и устройство устанавливается в исходное состояние. Для считывания информации из блока 1 оперативной памяти внешнее устройство снимает сигнал режима контроля с входа 21 и подает единичный сигнал чтения по входу 19 устройства. Триггер 17 фронтом тактового импульса устанавливается в нуль, закрывает элемент И 16 и подготавливает к открыванию элементы И 6 и 15. Единичный сигнал с входа 19 через элемент И 6 подается на вход запись/чтение блока 1 оперативной памяти и устанавливает режим считывания информации из блока 1. После этого внешнее устройство выдает импульс чтения по входу 20, который через элементы И 15, ИЛИ 5 запускает распределитель 3, работающий аналогично описанному. Первый импульс распределителя 3 подается на вход выборки блока 1 оперативной памяти, и данные из ячейки, адресуемой счетчиком 2, по выходу 23 поступают во внешнее устройство. Второй импульс распределителя 3 модифицирует счетчик 2 адреса и выдает по выходу 24 сигнал запроса следующего импульса чтения и т.д. После считывания признака конца последовательности из блока 1 оперативной памяти внешнее устройство сигналом начальной установки по входу 22 возвращает данное устройство в исходное состояние.

При необходимости произвести запись в блок 1 оперативной памяти произвольной, неупорядоченной последовательности (текст, и т.п.), внешнее устройство подает на входы 19 и 21 нулевые потенциальные сигналы. При этом также триггер 17 устанавливается в нуль, на выходе элемента И 6 формируется нулевой сигнал, соответствующий режиму записи информации в блок 1 оперативной памяти. Данные поступают по

входу 18, импульсы сопровождения по входу 20.- Импульсы сопровождения через эл: менты И 15, или 5 зэпускяют распределитель 3, организующий циклы записи ин 5 формации аналогично описанному.

В предлагаемом устройстве за счет введения блока постоянной памяти, второго распределителя, двух триггеров, четырех элементов И обеспечивается контроль оче- 0 редности поступления правильных байтов упорядоченной последовательности и в случае правильной очередности - запись этой последовательности в блок оперативной памяти, а в случае нарушения очередности 5 формирование сигнала ошибки, что повышает достоверность вводимой и выводимой упорядоченной информации.

Формула изобретения Устройство для записи информации в

0 оперативную память, содержащее блок оперативной памяти, адресные входы которого соединены с выходами счетчика, регистр, первый распределитель, тактовый вход которого соединен с выходом генератора им5 пульсов, первый триггер, первый и второй элементы И, элемент ИЛИ, отличающееся тем, что, с целью повышения достоверности в работе устройства при записи упорядоченной последовательности кодов, в

0 него введены блок постоянной памяти, второй распределитель, второй и третий триггеры, с третьего по шестой элементы И, причем информационные входы блока оперативной памяти являются информацион5 ными входами устройства и соединены с адресными входами первой группы блока постоянной памяти и информационными входами регистра, выходы которого соединены с адресными входами второй группы

0 блока постоянной памяти, выход которого соединен с информационным входом первого триггера, инверсный выход которого соединен с первым входом первого элемента И, прямой выход первого триггера соеди5 нен с первыми входами второго и третьего элементов И, выход последнего соединен с первым входом элемента ИЛИ, выход которого соединен с входом сброса первого рас- пределителя, первый выход которого

0 соединен с входом выборки блока оперативной памяти, второй выход - с тактовым входом счетчика и является выходом запроса информации устройства, входом задания режима которого является первый вход чет5 вертого элемента И выход которого соединен с входом разрешения записи-чтения блока оперативной памяти, выходы которого являются информационными выходами устройства, второй вход четвертого элемента И соединен с первым входом пятого злемента И и подключен к инверсному выходу второго триггера, прямой выход которого соединен с первым входом шестого элемента И, второй вход которого и второй вход пятого элемента И объединены и являются входом сигнала сопровождения информации устройства, выход пятого элемента И соединен с вторым входом элемента ИЛИ, информационный вход второго триггера является входом установки режима контроля устройства, тактовый вход второго триггера соединен с выходом генератора импульсов и тактовым входом второго распределителя, вход сброса которого соединен с выходом шестого элемента И, первый и третий выходы второго распределителя соединены соответственно с единичным входом и входом сброса третьего триггера, выход которого

Фиг. 2

соединен с входом выборки блока постоянной памяти, второй выход второго распределителя соединен с тактовым входом первого триггера, третий выход подключен

к второму входу второго элемента И, выход которого соединен с тактовым входом регистра, вход сброса которого соединен с входом сброса счетчика, с тактовым входом третьего триггера, единичным входом первого триггера и является входом начальной установки устройства, четвертый выход второго распределителя соединен с вторыми входами третьего и первого элементов И, выход первого элемента И является выходом сигнала ошибки устройства, вход сброса первого триггера и информационный вход третьего триггера подключены к шине питания.

4V3

| Буферное запоминающее устройство | 1987 |

|

SU1444884A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для записи информации в оперативную память | 1986 |

|

SU1322371A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-07-30—Публикация

1990-10-16—Подача