При реализации электронных схем в виде интегральной схемы на полупроводниковом кристалле иногда является необходимым подключать более высокие, чем напряжения питания, напряжения на кристалле к схемам или их частям. Эти высокие положительные или отрицательные напряжения могут при этом или подводиться к кристаллу дополнительно к обычным напряжениям питания или создаваться посредством насосов заряда на кристалле из напряжений питания. В каждом случае следует заботиться о надежном и быстром включении, причем падение напряжения на переключателе должно быть как можно малым.

В современных флеш-накопителях (Flash - стираемые световой вспышкой накопители), а в будущем также и для стандартных электронно-стираемых программируемых постоянных накопителей (EEPROM) необходимо прикладывать к ним для выбора линии слов отрицательное напряжение линии слов. Не выбранные линии слов удерживаются в этом случае на потенциале 0 В.

В EP 0456623 A2 импульсным положительным высоким напряжением через конденсатор в схеме инвертирования напряжения затвор p-МОП-передаточного транзистора имеет отрицательную полярность, так что отрицательное напряжение попадает от насоса заряда к линии слов накопителя. Вследствие токов утечки в соединениях эта схема должна эксплуатироваться в пакетном режиме работы. Это значит, что до конца программирования требуются повторяющиеся импульсы, откуда получается высокая мощность потерь.

Так как на кристалле накопителя кроме накопительных ячеек в большинстве случаев выполнены дополнительно имеющиеся логические схемы в МОП-технике и такие схемы таким образом в соответствии со стандартом эксплуатируются с чисто положительными напряжениями, должна быть гарантирована изоляция отрицательного напряжения относительно подложки полупроводниковой интегральной схемы. Это может достигаться, например, посредством изолированных ванн в так называемой технике "triple well".

При этом в p-подложке p-ванна для n-канальных транзисторов расположена в глубокой n-ванне и изолирована ею от p-подложки. Такая глубокая ванна получается за счет высокоэнергетического внедрения, обычно от 1 доз МэВ, с фосфором в качестве легирующего материала или за счет более низкой энергии и экстремально долгого времени диффузии.

Задачей изобретения является указание МОП-устройства для включения отрицательных, а в форме дальнейшего развития также положительных высоких напряжений посредством чисто положительного уровня включения на полупроводниковой интегральной схеме, которая не требует никакой изолированной ванны (никаких изолированных ванн).

Эта задача решается устройствами согласно пунктам 1 и 3 формулы изобретения. Предпочтительные дальнейшие формы развития изобретения приведены в зависимых пунктах формулы изобретения.

Особое преимущество соответствующего изобретению устройства заключается в том, что для технологической реализации не требуются никакие дорогие установки или соответственно большие времена нагрева для операции диффузионного процесса. Не нужны также никакие дополнительные операции процесса, так как в КМОП-технике транзисторы того же типа проводимости, что и подложка, уже реализованы в ванне и таким образом такая операция процесса при реализации КМОП-техники уже имеется.

Соответствующее изобретению устройство является особенно пригодным для включения отрицательных или в форме дальнейшего развития также положительных программирующих или соответственно стирающих напряжений на линиях слов флеш-накопителя (Flash-) или также электронно-стираемого программируемого постоянного накопителя (EEPROM), причем каждый раз можно выбирать только одну линию слов.

Изобретение поясняется ниже на примерах выполнения с помощью фигур. При этом на фигурах показано:

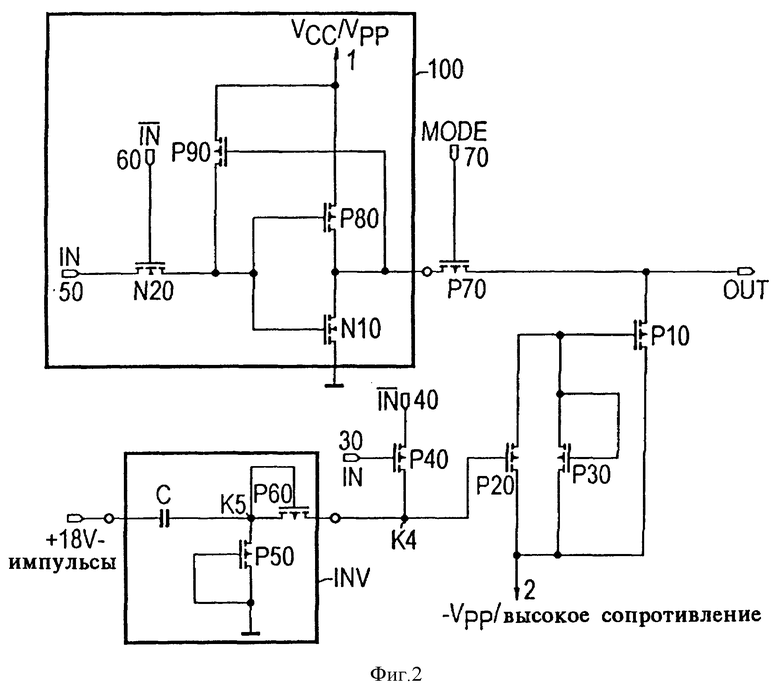

фигура 1 - первый вариант соответствующего изобретению устройства,

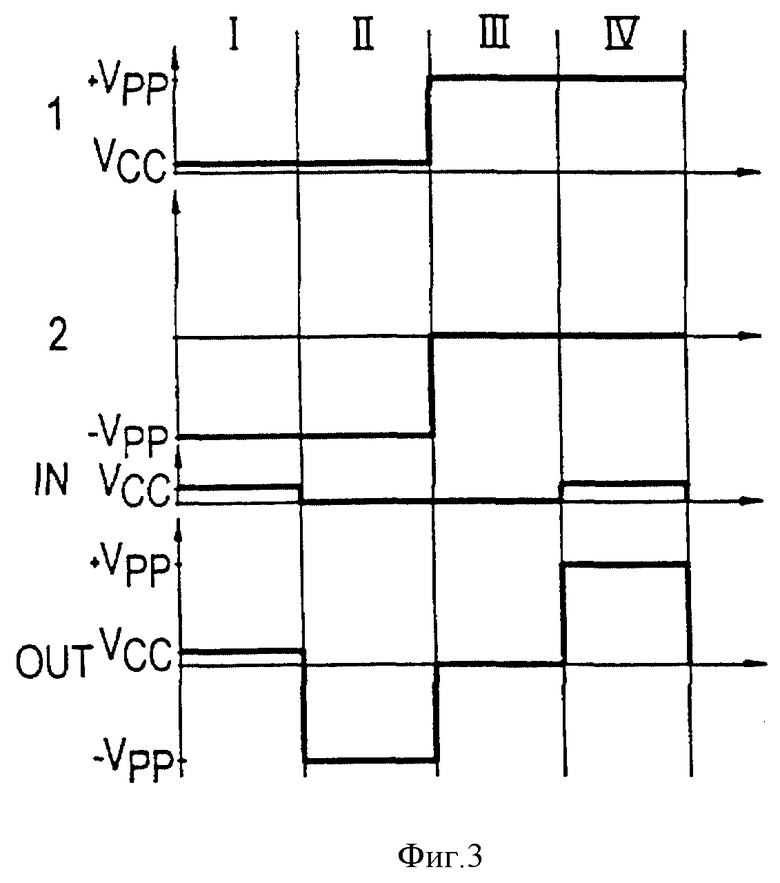

фигура 2 - второй вариант соответствующего изобретению устройства и

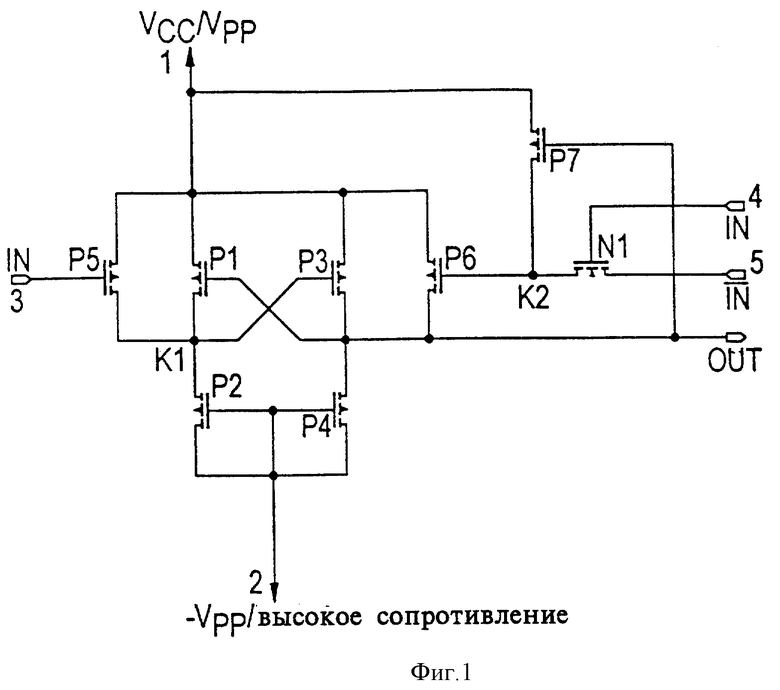

фигура 3 - представление подлежащих приложению к первому варианту напряжений, чтобы получить желаемое выходное напряжение.

Показанное на фигуре 1 устройство позволяет включать приложенное на его первом выводе 1 высокое напряжение Vpp или приложенное на втором выводе 2 высокое отрицательное напряжение -Vpp в зависимости от входного сигнала IN,  на управляющих выводах 3, 4, 5 на выходной вывод OUT. Пример относится к реализации устройства в виде интегральной схемы в p-подложке с выполненными в n-ваннах p-канальными транзисторами. Эквивалентным образом конечно могут реализовываться в n-подложке n-канальные транзисторы. Между первым выводом 1 и вторым выводом 2 включена первая последовательная схема из первого транзистора P1 и второго транзистора P2, а также параллельно ей вторая последовательная схема из третьего транзистора P3 и четвертого транзистора P4. Выводы затворов второго и четвертого транзисторов P2, P4 соединены также со вторым выводом 2, так что оба транзистора P2, P4 действуют как реализованные на диодах источники тока. Вывод затвора третьего транзистора P3 соединен с точкой соединения K1 первого и второго транзисторов P1, P2, а вывод затвора первого транзистора P1 соединен с образующей выходной вывод OUT точкой соединения третьего транзистора P3 и четвертого транзистора P4. Транзисторы P1 - P4 при этом имеют такие параметры, что в случае, когда второй и четвертый транзисторы P2, P4 включены проводяще, сначала точка соединения K1 первого и второго транзисторов P1, P2 подтягивается до второго вывода 2 так, что третий транзистор P3 проводит и таким образом подтягивает выходной вывод OUT до положительного потенциала, приложенного на первом выводе 1, так что первый транзистор P1 запирается. Параллельно нагрузочному участку первого транзистора P1 включен нагрузочный участок пятого транзистора P5. Вывод затвора этого пятого транзистора P5 соединен с управляющим выводом 3.

на управляющих выводах 3, 4, 5 на выходной вывод OUT. Пример относится к реализации устройства в виде интегральной схемы в p-подложке с выполненными в n-ваннах p-канальными транзисторами. Эквивалентным образом конечно могут реализовываться в n-подложке n-канальные транзисторы. Между первым выводом 1 и вторым выводом 2 включена первая последовательная схема из первого транзистора P1 и второго транзистора P2, а также параллельно ей вторая последовательная схема из третьего транзистора P3 и четвертого транзистора P4. Выводы затворов второго и четвертого транзисторов P2, P4 соединены также со вторым выводом 2, так что оба транзистора P2, P4 действуют как реализованные на диодах источники тока. Вывод затвора третьего транзистора P3 соединен с точкой соединения K1 первого и второго транзисторов P1, P2, а вывод затвора первого транзистора P1 соединен с образующей выходной вывод OUT точкой соединения третьего транзистора P3 и четвертого транзистора P4. Транзисторы P1 - P4 при этом имеют такие параметры, что в случае, когда второй и четвертый транзисторы P2, P4 включены проводяще, сначала точка соединения K1 первого и второго транзисторов P1, P2 подтягивается до второго вывода 2 так, что третий транзистор P3 проводит и таким образом подтягивает выходной вывод OUT до положительного потенциала, приложенного на первом выводе 1, так что первый транзистор P1 запирается. Параллельно нагрузочному участку первого транзистора P1 включен нагрузочный участок пятого транзистора P5. Вывод затвора этого пятого транзистора P5 соединен с управляющим выводом 3.

С этой частью представленного на фигуре 1 устройства уже возможно приложенное на выводе 2 высокое отрицательное напряжение -Vpp включать на выходной вывод OUT посредством приложенного на управляющем входе 3 входного сигнала IN, если на первом выводе 1 приложено напряжение питания Vcc полупроводниковой интегральной схемы. Это представлено на фигуре 3 в обозначенных I и II временных интервалах. Пока на управляющем выводе 3 состояние входного сигнала IN соответствует высокому логическому уровню High, а именно для КМОП-схем соответствует примерно значению положительного напряжения питания Vcc, пятый транзистор P5 запирается. Так как второй и четвертый транзисторы P2, P4 находятся в проводящем состоянии, то вследствие подходящего выбора параметров транзисторов P1-P4 точка соединения K1 первого и второго транзисторов подтягивается до потенциала -Vpp на втором выводе 2 так, что третий транзистор P3 проводит и таким образом подтягивает выходной вывод OUT до потенциала напряжения питания Vcc, приложенного на первом выводе 1, за счет чего первый транзистор P1 запирается и устройство за счет этого блокировано в этом состоянии. Это состояние представлено во временном интервале I фигуры 3. Если теперь, как показано во временном интервале II фигуры 3, состояние входного сигнала IN на управляющем входе 3 изменяется до низкого логического состояния Low, то есть принимает таким образом значение 0 В, то пятый транзистор P5 проводит, за счет чего точка соединения K1 подтягивается до потенциала напряжения питания Vcc и за счет этого третий транзистор P3 запирается. Теперь вследствие проводящего четвертого транзистора P4 выходной вывод OUT подтягивается до приложенного на втором выводе 2 высокого отрицательного потенциала -Vpp, за счет чего первый транзистор P1 также проводит и за счет этого устройство снова блокируется в этом состоянии.

Если также приложенное на первом выводе 1 высокое положительное напряжение Vpp должно иметь возможность проключаться к выходному выводу OUT, то описанная до сих пор схема должна быть дополнена в соответствии с устройством согласно фигуры 1. Для этого параллельно к нагрузочному участку третьего транзистора P3 включен нагрузочный участок шестого транзистора P6. Между первым выводом 1 и выводом затвора шестого транзистора P6 включен нагрузочный участок седьмого транзистора P7, вывод затвора которого соединен с выходным выводом OUT. Вывод затвора шестого транзистора P6 через нагрузочный участок первого n-канального транзистора N1 соединен с управляющим входом 6 для инвертированного входного сигнала  причем вывод затвора первого n-канального транзистора N1 соединен с управляющим входом 4 для входного сигнала IN. Вывод затвора первого n-канального транзистора N1 мог бы, конечно, точно также быть соединен с управляющим входом 3. Так как первый n-канальный транзистор N1 ни на одном из своих выводов не может придти в контакт с высоким отрицательным потенциалом -Vpp, является также ненужным выполнять его в глубокой ванне. Чтобы проключать к выходному выводу OUT высокое положительное напряжение Vpp, его прикладывают на первом выводе 1 вместо напряжения питания Vcc. Второй вывод 2 удерживается в подвешенном состоянии, что может происходить или путем отключения источника для высокого отрицательного потенциала -Vpp или за счет того, что выход этого источника принимает высокоомное состояние.

причем вывод затвора первого n-канального транзистора N1 соединен с управляющим входом 4 для входного сигнала IN. Вывод затвора первого n-канального транзистора N1 мог бы, конечно, точно также быть соединен с управляющим входом 3. Так как первый n-канальный транзистор N1 ни на одном из своих выводов не может придти в контакт с высоким отрицательным потенциалом -Vpp, является также ненужным выполнять его в глубокой ванне. Чтобы проключать к выходному выводу OUT высокое положительное напряжение Vpp, его прикладывают на первом выводе 1 вместо напряжения питания Vcc. Второй вывод 2 удерживается в подвешенном состоянии, что может происходить или путем отключения источника для высокого отрицательного потенциала -Vpp или за счет того, что выход этого источника принимает высокоомное состояние.

Пока входной сигнал IN и дальше принимает низкое логическое состояние Low, выходной вывод OUT остается соединенным через четвертый транзистор P4 со вторым выводом 2 и таким образом также находится в подвешенном состоянии. Это представлено во временном интервале III на фигуре 3. Если, однако, входной сигнал IN принимает высокое логическое состояние High, то пятый транзистор P5 снова запирается, в то время как первый n-канальный транзистор N1 проключается и тем самым на затворе шестого транзистора P6 прикладывается низкое логическое состояние Low, в результате чего он становится проводящим и подтягивает выходной вывод OUT до высокого положительного потенциала Vpp, приложенного на первом выводе 1. За счет этого седьмой транзистор P7 надежно запирается, так что шестой транзистор P6 остается в проводящем состоянии. Этот случай представлен во временном интервале IV фигуры 3.

При применении представленного на фигуре 1 устройства согласно изобретению во флеш-накопителе каждой линии слов придают в соответствие такое устройство и через выбор состояния входного сигнала IN приложенное на первом выводе 1 высокое положительное напряжение Vpp или приложенное на втором выводе 2 высокое отрицательное напряжение -Vpp может прикладываться к выходному выводу OUT устройства и таким образом необходимое стирающее или соответственно программирующее напряжение прикладывается к соответствующей линии слов флеш-накопителя.

Фигура 2 показывает другое соответствующее изобретению устройство, в котором к выходному выводу OUT этого устройства может включаться или высокое положительное напряжение Vpp или высокое отрицательное напряжение -Vpp. Какое из этих напряжений проключается, зависит опять-таки от того, какое состояние принимает входной сигнал IN на управляющих входах 3 - 6 для этого входного сигнала IN или соответственно инвертированный входной сигнал  а также от состояния управляющего сигнала MODE, приложенного к другому входному выводу 7. Также и в этом варианте все транзисторы, которые могут придти в контакт с высоким отрицательным напряжением -Vpp, являются транзисторами того же типа проводимости, что и подложка, в примере на фигуре 2, где предположена p-подложка, показанные там транзисторы являются таким образом p-канальными транзисторами. Между выходным выводом OUT и вторым выводом 2 для высокого отрицательного потенциала -Vpp включен нагрузочный участок первого транзистора P10. Между выводом затвора этого первого транзистора P10 и вторым выводом 2 включен нагрузочный участок второго транзистора P20 и параллельно к нему нагрузочный участок третьего транзистора P30. Вывод затвора этого третьего транзистора P30 соединен с его выводом истока, так что этот транзистор включен в качестве диода. Если теперь на выводе затвора второго транзистора P20 приложено высокое отрицательное напряжение, то этот второй транзистор P20 проключается, за счет этого вывод затвора первого транзистора P10 подтягивается до приложенного на втором выводе 2, высокого отрицательного потенциала -Vpp. За счет этого, с одной стороны, первый транзистор P10 проключается, вследствие чего высокий отрицательный потенциал -Vpp проключается к выходному выводу OUT, и, с другой стороны, включенный в качестве диода третий транзистор P30 начинает проводить, в результате чего вывод затвора первого транзистора P10 удерживается на высоком отрицательном потенциале -Vpp. За счет этого является возможным нагружать вывод затвора второго транзистора P20 только импульсным отрицательным напряжением. Оно производится из высокого положительного импульса напряжения порядка 18 В посредством схемы инвертирования напряжения INV. Эта схема инвертирования напряжения INV образована обычным образом из конденсатора С, который включен последовательно с пятым транзистором P30, включенным в качестве диода в прямом направлении, и шестым транзистором P60, включенным в качестве диода в направлении запирания, который соединен с точкой соединения конденсатора С и пятого транзистора P50. Не соединенный с транзисторами P50, P60 вывод конденсатора С образует входной вывод, а анод включенного в направлении запирания диода P60 - выходной вывод схемы инвертирования напряжения INV.

а также от состояния управляющего сигнала MODE, приложенного к другому входному выводу 7. Также и в этом варианте все транзисторы, которые могут придти в контакт с высоким отрицательным напряжением -Vpp, являются транзисторами того же типа проводимости, что и подложка, в примере на фигуре 2, где предположена p-подложка, показанные там транзисторы являются таким образом p-канальными транзисторами. Между выходным выводом OUT и вторым выводом 2 для высокого отрицательного потенциала -Vpp включен нагрузочный участок первого транзистора P10. Между выводом затвора этого первого транзистора P10 и вторым выводом 2 включен нагрузочный участок второго транзистора P20 и параллельно к нему нагрузочный участок третьего транзистора P30. Вывод затвора этого третьего транзистора P30 соединен с его выводом истока, так что этот транзистор включен в качестве диода. Если теперь на выводе затвора второго транзистора P20 приложено высокое отрицательное напряжение, то этот второй транзистор P20 проключается, за счет этого вывод затвора первого транзистора P10 подтягивается до приложенного на втором выводе 2, высокого отрицательного потенциала -Vpp. За счет этого, с одной стороны, первый транзистор P10 проключается, вследствие чего высокий отрицательный потенциал -Vpp проключается к выходному выводу OUT, и, с другой стороны, включенный в качестве диода третий транзистор P30 начинает проводить, в результате чего вывод затвора первого транзистора P10 удерживается на высоком отрицательном потенциале -Vpp. За счет этого является возможным нагружать вывод затвора второго транзистора P20 только импульсным отрицательным напряжением. Оно производится из высокого положительного импульса напряжения порядка 18 В посредством схемы инвертирования напряжения INV. Эта схема инвертирования напряжения INV образована обычным образом из конденсатора С, который включен последовательно с пятым транзистором P30, включенным в качестве диода в прямом направлении, и шестым транзистором P60, включенным в качестве диода в направлении запирания, который соединен с точкой соединения конденсатора С и пятого транзистора P50. Не соединенный с транзисторами P50, P60 вывод конденсатора С образует входной вывод, а анод включенного в направлении запирания диода P60 - выходной вывод схемы инвертирования напряжения INV.

Если, например, во флеш-накопителе одна из многих линий слов должна быть нагружена отрицательным программирующим напряжением, то каждая из линий слов может быть соединена с выходным выводом такого соответствующего изобретению устройства. Чтобы выбрать одно из устройств, можно прикладывать к подлежащему выбору устройству или положительный (например, 18 В) импульс напряжения, или соединять вывод затвора второго транзистора P20 через нагрузочный участок четвертого транзистора P40 с управляющим выводом 40, который нагружен инвертированным входным сигналом  Вывод затвора этого четвертого транзистора P40 соединен при этом с входным выводом 30, который нагружен неинвертированным входным сигналом IN. Если входной сигнал принимает состояние высокого уровня High, то четвертый транзистор P40 запирается так, что отрицательный импульс напряжения проключается с выхода схемы инвертирования напряжения INV к выводу затвора второго транзистора P20. Однако если входной сигнал принимает состояние низкого логического уровня Low, то четвертый транзистор P40 проводит, так что отрицательный импульс напряжения отводится с выхода схемы инвертирования напряжения INV к входному выводу 40 через четвертый транзистор P40. Путем выбора состояния входного сигнала IN на приданных в соответствие различным линиям слов флеш-накопителя устройствах могут быть выбраны соответствующие устройства и таким образом линии слов.

Вывод затвора этого четвертого транзистора P40 соединен при этом с входным выводом 30, который нагружен неинвертированным входным сигналом IN. Если входной сигнал принимает состояние высокого уровня High, то четвертый транзистор P40 запирается так, что отрицательный импульс напряжения проключается с выхода схемы инвертирования напряжения INV к выводу затвора второго транзистора P20. Однако если входной сигнал принимает состояние низкого логического уровня Low, то четвертый транзистор P40 проводит, так что отрицательный импульс напряжения отводится с выхода схемы инвертирования напряжения INV к входному выводу 40 через четвертый транзистор P40. Путем выбора состояния входного сигнала IN на приданных в соответствие различным линиям слов флеш-накопителя устройствах могут быть выбраны соответствующие устройства и таким образом линии слов.

На фигуре 2 показано, кроме того, устройство 100 для включения высокого положительного напряжения Vpp к выходному выводу OUT, которое, например, известно из публикации Proceedings ISSCC 1991, стр. 260. Выход этой схемы соединен через седьмой транзистор P70 с выходным выводом OUT, причем вывод затвора этого седьмого транзистора P70 соединен с входным выводом 70 для управляющего сигнала MODE. Если на выходном выводе OUT должно включаться высокое отрицательное напряжение -Vpp, то на входном выводе 70 управляющий сигнал MODE должен принимать высокое логическое состояние High, так что седьмой транзистор P70 запирается и тем самым высокое отрицательное напряжение -Vpp от устройства 100 для включения высоких положительных напряжений изолировано, так как оно содержит также n-канальные транзисторы, которые не должны выполняться в глубоких изолирующих ваннах.

В устройстве для включения высоких положительных напряжений между первым выводом 1 для положительных напряжений и выводом корпуса включена последовательная схема из восьмого транзистора P80 и первого n-канального транзистора N10. Выводы затворов этих обоих транзисторов соединены друг с другом и через нагрузочный участок второго n-канального транзистора N20 с управляющим выводом 50, к которому может прикладываться входной сигнал IN. Вывод затвора этого второго n-канального транзистора N20 соединен с входным выводом 60, к которому может прикладываться инвертированный входной сигнал  Точка соединения восьмого транзистора P80 и первого n-канального транзистора N10 образует выходной вывод этого устройства 100 для включения высоких положительных напряжений и соединена с выводом затвора девятого транзистора P90, нагрузочный участок которого расположен между первым выводом 1 и точкой соединения выводов затвора восьмого транзистора P80 и первого n-канального транзистора N10.

Точка соединения восьмого транзистора P80 и первого n-канального транзистора N10 образует выходной вывод этого устройства 100 для включения высоких положительных напряжений и соединена с выводом затвора девятого транзистора P90, нагрузочный участок которого расположен между первым выводом 1 и точкой соединения выводов затвора восьмого транзистора P80 и первого n-канального транзистора N10.

Для включения высокого отрицательного напряжения (-Vpp), например, в качестве программирующего напряжения на линии слов флеш-накопителя (Flash) указаны два варианта устройств, которые выполнены только на транзисторах того же типа проводимости, что и подложка. Технический результат: за счет этого можно отказаться от глубоких изолированных ванн, которые требуют специальной технологии. 2 с. и 4 з.п. ф-лы, 3 ил.

| Пломбировочный материал | 1973 |

|

SU456623A1 |

| US 5371705 A, 06.12.94 | |||

| 0 |

|

SU352379A1 | |

| US 5335200 A, 02.08.94 | |||

| US 5077691 A, 31.12.91 | |||

| ТРИГГЕР НА МДП-ТРАНЗИСТОРАХ | 0 |

|

SU352376A1 |

| GB 2060300 A, 29.04.81 | |||

| Способ модификации синтетических уретановых каучуков путем введения в них полимеров физических методов | 1972 |

|

SU437402A1 |

Авторы

Даты

1999-09-10—Публикация

1995-12-29—Подача