Изобретение относится к контрольно-измерительной технике и автоматике и может быть использовано для контроля параметров, которые могут взаимно компенсировать друг друга.

Известно устройство для контроля параметров, содержащее нормализатор, дискриминатор уровней, с первого по третий элементы ИЛИ, генератор импульсов, с первого по третий элементы И, триггер, первый и второй счетчики, блок сравнения (авторское свидетельство СССР N 1030808, кл. G 06 F 15/46, 1983). Недостаток этого устройства: невозможность одновременного контроля двух параметров.

Наиболее близким аналогом (прототипом) является устройство для контроля параметров, содержащее датчик первого параметра, задатчик верхней уставки первого параметра, задатчик нижней уставки первого параметра, датчик второго параметра, задатчик верхней уставки второго параметра, задатчик нижней уставки второго параметра, с первого по четвертый компараторы, первый и второй элементы 2И-ИЛИ, синхровход устройства, с первого по третий счетчики импульсов, элемент ИЛИ, с первого по четвертый входы задания устройства, с первого по третий мультиплексоры и выход устройства (а.с. СССР N 1620994).

Недостатком этого устройства является отсутствие возможности принятия решения при контроле двух взаимно компенсирующих параметров.

Техническим результатом заявленного изобретения является повышение достоверности контроля за счет учета взаимной компенсации двух параметров. Этот учет можно осуществить путем введения понятия обобщенного параметра, который является функцией первого параметра x(t) и второго параметра y(t)

Z(t) = ϕ[x(t), y(t)].

Необходимо определить прогнозируемое значение обобщенного параметра Z(tn) как функцию прогнозируемых значений первого x(tn) и второго y(tn) параметров. Момент прогноза tn можно определить по следующей формуле:

tn = t2+Δt,(1)

Δt = t2-t1,(2)

где Δt - глубина прогноза;

t1 - момент 1-го опроса контролируемых параметров;

t2 - момент 2-го опроса контролируемых параметров.

Прогнозируемое значение x(tn) первого параметра оценивается по следующей зависимости:

x(tn)=a0 + a1tn, (3)

где a0 и a1 - коэффициенты аппроксимации.

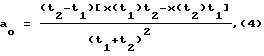

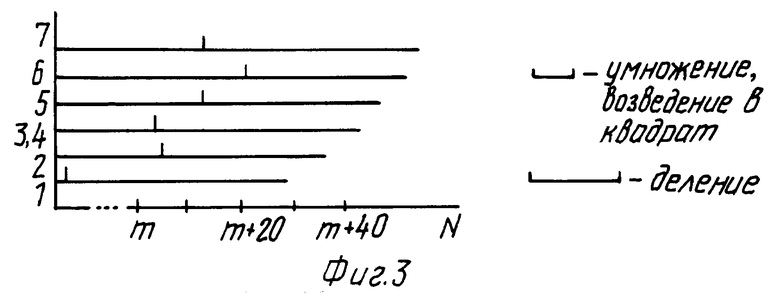

Используя метод наименьших квадратов, можно записать следующие формулы для определения этих коэффициентов:

где x(t1) и x(t2) - значения первого параметра в моменты соответственно 1-го и 2-го опросов.

Значение y(tn) определяется аналогично.

В заключение следует сравнить прогнозируемое значение обобщенного параметра Z(tn) с его нижней и верхней уставками и принять соответствующее решение.

Технический результат достигается тем, что устройство для контроля параметров, содержащее датчик первого параметра, датчик второго параметра, задатчики нижней и верхней уставок первого параметра, задатчики нижней и верхней уставок второго параметра, с первого по четвертый компараторы, с первого по третий счетчики импульсов, с первого по третий мультиплексоры, элементы ИЛИ, первый и второй элементы 2И-ИЛИ, первые входы первого и второго вентилей каждого из этих элементов соединены с выходами первого, второго, третьего и четвертого компараторов, вторые входы каждого из вентилей подключены к синхровходу устройства, а выходы первого и второго элементов 2И-ИЛИ соединены с синхровходами соответственно первого и второго счетчиков импульсов, выходы которых подключены к информационным входам соответственно первого и второго мультиплексоров, управляющие входы которых соединены соответственно с первым и вторым входами задания устройства, а выходы - с первым и вторым входами элемента ИЛИ, выход которого подключен к выходу устройства, выходы задатчиков нижней и верхней уставок первого параметра соединены с первыми входами соответственно первого и второго компараторов, выходы задатчиков нижней и верхней уставок второго параметра подключены к первым входам соответственно третьего и четвертого компараторов, синхровход третьего счетчика импульсов соединен с синхровходом устройства, а выход - с информационным входом третьего мультиплексора, первый и второй управляющий входы которого подключены к третьему и четвертому входам задания устройства, первый выход - к входу сброса первого счетчика импульсов, а второй выход - к входам сброса второго и третьего счетчиков импульсов, дополнительно содержит первый и второй блоки аппроксимации и прогноза, первый и второй адресные регистры, первый и второй дешифраторы, постоянное запоминающее устройство, первый и второй переключатели, задатчики нижней и верхней уставок обобщенного параметра, пятый и шестой компараторы, блок индикации и элемент И, выход которого подключен к входу блока индикации, а первый и второй входы - к выходам соответственно пятого и шестого компараторов, первые входы которых соединены с выходами задатчиков соответственно верхней и нижней уставок обобщенного параметра, а вторые входы - с выходом постоянного запоминающего устройства, управляющий вход которого подключен к пятому входу задания устройства, а первый вход через последовательно соединенные первый дешифратор первый адресный регистр и первый блок аппроксимации и прогноза - с первым выходом первого переключателя, второй выход которого подключен к вторым входам первого и второго компаратора, а вход - к выходу датчика первого параметра, второй вход постоянного запоминающего устройства соединен через последовательно соединенные второй дешифратор, второй адресный регистр и второй блок аппроксимации и прогноза с первым выходом второго переключателя, второй выход которого подключен к вторым входам третьего и четвертого компараторов, а вход - к выходу датчика второго параметра, кроме того, блок аппроксимации и прогноза содержит коммутатор, с первого по шестой элементы задержки, с первого по пятый блоки умножения, с первого по третий блоки вычитания, с первого по четвертый регистры, квадратор, с первого по третий сумматоры, первый и второй блоки деления, генератор тактовых импульсов и распределитель импульсов, с первого по седьмой выходы которого соединены соответственно с управляющим входом коммутатора, с входом записи первого регистра, с входами считывания второго и третьего регистров, с входами записи и считывания четвертого регистра и с входом считывания первого регистра, а тактовый вход распределителя импульсов подключен к выходу генератора тактовых импульсов, информационный вход коммутатора является входом блока аппроксимации и прогноза, первый выход соединен с первыми входами первого блока вычитания и первого блока умножения, а второй выход - с входом первого элемента задержки, выход которого подключен ко второму входу первого блока вычитания и к первому входу второго блока умножения, выход которого соединен с первым входом второго блока вычитания, второй вход которого подключен к выходу первого блока умножения, а выход - к первому входу третьего блока умножения, выход которого соединен с первым входом первого блока деления, выход второго регистра подключен ко второму входу первого блока умножения, к первому входу первого сумматора, а также через второй элемент задержки к первому входу третьего блока вычитания, второй вход которого соединен с выходом третьего элемента задержки, а выход - со вторым входом третьего блока умножения, с первым входом второго сумматора и с первым входом четвертого блока умножения, выход которого подключен к первому входу второго блока деления, а второй вход - к выходу первого регистра, информационный вход которого соединен с выходом первого блока вычитания, выход третьего регистра подключен к входам третьего и четвертого элементов задержки, к второму входу второго блока умножения и к второму входу первого сумматора, выход которого через квадратор соединен с информационным входом четвертого регистра, выход которого подключен ко вторым входам первого и второго блоков деления, второй вход второго сумматора соединен с выходом четвертого элемента задержки, а выход через пятый элемент задержки - с первым входом пятого блока умножения, второй вход которого подключен к выходу второго блока деления, а выход - к первому входу третьего сумматора, второй вход которого через шестой элемент задержки соединен с выходом первого блока деления, а выход является выходом блока аппроксимации и прогноза.

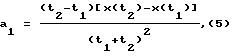

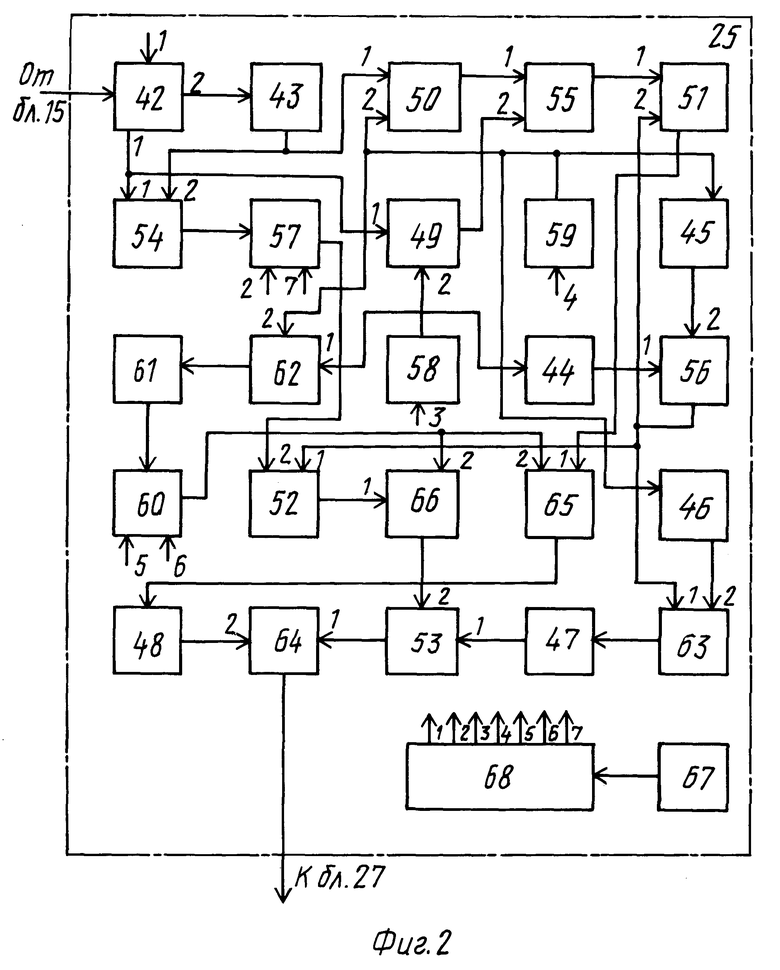

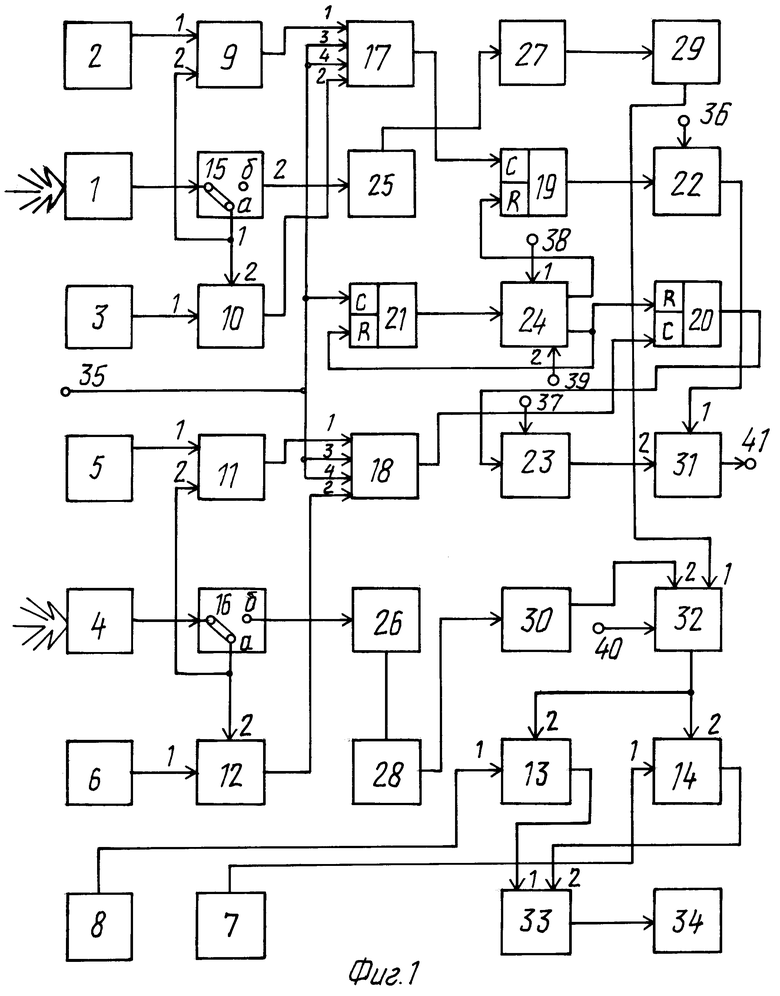

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 изображена блок-схема блока аппроксимации и прогноза (для ликвидации громоздкости связи между распределителем импульсов и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг. 3 представлена циклограмма работы блока аппроксимации и прогноза (по оси ординат обозначены номера выходов распределителя импульсов, а по оси абсцисс - число тактов, причем длительность операций сложения и вычитания принята за один такт, а длительность остальных вычислительных операций приведена справа).

Устройство для контроля параметров (фиг. 1) содержит датчик 1 первого параметра, задатчик 2 нижней уставки первого параметра, задатчик 3 верхней уставки первого параметра, датчик 4 второго параметра, задатчик 5 нижней уставки второго параметра, задатчик 6 верхней уставки второго параметра, задатчик 7 нижней уставки обобщенного параметра, задатчик 8 верхней уставки обобщенного параметра, первый 9, второй 10, третий 11, четвертый 12, пятый 13, шестой 14 компараторы, первый 15 и второй 16 переключатели, первый 17 и второй 18 элементы 2И-ИЛИ, первый 19, второй 20 и третий 21 счетчики импульсов, первый 22, второй 23 и третий 24 мультиплексоры, первый 25 и второй 26 блоки аппроксимации и прогноза, первый 27 и второй 28 адресные регистры, первый 29 и второй 30 дешифраторы, элемент ИЛИ 31, постоянное запоминающее устройство 32, элемент И 33, блок 34 индикации, синхровход 35 устройства, первый 36, второй 37, третий 38 и выход 41 устройства.

Первый 25 и второй 26 блоки аппроксимации и прогноза имеют одинаковую структуру. В качестве примера на фиг. 2 приведена блок-схема блока 25. Блок аппроксимации и прогноза содержит коммутатор 42, первый 43, второй 44, третий 45, четвертый 46, пятый 47 и шестой 48 элементы задержки, первый 49, второй 50, третий 51, четвертый 52 и пятый 53 блоки умножения, первый 54, второй 55 и третий 56 блоки вычитания, первый 57, второй 58, третий 59 и четвертый 60 регистры, квадратор 61, первый 62, второй 63 и третий 64 сумматоры, первый 65 и второй 66 блоки деления, генератор 67 тактовых импульсов и распределитель 68 импульсов. Учитывая, что значения t1 и t2 "зашиты" в первом 58 и втором 59 регистрах заранее, у этих регистров отсутствуют управляющий вход записи и информационный вход.

Устройство для контроля параметров работает следующим образом. Его работа осуществляется в двух режимах.

Режим 1. Он осуществляется, когда контролируемые параметры не являются взаимно компенсируемыми. В этом случае первый 15 и второй 16 переключатели (фиг. 1) устанавливаются в положение "а". На вход устройства поступают импульсы, подсчитываемые счетчиками 19, 20 и 21. При этом счетчик 21 определяет время контроля процесса в одном цикле, а счетчики 19 и 20 - время выхода соответствующего параметра за верхнюю и нижнюю заставку.

При выходе одного из параметров процесса за одну из уставок на соответствующий выход устройства выдается сигнал на изменение величины параметра в сторону оптимальной величины. На входы 36, 37, 38 задаются эталоны времени для каждого параметра процесса, по истечении которого работа объекта не гарантируется с заданной достоверностью. Каждый параметр оказывает свое воздействие на объект и регламентируется соответствующим отрезком времени. В соответствии с длительностью допустимого времени на коррекцию того или иного параметра (например, температуры и влажности, освещенности и вибрации и т.п. ) в устройстве используется необходимый канал контроля - коррекции с уменьшением временных интервалов допустимым образом. Если счетчики 19 и 20 не выдали в элемент ИЛИ 31 сигнал превышения времени нарушенного режима работы объекта, то через некоторое время они сбрасываются соответствующим сигналом мультиплексора 24.

Режим 2. Он осуществляется, когда контролируемые параметры являются взаимно компенсируемыми. В этом случае первый 15 и второй 16 переключатели (фиг. 1) устанавливаются в положение "б". Через эти переключатели значение параметров в момент t1 x(t1) и y(t1) поступают на входы соответственно первого и второго 26 блоков аппроксимации и прогноза. Порядок работы этих блоков рассмотрим на примере блока 25.

Сигнал, соответствующий значению x(t1), поступает на информационный вход коммутатора 42 (фиг. 2). На управляющий вход блока 42 подается сигнал с первого выхода распределителя 68 импульсов, что приводит к засылке величины x(t1) со второго выхода коммутатора 42 на вход первого элемента 43 задержки. Сигнал, соответствующий значению x(t2), в момент t2 с первого выхода коммутатора 42 (из-за отсутствия управляющего сигнала) поступает на первый вход первого блока 54 вычитания, на второй вход которого подается с выхода первого элемента 43 задержки величина x(t1). С выхода блока 54 сигнал, соответствующий величине [x(t2)-x(t1)], засылается на информационный вход первого регистра 57 и направляется со второго выхода распределителя 68 импульсов.

С третьего и четвертого выходов блока 68 подаются управляющие сигналы на входы считывания соответственно второго 58 и третьего 59 регистров. С выхода блока 58 сигнал, соответствующий величине t1, поступает на первый вход первого сумматора 62, на второй вход первого блока 49 умножения и на вход второго элемента 44 задержки, а с выхода блока 59 сигнал, соответствующий величине t2, засылается на вторые входы первого сумматора 62 и второго блока 50 умножения, а также на входы третьего 45 и четвертого 46 элементов задержки. С выхода блока 62 сигнал, соответствующий величине (t1+t2), направляется на вход квадратора 61, с выхода которого значение (t1+t2)2 подается на информационный вход четвертого регистра 60. Управляющий сигнал на вход записи блока 60 засылается с пятого выхода распределителя 68 импульсов.

С выходов первого 49 и второго 50 блоков умножения сигналы, соответствующие значениям x(t2)t1 и x(t1)t2, подаются на входы второго блока 55 вычитания, с выхода которого сигнал, соответствующий величине [x(t2)t1 - x(t1)t2] , поступает на первый вход третьего блока 51 умножения. С выходов второго 44 и третьего 45 элементов задержки значения t1 и t2 засылаются на входы третьего блока 56 вычитания, с выхода которого сигнал, соответствующий величине (t2 - t1), определяемой по формуле (2), подается на входы третьего 51 и четвертого 52 блоков умножения, а также на вход второго сумматора 63. По сигналу с седьмого выхода распределителя 68 импульсов на вход считывания первого регистра 57 с его выхода сигнал, соответствующий величине [x(t2) - x(t1)], направляется на второй вход четвертого блока 52 умножения. С выходов третьего 51 и четвертого 52 блоков умножения значения (t2 - t1) [x(t1)t2 - x(t2)t1] и (t2 - t1) [x(t2) - x(t1)] подаются на первые входы соответственно первого 65 и второго 66 блоков деления, на вторые входы которых по сигналу с шестого выхода распределителя 68 импульсов на вход считывания четвертого регистра 60 с его выхода засылается сигнал, соответствующий величине (t2 + t1)2.

С выходов блоков 65 и 66 значения коэффициентов аппроксимации a0 и a1, определенные по формулам (4) и (5), подаются соответственно на вход шестого элемента 48 задержки и на второй вход пятого блока 53 умножения. С выхода четвертого элемента 46 задержки сигнал, соответствующий величине t2, поступает на второй вход второго сумматора 63, с выхода которого значение момента прогноза tn через пятый элемент 47 задержки засылается на первый вход пятого блока 53 умножения. С выхода блока 53 сигнал, соответствующий величине a1tn, подается на первый вход третьего сумматора 64, на второй вход которого с выхода шестого элемента 48 задержки направляется значение a0. С выхода блока 64 сигнал, соответствующий прогнозируемому значению первого параметра x(tn), определяемому по формуле (3), засылается на выход первого блока 25 аппроксимации и прогноза. Аналогичным образом с помощью второго блока 26 аппроксимации и прогноза оценивается прогнозируемое значение второго параметра y(tn).

С выходов блоков 25 и 26 значения x(tn) и y(tn) поступают соответственно через последовательно соединенные первый адресный регистр 27 и первый дешифратор 29, а также второй адресный регистр 28 и второй дешифратор 30 на первый и второй входы постоянного запоминающего устройства 32. По сигналу с пятого входа 40 задания считывания устройства с выхода блока 32 прогнозируемое значение обобщенного параметра Z(tn) подается на вторые входы пятого 13 и шестого 14 компараторов, на первые входы которых с выходов блоков 8 и 7 засылаются сигналы, соответствующие величинам верхней и нижней уставок для обобщенного параметра.

Пятый компаратор 13 настроен следующим образом: если значение Z(tn) меньше или равно величине верхней уставке, то на выходе блока 13 появится 1. В противном случае на выходе этого блока будет 0. Шестой компаратор 14 настроен следующим образом: если значение Z(tn) больше или равно нижней уставке, то на выходе блока 14 появится 1. В противном случае на выходе этого блока будет 0. Таким образом, в случае благоприятного исхода сравнения на выходе элемента И33 появится 1 и на блоке 34 индикации появится транспарант "Норма". В противном случае на выходе блока 33 будет 0 и на блоке 34 индикации загорится транспарант "Нет нормы".

Таким образом, описанное устройство существенно повышает достоверность контроля за счет учета взаимной компенсации двух параметров. В данной ситуации может быть принято более обоснованное решение по результатам контроля.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в различных областях (отраслях) при контроле многопараметрических процессов.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ | 2004 |

|

RU2273559C1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| УСТРОЙСТВО ДЛЯ ТЕХНИКО-ЭКОНОМИЧЕСКОЙ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2011 |

|

RU2470365C1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2427900C1 |

Изобретение относится к контрольно-измерительной технике и автоматике и может быть использовано для контроля параметров, которые могут взаимно компенсировать друг друга. Техническим результатом является повышение достоверности контроля за счет учета взаимной компенсации двух параметров. Устройство содержит дополнительно введенные блоки и элементы, позволяющие оценить прогнозируемые значения обобщенного параметра и сравнить его с допустимыми верхней и нижней уставками. 1 з.п.ф-лы, 3 ил.

| Устройство для контроля параметра | 1988 |

|

SU1620994A1 |

| Устройство для контроля параметров | 1982 |

|

SU1030808A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ И КОНТРОЛЯ ПАРАМЕТРОВ | 1992 |

|

RU2029345C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2030781C1 |

| Устройство для контроля параметров | 1982 |

|

SU1091127A1 |

| Устройство для контроля параметров | 1986 |

|

SU1377829A1 |

| Ультразвуковое фокусирующее устройство | 1978 |

|

SU879447A1 |

| JP 6327810 A2, 15.11.1988 | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

Авторы

Даты

2000-12-20—Публикация

2000-05-10—Подача