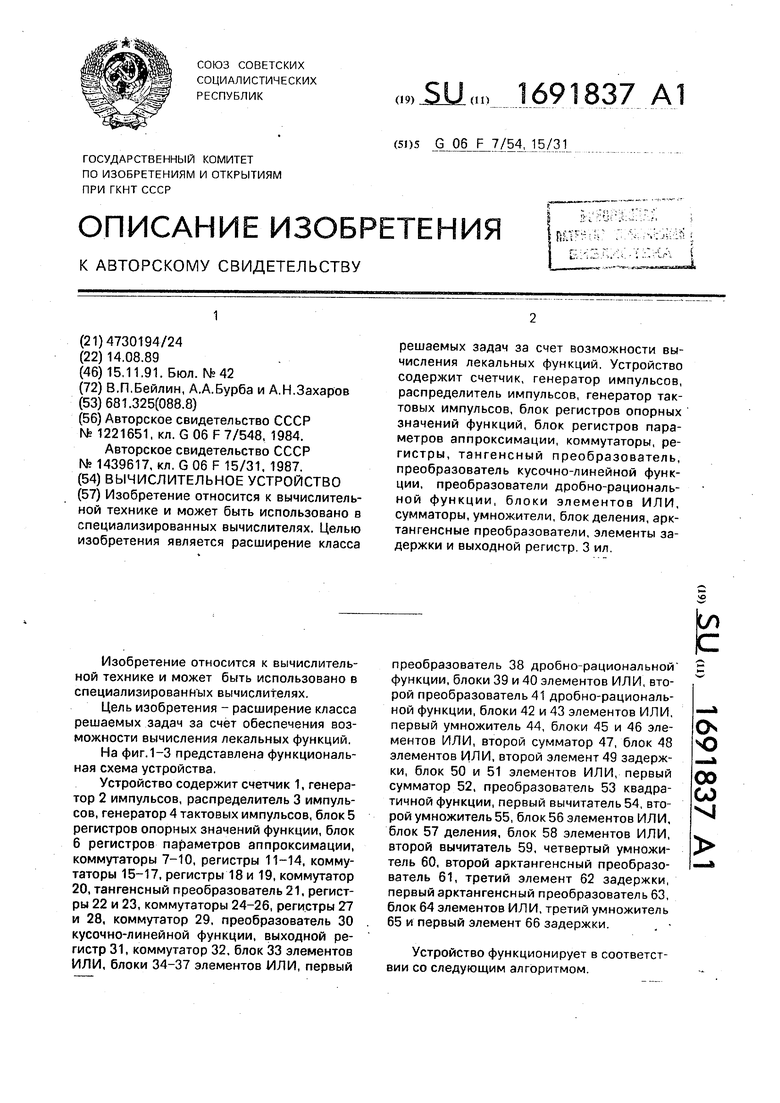

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности вычисления лекальных функций.

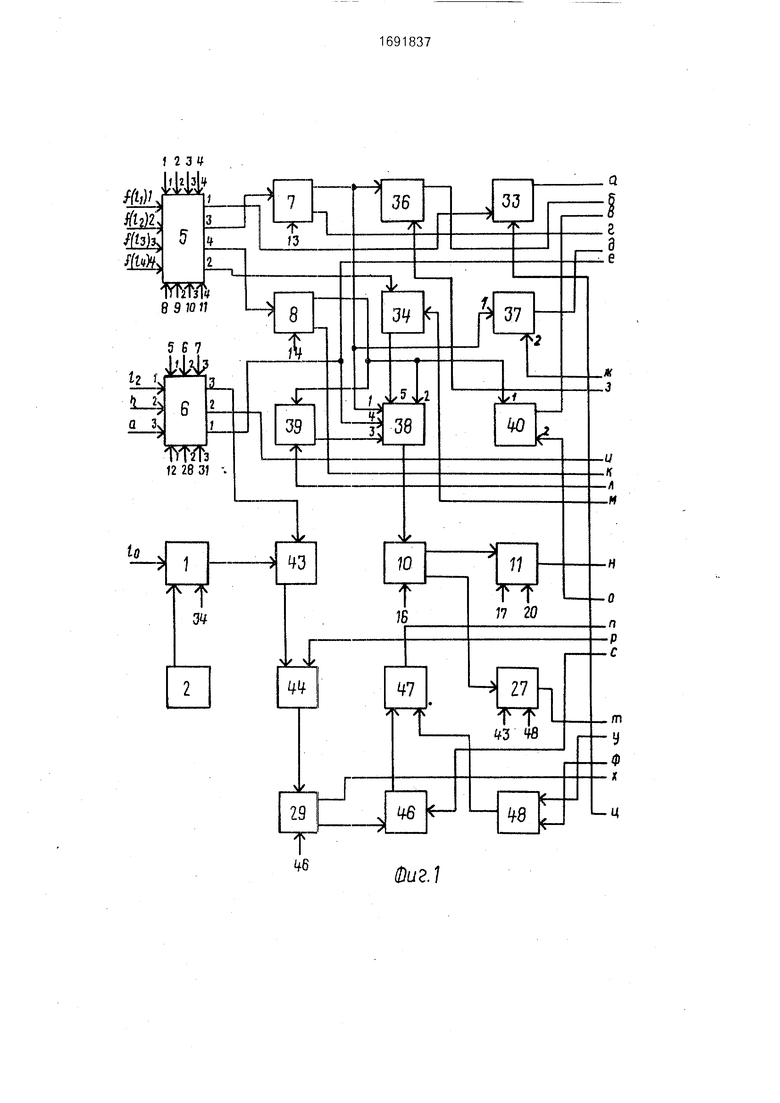

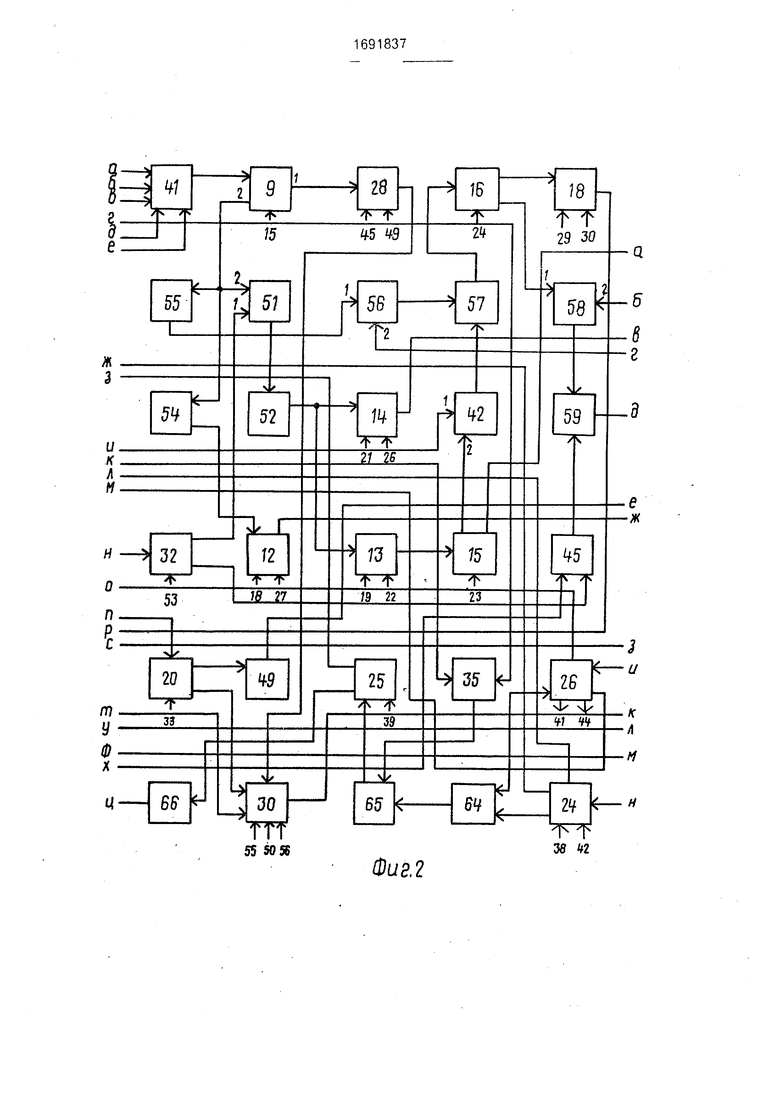

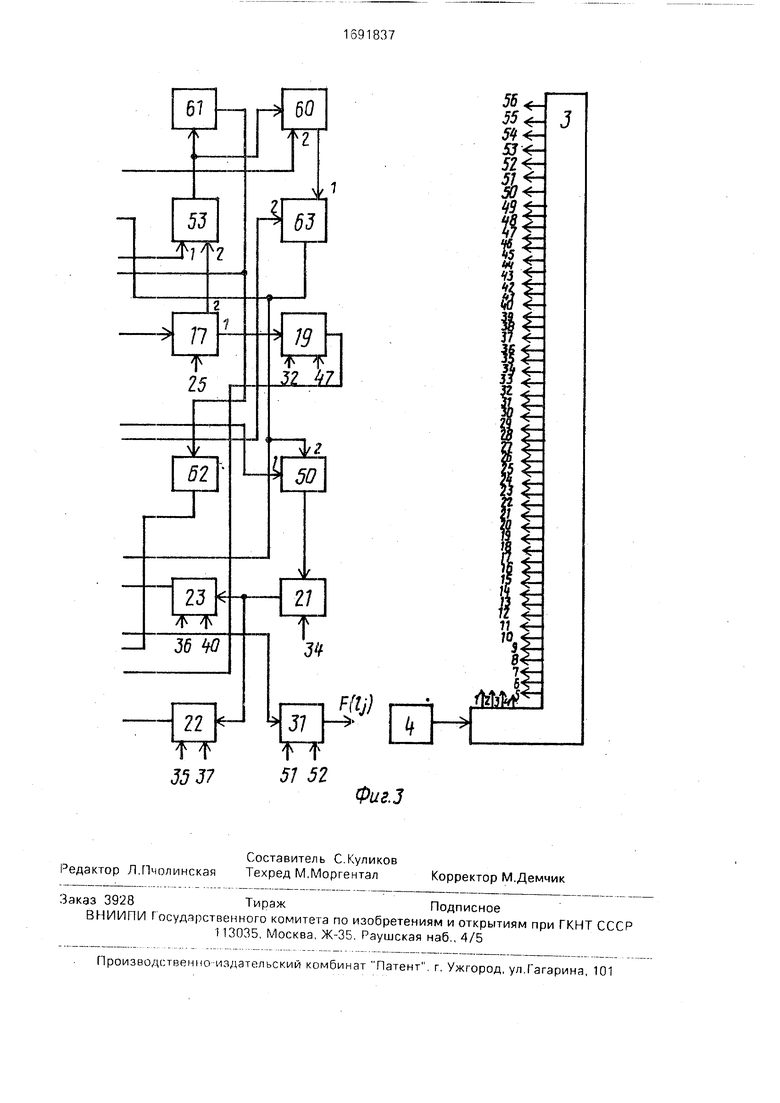

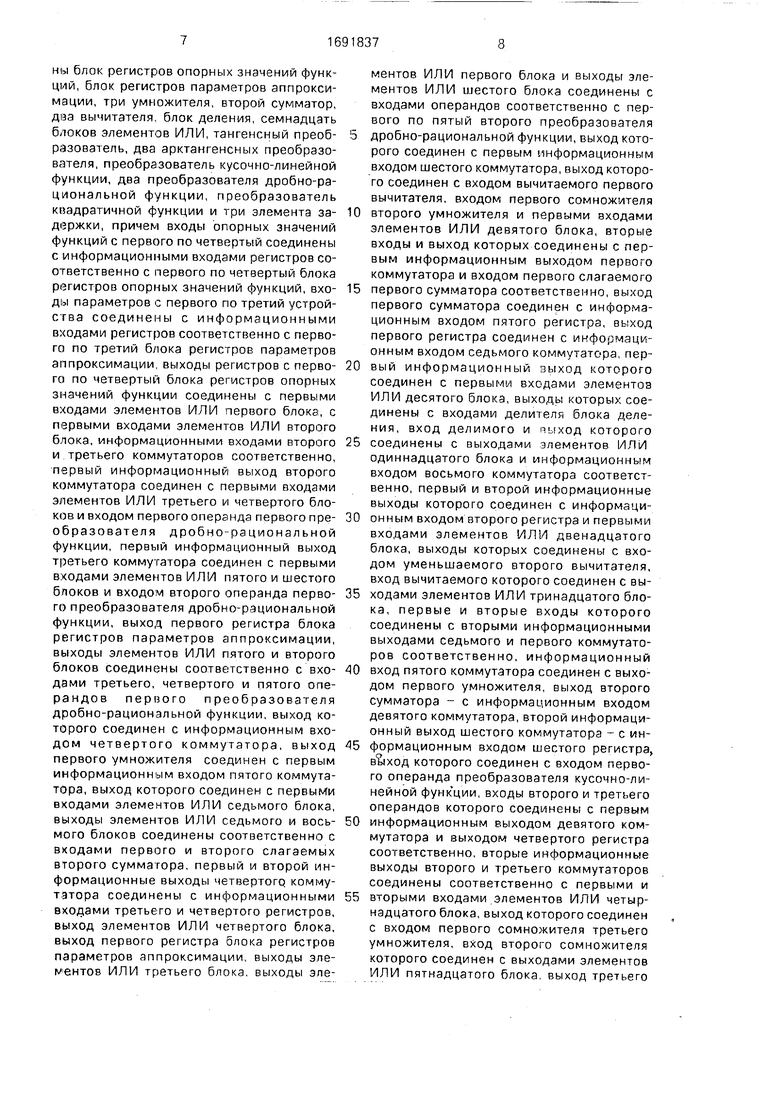

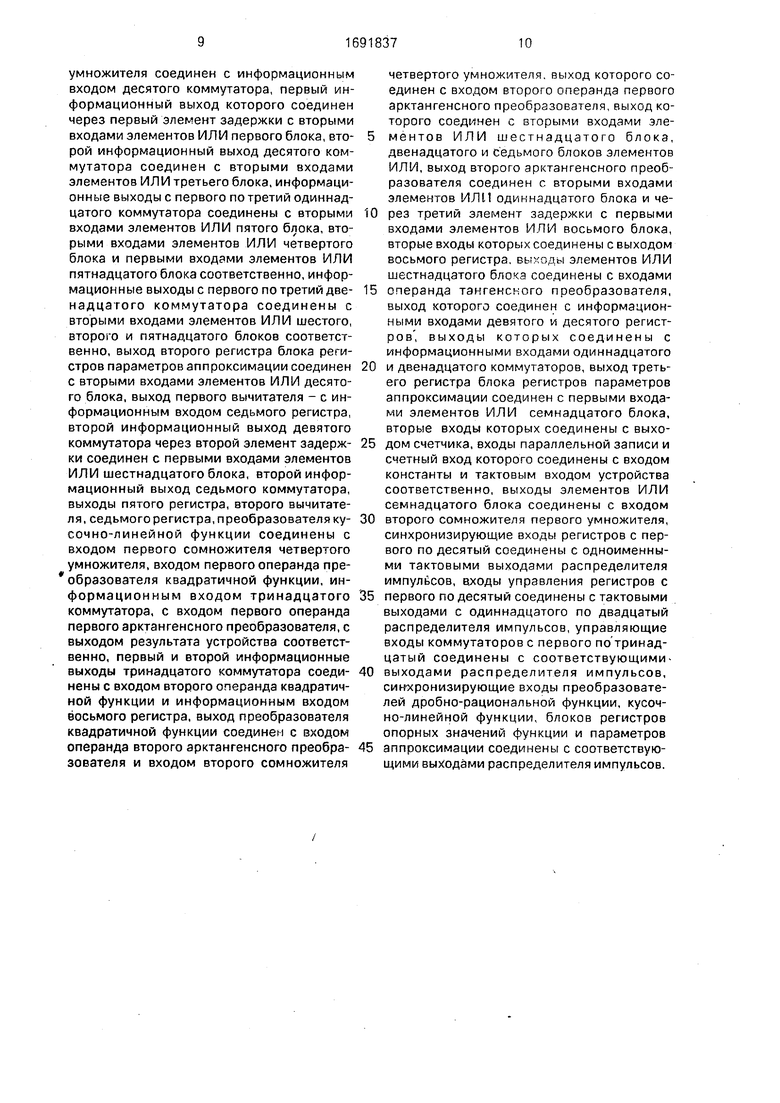

На фиг.1-3 представлена функциональная схема устройства.

Устройство содержит счетчик 1, генератор 2 импульсов, распределитель 3 импульсов, генератор 4 тактовых импульсов, блок 5 регистров опорных значений функции, блок 6 регистров параметров аппроксимации, коммутаторы 7-10, регистры 11-14, коммутаторы 15-17, регистры 18 и 19, коммутатор 20, тангенсный преобразователь 21, регистры 22 и 23, коммутаторы 24-26, регистры 27 и 28, коммутатор 29, преобразователь 30 кусочно-линейной функции, выходной регистр 31, коммутатор 32, блок 33 элементов ИЛИ, блоки 34-37 элементов ИЛИ, первый

преобразователь 38 дробно-рациональной функции, блоки 39 и 40 элементов ИЛИ, второй преобразователь 41 дробно-рациональной функции, блоки 42 и 43 элементов ИЛИ, первый умножитель 44, блоки 45 и 46 элементов ИЛИ, второй сумматор 47, блок 48 элементов ИЛИ, второй элемент 49 задержки, блок 50 и 51 элементов ИЛИ, первый сумматор 52, преобразователь 53 квадратичной функции, первый вычитатель 54, второй умножитель 55, блок 56 элементов ИЛИ, блок 57 деления, блок 58 элементов ИЛИ, второй вычитатель 59, четвертый умножитель 60, второй арктангенсный преобразователь 61, третий элемент 62 задержки, первый арктангенсный преобразователь 63, блок 64 элементов ИЛИ, третий умножитель 65 и первый элемент 66 задержки..

Устройство функционирует в соответствии со следующим алгоритмом.

Os sQ

00

СО XI

Линейная трансформация F(lj) лекальной функции производится в соответствии со следующим выражением:

F(lj) Z y(tj)-f Y,(1)

где р(tj) - лекальная функция, выраженная через тангенс аргумента;

Z, Y - коэффициенты трансформации лекала.

Аргументы tj лекальной функции выражаются через аргументы 1| аппроксимируемой функции следующим образом:

tj Klj + X,(2)

где К, X - коэффициенты трансформации лекала.

Если ИЦ - выбранные опорные точки функции f(l), определенной на интервале а, Ь, то наложение трансформированной лекальной функции на 4 выбранные точки функции f(l) выполняется, если справедливо равенство

f(li) --F(h), 1 1,2,3,4.(3)

Из системы уравнений (3) с учетом (2) можно получить в случае аппроксимации лекальной функции круговым тангенсом

К-,(4)

t2 arctg

Ч

1 - vi

(1 + vi)tg г X t2 - К12;

Y 1М JZM № v &)

fP(t3)-p(t2)

Z- f( 3)-f(l2) ф (t3) - Р (t2)

где t3 ts + r, (9)

(5) (6) (7)

(8)

arctg

k:14

1 + 15

V.

11 f(l3)-f(l2)

(10) (11)

va

l(L2j(12)

f(U)-f(l3)-( }

На информационные входы блока 5 регистров опорных значений функции поступает исходная информация в виде сигналов, соответствующих величинам f(h), fffe) f(la) и ). На информационные входы блока 6 регистров параметров аппроксимации поступает исходная информация в виде сигналов, соответствующих величинам 2. f и а (а - постоянная величина, равная -1).

Сигнал, соответствующий величине f(l2), поступает через коммутатор 7 на вход пер0

5

0

5

0

0

5

0

5

вого преобразователя 38 дробно-рациональной функции, а также через блоки 36 элементов ИЛИ и 37 на входы второго одноименного преобразователя 41. Сигнал, соответствующий величине f(h), поступает через блок 38 элементов ИЛИ на вход второго преобразователя 41 дробно-рациональной функции, Сигнал, соответствующий величине f(ls), поступает через коммутатор 8 и через блок элементов ИЛИ 39 на вход первого преобразователя 38 дробно-рациональной функции, а также через блок 40 элементов ИЛИ на вход второго преобразователя 41 дробно-рациональной функции, и непосредственно на вход первого преобразователя 38.

Сигнал, соответствующий величине f(U), поступает через блок 34 элементов ИЛИ на вход первого преобразователя 38 дробно- рациональной функции. Сигнал, соответствующий величине а (равный -1), поступает на входы первого и второго преобразователей 38 и 41 дробно-рациональной функции.

Преобразователь 38 оценивает величину V2 в соответствии с формулой (12). В данном случае: f f03), р fOz), с f(U), ip f02), а -1. Сигнал, соответствующий величине Vz поступает через коммутатор 10 на информационный вход регистра 11.

Преобразователь 41 оценивает величину vi в соответствии с формулой (11). В данном случае: f f02), р f(li), с 10з), V f(l), a -1. Сигнал, соответствующий величине vi , поступает через коммутаторЭ на входы второго умножителя 55 и первого вы- читателя 54, а также через блок 51 элементов ИЛИ на вход первого сумматора 52

С выхода сумматора 52 сигнал, соответствующий величине (1 + vi), подается на информационный вход регистра 13, а с выхода вычитателя 54 сигнал, соответствующий величине (1 - vi), подается на информационный вход регистра 12. С выхода умножителя 55 сигнал, соответствующий величине 3 fi , поступает через блок 56 элементов ИЛИ на вход делимого блока 57 деления.

Сразу после вычисления величины (1 + + vi) подается сигнал с выхода распределителя 3 импульсов на вход считывания первого регистра 11, с выхода которого сигнал, соответствующий величине V2 , посылается через коммутатор 32 и блок 51 элементов ИЛИ на вход первого сумматора 52, с выхода которого сигнал, соответствующий величине (1 + V2) подается на информационный вход регистра 14,

Сигнал, соответствующий величине (1 + + vi), с выхода регистра 13 через коммутатор

15и блок 42 элементов ИЛИ подается на вход делителя блока 57 деления. С выхода блока 57 сигнал, соответствующий величине 3 Vi/(1 + vi), посылается через коммутатор

16и блок 58 элементов ИЛИ на вход уменьшаемого вторичного вычитателя 59. На вход вычитаемого вычитателя 59 через блок элементов ИЛИ 45 и коммутатор 32 направляется сигнал, соответствующий величине

V2.

С выхода второго вычитателя 59 сигнал, соответствующий величине 3 vi/(1 + vi) -V2, через коммутатор 17 поступает на вход преобразователя 53 квадратичной функции, на другой вход которого с выхода регистра 14 подается сигнал, соответствующий величине (1 +V2). Преобразователь 53 осуществляет извлечение квадратного корня из отношения двух чисел, т.е. вычисление аргумента arctg.

С выхода преобразователя 53 квадратичной функции сигнал, соответствующий аргументу arctg в формуле (10) или величине tg т, поступает на вход второго арктангенс- ного преобразователя 61 и на вход четвертого умножителя 60. С выхода преобразователя 61 сигнал, соответствующий величине г, подается на вход третьего элемента 62 задержки, а также через блок

56элементов ИЛИ на вход делимого блока

57деления. На вход делителя блока 57 через блок 42 элементов ИЛИ с выхода блока б регистров второго блока параметров аппроксимации направляется сигнал, соответствующий величине rj. С выхода блока 57 деления сигнал, соответствующий величине К, подается через коммутатор 16 на информационный вход регистра 18.

На вход четвертого умножителя 60 подается сигнал, соответствующий величине (1 + Vi). С выхода умножителя 60 сигнал, соответствующий величине (1 + v tg т, подается на вход первого арктангенсного преобразователя 63. На второй вход преобразователя 63 подается сигнал с выхода регистра 12. Далее определяется величина V2 в соответствии с формулой (5), которая посылается на входы блоков 46, 50 и 58 элементов ИЛИ.

С выхода блока 46 элементов ИЛИ сигнал, соответствующий величине t2, подается на вход второго сумматора 47, на другой вход которого с выхода третьего элемента 62 задержки через блок 48 элементов ИЛИ посылается сигнал, соответствующий величине т, С выхода второго сумматора 47 сигнал, соответствующий величине 1з, вычисленной по формуле (9), подается на информационный вход коммутатора 20.

В дальнейшем осуществляется вычисление коэффициентов X. Y и Z трансформа- 5 ции лекал соответственно по формулам (6). (7) и (8).

Сигналы, соответствующие величинам X, Y и Z, посылаются на информационные входы соответственно регистров 19, 28 и 27.

0Далее вычисляется аргумент tj лекальной функции. С входа устройства на вход счетчика 1 поступает начальное значение 1о. За счет генератора 2 импульсов, сигналы с выхода которого подаются на счетный вход

5 счетчика 1, формируется аргумент Ij. Сигнал, соответствующий величине Ij, подается через блок 43 элементов ИЛИ на вход первого умножителя 44, на другой вход которого с выхода регистра 18 посылается сигнал, со0 ответствующий коэффициенту К. С выхода умножителя 44 сигнал, соответствующий величине Klj, подается через коммутатор 29 и блок 46 элементов ИЛИ на вход второго сумматора 47. На другой вход этого сумма5 тора с выхода регистра 19 через блок элементов ИЛИ 48 направляется сигнал, соответствующий величине X.

С выхода сумматора 47 сигнал, соответствующий величине tj, поступает через ком0 мутатор 20 на вход преобразователя 30 кусочно-линейной функции, на другие входы которого с регистров 27 и 28 поступают сигналы, соответствующие коэффициентам Z и Y. Преобразователь 30 вычисляет линей5 ную трансформацию F(lj) лекальной функции по формуле (1), которая направляется на выход устройства.

В дальнейшем работа устройства для вычисления по формуле (2) и (1) повторяется0 до тех пор, пока не исчерпаются аргументы Ij, т.е. формулы (2) и (1) отрабатываются в цикле.

Управляющие сигналы для работы устройства обеспечиваются распределителем

5 3 импульсов.

Формула изобретения Вычислительное устройство, содержащее тринадцать коммутаторов, десять реги- стров, первый умножитель, первый

0 сумматор, счетчик и распределитель импульсов, причем выход первого сумматора соединен с информационным входом первого регистра, выход второго регистра - с входом первого сомножителя первого умно5 жителя, выход третьего регистра - с первым информационным входом первого комму-.

татора, отличающееся тем, что. с целью расширения класса решаемых задач за счет возможности вычисления лекаль- ных функций, в него дополнительно введены блок регистров опорных значений функций, блок регистров параметров аппроксимации, три умножителя, второй сумматор, два вычитателя, блок деления, семнадцать блоков элементов ИЛИ, тангенсный преобразователь, два арктангенсных преобразователя, преобразователь кусочно-линейной функции, два преобразователя дробно-рациональной функции, преобразователь квадратичной функции и три элемента за- Д(ржки, причем входы опорных значений функций с первого по четвертый соединены с информационными входами регистров соответственно с первого по четвертый блока регистров опорных значений функций, входы параметров с первого по третий устрой- сгва соединены с информационными входами регистров соответственно с первого по третий блока регистров параметров аппроксимации, выходы регистров с первого по четвертый блока регистров опорных значений функции соединены с первыми входами элементов ИЛИ первого блока, с первыми входами элементов ИЛИ второго блока, информационными входами второго и третьего коммутаторов соответственно, первый информационный выход второго коммутатора соединен с первыми входами элементов ИЛИ третьего и четвертого блоков и входом первого операнда первого преобразователя дробно-рациональной функции, первый информационный выход третьего коммутатора соединен с первыми входами элементов ИЛИ пятого и шестого бпоков и входом второго операнда первого преобразователя дробно-рациональной функции, выход первого регистра блока регистров параметров аппроксимации, выходы элементов ИЛИ пятого и второго блоков соединены соответственно с входами третьего, четвертого и пятого операндов первого преобразователя дробно-рациональной функции, выход которого соединен с информационным входом четвертого коммутатора, выход первого умножителя соединен с первым информационным входом пятого коммутатора, выход которого соединен с первыми входами элементов ИЛИ седьмого блока, выходы элементов ИЛИ седьмого и восьмого блоков соединены соответственно с входами первого и второго слагаемых второго сумматора, первый и второй информационные выходы четвертого коммутатора соединены с информационными входами третьего и четвертого регистров, выход элементов ИЛИ четвертого блока, выход первого регистра блока регистров параметров аппроксимации, выходы элементов ИЛИ третьего блока, выходы элементов ИЛИ первого блока и выходы элементов ИЛИ шестого блока соединены с входами операндов соответственно с первого по пятый второго преобразователя дробно-рациональной функции, выход которого соединен с первым информационным входом шестого коммутатора, выход которого соединен с входом вычитаемого первого вычитателя, входом первого сомножителя 0 второго умножителя и первыми входами элементов ИЛИ девятого блока, вторые входы и выход которых соединены с первым информационным выходом первого коммутатора и входом первого слагаемого 5 первого сумматора соответственно, выход первого сумматора соединен с информационным входом пятого регистра, выход первого регистра соединен с информационным входом седьмого коммутатора, пер- 0 вый информационный 1зыход которого соединен с первыми входами элементов ИЛИ десятого блока, выходы которых соединены с входами делителя блока деления, вход делимого и которого 5 соединены с выходами элементов ИЛИ одиннадцатого блока и информационным входом восьмого коммутатора соответственно, первый и второй информационные выходы которого соединен с информаци- 0 онным входом второго регистра и первыми входами элементов ИЛИ двенадцатого блока, выходы которых соединены с входом уменьшаемого второго вычитателя, вход вычитаемого которого соединен с вы- 5 ходами элементов ИЛИ тринадцатого блока, первые и вторые входы которого соединены с вторыми информационными выходами седьмого и первого коммутаторов соответственно, информационный О вход пятого коммутатора соединен с выходом первого умножителя, выход второго сумматора - с информационным входом девятого коммутатора, второй информационный выход шестого коммутатора - с ин- 5 формационным входом шестого регистра, в ыход которого соединен с входом первого операнда преобразователя кусочно-линейной функции, входы второго и третьего операндов которого соединены с первым 0 информационным выходом девятого коммутатора и выходом четвертого регистра соответственно, вторые информационные выходы второго и третьего коммутаторов соединены соответственно с первыми и 5 вторыми входами элементов ИЛИ четырнадцатого блока, выход которого соединен с входом первого сомножителя третьего умножителя, вход второго сомножителя которого соединен с выходами элементов ИЛИ пятнадцатого блока, выход третьего

умножителя соединен с информационным входом десятого коммутатора, первый информационный выход которого соединен через первый элемент задержки с вторыми входами элементов ИЛИ первого блока, вто- 5 рой информационный выход десятого коммутатора соединен с вторыми входами элементов ИЛИ третьего блока, информационные выходы с первого по третий одиннадцатого коммутатора соединены с вторыми 10 входами элементов ИЛИ пятого блока, вторыми входами элементов ИЛИ четвертого блока и первыми входами элементов ИЛИ пятнадцатого блока соответственно, информационные выходы с первого по третий две- 15 надцагого коммутатора соединены с вторыми входами элементов ИЛИ шестого, второго и пятнадцатого блоков соответственно, выход второго регистра блока регистров параметров аппроксимации соединен 20 с вторыми входами элементов ИЛИ десятого блока, выход первого вычитателя - с информационным входом седьмого регистра, второй информационный выход девятого коммутатора через второй элемент задерж- 25 ки соединен с первыми входами элементов ИЛИ шестнадцатого блока, второй информационный выход седьмого коммутатора, выходы пятого регистра, второго вычитателя, седьмого регистра, преобразователя ку- 30 сочно-линейной функции соединены с входом первого сомножителя четвертого умножителя, входом первого операнда пре- образователя квадратичной функции, информационным входом тринадцатого 35 коммутатора, с входом первого операнда первого арктангенсного преобразователя, с выходом результата устройства соответственно, первый и второй информационные выходы тринадцатого коммутатора соеди- 40 йены с входом второго операнда квадратичной функции и информационным входом восьмого регистра, выход преобразователя квадратичной функции соединен с входом операнда второго арктангенсного преобра- 45 зователя и входом второго сомножителя

четвертого умножителя, выход которого соединен с входом второго операнда первого арктангенсного преобразователя, выход которого соединен с вторыми входами элементов ИЛИ шестнадцатого блока, двенадцатого и седьмого блоков элементов ИЛИ, выход второго арктангенсного преобразователя соединен с вторыми входами элементов ИЛИ одиннадцатого блока и через третий элемент задержки с первыми входами элементов ИЛИ восьмого блока, вторые входы которых соединены с выходом восьмого регистра, выходы элементов ИЛИ шестнадцатого блока соединены с входами операнда тангенсного преобразователя, выход которого соединен с информационными входами девятого и десятого регистров , выходы которых соединены с информационными входами одиннадцатого и двенадцатого коммутаторов, выход третьего регистра блока регистров параметров аппроксимации соединен с первыми входами элементов ИЛИ семнадцатого блока, вторые входы которых соединены с выходом счетчика, входы параллельной записи и счетный вход которого соединены с входом константы и тактовым входом устройства соответственно, выходы элементов ИЛИ семнадцатого блока соединены с входом второго сомножителя первого умножителя, синхронизирующие входы регистров с первого по десятый соединены с одноименными тактовыми выходами распределителя импульсов, входы управления регистров с первого по десятый соединены с тактовыми выходами с одиннадцатого по двадцатый распределителя импульсов, управляющие входы коммутаторов с первого по тринадцатый соединены с соответствующими- выходами распределителя импульсов, син-хронизирующие входы преобразователей дробно-рациональной функции, кусочно-линейной функции, блоков регистров опорных значений функции и параметров аппроксимации соединены с соответствующими выходами распределителя импульсов.

Ж

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления тригонометрического тангенса | 1986 |

|

SU1334144A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

| Устройство для вычисления эллиптических функций | 1987 |

|

SU1474641A2 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления лекальных функций. Устройство содержит счетчик, генератор импульсов, распределитель импульсов, генератор тактовых импульсов, блок регистров опорных значений функций, блок регистров параметров аппроксимации, коммутаторы, регистры, тангенсный преобразователь, преобразователь кусочно-линейной функции, преобразователи дробно-рациональной функции, блоки элементов ИЛИ, сумматоры, умножители, блок деления, арк- тангенсные преобразователи, элементы задержки и выходной регистр. 3 ил.

и к

А М

т У

Ф

Фиг. 2

Фиг.З

| Устройство для вычисления функции арктангенса | 1984 |

|

SU1221651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1991-11-15—Публикация

1989-08-14—Подача