Настоящее изобретение относится в основном к отображающему фоновое изображение устройству и к используемому им внешнему запоминающему устройству. Более конкретно, настоящее изобретение относится к отображающему фоновое изображение устройству, требующему отображения некоторого множества фоновых сцен, подобного телевизионному игровому набору, и используемому им внешнему запоминающему устройству.

Пример отображающего изображения устройства для отображения фонового изображения в комбинации с подвижным изображением описан в японском патенте N 7478/1990 (соответствующем патенту США N 4824106).

На известном уровне техники только один фоновый экран может быть отображен в одном кадре (сцене). Предполагается, что на известном уровне техники возможны изменения, благодаря которым можно отображать некоторое множество фоновых экранов в одной сцене путем увеличения объема памяти. Количество данных, которое микропроцессор (центральное процессорное устройство), применяемый для отображения изображения, может обработать за единицу времени, ограничено и адресное пространство микропроцессора также ограничено. Поэтому число фоновых экранов, образующих одну сцену, число ячеек, образующих один фоновый экран, число цветов, используемых в каждом из фоновых экранов, и т. д. естественным образом ограничено. Например, если число ячеек, образующих один фоновый экран, возрастет, то может увеличиться число цветов на точку, в то время как число фоновых экранов, которые можно отобразить в одной сцене, уменьшится. С другой стороны, если уменьшить число ячеек, можно увеличить число фоновых экранов, в то время как число цветов на точку уменьшится.

Основной целью настоящего изобретения является создание отображающего фоновое изображение устройства, способного отображать фоновое изображение, имеющее некоторое множество сцен, путем переключения множества фоновых экранов, и используемого им внешнего запоминающего устройства.

Другой целью настоящего изобретения является создание отображающего фоновое изображение устройства, способного отображать некоторое множество фоновых изображений при меньшем объеме памяти путем более эффективного использования памяти, и используемого им внешнего запоминающего устройства.

Отображающее фоновое изображение устройство, соответствующее настоящему изобретению, отображает на растровом развертывающем дисплее фоновое изображение, на котором N символов и M символов, каждый из которых состоит из заданного числа элементов изображения, расположены соответственно в горизонтальном направлении и вертикальном направлении, чтобы представлять один фоновый экран, а некоторое множество фоновых экранов образует одну сцену. Отображающее фоновое изображение устройство содержит средство генерации данных режима (постоянная память 38 во внешней памяти 36 и микропроцессор 12 в варианте осуществления) для генерирования режимных данных для указания числа фоновых экранов, образующих некоторую сцену, и числа ячеек, используемых в каждом фоновом экране, средство запоминающего устройства данных обозначения символов (постоянная память 38 и экранная память произвольного доступа 42 в варианте осуществления), имеющее область памяти, которая может запоминать данные обозначения символов для образования H • b символов для каждого из фоновых экранов, число которых может быть указано средством генерации данных режима, средство запоминающего устройства данных элементов изображения (постоянная память 38 и экранная память произвольного доступа 42 в варианте осуществления) для хранения данных элементов изображения для каждого из множества символов, каждый из которых содержит не менее двух ячеек на элемент изображения, и обозначенных данными обозначения символов, первое средство считывания (схема адресации экранов 16 в варианте осуществления) для считывания данных обозначения символов из средства запоминающего устройства данных обозначения символов синхронно с горизонтальной разверткой растрового развертывающего дисплея, второе средство считывания (схема адресации символов 18 в варианте осуществления) для считывания из средства запоминающего устройства данных элементов изображения (данных элементов изображения) каждого из символов, обозначенных данными обозначения символов, синхронно с горизонтальной разверткой растрового развертывающего дисплея и на основании данных обозначения символов, считанных из средства запоминающего устройства данных обозначения символов, средство параллельно-последовательного преобразования (схема параллельно-последовательного преобразования 26 в варианте осуществления) для промежуточного хранения данных элементов изображения, считанных из средства запоминающего устройства данных элементов изображения вторым средством считывания для каждого заданного числа битов параллельным способом, и выдачи их в виде битовой последовательности, средство вывода (комбинирующая данные элементов изображения схема 30 в варианте осуществления) для вывода данных элементов изображения для каждого фонового экрана, обозначенного режимными данными путем комбинирования данных элементов изображения, выводимых из средства параллельно-последовательного преобразования, и средство генерации видеосигнала (генерирующая цвет схема 34 в варианте осуществления) для генерирования видеосигнала на основе данных элементов изображения для каждого фонового экрана, выводимого из средства вывода.

Внешнее запоминающее устройство (внешняя память 36 в варианте осуществления), соответствующая настоящему изобретению, используется совместно с отображающим фоновое изображение устройством. Отображающее фоновые изображения устройство отображает на растровом развертывающем дисплее фоновое изображение, на котором N символов и M символов, каждый из которых содержит заданное число элементов изображения, подходящим образом расположены в горизонтальном направлении и вертикальном направлении, чтобы представлять один фоновый экран, а некоторое множество фоновых экранов образует одну сцену. Внешнее запоминающее устройство имеет средство запоминания программы (постоянная память 38 в варианте осуществления) для хранения программных данных, необходимых для отображения фонового изображения.

Запоминающее программные данные устройство имеет запоминающую режимные данные область (область 38c в постоянной памяти 38 в варианте осуществления) для хранения режимных данных для обозначения числа фоновых экранов, образующих сцену, и числа ячеек, используемых в каждом из фоновых экранов, запоминающую данные элементов изображения область (область 38a в постоянной памяти 38 в варианте осуществления) для хранения данных элементов изображения некоторого множества символов, каждый из которых содержит не менее двух ячеек на элемент изображения, запоминающую данные обозначения символов область (область 38b в постоянной памяти 38 в варианте осуществления), имеющее запоминающую область, которая может хранить данные обозначения символов для обозначения максимально H • M символов и их позиций на дисплее для каждого из фоновых экранов, число которых может быть обозначено режимными данными, и запоминающая данные передаточных программ область (область 38d в постоянной памяти ROM 38 в варианте осуществления) для запоминания программных данных для передачи названных выше режимных данных, названных выше данных элементов изображения и названных выше данных обозначения символов. Отображающее фоновые изображения устройство содержит записываемую-считываемую память (память произвольного доступа 40 в варианте осуществления) для передачи данных обозначения символов и данных элементов изображения на записываемую-считываемую память на базе данных передаточных программ, хранящихся в запоминающем устройстве передаточных программ средстве, считывающее режимные данные средство (режимный регистр 14 в варианте осуществления) для считывания режимных данных из запоминающей режимные данные области, первое средство считывания (схема адресации экранов 16 в варианте осуществления) для считывания обозначающих символы данных из записываемой-считываемой памяти синхронно с горизонтальной разверткой растрового развертывающего дисплея, второе средство считывания (схема адресации символов 18 в варианте осуществления) для считывания из записываемой-считываемой памяти данных элементов изображения каждого из символов, обозначаемых обозначающими символы данными синхронно с горизонтальной разверткой растрового развертывающего дисплея, средство параллельно-последовательного преобразования (схема 28 параллельно-последовательного преобразования в варианте осуществления) для промежуточного хранения данных элементов изображения, считанных вторым средством считывания, для каждого заданного числа параллельных битов и выдача их в виде последовательности битов, средство вывода (комбинирующая данные элементов изображения схема 30 в варианте осуществления) для вывода данных элементов изображения для каждого фонового экрана, обозначенного режимными данными из считывающего режимные данные устройства, путем комбинирования данных элементов изображения, выводимых из средства параллельно-последовательного преобразования, и средство генерирования видеосигнала (генерирующая цвет схема 34 в варианте осуществления) для генерирования видеосигнала на базе данных элементов изображения для каждого фонового экрана, выводимого из средства вывода.

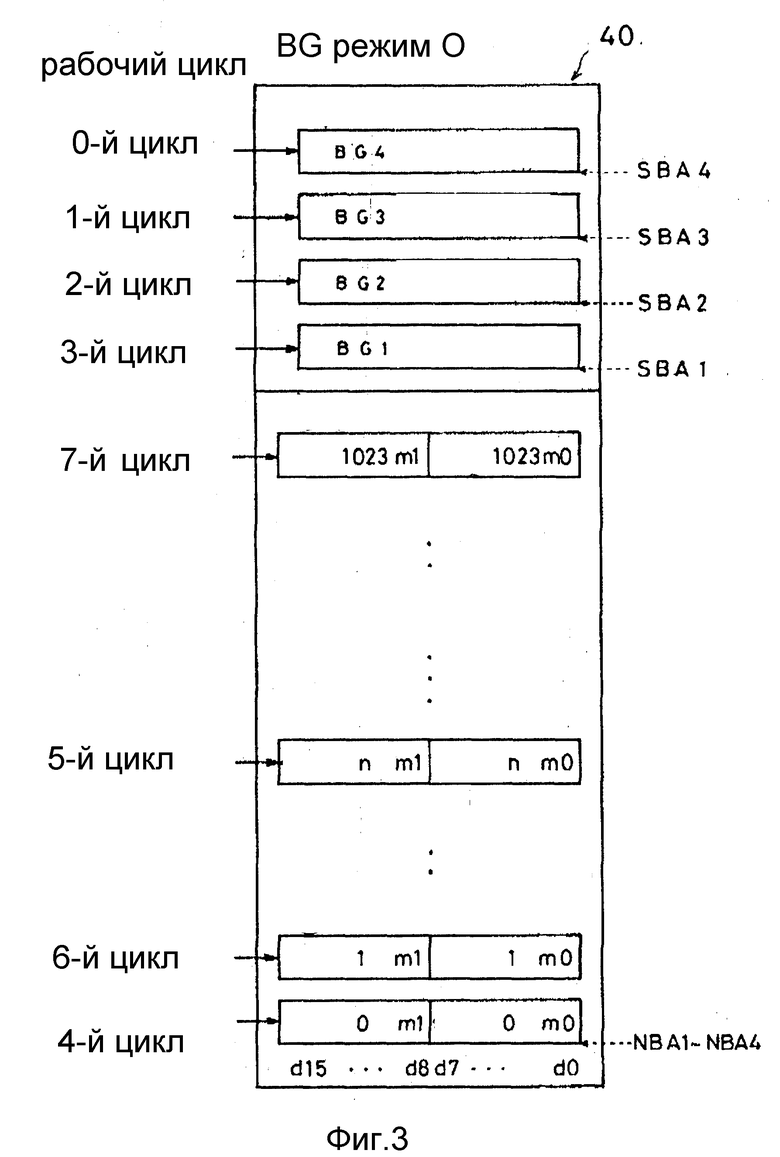

Когда внешняя память 36 соединена с отображающим фоновые изображения устройством 10, соответствующие данные обозначения символов, образующие фоновые экраны с BG1 по BG4 и данные элементов изображения множества символов, используемых в каждом из фоновых экранов с (BG1 по BG4), соответственно считываются из запоминающей данные обозначения символов области и запоминающей данные элементов изображения области на основе данных передаточных программ, хранящихся в средстве запоминания данных передаточных программ, подобном постоянной памяти 38, и записываются в записываемую-считываемую память. В то же самое время соответствующие данные записываются в записываемую-считываемую память, подобную памяти 40 произвольного доступа, другими словами, экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа с форматом, изображенным на фиг.3.

HV счетчик 22, используемый в варианте осуществления, дает показание Hc, соответствующее горизонтальной позиции электронного луча, и показание Vc, соответствующее его вертикальной позиции, синхронно с разверткой электронным лучом дисплея. Генерирующая тактовые сигналы схема 20 генерирует сигналы за восемь циклов, т.е. с нулевого по седьмой цикл, во время перемещения электронного луча по точкам дисплея, подавая тактовые сигналы с нулевого по третий цикл на первое средство считывания, т.е. на схему 16 адресации экранов, и тактовые сигналы с четвертого по седьмой цикл на второе средство считывания, т. е. на схему 18 адресации символов. Схема 16 адресации экранов генерирует адреса, имеющие базовые адреса экранов SBA4, SBA3, SBA2 и SBA1, соответствующие фоновым экранам BG4, BG3, BG2 и BG1, прибавляя к адресу, представляющему позицию на дисплее, соответствующую показаниям счетчика Hc и Vc в текущий момент, последовательно для каждого цикла в соответствующие такты нулевого цикла до третьего цикла, для указания (обозначения) адреса считывания экранной памяти 42 произвольного доступа. Аналогично, данные обозначения символов (см. фиг. 11) считываются из экранной памяти 42 произвольного доступа.

Символьные коды (с d0 по d9), входящие в состав данных обозначения символов, образующие каждый из фоновых экранов с BG1 по BG4, поступающие на схему 18 адресации символов в качестве данных, указывающих адрес в символьной памяти 44 произвольного доступа. Схема 18 адресации символов выдает адрес символа на основе обозначающих символ данных, образующих фоновые экраны с BG4 по BG1, последовательно считываемых с нулевой по третий цикл и синхронно с тактовыми сигналами с четвертого по седьмой цикл.

Аналогично, данные элементов изображения считываются из символьной памяти 44 произвольного доступа.

Данные элементов изображения, имеющие имена 0, n, 1 и 1023, считываемые по тактовым сигналам с четвертого по седьмой цикл, фиксируются в четырех фиксирующих схемах с 26a по 26d фиксирующей схемы 26 (см. фиг. 1) в указанном порядке параллельным образом. Данные, т.е. цветовые данные восьми элементов изображения в горизонтальном направлении одного символа, который соответствует определенной дисплейной позиции каждого из фоновых экранов с BG1 по BG4 (данные из двух битов для обозначения четырех цветов на элемент изображения), поступают параллельно на параллельно-последовательный преобразователь 28. Последовательно-параллельный преобразователь 28 считывает параллельные битовые данные и временно хранит их по сигналу "записать" W от генерирующей тактовые сигналы схемы 20. Последовательно-параллельный преобразователь 28 преобразует параллельные битовые данные в последовательные битовые данные синхронно с тактовым сигналом "считать", поступающим с временным интервалом, который в два раза длиннее временного интервала, в течение которого электронный луч проходит через один элемент изображения, и подает их на комбинирующую данные элементов изображения схему 30.

Комбинирующая данные элементов изображения схема 30 на основе режимных данных комбинирует пары последовательных данных a0 и a1, b0 и b1, c0 и c1, d0 и d1, e0 и e1, f0 и f1, исходящие из последовательно-параллельного преобразователя 28, для получения данных из битов, число которых соответствует числу ячеек. Поэтому цветовые данные для каждого фонового экрана (с BG4 по BG1) выводятся и поступают на генерирующую цвет схему 34. Генерирующая цвет схема 34 генерирует цветной видеосигнал (аналоговый сигнал), определяемый цветовыми данными и палитровыми данными, и передает его на дисплей.

Описанным выше образом режимные данные, предварительно заданные, позволяют произвольно определять число фоновых экранов в каждой сцене и комбинацию числа цветов, используемых в каждом из фоновых экранов.

В соответствии с настоящим изобретением генерируются режимные данные для обозначения числа фоновых экранов, образующих одну сцену и комбинации числа ячеек и числа цветов, используемых в каждом из фоновых экранов, и только необходимые данные считываются из средства запоминающего устройства данных обозначения символов и средства запоминающего устройства данных элементов изображения на основе режимных данных, что позволяет максимизировать способность микропроцессора отображать изображение в ограниченное время обработки.

Далее, если данные элементов изображения символов и данные обозначения символов, применяемые во всех сценах, хранятся в неразрушающемся запоминающем устройстве и только данные одной сцены (кадра) считываются за один раз и временно хранятся в произвольного доступа памяти или в чем-то подобном, то имеется возможность эффективно использовать память, подобную памяти произвольного доступа.

Названные и другие цели, признаки, аспекты и преимущества настоящего изобретения станут очевидны после ознакомления с нижеследующим подобным описанием настоящего изобретения, которое ведется со ссылками на приложенные чертежи.

Фиг. 1 является блок-схемой одного из вариантов осуществления настоящего изобретения.

Фиг. 2 иллюстрирует карту постоянной памяти, встроенной во внешнюю память.

Фиг. 3 иллюстрирует карту памяти произвольного доступа в BG режима 0.

Фиг. 4 иллюстрирует карту памяти произвольного доступа в BG режиме 1.

Фиг. 5 иллюстрирует карту памяти произвольного доступа в BG режиме 2.

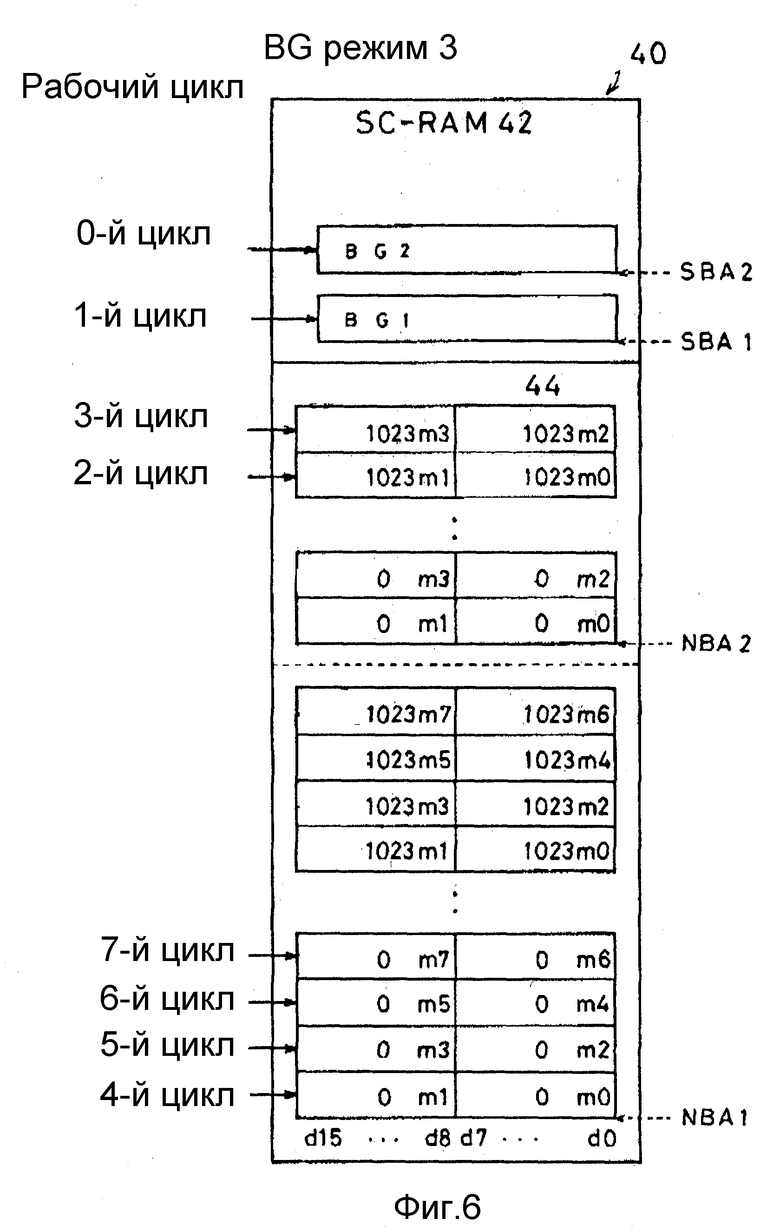

Фиг. 6 иллюстрирует карту памяти произвольного доступа в BG режиме 3.

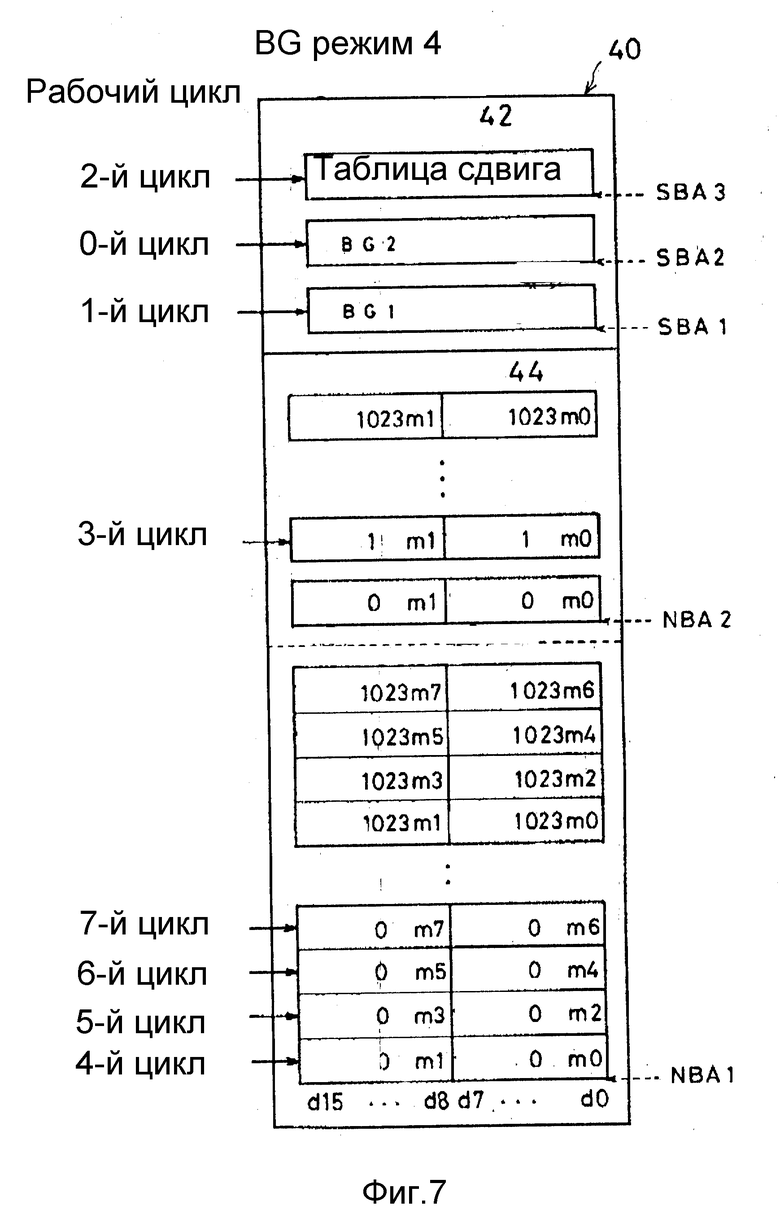

Фиг. 7 иллюстрирует карту памяти произвольного доступа в BG режиме 4.

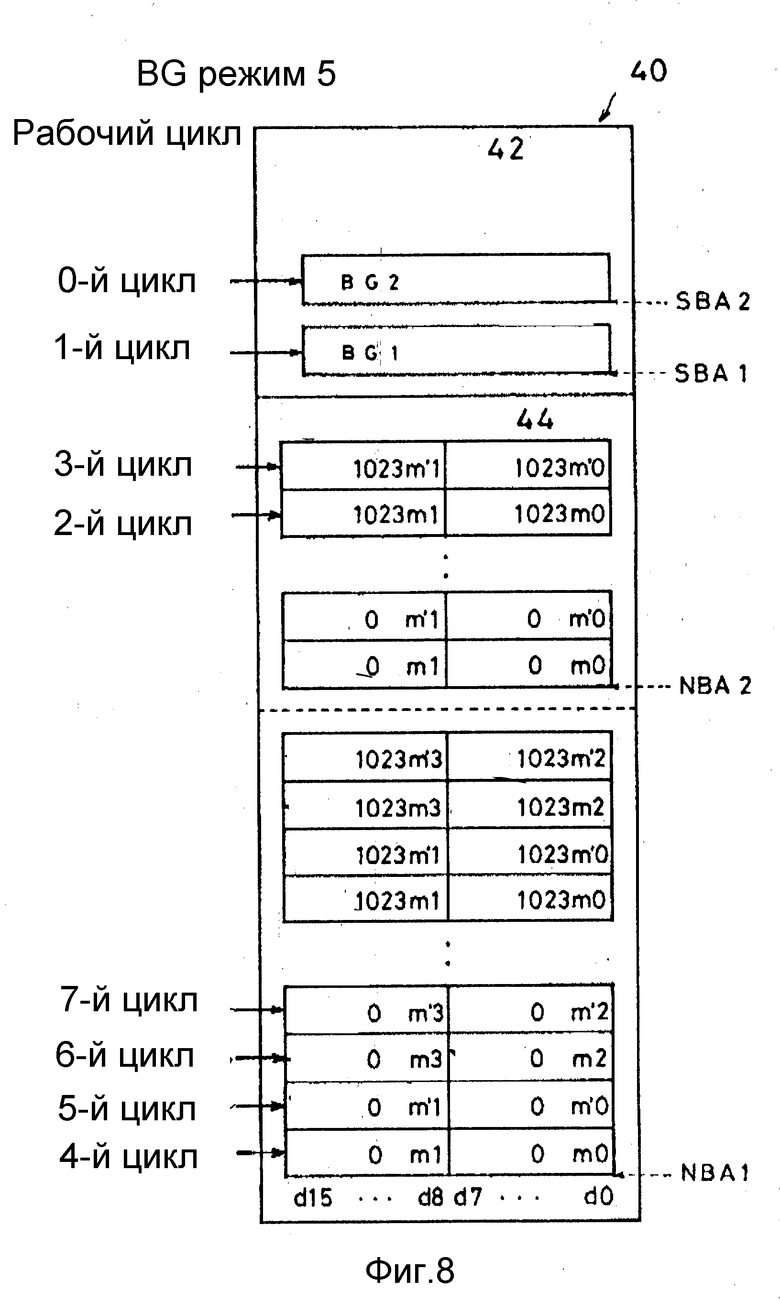

Фиг. 8 иллюстрирует карту памяти произвольного доступа в BG режиме 5.

Фиг. 9 иллюстрирует карту памяти произвольного доступа в BG режиме 6.

Фиг. 10 иллюстрирует состояние, когда запоминаются данные одного фонового экрана.

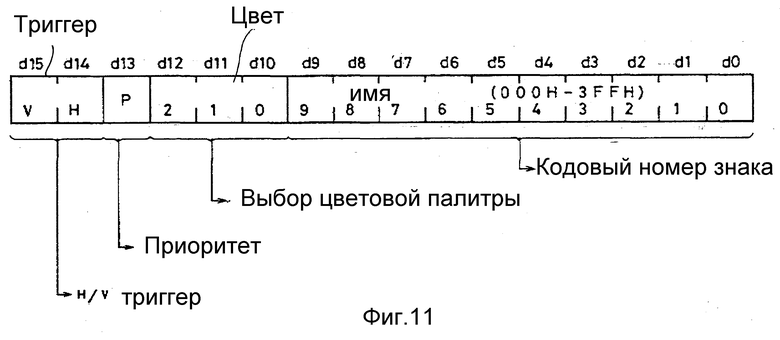

Фиг. 11 представляет формат данных одного символа экранной памяти произвольного доступа.

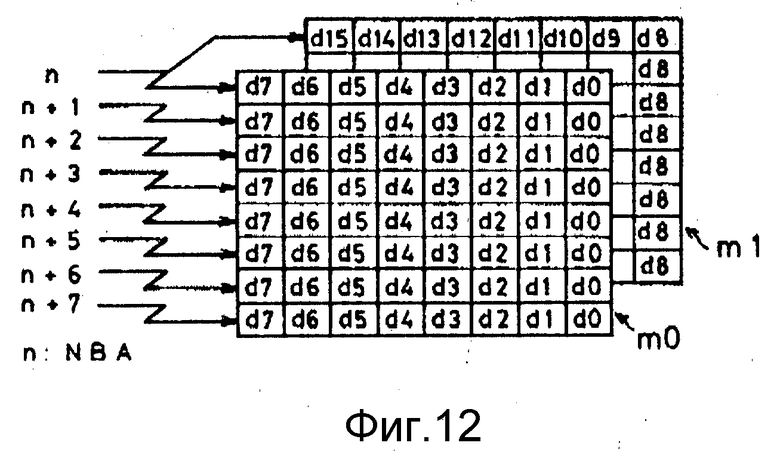

Фиг. 12 представляет структуру данных одного символа, хранящегося в символьной памяти произвольного доступа.

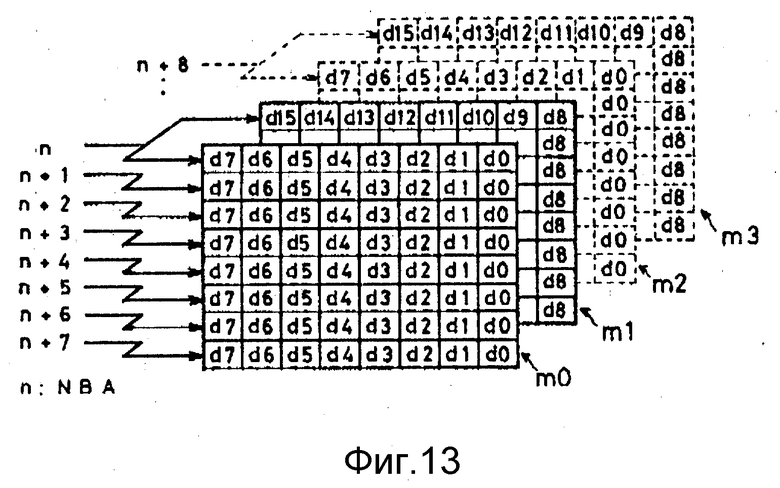

Фиг. 13 представляет структуру данных одного символа, хранящегося в символьной памяти произвольного доступа.

Фиг. 14 представляет структуру данных одного символа, хранящегося в символьной памяти произвольного доступа.

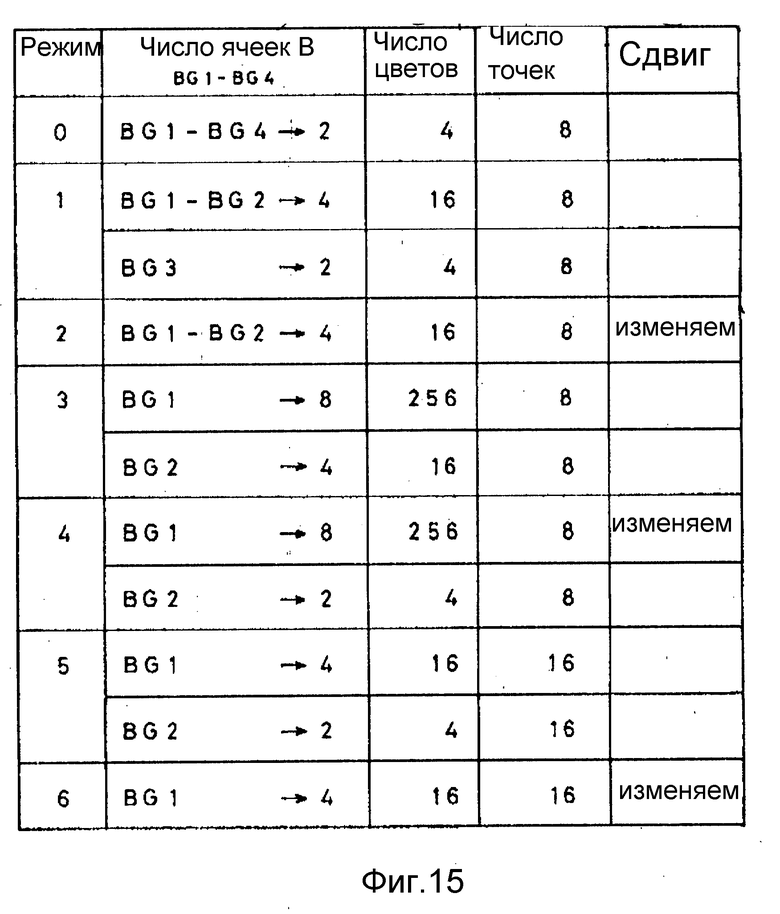

Фиг. 15 иллюстрирует зависимость между числом ячеек, числом цветов, числом элементов изображения в горизонтальном направлении одного символа и наличием или отсутствием смещающего изменения режима.

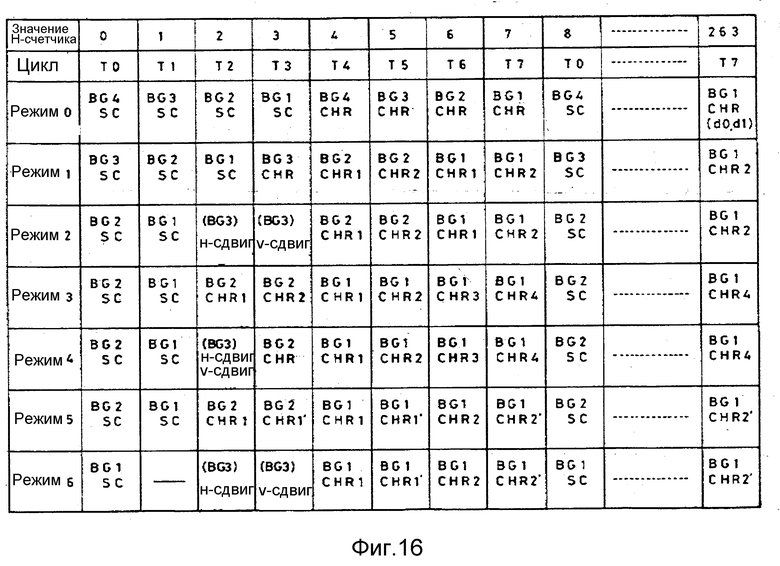

Фиг. 16 иллюстрация цикла обработки фонового изображения варианта осуществления, представленного фиг. 1.

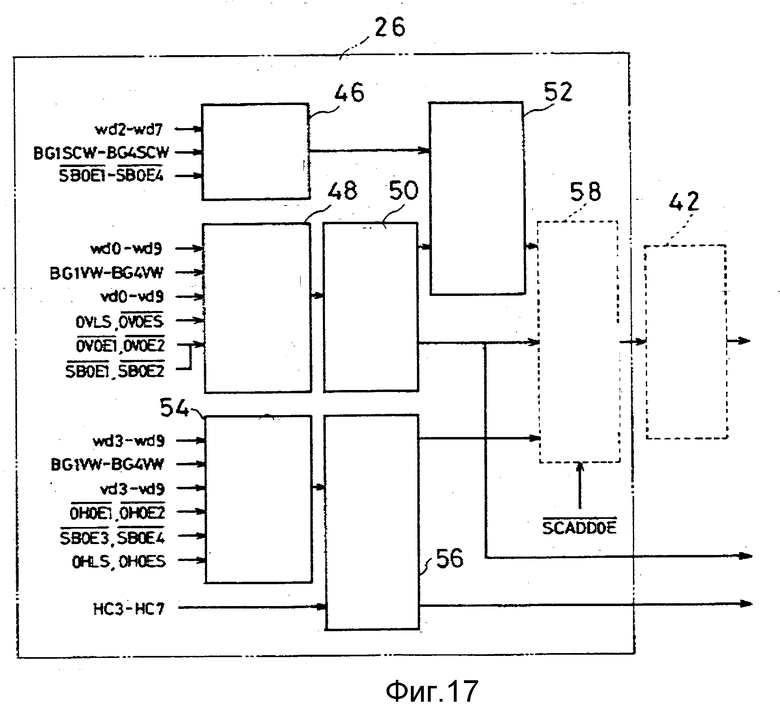

Фиг. 17 является блок-схемой адресации экранов варианта, представленного фиг. 1.

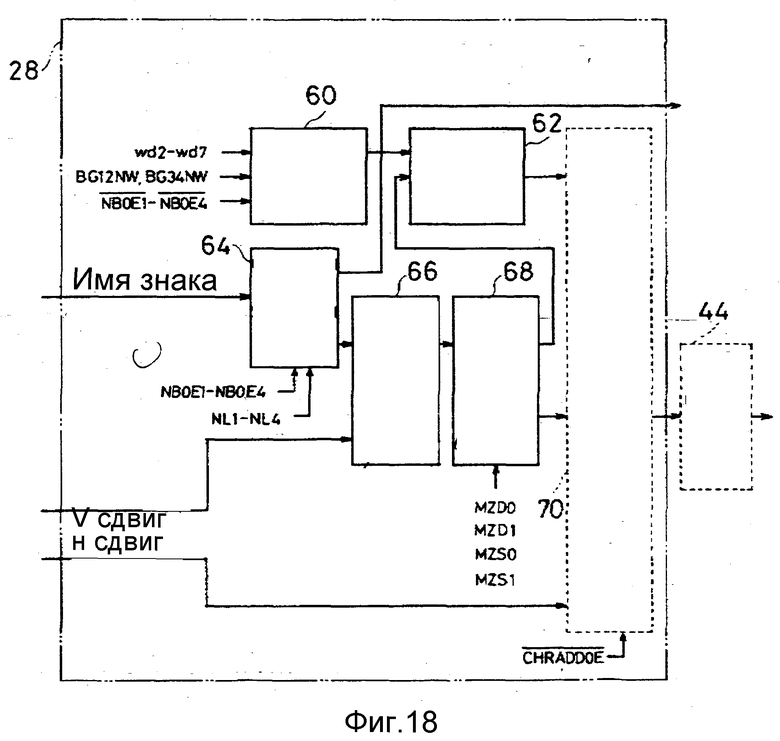

Фиг. 18 является блок-схемой адресации символов варианта осуществления, представленного фиг. 1.

Фиг. 19 является блок-схемой преобразующей цветовые коды схемы, соответствующей варианту осуществления, представленного фиг. 1,

Фиг. 20 является блок-схемой выводящей схемы, соответствующей варианту осуществления, представленного фиг. 1.

Отображающее фоновые изображения устройство 10 в варианте осуществления, представленном фиг. 1, применяется совместно с дисплеем растрового развертывающего типа (не показан), который является одним из возможных дисплеев. Дисплей растрового развертывающего типа имеет дисплейный экран, состоящий из X элементов изображения в горизонтальном направлении и Y элементов изображения в вертикальном направлении. Когда один символ, образующий фоновое изображение, имеет n элементов изображения в горизонтальном направлении и m элементов изображения в вертикальном направлении, на дисплейном экране можно отобразить всего H • M символов, содержащих N (=x/n) символов в горизонтальном направлении и M (=y/m) символов в вертикальном направлении.

Устройство отображения фоновых изображений 10, представленное фиг. 10, содержит микропроцессор 12. Микропроцессор 12 служит в качестве средства управления записью для управления записью данных в записываемую-считываемую память, подобную памяти 40 произвольного доступа (которая описана ниже). Память 40 произвольного доступа включает в себя экранную память 42 произвольного доступа и символьную память 44 произвольного доступа, как иллюстрируют фиг. 3 и 9.

Режимный регистр 14, схема 16 адресации экранов для обозначения адреса записи и адреса считывания в экранной памяти 42 произвольного доступа и схема 18 адресации символов для обозначения адреса записи и считывания в символьной памяти 44 произвольного доступа соединены с микропроцессором 12 через посредство шины данных и шины адресов. Генерирующая тактовые сигналы схема 20 соединена с режимным регистром 14. Показание счета Hc и показание счета Vc, представляющие соответственно позицию горизонтальной развертки и позицию вертикальной развертки электронного луча на дисплее (не показан), выводятся из HV счетчика 22 на генерирующую тактовые сигналы схему 20. Генерирующая тактовые сигналы схема 20 подает управляющий считыванием сигнал на схему 16 адресации экранов и схему 18 адресации символов последовательно каждый цикл с нулевого по седьмой цикл на основе счетных показаний Hc и Hv счетчика HV 22. В результате этого данные обозначения символов и данные элементов изображения считываются из экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа за восемь циклов на каждом временном периоде, в течение которого одна точка отображается на экране. Однако решение о том, какие циклы следует использовать для подачи управляющего записью сигнала на схему 16 адресации экранов и схему 18 адресации символов, зависит от того, какой из BG режимов от нулевого до седьмого представлен режимными данными в режимном регистре 14. В настоящем варианте осуществления управляющий считыванием сигнал поступает на схему 16 адресации экранов в по крайней мере двух циклах, т.е. нулевом цикле и первом цикле, и максимально в четырех циклах, т.е. с нулевого по третий цикл, в то время как он поступает на схему 18 адресации символов по крайней мере в четырех циклах, т. е. с четвертого по седьмой цикл, и максимально в шести циклах, т.е. со второго по седьмой цикл.

Данные элементов изображения, считанные из символьной памяти 44 произвольного доступа, поступают на фиксирующие схемы с 26a по 26f, встроенные в преобразующую цветовые коды схему 24 параллельным образом. Число фиксирующих схем с 26a по 26f, которое следует предусмотреть, ассоциируется с числом фоновых экранов и числом ячеек, которое обозначается режимными данными (шесть соответствует максимальному числу циклов, отводимых на считывание из символьной памяти 44 произвольного доступа в варианте осуществления), и каждая из фиксирующих схем имеет запоминающие элементы (триггеры) на 16 битов. Данные, фиксируемые этими фиксирующими схемами с 26a по 26f, преобразуются в последовательные битовые данные параллельным образом схемой 28 параллельно-последовательного преобразования и поступают на комбинирующую данные элементов изображения схему 30, встроенную в выходную схему 29, как последовательные данные по два бита на точку. Комбинирующая данные элементов изображения схема 30 преобразует последовательные битовые данные в комбинацию данных элементов изображения для каждого фонового экрана (с BG1 по BG4) так, что данные элементов изображения оказываются комбинацией ячеек, соответствующих BG режиму, на основе режимных данных из режимного регистра 14 и подает их на приоритетную схему 32. Приоритетная схема 32 подает данные элементов изображения обладающего наибольшим приоритетом одного из фоновых экранов (с BG1 по BG4) на генерирующую цвет схему 34 в качестве обозначающих цвет данных на основе комбинации приоритетных данных из одного бита, которые вместе с именем символа входят в состав данных обозначения символов. Генерирующая цвет схема 34 генерирует цветной видеосигнал (аналоговый сигнал) на основе палитровых данных, считанных из экранной памяти 42 произвольного доступа и каждого (набора) из данных элементов изображения.

Внешняя память 36, содержащая постоянную память 38, которая является одним из примеров неразрушаемой памяти, в корпусе или кассете (не показана) устанавливается с возможностью съема на микропроцессор 12. Эта постоянная память 32 имеет запоминающую данные элементов изображения область 38a, запоминающую данные обозначения символов область 38b, запоминающую режимные данные область 38c и запоминающую пересылающие (считывающие) данные программы область 38d, как иллюстрирует карта памяти на фиг. 2.

Более конкретно, запоминающая данные элементов изображения область 38a обладает информационной емкостью, достаточной для хранения шаблонных данных элементов изображения (графических данных) для всех символов, отображаемых во всех сценах, и хранит данные элементов изображения для каждой ячейки так, что один элемент изображения (или один пиксел) на дисплее представлен не менее чем двумя ячейками. Запоминающая данные обозначения символов область 38b обладает емкостью, достаточной для хранения всех фоновых экранов, и хранит данные обозначения символов для обозначения максимально N x M символов для каждого фонового экрана относительно всех фоновых экранов. Запоминающая режимные данные область 36c хранит режимные данные, причем эти режимные данные выбирают или обозначают не менее одного из максимального числа фоновых экранов (четыре экрана с BG1 по BG4 в варианте осуществления), которые могут быть отображены в одной сцене, т.е. в одном кадре, и обозначают число ячеек в каждом из фоновых экранов. Эти режимные данные запоминаются в зависимости от тактов, когда меняются режимы отображения фоновых изображений (семь режимов, от BG режима 0 до BG режима 6 в варианте осуществления). Режимные данные могут запоминаться для каждой дисплейной сцены. Запоминающая пересылающие данные программы область 38d запоминает программы для пересылки данных, необходимых для отображения в одной сцене из данных элементов изображения, данных обозначения символов и режимных данных, хранящихся в названных выше запоминающих областях с 38a по 38c, на экранную память 42 произвольного доступа, символьную память 44 произвольного доступа и режимный регистр 14.

Далее, когда внешняя память 36 используется в качестве кассеты для телевизионного игрового комплекта (набора), т.е. отображающее фоновые изображения устройство 10 является телевизионным игровым комплектом, постоянная память 38 имеет запоминающую звуковые программы область 38e и запоминающую программу считывания контроллера область 38f, как показано на фиг. 2. Запоминающая звуковые программы область 38e хранит данные для создания музыкального сопровождения и звуковых эффектов. Запоминающая программу считывания контроллера область 38f хранит данные для периодического опознания рабочего состояния контроллера (не представлен на рисунке), соединенного с телевизионным игровым комплектом.

Как видно на фиг. 3 - 9, хотя экранная память 42 произвольного доступа и символьная память 44 произвольного доступа образуют соответственно пространства памяти, полученные разделением одной памяти произвольного доступа большого объема, можно использовать две меньшего объема памяти произвольного доступа в качестве экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа, соответственно. В случае, когда для прокрутки необходима запоминающая область, равная четырем экранам на один фоновый экран, необходима экранная память 42 произвольного доступа объемом 32 • 32 • 4 = 4096 слов (приблизительно 4K слов), т.е. 8192 = 8Kбайтов на фоновый экран (BG), поскольку одно слово равно двум байтам. Поэтому, в случае BG режима 0, когда максимально используется четыре фоновых экрана с BG1 по BG4, 8192 • 4 = 32 Kбайта, что в четыре раза превышает названную выше необходимую емкость. Первые адреса в областях для хранения соответствующих обозначающих символы данных, образующих фоновые экраны с BG1 по BG4 в экранной памяти 42 произвольного доступа, соответственно определяются как базовые экранные адреса (с SBA1 по SBA4). Однако в некоторых режимах некоторая часть базовых экранных адресов может не существовать.

Зависимость между адресным пространством любого одного из фоновых экранов с BG1 по BG4d экранной памяти 42 произвольного доступа и базовыми экранными адресами (SBA) проиллюстрирована фиг. 10. Если BA представить числом n (равным любому реальному адресу любого одного из SBA1 по SBA4), три цифры после n представляют адрес в шестнадцатеричной системе исчисления. Каждая адресная позиция (клетка на фиг. 10) получена делением дисплея на 32 части в вертикальном направлении и в горизонтальном направлении. Данные обозначения символов для обозначения (указания) символа, подлежащего отображению в позиции, записывается по адресу экранной памяти 42 произвольного доступа, который соответствует этой позиции. В данных обозначения символов одно слово содержит шестнадцать битов с d0 по d15, символьный код (или имя символа) обозначается в младших десяти битах с d0 по d9, цветная палитра задается тремя битами с d10 по d12, приоритет каждого символа среди фоновых экранов (BG1 по BG4) обозначается одним битом d13, а V триггер и H триггер символа обозначаются старшими двумя битами d14 и d15, как иллюстрирует фиг. 11. Хотя приоритетные данные имеют только один бит на фоновый экран, фоновый экран, подлежащий отображению по приоритету, может быть идентифицирован этими приоритетными данными в комбинации с приоритетными данными другого фонового экрана. Подобные данные обозначения символов имеют одну и ту же структуру данных в любом режиме.

С другой стороны, в символьной памяти 44 произвольного доступа число байтов (число ячеек) для представления восьми элементов изображения в горизонтальном направлении одного символа отлично, и максимальное число символов, которые могут быть отображены в одной сцене, разнится в зависимости от случаев, когда число ячеек (число цветов) ограничено для увеличения числа символов, число символов ограничено для увеличения числа ячеек (числа цветов), а также число битов данных для каждого элемента изображения увеличено для обеспечения точного высококачественного изображения. Условия определяются на основе любого одного из режимов с BG0 по BG6, обозначаемого режимными данными. Объем одного символа, хранящегося в символьной памяти 44 произвольного доступа, разнится в зависимости от числа битов (количества данных) для представления одной точки.

Например, когда одна точка представляется двумя битами, используют две ячейки m0 и m1 на символ, причем клетка 0 образуется из восьми байтов (с n по n + 7), каждый из которых имеет восемь битов с d0 по d7, клетка m1 образуется из восьми байтов (с n по n + 7), каждый из которых имеет восемь битов с d8 по d15, как иллюстрирует фиг. 12. Другими словами, одно слово (=двум байтам) содержит 16 битов с d0 по d15, и биты с d0 по d7 и биты с d8 по d15 в одном и том же слове образуют пары.

Когда один элемент изображения представляется четырьмя битами, используются четыре ячейки m0 по m4 на один символ, причем ячейки m0 по m1 образуются восемью словами, т.е. с n по n + 7, ячейки m2 и m3 образуются восемью словами, т.е. с n + 8 по n + 15, как иллюстрирует фиг. 13.

Когда один элемент изображения представляется восемью битами, восемь ячеек с m по m7 используются на один символ, причем ячейки m0 и m1, ячейки m2 и m3, ячейки m4 и m5 и ячейки m6 и m7 образуются соответственно с восемью словами, т.е. с n по n + 7, с n + 8 по n + 15, с n + 15 по n + 23 и с n + 24 по n + 31, как иллюстрирует фиг. 14.

Число ячеек, число цветов и тому подобное для каждого фонового экрана (с BG1 по BG4) переключаются изменением способа записи в экранную память 42 произвольного доступа и/или символьную память 44 произвольного доступа, входящих в память 40 произвольного доступа в зависимости от того, какой из режимов с BG0 по BG4 используется, о чем подробно будет сказано ниже.

Изучим теперь карты памяти каждого BG режима памяти 40 произвольного доступа, которые представлены на фиг. 15 и фиг. 3 - 9, при этом ниже будут описаны подробно зависимости между числом ячеек в каждом фоновом экране (BG), которое отличает настоящее изобретение, числом цветов, числом элементов изображения на одной строке в горизонтальном направлении одного символа и наличием или отсутствием сдвигового изменения и данными в памяти 40 произвольного доступа, соответствующими каждому BG режиму.

В BG режиме 0, когда отображаются четыре фоновых экрана, используются две ячейки m0 и m1 на каждый фоновый экран (с BG1 по BG4), обеспечивая возможность отображать четыре (22) цвета. Дополнительно, BG режим 0 является режимом для предоставления одной строки в горизонтальном направлении одного символа восемью точками. Формат хранения (или записывания) данных обозначения символов и данных элементов изображения в экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа проиллюстрирован фиг. 3.

В BG режиме 1, когда отображаются три фоновых экрана, 16 (=24) цветов могут быть отображены с помощью четырех ячеек m0 и m3 в фоновых экранах BG1 и BG4 и четыре цвета могут быть отображены с помощью двух ячеек m0 и m1 в фоновом экране BG3. Этот BG режим 1 является режимом для предоставления одной строки в горизонтальном направлении одного символа восемью точками. Формат хранения данных обозначения символов и данных элементов изображения в экранной памяти 42 произвольного доступа и символьной памяти 44 представлен фиг. 4.

В BG режиме 2, когда два фоновых экрана отображаются, 16 (=24) цветов могут быть отображены с помощью четырех ячеек m0 и m3 на фоновых экранах BG1 и BG2. BG режим 2 является режимом для предоставления одной строки в горизонтальном направлении одного символа восемью точками. Формат хранения данных обозначения символов и данных элементов изображения в экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа представлен на фиг. 5.

В BG режиме 3, когда отображаются два фоновых экрана, могут быть отображены 256 (=28) цветов с помощью восьми ячеек m0 по m7 на фоновом экране BG1 и 16 цветов может быть отображено с помощью четырех ячеек m0 по m3 на фоновом экране BG2. BG режим 2 является режимом для представления одной строки в горизонтальном направлении одного символа восемью точками. Формат хранения данных обозначения символов и данных элементов изображения в экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа в этом случае представлен на фиг. 6.

В BG режиме 4, когда отображаются два фоновых экрана, можно отобразить 256 (=28) цветов с помощью восьми ячеек m0 по m7 на фоновом экране BG1 и четыре цвета можно отобразить с помощью двух ячеек m0 по m3 на фоновом экране BG2. BG режим 4 является режимом для представления одной строки в горизонтальном направлении одного символа восемью точками. Формат хранения данных обозначения символов и данных элементов изображения в экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа в этом случае представлен на фиг. 7.

В BG режиме 6, когда отображается один фоновый экран, может быть отображено 16 цветов с помощью восьми ячеек m0 по m3 на фоновом экране BG1. BG режим 6 является режимом для представления одной строки в горизонтальном направлении одного символа 16 точками. Формат хранения данных обозначения символов и данных элементов изображения в экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа в этом случае показан на фиг. 9.

В BG режиме 2 для фонового экрана BG14 и BG режиме 4 или в BG режиме 6 смещение изменяемо. Изменение смещения означает изменение базового экранного адреса, в результате которого весь фоновый экран перемещается в горизонтальном направлении или вертикальном направлении (что часто называют "прокруткой").

Ниже дано описание работы варианта осуществления, представленного Фиг. 1. В качестве примера для иллюстрации выбран случай, когда фоновый экран сначала отображается в BG режиме 0, а затем BG режим 0 наполовину переходит в BG режим 3.

Сначала перед отображением в BG режиме 0 микропроцессор 12 считывает режимные данные для обозначения (указания) BG режима 0 из запоминающей области 38c и временно запоминает их в режимном регистре 14 на основе программных данных в запоминающей передаточные программы области 38d во время инициации или во время периода гашения (включая как горизонтальное гашение, так и вертикальное гашение) дисплея. В это же время соответствующие данные обозначения символов, образующие фоновые экраны с BG1 по BG4, считываются из запоминающей области 38d и записываются в экранную память 42 произвольного доступа и некоторое множество (например, максимально 1024) данных элементов изображения, используемых в каждом из фоновых экранов с BG1 по BG4, также считывается из запоминающей области 38a и записывается в символьную память 44 произвольного доступа. Состояние каждой из экранной памяти 42 произвольного доступа в этот момент представлено на фиг. 3, как сказано выше.

После этого данные считываются из экранной памяти 42 произвольного доступа и символьной памяти 44 произвольного доступа синхронно с разверткой дисплея. Более конкретно, HV счетчик дает показание Hc, соответствующее горизонтальной позиции электронного луча, и показание Vc, соответствующее его вертикальной позиции, синхронно с разверткой электронным лучом дисплея и подает показания счетчика на генерирующую тактовые сигналы схему 20, схему 16 адресации экранов и схему 18 адресации символов. В ответ на это генерирующая тактовые сигналы схема 20 генерирует сигналы в восьми циклах, т.е. с нулевого цикла до седьмого цикла, в то время как электронный луч перемещается на одну точку на дисплее и подает сигналы с нулевого цикла до третьего цикла на схему 16 адресации экранов, а сигналы с четвертого цикла до седьмого цикла подает на схему 18 адресации символов.

Схема 16 адресации экранов генерирует адреса, имеющие базовые экранные адреса SBA4, SBA3, SBA2 и SBA1, соответствующие фоновым экранам BG4, BG3, BG2 и BG1, складываемым с адресом (который может быть любым из интервала от 000H до 3FFH), представляющим позицию дисплея, соответствующую показаниям счетчика Hc и Vc в текущий момент, последовательно для каждого цикла в подходящие моменты тактирования от нулевого до третьего цикла, чтобы указать адрес считывания экранной памяти 42 произвольного доступа. Более конкретно, схема 16 адресации экранов включает в себя схему 46 генерирования базовых адресов, выбирающую V (вертикальное) смещение схему 48, вычисляющую V смещение схему 50, вычисляющую базовые адреса схему 52, выбирающую H (горизонтальное) смещение схему 54, вычисляющую H-смещение схему 56 и выбирающую адрес схему 58, что иллюстрирует фиг. 17. Данные H (горизонтального) смещения выдает выбирающая H смещение схема 54, и они складываются с выходным сигналом HV счетчика 22, т.е. с показанием Hc вычисляющей H-смещение схемой 56. С другой стороны, данные V (вертикального смещения) выдает выбирающая V-смещение схема 48, и они складываются с показанием Vc (или его модификацией) HV счетчика 22 вычисляющей V (вертикальное) смещение схемой 50. С другой стороны, базовый экранный адрес, полученный генерирующей базовые адреса схемой 46 и вычисляющей базовый адреса схемой 52, совместно с соответствующими выходными сигналами вычисляющей V (вертикальное) смещение схемой 50 и вычисляющей H (горизонтальное) смещение схемы 56 поступают на выбирающую адреса схему 58. Выбирающая адреса схема 58 преобразует входные сигналы в зависимости от символьного размера, перемежения или отсутствия перемежения и подает их на экранную память 42 произвольного доступа в качестве экранных адресов. В ответ на это данные обозначения символов (см. фиг. 11) считываются из экранной памяти 42 произвольного доступа. Более конкретно, символы кодов (с d0 по d9), входящие в состав обозначающих символы данных, образующие каждый из фоновых экранов с BG1 по BG4, поступают на схему 18 адресации символов в качестве данных, указывающих адрес символьной памяти 44 произвольного доступа. В то же время палитровые данные (с d10 по d12) из символьной памяти 44 произвольного доступа поступают на генерирующую цветовой сигнал схему 34, а BG приоритетные данные (d13) поступают на приоритетную схему 32.

С другой стороны, схема 18 адресации символов выдает символьные адреса на основе данных обозначения символов, образующих фоновые экраны BG1 по BG4, последовательно считываемых с нулевого цикла по третий цикл и синхронно с тактированием циклов с четвертого по седьмой. Более конкретно, схема 18 адресации символов включает в себя генерирующую базовые адреса схему 60, вычисляющую базовые адреса схему 62, выбирающую имя символа схему 64, вычисляющую смещение адреса символа схему 66, выбирающую число цветов для символьного адреса схему 68 и переключающую символьного адреса схему 70, как это иллюстрирует фиг. 18. Символьное имя, входящее в состав данных обозначения символов, выводится из выбирающей символьное имя схемы 64 и подается на вычисляющую смещение символьного адреса схему 66. Данные V (вертикального) смещения поступают на вычисляющую смещение символьного адреса схему 66 и складываются с данными символьного имени в вычисляющей смещение символьного адреса схеме 66. Результаты сложения поступают на выбирающую символьный адрес схему 70 и вычисляющую базовые адреса схему 62 через выбирающую число цветов для символьного адреса схему 68. Вычисляющая базовые адреса схема 62 складывает выходной сигнал выбирающей число цветов для символьного адреса схемы 68 с базовым адресом имени NBA, поступающим от генерирующей базовые адреса схемы 60, и подает результаты сложения на выбирающую символьный адрес схему 70. Далее, выбирающая символьный адрес схема 70 подает на символьную память 44 произвольного доступа один из адресов, вводимый в выбирающую символьный адрес схему 70, в зависимости от наличия или отсутствия смещения, H (горизонтального) триггера и/или V (вертикального) триггера. В ответ на это символьные имена (символьные коды) в символьной памяти 44 произвольного доступа указываются в порядке 0, n, 1 и 1023, например, в примере на фиг. 3, и в то же время данные элементов изображения из двух битов, которые соответствуют друг другу, считываются на основе показаний счетчика Hc и Vc из генерирующей тактовые сигналы схемы 20.

Данные элементов изображения с именами 0, n, 1 и 1023, считанные в такты четвертого и седьмого циклов, фиксируются соответственно в четырех фиксирующих схемах с 26a по 26d фиксирующей схемы 26 на 16 битов (см. фиг. 1) в указанном порядке при битовой параллельности. Эти данные, т.е. цветовые данные, соответствующие восьми точкам в горизонтальном направлении одного символа, которые соответствуют определенной дисплейной позиции каждого из фоновых экранов с BG1 по BG4 (данные их двух битов для обозначения четырех цветов на элемент изображения), поступают параллельно на схему 28 параллельно-последовательного преобразования. Схема 28 параллельно-последовательного преобразования считывает параллельные битовые данные в ответ на сигнал "записать" W от генерирующей тактовые сигналы схемы 20, т.е. сигнал от тактирующей фиксирование схемы 72, представленной на фиг. 19, и временно запоминает этот сигнал. Схема 28 параллельно-последовательного преобразования преобразует параллельные битовые данные в последовательные битовые данные синхронно с тактирующим считывание сигналом "тактировать", поступающим в период, который в два раза превышает период, за который электронный луч перемещается на один элемент изображения, т.е. в ответ на сигнал от тактирующей синхронизацию схемы 74, представленной фиг. 19, и подает их на комбинирующую данные элементов изображения схему 30 (см. фиг. 1 и 19).

Комбинирующая данные элементов изображения схема 30 на основе режимных данных комбинирует пары последовательных данных, т.е. a0 и a1, b0 и b1, c0 и c1, d0 и d1, e0 и e1 и f0 и f1, поступающие от схемы 28 параллельно-последовательного преобразования, с битами, число которых соответствует числу ячеек. Затем цветовые данные для каждого из фоновых экранов (с BG4 по BG1) выводятся и поступают на приоритетную схему 32 (см. фиг. 1 и 20). Приоритетная схема 32 подает цветовые данные более высокого приоритета фонового экрана на генерирующую цвета схему 34 (см. фиг. 1 и 2) на основе режимных данных и приоритетных данных. В то же время, когда обеспечена опознающая прозрачность схема 82 (см. фиг. 20), и цветовые данные более высокого приоритета фонового экрана имеют признак прозрачности, выводятся цветовые данные следующего по старшинству приоритетов фонового экрана. В ответ на это генерирующая цветовые данные схема 34 генерирует цветовой видеосигнал (аналоговый сигнал), определяемый комбинацией цветовых данных и палитровых данных, и подает его на дисплей. Более конкретно, данные элементов изображения для каждого фонового экрана поступают в виде цветового кода на комбинирующую цветовые коды схему 80 и комбинируются с цветовым кодом подвижного символа в комбинирующей цветовой сигнал схеме 34. В то же время функционирование приоритетной схемы 32 принуждает выбирающую цветовой код схему 88 сделать эффективным цветовой код символа, подлежащего отображению, в соответствии с приоритетом. Сигнал выводится из выбирающей цветовую палитру схемы 88 на основе палитровых данных и поступает на генерирующую видеосигнал схему 90. Затем цветовой видеосигнал снимается с генерирующей видеосигнал схемы 90.

Описанные выше операции воспроизводятся применительно фоновым экранам с BG1 и BG4 для формирования одной сцены. Когда отображается один и тот же фоновый экран, одна и та же операция воспроизводится кадр за кадром синхронно с разверткой дисплея без перезаписи данных в экранную память 42 произвольного доступа и символьную память 44 произвольного доступа.

Далее, фоновый экран можно заменить без изменения BG режима. В этом случае, однако, микропроцессор 12 может считывать данные обозначения символов и данные элементов изображения из запоминающих областей 38b и 38a без считывания режимных данных и записи данных в экранную память 42 произвольного доступа и символьную память 44 произвольного доступа.

В то же время, если желательно увеличить число цветов вместо уменьшения числа фоновых экранов при отображении фонового экрана в описанном выше BG режиме 0, выполняется следующая операция. Более конкретно, микропроцессор 12 считывает режимные данные для указания BG режима 3 на основе программы в запоминающей передаточные программы области 38d и временно запоминает их в режимном регистре 14 во время инициализации или в течение периода гашения. Дополнительно, микропроцессор 12 записывает данные обозначения символов, образующие фоновые экраны BG1 и BG2, хранящиеся в запоминающей области 38d, в соответствующие области в экранной памяти 42 произвольного доступа, одновременно записывая данные элементов изображения, подлежащие отображению, в качестве фоновых экранов BG1 и BG2, хранящихся в запоминающей области 38a, в соответствующие области в символьную память 44 произвольного доступа. В этом случае, поскольку фоновый экран BG1 имеет восемь ячеек m0 до m7, а фоновый экран BG2 имеет четыре ячейки m0 по m3, данные элементов изображения, используемые в фоновом экране BG1, записываются в каждую из ячеек m0 по m7 по базовому именному адресу (NBA) 1 и данные элементов изображения, используемые в фоновом экране BG2, записываются в каждую из ячеек m0 до m4 в базовый именной адрес NBA 2.

С другой стороны, в BG режиме 3 считывание из экранной памяти 44 произвольного доступа выполняется в нулевом цикловом периоде и первом цикловом периоде, поскольку число фоновых экранов меньше, а число ячеек больше, чем в BG режиме 0. Дополнительно, данные элементов изображения, соответствующие фоновому экрану BG2 в символьной памяти 44 произвольного доступа, считываются за два цикла, т.е. во втором и третьем циклах, и данные элементов изображения, соответствующие фоновому экрану BG1, считываются за четыре цикла, т.е. с четвертого по седьмой цикл. Другие операции почти аналогичны тем, которые исполняются в BG режиме 0, и потому их детальное описание опущено.

Если число фоновых экранов, образующих одну сцену, число ячеек (т.е. число цветов), используемых в каждом фоновом экране, и число элементов изображения на одной строке в горизонтальном направлении одного символа переключаются на основе BG режима, как в настоящем варианте осуществления, производительность микропроцессора 12 отображать изображение на ограниченном временном интервале может быть максимизирована. Дополнительно, данные, ранее записанные во внешнюю память 36, т.е. в память 38, считываются по мере необходимости. Поэтому, если емкость памяти 40 произвольного доступа мала, некоторое множество фоновых изображений может быть отображено лишь путем изменения BG режима, что позволяет эффективно использовать память 40 произвольного доступа.

Хотя в описанном выше варианте осуществления генерирующее данные обозначения символов устройство и генерирующее данные элементов изображения устройство содержит постоянную память 38 и память 40 произвольного доступа и данные, хранящиеся в постоянном памяти 38, пересылаются в память 40 произвольного доступа, режимные данные, данные обозначения символов и данные символьных шаблонов могут храниться в постоянной памяти в связи с каждым дисплейным экраном, если требуется достичь лишь максимальной производительности микропроцессора 12.

Дополнительно, хотя в описанном выше варианте осуществления в качестве внешнего запоминающего устройства используется запоминающая кассета, в настоящем изобретении может быть использовано внешнее запоминающее устройство, подобное CD-ROM. Когда используется запоминающая кассета, постоянная память 38, содержащаяся в запоминающей кассете, хранит, например, описанные выше программные данные, включающие в себя данные обозначения символов, данные элементов изображения и режимные данные, и микропроцессор управляет отображением фонового изображения на основе программных данных.

С другой стороны, когда используется CD-ROM постоянная память, программные данные, описанные выше, например, записываются оптически в качестве цифровых данных в CD-ROM постоянную память (не показана). Дополнительно, оптический считыватель для оптического считывания данных, записанных в CD-ROM постоянной памяти, соединяется с подходящим разъемом, например удлинительным разъемом (не показан). Когда используется CD-ROM, также используется запоминающая кассета. В этом случае, однако, запоминающая кассета содержит постоянную память (не показана), хранящую пусковую программу для управления работой оптического считывателя, и буферную память произвольного доступа (не показана) для временного хранения программных данных, считываемых из CD-ROM постоянной памяти. Перед началом дисплейной работы микропроцессор 12 подает управляющие данные на оптический считыватель на основе пусковой программы из постоянной памяти для считывания данных, записанных в CD-ROM постоянной памяти. Часть данных обозначения символов, считанных их CD-ROM памяти, пересылается на экранную память 42 произвольного доступа, и данные элементов изображения аналогичным образом пересылаются на символьную память 44 произвольного доступа. В то же самое время другие программные данные, включающие режимные данные, пересылаются на буферную память произвольного доступа в запоминающей кассете. После того как данные, считанные из CD-ROM постоянной памяти оптическим считывателем, переданы однажды в соответствующие памяти, микропроцессор 12 выполняет описание выше операции путем обращения к соответствующим памятям.

Хотя настоящее изобретение подробно описано и проиллюстрировано, должно быть ясно, что это сделано исключительно ради иллюстративных целей и что не может восприниматься как ограничение, поскольку сущность и объем настоящего изобретения ограничиваются исключительно приложенной формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОБРАБАТЫВАЮЩЕЕ ИЗОБРАЖЕНИЕ УСТРОЙСТВО И ВНЕШНЕЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2163734C2 |

| УСТРОЙСТВО ОБРАБОТКИ ИЗОБРАЖЕНИЯ | 1990 |

|

RU2113727C1 |

| УСТРОЙСТВО ДИСПЛЕЯ ПОДВИЖНОГО ИЗОБРАЖЕНИЯ И ВНЕШНЕЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, ИСПОЛЬЗУЕМОЕ ДЛЯ НЕГО | 1991 |

|

RU2106012C1 |

| СИСТЕМА ОБРАБОТКИ ИЗОБРАЖЕНИЯ С АНАЛОГОВЫМ ДЖОЙСТИКОМ | 1996 |

|

RU2155368C2 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 1995 |

|

RU2117388C1 |

| КРАНОВОЕ ПРЕДОХРАНИТЕЛЬНОЕ УСТРОЙСТВО | 1989 |

|

RU2093452C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ С АНАЛОГОВЫМ ДЖОЙСТИКОМ (ВАРИАНТЫ) | 1996 |

|

RU2163159C2 |

| СПОСОБ И СИСТЕМА КОДИРОВАНИЯ И СПОСОБ И СИСТЕМА ДЕКОДИРОВАНИЯ | 1996 |

|

RU2154350C2 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ СИМВОЛОВ, СТОХАСТИЧЕСКИЙ КОДЕР (ВАРИАНТЫ) | 1995 |

|

RU2125765C1 |

| УСТРОЙСТВО И СПОСОБ ПЕРЕМЕЖЕНИЯ/ОБРАТНОГО ПЕРЕМЕЖЕНИЯ ДЛЯ СИСТЕМЫ СВЯЗИ | 1999 |

|

RU2216099C2 |

Изобретение относится к вычислительной технике. Его использование в системах отображения изображений с фоновыми экранами позволяет произвольно определять число фоновых экранов в каждой сцене и комбинацию числа цветов каждого из фоновых экранов. Отображающее фоновое изображение устройство содержит средство запоминающего устройства данных изображения символов, средство запоминающего устройства данных элементов изображения, первое и второе средства считывания, средство параллельно-последовательного преобразования, средство вывода и средство генерации видеосигнала. Технический результат достигается благодаря введению средства генерации данных режима и выполнению средства параллельно-последовательного преобразования с возможностью запоминания данных элементов изображения для заданного числа элементов изображения на один символ. 5 з.п.ф-лы, 20 ил.

5. Устройство по любому предшествующему пункту, также содержащее средство (20) генерации хронирующего сигнала, причем указанное средство генерации хронирующего сигнала содержит первое средство генерации тактового сигнала для генерации тактового сигнала низкой скорости, второе средство генерации тактового сигнала для генерации тактового сигнала высокой скорости и средство выбора указанного тактового сигнала низкой скорости или указанного тактового сигнала высокой скорости на основе указанных данных режима и для направления этих сигналов к средству (28) параллельно-последовательного преобразования.

| US 4824106 A, 25.04.89 | |||

| US 4498079 A, 05.02.85 | |||

| ДУШЕВАЯ ГОЛОВКА | 1994 |

|

RU2100100C1 |

| ТРОХОИДНАЯ РОТОРНАЯ МАШИНА | 1993 |

|

RU2105157C1 |

| СПОСОБ УПРАВЛЕНИЯ РЕАКТИВНОСТЬЮ НЕЙТРОННОЙ ЦЕПНОЙ РЕАКЦИИ В ЯДЕРНОМ РЕАКТОРЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2147774C1 |

| DE 3133902 A1, 17.03.83 | |||

| УСТРОЙСТВО ДЛЯ СОЕДИНЕНИЯ ЗАДНЕЙ БАБКИ ТОКАРНОГО СТАНКА С ЕГО СУППОРТОМ | 0 |

|

SU163863A1 |

| Устройство для отображения информации на цветном индикаторе | 1988 |

|

SU1547023A1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

Авторы

Даты

1999-01-27—Публикация

1991-11-18—Подача