Изобретение касается устройства дисплея подвижных изображений и внешнего запоминающего устройства (ЗУ), соответствующего для использования в нем, и более конкретно касается устройства дисплея подвижных изображений, такого как видеоигровое устройство, персональный компьютер, для оживления (придания подвижности) визуализации крупноразмерного объекта на мониторе растрового типа путем объединения одного или больше символов, каждый содержащий множество точек в горизонтальном и вертикальном направлениях соответственно, и внешнего ЗУ, соответствующего для использования в устройстве дисплея подвижного изображения.

Известно устройство оживленного дисплея или подвижного изображения, такое как "Семейный компьютер" (название, используемое в торговле), "Система развлечений Нинтендо" (название) и т.д. которые описаны в японской выложенной патентной заявке N 59-118184 (соответствующей патенту США N 4.824.106), поданной и опубликованной 7 июля 1984 г. Описание содержит первое ЗУ для хранения в нем данных об объекте (символе), соответствующих одному экрану, второе ЗУ для хранения в нем только данных об объекте, визуализируемом во время следующего периода горизонтального сканирования, и множество сдвиговых регистров, каждый из которых используется для хранения в нем данных о точке (графических данных) объекта. Описанное устройство оживленного дисплея подает на выход данные о горизонтальном и вертикальном положениях, коды объекта и данные признаков в отношении каждого объекта. Дополнительно такое устройство сравнивает вертикальную позицию дисплея объекта и номер строки горизонтального сканирования на мониторе с целью вынесения решения так называемого "определения попадания в диапазон", определяющего, должен или нет объект визуализироваться во время следующего периода горизонтального сканирования. Затем устройство дисплея подвижного изображения возбуждается, чтобы вынести решение по объекту о попадании в диапазон в отношении каждого объекта с тем, чтобы графические данные объекта, попадающего по решению в диапазон, передать из первого ЗУ во второе ЗУ, тем самым передавая графические данные в соответствующий сдвиговый регистр во время периода горизонтального запирания.

В описанном устройстве дисплея подвижного изображения графические данные объекта, находящегося по решению о нем в положении попадания в диапазон, в течение периода горизонтального запирания передаются на сдвиговый регистр. Поэтому скорость обработки значительно более высокая может быть реализована. Однако когда необходимо визуализировать крупноразмерный объект посредством этого устройства дисплея подвижного изображения, нагрузка, поступающая на ЦП (микропроцессор), увеличивается и ОАМ (ЗУ признаков объекта) необходимо с большой емкостью. Конкретно, представляется форме данных из 4 байтов в предшествующем уровне техники. Поэтому необходимо переписывать и перегружать крупноразмерный объект, содержащий группу II символов, в данные из 4 байтов х II в каждом первом и втором ЗУ, чтобы визуализировать такой объект. Таким образом, когда крупноразмерный объект визуализируется, нагрузка, возлагаемая на ЦП (микропроцессор), увеличивается, тем самым оказывая влияние на остальную арифметическую обработку и т.д. Поэтому размер каждого объекта и количество объектов ограничены, когда требуется визуализировать объект в диапазоне, в котором увеличение нагрузки, упомянутое выше, не оказывает влияния на такую арифметическую обработку. Дополнительно данные об объекте из всех символов объекта, т.е. данные о горизонтальных и вертикальных позициях, кодах цвета, и данные о признаках должны загружаться в ОАМ, тем самым вызывая необходимость увеличения емкости хранения ОАМ.

В противоположность вышеприведенному прототипу предшествующего уровня техники предложено устройство обработки изображений, способное визуализировать крупноразмерный объект, которое (устройство) описано, например, в японской патентной выложенной заявке N 62-24296, поданной и опубликованной 2 февраля 1987 г. Согласно описанию данные о размерах горизонтального и вертикального дисплея загружены в ЗУ признаков (соответствующего ОАМ, упомянутому выше). Дополнительно, данные о размере вертикального дисплея используются для определения попадания в диапазон, а данные о размере горизонтального дисплея используются как адрес считывания в отношении RAM символов. Таким образом, описание может создать преимущество в том, что размер объекта может произвольно изменяться в отношении каждого объекта.

В устройстве обработки изображения, описанном в японской патентной выложенной заявке N 62-24296, данные о размере горизонтального дисплея не используются, однако, для решения о попадании в диапазон, и поэтому данные о всех объектах, по решению находящихся в положении попадания в диапазон на основании данных о размере вертикального дисплея, электрически обрабатываются таким же образом, как описано в японской патентной выложенной заявке N 59-118184. Особенно, даже когда детектируемый объект лежит за обеими кромками экрана монитора, определяется, что объект в положении попадания в диапазон, вопреки факту, что объект нормально не визуализируется на экране, если решение о попадании в диапазон вынесено на основании только данных о размере вертикального дисплея. Иначе говоря, даже объект, лежащий за диапазоном, в каком он может быть визуализирован в горизонтальном направлении на экране монитора, подвергается обработке в отношении преобразования данных объекта в графические данные. С другой стороны, время, необходимое для осуществления такого процесса преобразования, поддерживается постоянным, тем самым вызывая проблему, что число объектов, каждый способный быть визуализирован одной горизонтальной строкой, значительно уменьшается. Чтобы решить такую проблему. ЦП (микропроцессор) делает необходимым выполнение процесса, чтобы избежать определения в отношении объекта, лежащего за диапазоном дисплея объекта, что он в положении попадания в диапазон. Таким образом, нагрузка или затруднения, налагаемые на ЦП, полностью не устраняются.

Имея в виду вышеназванную проблему, основная цель настоящего изобретения состоит поэтому в создании нового устройства подвижного изображения на дисплее и внешнего ЗУ, соответствующего для использования в этом устройстве.

Другая цель настоящего изобретения состоит в создании устройства дисплея подвижного изображения, способного визуализировать максимальное число объектов без снижения количества объектов, визуализируемых в горизонтальном направлении.

Еще одна цель настоящего изобретения состоит в создании устройства дисплея подвижного изображения, способного значительно снижать любую нагрузку, налагаемую на ЦП (микропроцессор), когда визуализируется крупноразмерный объект.

Еще одна цель настоящего изобретения состоит в создании устройства дисплея подвижного изображения, способного визуализировать крупноразмерный объект, используя ЗУ признаков подвижного изображения, имеющего небольшую емкость памяти.

Еще одна цель настоящего изобретения состоит в создании устройства дисплея подвижного изобретения, способного визуализировать каждый из объектов разных размеров путем использования ЗУ, имеющего небольшую емкость памяти.

Еще одна цель настоящего изобретения состоит в создании устройства дисплея подвижного изображения, способного увеличивать количество визуализируемых объектов, используя ЗУ, имеющее небольшую емкость памяти.

Еще одна цель настоящего изобретения состоит в создании устройства дисплея подвижного изображения, способного снижать нагрузку, налагаемую на процессор, для выполнения процесса оживления изображения.

Еще одна цель настоящего изобретения состоит в создании устройства дисплея подвижного изображения типа, в котором, когда некоторые или все объекты лежат в диапазоне экрана, обработка данных участка, попадающего в диапазон, блокируется с тем, чтобы надежно устранить неэффективную обработку данных, тем самым делая возможным существенное снижение числа объектов.

Еще одна цель настоящего изобретения состоит в создании внешнего ЗУ, используемого в каждом из вышеописанных устройств дисплея подвижного изображения.

Согласно одному отличительному признаку первого изобретения предусматривается устройство дисплея подвижного изображения типа, в котором крупноразмерный объект может быть визуализирован на мониторе растрового типа путем объединения одного или больше символов, каждый содержащий множество точек в горизонтальном и вертикальном направлениях соответственно, причем устройство дисплея подвижного изображения включает в себя:

первое средство ЗУ для предварительной загрузки графических данных символов, составляющих объект, в соответствующий адресный район для каждого объекта;

средство генерирования данных об обозначении объекта для генерирования данных, обозначающих объект, используемые для обозначения по крайней мере одного объекта, визуализируемого на мониторе во время следующего периода вертикального сканирования на мониторе;

средство генерирования позиционых данных для генерирования позиционных данных, используемых для представления горизонтальной и вертикальной позиций обозначенного объекта на мониторе, на котором обозначенный объект должен быть визуализирован;

средство генерирования данных выбора размера для генерирования данных выбора размера, используемых для выбора одного из размеров объекта;

второе средство ЗУ для временного хранения данных обозначения объекта и позиционных данных в нем;

средство определения попадания в диапазон для вынесения решения, должен или нет объект визуализироваться на мониторе во время следующего периода горизонтального сканирования, на основе данных о вертикальной позиции, поданных из второго средства ЗУ, и данных выбора размера, поданных от средства генерирования данных о выборе размера, и для вынесения решения, должен или нет объект визуализироваться на мониторе во время следующего периода горизонтального сканирования, на основе данных о горизонтальной позиции, поданных на выход из второго средства ЗУ, и данных о выборе размера, посланных на выход из средства генерирования данных о выборе размера, и

средство образования адреса считывания для образования адреса считывания для первого средства ЗУ в отношении объекта, подпадающего под решение об объекте, что он находится в состоянии попадания в диапазон, с помощью средства определения попадания в диапазон, на основе данных обозначения объекта, позиционных данных и данных о выборе размера, тем самым посылая образованный таким образом адрес считывания на первое средство ЗУ.

По случаю, когда первое изобретение применяется к внешнему ЗУ, внешнее ЗУ образовано со средством генерирования данных об обозначении объекта, средством генерирования позиционных данных и средством генерирования данных о выборе размера.

Например, один символ представлен в форме 8 точек (элементов изображения) в горизонтальном направлении х 0 точек (элементов изображения) в вертикальном направлении. Один объект может быть образован группой или комбинацией одного или больше символов. Графические данные (данные точки) одного или больше символов, содержащие каждый, например, 128 объектов, загружаются в первое средство ЗУ, такое как ЗУ видеоданных и т.д. в отношении каждого объекта заранее. Таким образом, требуемый объект может быть визуализирован на мониторе растрового типа путем считывания графических данных из первого средства ЗУ.

Микропроцессор (ЦП) возбуждается для размещения данных объекта во втором средстве ЗУ, таком как ОАМ (ЗУ признаков объекта), и т.д. в то время как исходное условие устанавливается в данный момент или в течение периода вертикального запирания на мониторе растрового типа. Такие данные об объекте включают в себя, например, данные обозначения объекта (данные наименования), данные о вертикальной позиции, данные о горизонтальной позиции и данные о выборе размера объекта, а также данные о палитре цветов, данные о вертикальном и горизонтальном перебросе и данные дисплея приоритета и т.д.

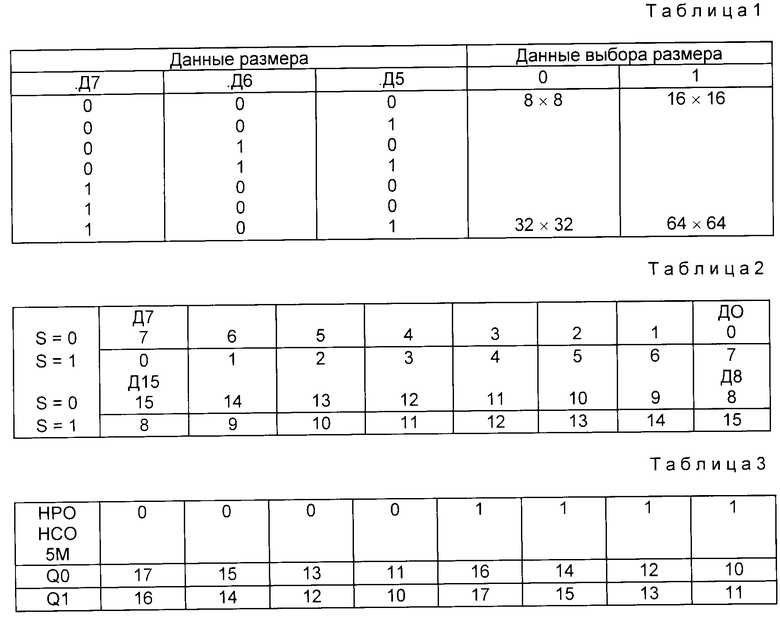

Данные определения размера объекта включают в себя данные обозначения размера объекта и данные выбора размера, например. Данные обозначения размера используются для обозначения двух размеров объекта, например, "8х8", "16х16", "32х32" и "64х64". Данные выбора размера будут, например, либо "0", либо "I". Когда "0" установлен в качестве данных выбора размера, один из обозначенных таким образом двух размеров выбирается. Когда "I" установлена в качестве данных выбора размера, выбирается другой размер его. Таким образом, размер объекта может определяться путем использования данных определения размера.

Средство определения попадания в диапазон сравнивает номер горизонтальной строки монитора растрового типа и данные вертикальной позиции объекта, например, и после этого выносит решение в отношении определения, находится или нет соответствующий объект в положении попадания в диапазон, т.е. он должен быть визуализирован посредством следующей горизонтальной строки, основываясь на результате его сравнения и размере объекта, упомянутом выше. В то же время средство определения попадания в диапазон выносит решение, является или нет соответствующий объект в положении попадания в диапазон, основываясь, например, на результате, полученном путем выполнения арифметической операции по абсолютной величине горизонтальной позиции объекта и размера объекта.

Затем графические данные объекта, подпадающего под определение, что находится в положении попадания в диапазон, по горизонтальному и вертикальному направлениям с помощью средства определения попадания в диапазон, считываются из первого средства ЗУ. Более конкретно, средство образования адреса считывания образует адрес считывания, основываясь на данных обозначения объекта, позиционных данных и размере объекта таким образом, чтобы считывать графические данные объекта, подпадающего под определение попадания в диапазон, из первого средства ЗУ.

Согласно первому изобретению средство определения попадания в диапазон выносит решение, находится или нет объект в положении попадания в диапазон в вертикальном и горизонтальном направлениях. Поэтому объект, подлежащий фактически визуализации, подвергается только определению попадания в диапазон, по сравнению со способом вынесения решения, находится или нет объект в положении попадания в диапазон только в вертикальном направлении, как в описании каждой из японских патентных выложенных заявок NN 59-118184 и 62-24296, тем самым создавая возможность предотвращения значительного снижения числа объектов. Объект, подпадающий под определение, что находится в положении попадания в диапазон, всегда визуализируется, и поэтому большое время обработки ЦП или микропроцессора может быть устранено, тем самым давая возможность улучшить эффективность функционирования микропроцессора.

Согласно одному отличительному признаку второго изобретения, предусматривается устройство дисплея подвижного изображения типа, в котором объект крупного размера может визуализироваться на мониторе растрового типа путем объединения одного или больше символов, каждый содержащий множество точек в горизонтальном и вертикальном направлениях соответственно, которое (устройство дисплея подвижного изображения) включает в себя:

первое средство ЗУ для предварительной загрузки графический данных символов, составляющих объект, в соответствующий адресный район для каждого объекта;

средство генерированных данных обозначения объекта для генерирования данных обозначения объекта, используемых для обозначения по крайней мере одного визуализируемого объекта на мониторе, во время следующего периода вертикального сканирования на мониторе;

средство генерирования позиционных данных для генерирования позиционных данных, используемых для представления позиций обозначенного объекта на мониторе, на котором обозначенный объект должен быть визуализирован;

средство генерирования данных о выборе размера для выбора размера объекта для каждого объекта;

средство генерирования данных режима обозначения для генерирования данных режима назначения, используемых для определения режима обозначения размера для каждого экрана монитора;

второе средство ЗУ для временного хранения данных обозначения объекта и позиционных данных в нем;

средство определения попадания в диапазон для вынесения решения, должен или нет объект визуализироваться на мониторе во время следующего периода горизонтального сканирования, основываясь на комбинации позиционных данных, считанных из второго средства ЗУ, данных выбора размера, подданных из средства генерирования данных о выборе размера, и данных режима обозначения, посланных на выход из средства генерирования данных режима обозначения, и

средство образования адреса считывания для образования адреса считывания для первого средства ЗУ в отношении объекта, подпадающего под решение об объекте, как находящийся в положении попадания в диапазон, с помощью средства определения попадания в диапазон, с тем чтобы подать образованный таким образом адрес считывания на первое средство ЗУ.

Когда второе изобретение применяется к внешнему ЗУ, внешнее ЗУ образуется со средством генерирования данных обозначения объекта, средством генерирования позиционных данных, средством генерирования данных о выборе размера и средством генерирования данных режима обозначения.

Согласно второму изобретению средство определения попадания в диапазон выносит решение, находится или нет соответствующий объект в положении попадания в диапазон, т.е. должен быть визуализирован с помощью следующей горизонтальной строки на основе размера объекта, определяемого с помощью данных обозначения размера, и данных выбора размера, и позиционных данных объекта на мониторе. Дополнительно средство образования адреса считывания образует адрес считывания на основе, например, данных обозначения объекта, позиционных данных, данных обозначения размера и данных выбора размера таким образом, чтобы считывать графические данные объекта, подпадающего под решение о попадании в диапазон из первого средства ЗУ.

Согласно также второму изобретению данные обозначения размера используются для обозначения множества видов размеров, и данные выбора размера используются для выбора и определения размера каждого объекта. Поэтому можно значительно сократить количество данных, используемых для определения размера объекта, по сравнению с традиционным примером. Соответственно не только емкость памяти ОАМ может быть значительно уменьшена, но и емкость памяти ЗУ программ может быть также уменьшена. Предположим теперь, что 128 объектов может быть визуализировано на одном экране как максимум, и предусмотрено шесть видов визуализируемых размеров, например. В этом случае 3-битовые данные обозначения размера и 1-битовые данные выбора размера могут быть установлены для каждого экрана и каждого объекта соответственно. Таким образом, данные на 131 битах (=128•1+3) могут использоваться, чтобы попеременно или регулируемо определять размеры объектов. Количество таких данных может быть около 1/5 (=131/768) по сравнению с техническим решением, описанным в японской патентной выложенной заявке N 62-24296.

Согласно одному отличительному признаку третьего изобретения предусматривается устройство дисплея подвижного изображения типа, в котором объект крупного размера может быть визуализирован на мониторе растрового типа путем объединения одного или больше символов, каждый содержащий множество точек в горизонтальном и вертикальном направлениях соответственно, которое (устройство дисплея подвижного изображения) включает в себя;

первое средство ЗУ для предварительной загрузки графических данных о символах, составляющих объект, в соответствующий адресный район для каждого объекта;

средство генерирования данных обозначения объекта для генерирования данных обозначения объекта, используемых для обозначения по крайней мере одного объекта, подлежащего визуализации на мониторе, во время следующего периода вертикального сканирования на мониторе;

средство генерирования позиционных данных для генерирования позиционных данных, используемых для представления позиций обозначенного объекта на мониторе, на котором обозначенный объект должен визуализироваться;

средство генерирования данных определения размера для генерирования данных определения размера, используемых для вынесения решения о размере объекта8

второе средство ЗУ для временного хранения данных обозначения объекта и позиционных данных в нем;

средство определения попадания в диапазон для вынесения решения, должен или нет объект быть визуализирован на мониторе во время следующего периода горизонтального сканирования, на основе позиционных данных, считанных из второго средства ЗУ, и данных определения размера, поданных из средства генерирования данных определения размера;

средство для считывания графических данных из первого средства ЗУ в отношении объекта, подпадающего под решение об объекте как находящемся в положении попадания в диапазон, с помощью средства определения попадания в диапазон;

средство определения попадания за диапазон для вынесения решения, находится или нет часть объекта, подпадающего под определение объекта, как находящегося в положении попадания в диапазон с помощью средства определения попадания в диапазон, за диапазоном экрана на мониторе, и

средство предотвращения считывания для предотвращения считывания из первого средства ЗУ графических данных о части объекта, подпадающего под решение об объекте, находящемся за экраном, с помощью средства определения попадания в диапазон.

Согласно третьему изобретению, графические данные объекта, подпадающего под решение о нем, как находящемся в положении попадания в диапазон в горизонтальном и вертикальном направлениях с помощью средства определения попадания в диапазон, считываются из первого средства ЗУ. С другой стороны, когда объект представлен размером объекта, определяемым на основе данных определения размера объекта, средство определения выхода за диапазон, такое как схема управления счетчика размера, выносит решение, лежит или нет часть объекта за левой кромкой и/или правой кромкой в горизонтальном направлении на экране монитора, на основе позиционных данных в горизонтальном направлении и учитывая размер объекта. Если определено, что часть объекта лежит за левой кромкой, тогда средство предотвращения считывания возбуждается для предварительной установки адреса для образования начала при считывании графических данных объекта в адрес графических данных для фактически визуализируемых символов, тем самым предотвращая считывание неэффективных графических данных. Если определено, что часть объекта лежит за правой кромкой, тогда на выход подается сигнал. В ответ на этот сигнал средство предотвращения тогда предотвращает считывание графических данных из первого средства ЗУ. Конкретно, данные обозначения следующего объекта блокируются в регистре, используемом для хранения в нем данных обозначения объекта, тем самым приступая к процессу в отношении следующего объекта.

Согласно также третьему изобретению, когда часть объекта лежит за экраном монитора, считывание графических данных относительно такой части из первого средства ЗУ запрещается. Поэтому процесс неэффективен данных относительно части объекта, которая находится за обеими кромками экрана монитора, как сказано выше, не исполняется. Поэтому реально устранение значительного снижения числа объектов и одновременно надежно снижается нагрузка на процессор, используемый для обработки подвижных изображений, тем самым создавая возможность более быстрой скорости обработки в целом.

Вышеприведенные и другие цели, отличительные признаки и преимущества настоящего изобретения станут видны из нижеследующего подробного описания и приложенной формулы изобретения, взятые совместно с прилагаемыми чертежами, в которых показан предпочтительный вариант реализации настоящего изобретения в качестве иллюстративного примера.

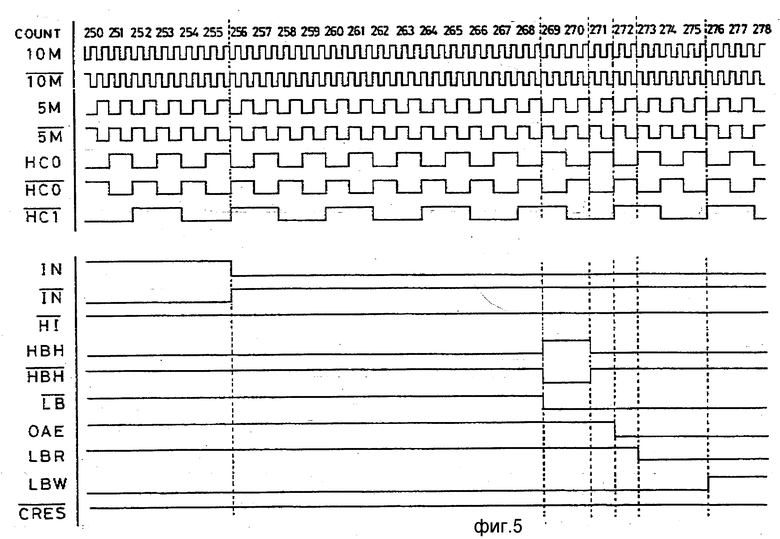

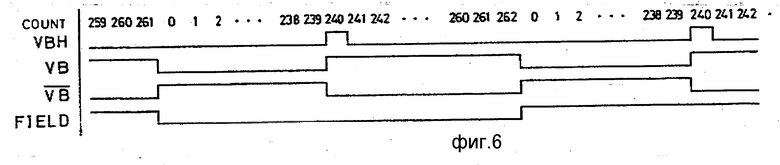

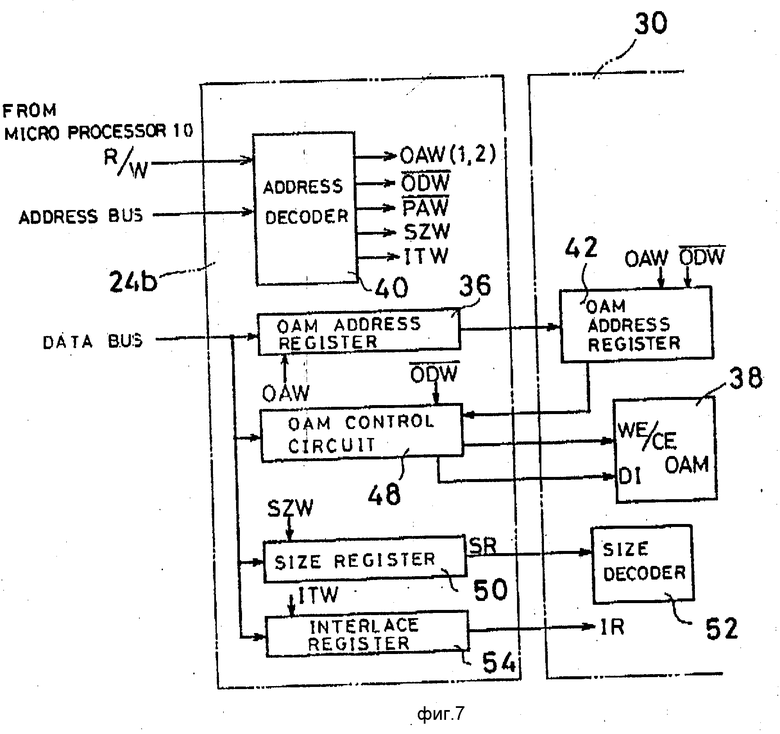

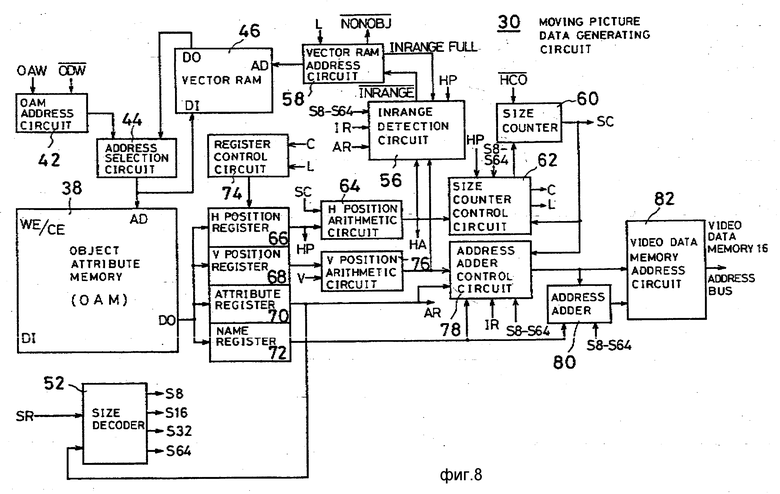

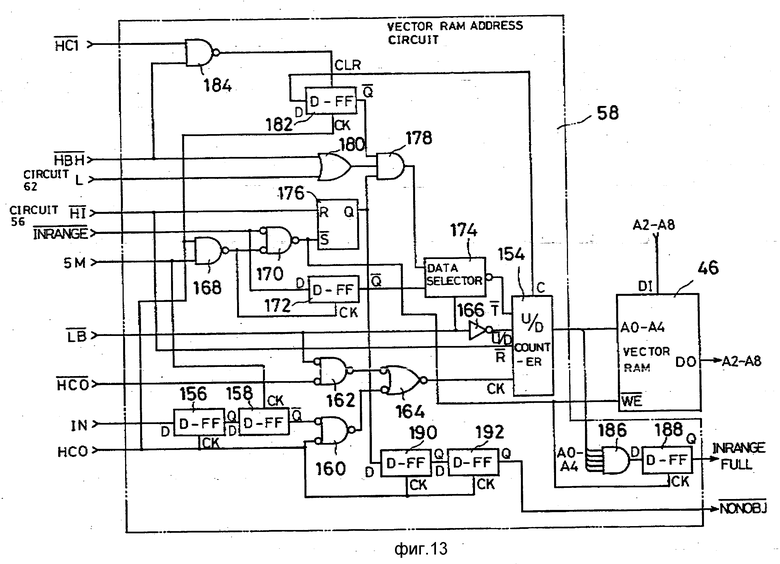

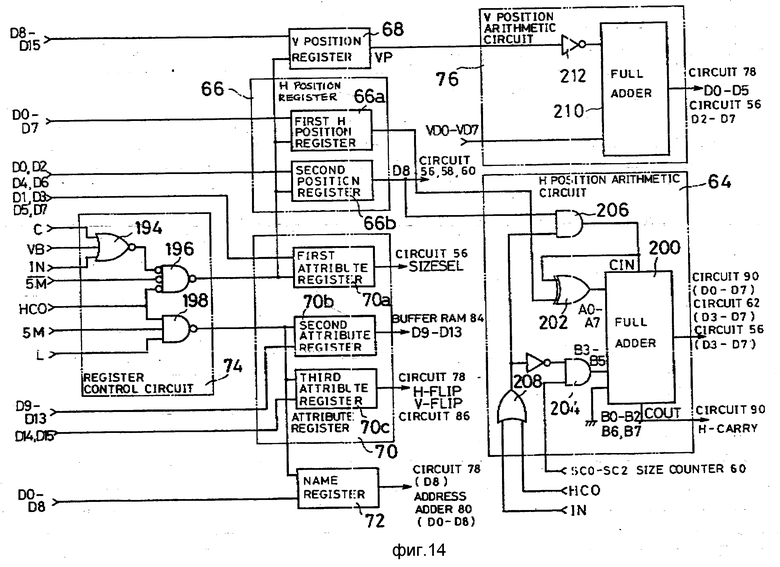

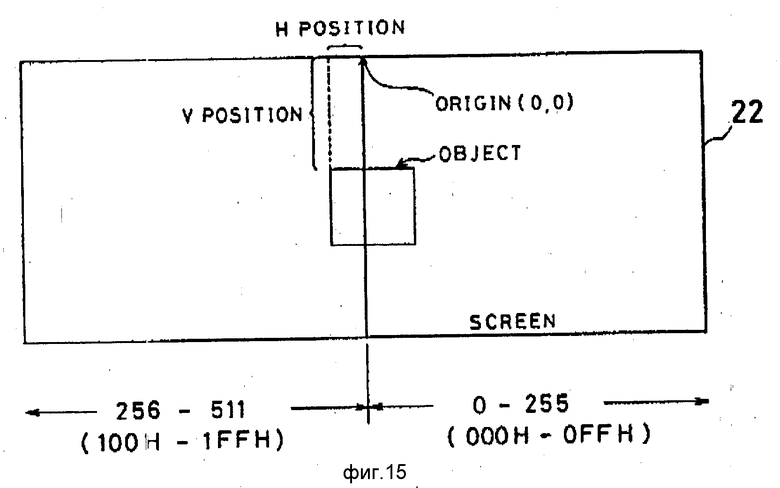

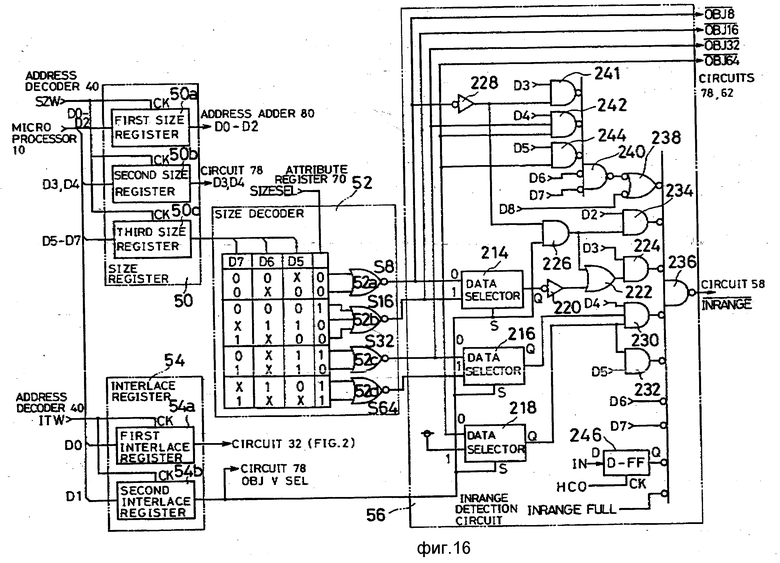

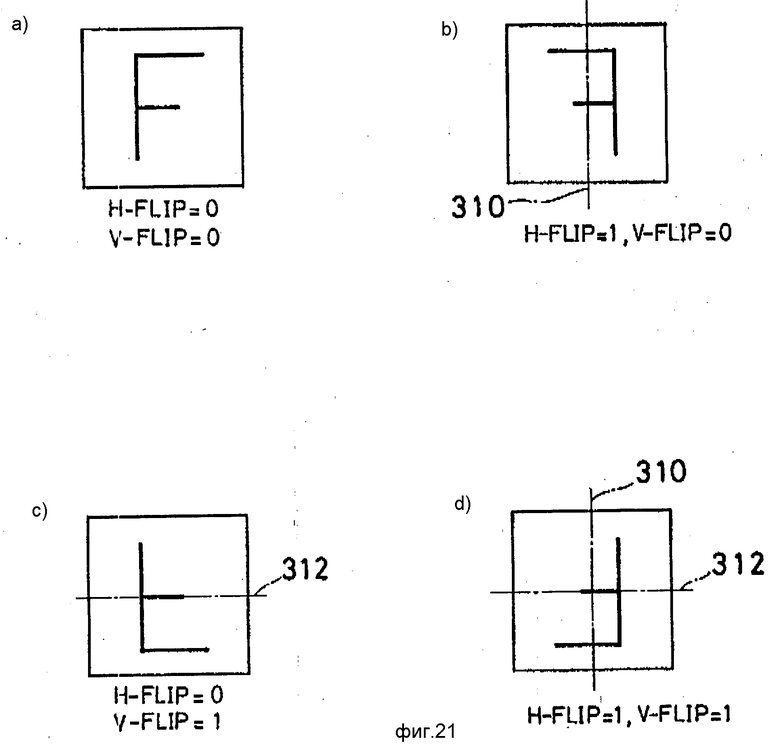

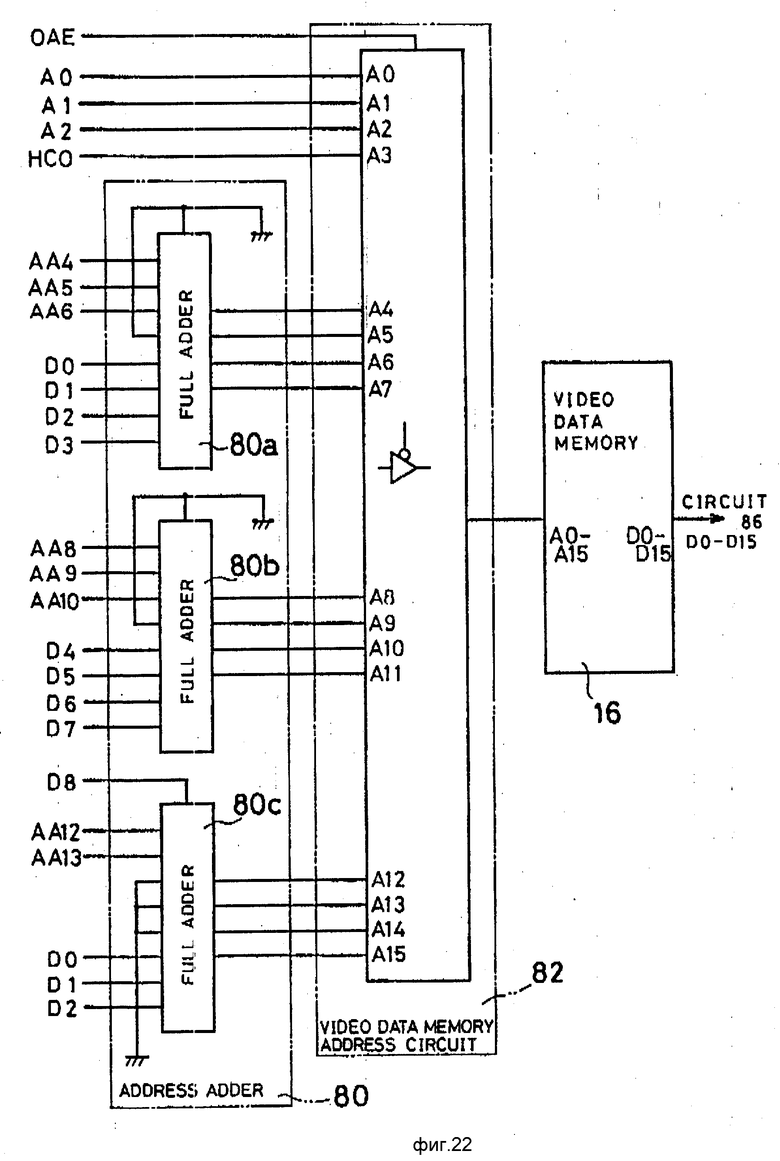

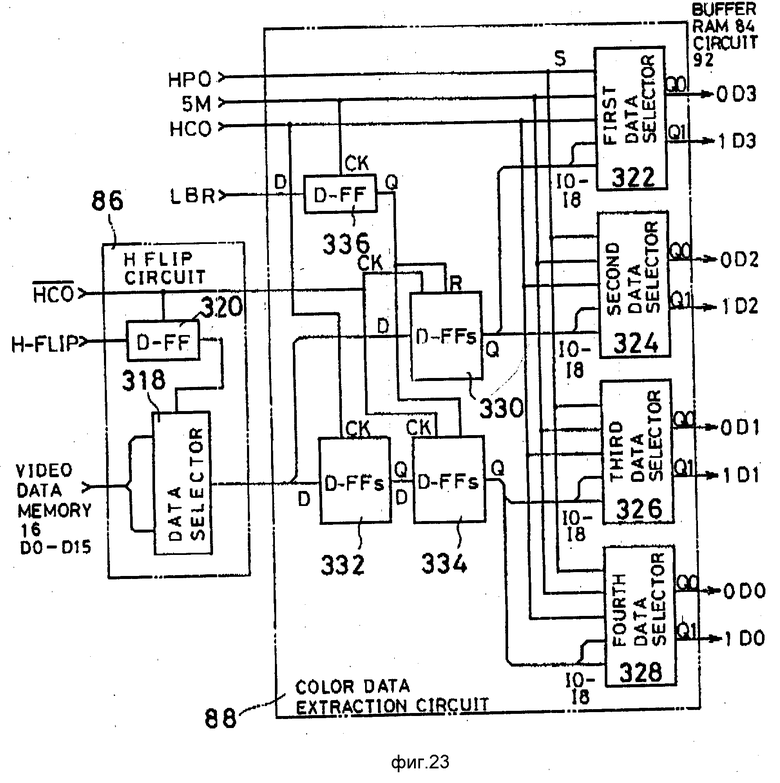

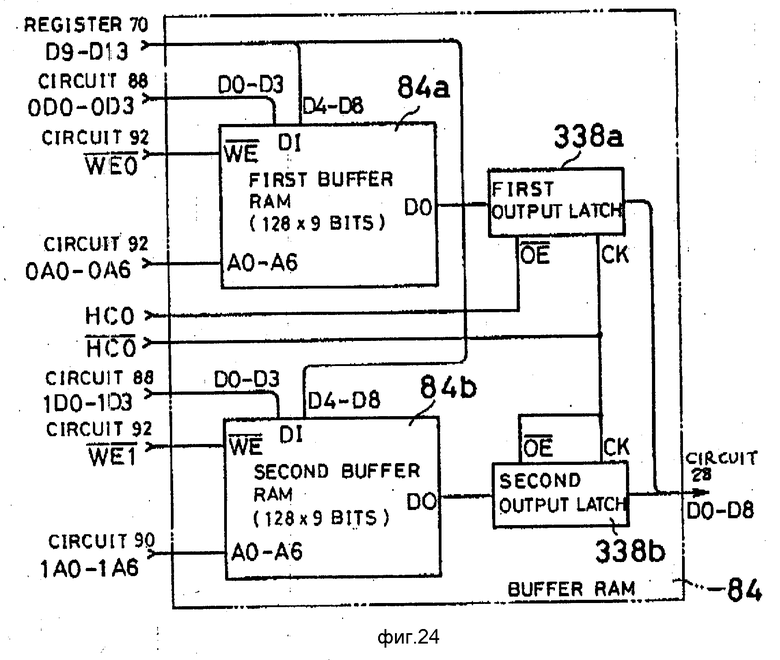

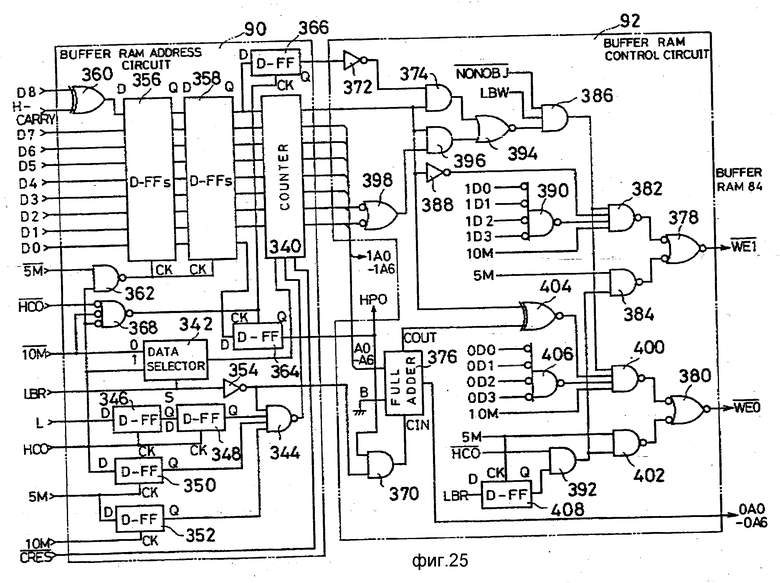

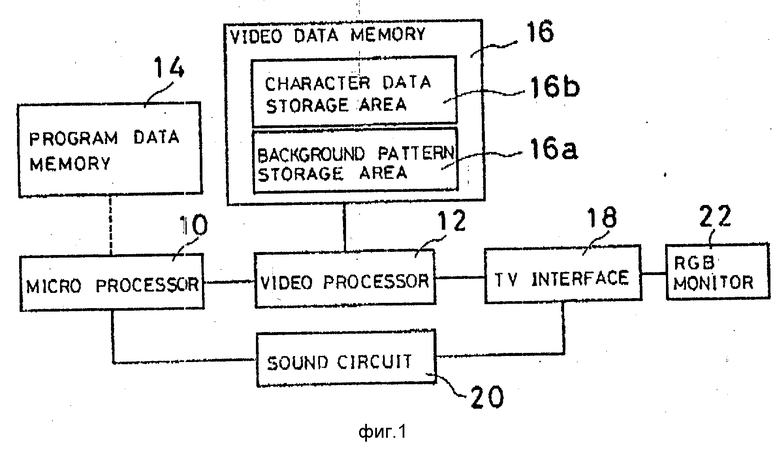

На фиг. 1 изображена блок-схема, показывающая один вариант реализации настоящего изобретения; на фиг. 2 блок-схема, показывающая видеопроцессор, используемый в варианте реализации, показанном на фиг. 1; на фиг. 3 - блок-схема, показывающая схему генерирования сигнала синхронизации; на фиг. 4 и 5 графики синхронизации для описания соответствующих синхронизирующих сигналов в горизонтальном направлении; на фиг. 6 график синхронизации для описания соответствующих синхросигналов в вертикальном направлении; на фиг. 7, 8 и 9 блок-схемы, каждая показывающая схему генерирования данных оживления изображения, показанной на фиг. 2; на фиг. 10 схема для описания одного примера данных объекта; на фиг. 11 блок-схема, показывающая схему адресов ОАМ подробно; на фиг. 12 блок-схема, показывающая схему выбора адреса, схему управления ОАМ и ОАМ подробно; на фиг. 13 блок-схема, показывающая схему адреса векторного RAM и векторное RAM подробно; на фиг. 14 блок-схема, показывающая подробно схему управления регистром, регистр H-позиции, регистр V-позиции, регистр признака, регистр имени/названия, арифметическую схему H-позиции и арифметическую схему V-позиции; на фиг. 15 схема для описания горизонтальной (H) позиции и вертикальной (V) позиции, указывающих на объект на экране монитора; на фиг. 16 блок-схема, показывающая подробно регистр размера, регистр чередования, декодер размера и схему определения попадания в диапазон; на фиг. 17 и 18 схемы, каждая показывающая один пример формата ЗУ в ЗУ видеоданных; на фиг. 19 блок-схема, показывающая схему управления счетчиком размера подробно; на фиг. 20 блок-схема, показывающая схему управления сумматором адресов подробно; на фиг. 21 (a-d) схемы, каждая показывающая состояние H-перескока и состояние V-перескока; на фиг. 22 - блок-схема показывающая подробно сумматор адресов, схему адресов/ЗУ видеоданных и ЗУ видеоданных; на фиг. 23 блок-схема, показывающая схему H инверсии и схему извлечения данных о цвете подробно; на фиг. 24 блок-схема, показывающая подробно буферное RAM; на фиг. 25 блок-схема, показывающая схему адресов буферного RAM и схему управления буферных RAM подробно.

Наилучший вариант реализации изобретения. Общая конструкция.

Обращаясь к фиг. 1, микропроцессор 10 служит для управления всей операцией/функционированием устройства дисплея подвижных изображений, таким как видеопроцессор 12, и т.д. в соответствии с данными программы, посылаемыми из ЗУ 14 данных программы, которое включено, как пример, в загружаемую и разгружаемую кассету ЗУ. В качестве микропроцессора 10 используется 16-битовый микропроцессор, такой как IC "RF5A22", производства РИКОХ КО.ЛТД. Видеопроцессор 12 считывает графические данные из ЗУ 16 видеоданных в ответ на команду или инструкцию от микропроцессора 10, и затем посылает считанные таким образом данные на телевизионный интерфейс 18. ЗУ 16 видеоданных содержит SRAM (Статическое ЗУ произвольной выборки), например, емкостью 64 килобайтов, т. е. включает в себя зону хранения 16а фонового изображения и зону хранения данных о символах 16b. Иначе говоря, зона хранения 16a фонового изображения и зона хранения 16b данных о символах образованы одним SRAM. Причина для такого выполнения конструкции в том, что операционная скорость быстрая, и емкость каждой зоны хранения может произвольно устанавливаться посредством символа (объекта) и фонового изображения. Дополнительно звуковая схема 20 генерирует данные, указывающие необходимую музыку и эффективный звук в цифровой форме в соответствии с командой, выданной микропроцессором 10, для подачи на телевизионный интерфейс 18. Телевизионный интерфейс 18 преобразует графические данные, полученные от видеопроцессора 12, в сигнал RGB (КЗС-красный, зеленый, синий прим. переводч.) и затем посылает его на видеосхему монитора RGB 22. Дополнительно телевизионный интерфейс 18 преобразует звуковые данные, генерируемые звуковой схемой 20, в звуковой сигнал для подачи на звуковую схему в мониторе RGB 22. Например, интегральная схема "CXD 12220", производства фирмы СОНИ КОРП. возможна в качестве звуковой схемы 20. Таким образом, такой объект, как видеоигра, и фоновое изображение, которые изменяются в соответствии с прогрессом программ, предварительно установленных в ЗУ 14 данных о программах, визуализируется на экране монитора RGB 22.

Вариант реализации, показанный на фиг. 1, представляет случай, когда телевизионный интерфейс 18 преобразует графические данные в RGB-сигнал. Однако настоящий вариант реализации может альтернативно использовать телевизионный интерфейс, который преобразует графические данные в телевизионный видеосигнал. В этом случае в качестве монитора может использоваться домашний телевизор, который широко доступен.

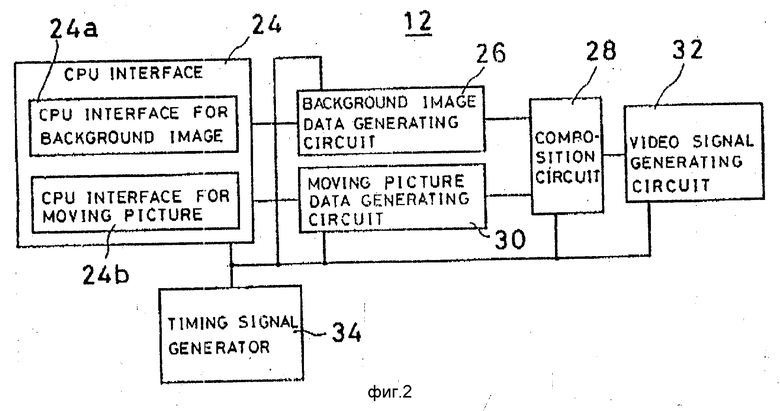

На фиг. 2 представлена блок-схема, показывающая подробно видеопроцессор 12 в варианте реализации, показанном на фиг. 1. Видеопроцессор 12 включает в себя интерфейс 24 центрального процессора, имеющий фиксатор (защелку) данных для фиксирования данных от микропроцессора 10 в нем, и декодер адресов или тому подобное. Интерфейс 24 ЦП включает в себя интерфейс 24а ЦП для обработки фонового изображения и интерфейс 24b ЦП для обработки оживления (объекта). Интерфейс 24а ЦП возбуждается таким образом, чтобы сделать возможным осуществление передачи данных относительно фонового изображения между микропроцессором 10 и видеопроцессором 12. С другой стороны, интерфейс 24b ЦП возбуждается для создания возможности передачи данных относительно объекта между микропроцессором 10 и видеопроцессором 12.

Затем схема генерирования данных фонового изображения 26 считывает данные образца (код символа), представляющих фоновое изображение из зоны 16а хранения фонового изображения ЗУ 16 видеоданных в ответ на данные программы, поданные на выход из микропроцессора 10 через интерфейс 14а ЦП. После этого схема 26 генерирования данных о фоновом изображении считывает графические данные, указывающие фоновое изображение, из зоны 16b хранения данных символа ЗУ 16 видеоданных на основе данных образца, считанных таким образом, и затем посылает считанные таким образом графические данные на схему 28 синтезатора. С другой стороны схема генерирования данных оживленного или подвижного изображения 30, к которой относится настоящее изобретение, будет описываться более подробно ниже. Однако схема 30 генерирования данных оживления изображения считывает графические данные, указывающие объект из зоны 16b хранения данных символов ЗУ 16 видеоданных, на основе данных программы, генерированных микропроцессором 10, и посылает считанные таким образом данные на синтезатор 28.

Как будет описано ниже, схема 28 синтезатора определяет или принуждает уровень приоритета в отношении того, должен ли либо объект, либо фоновое изображение быть указано, когда объект и фоновое изображение накладываются друг на друга. Поэтому, если объекту придан наивысший приоритет, тогда он визуализируется на экране. Однако фоновое изображение, которое накладывается на объект, не визуализируется на нем. Если фоновое изображение получило наивысший приоритет, тогда оно визуализируется на экране, но объект, который накладывается на фоновое изображение, не визуализируется на нем. Таким образом, графические данные, синтезированные схемой 28 синтезатора, подаются на схему 32 генерирования сигнала изображения. Схема 32 генерирования сигнала изображения имеет цветовой кодер для образования RGB-сигнала в соответствии с кодом цвета на точку (элемент изображения), поданный на выход со схемы 28 синтезатора. RGB-сигнал, образуемый кодером цвета, посылается на монитор 32, как описано выше.

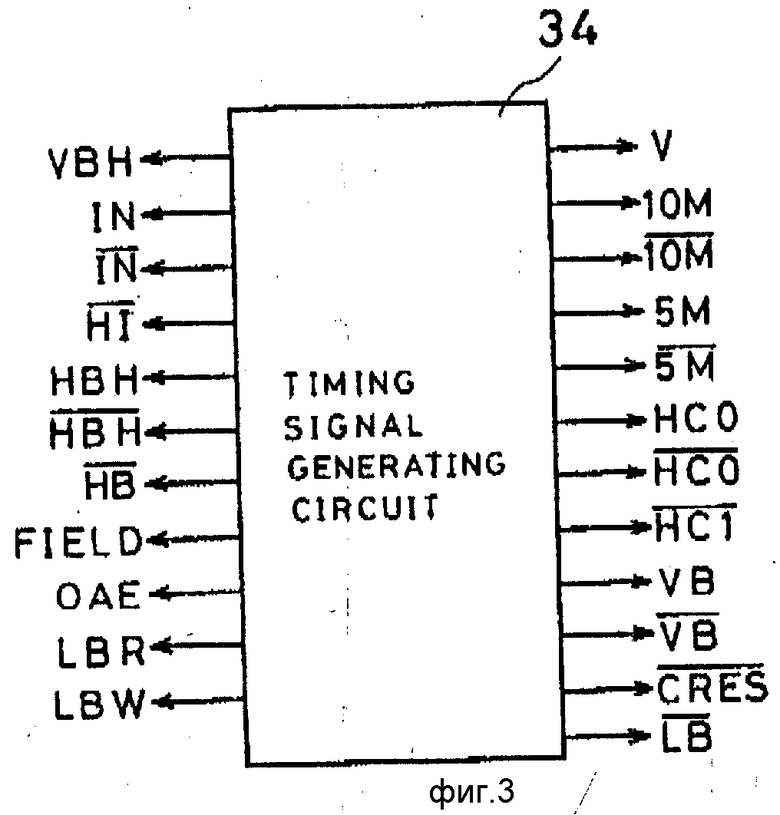

Затем схема 34 генерирования сигнала синхронизации принимает основной синхросигнал 21,47727 МГц, показанный на фиг. 4 и 5, для электрической обработки путем использования, например, счетчика, декодера, логической схемы и т.д. чтобы тем самым генерировать некоторое число синхронизирующих сигналов, показанных на фиг. 3 и фиг. 4 и 5. После этого схема 34 генерирования синхронизирующего сигнала служит для подачи этих синхросигналов на интерфейс 24 ЦП, схему 26 генерирования данных фонового изображения, схему 28 синтезатора, схему 30 генерирования данных оживления изображения, схему 32 генерирования сигнала изображения и т.д.

Покажем более конкретно: когда основной синхронизирующий импульс на частоте деленной на 1/2, получаем синхронизирующий сигнал либо 10М, либо /10М ("/" есть просто обратное 10М в настоящем описании). Когда такой синхросигнал является далее частотой, деленной на 1/2, получаем синхросигнал либо 5М, либо /5М.

Период, необходимый для визуализации 1 точки (элемента изображения) на экране RGB-монитора 22 (см. фиг.1), соответствует одному полному циклу синхронизирующего сигнала 5М. Таким образом, время "0-341" как отсчетная величина синхросигнала 5М, является горизонтальным периодом. Время "0-268" как отсчетная величина синхросигнала 5М в течение такого горизонтального периода, соответствует одному периоду дисплея или визуализации горизонтальной строки, тогда как время "269-341", как отсчетная величина его, эквивалентно периоду горизонтального запирания. Вертикальный сигнал V (см. фиг. 3) образуется для каждого горизонтального периода, т.е. каждый раз отсчетная величина синхросигнала 5М составляет "0-341", и после этого отсчитывается в вертикальном положении при сканировании, т.е. номер строки. Если одно поле в момент чередующегося сканирования составляет 262 горизонтальных строки, как показано на фиг. 6, тогда получаем поле (FIELD) синхросигнала в течение интервала, в который отсчетная величина вертикального сигнала V составляет "0-262". Период, в каком поле сигнала имеет высокий уровень, соответствует одному вертикальному периоду, и "0-239" как отсчетная величина сигнала V эквивалентно периоду вертикальной визуализации. Дополнительно, "240-262" как отсчетная величина сигнала V, соответствует периоду вертикального запирания.

Как показано на фиг. 6, синхросигнал VBH подается на выход во время интервала, в каком отсчетная величина вертикального сигнала составляет "240", и показывает начало периода вертикального запирания. Синхросигнал VB делается высоким по уровню во время периода вертикального запирания, и синхросигнал /VB делается высоким по уровню во время периода вертикальной визуализации.

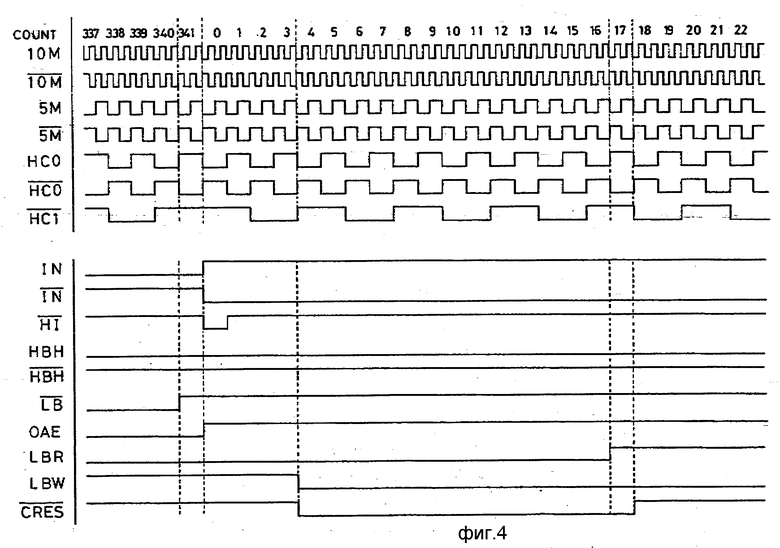

Синхросигнал HCO, показанный на фиг. 4 и 5, получают в результате деления частоты вышеназванного сигнала 5М на 1/2, тогда как синхросигнал /HCO получают путем простого инвертирования сигнала HCO. Синхросигнал /HCI получают путем деления частоты сигнала /HCO на 1/2. Как показано на фиг. 4 и 5, синхросигнал IN есть сигнал, который приобретает высокий уровень, т.е. указывающим состояние объекта, обрабатываемого схемой определения попадания в диапазон во время периода горизонтальной визуализации, т.е. в течение интервала, в котором отсчетная величина сигнала 5М составляет "0-255". Дополнительно синхросигнал /IN является простым инвертированием синхросигнала IN. Синхросигнал /HI подается на выход для каждого горизонтального периода в течение интервала, в каком отсчетная величина сигнала 5М составляет "0". Как показано на фиг. 5, синхросигнал HBH подается на выход во время отсчетной величины сигнала 5М "269-270", и показывает начало периода горизонтального запирания. Дополнительно, синхросигнал /HBH является просто инвертированием сигнала HBH. Таким образом, синхросигнал /HBH становится высоким по уровню во время интервала, в котором отсчетная величина сигнала 5М составляет "272-268" (либо опечатка, либо отсчет по убывающей прим. переводч.). По случаю, синхросигнал /HB делается низким по уровню во время периода горизонтального запирания. Как показано на фиг. 4 и 5, синхросигнал /LB подается на выход как сигнал высокого уровня в течение интервала, в котором отсчетная величина сигнала 5М составляет "341-268", тогда как синхросигнал OAE подается на выход как сигнал высокого уровня в течение интервала, в котором отсчетная величина сигнала 5М составляет "0-271", как показано на фиг. 4 и 5. Как показано на фиг. 4 и 5, синхросигнал LBR подается на выход как сигнал высокого уровня в течение интервала, в котором отсчетная величина сигнала 5М составляет "17-272", тогда как синхросигнал LBW подается на выход как сигнал высокого уровня в течение интервала, в котором отсчетная величина сигнала 5М составляет "276-3". Далее, синхросигнал /CRES образуется как сигнал низкого уровня в течение интервала, в каком отсчетная величина сигнала 5М составляет "3-17", как показано на фиг. 4 и 5.

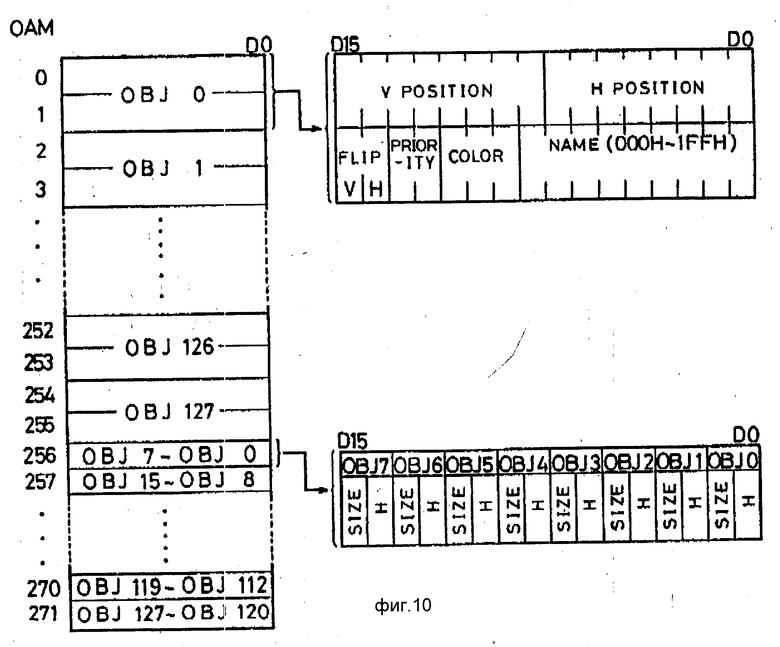

Как показано на фиг. 7, интерфейс 24b ЦП включает в себя 8-битовый регистр 36 адресов ОАМ, используемый для приема данных от шины данных микропроцессора 10. Регистр 36 адресов ОАМ принимает адрес от микропроцессора 10, когда данные записаны в ОАМ (ЗУ признаков объекта), включенное в схему 30 генерирования данных оживления изображения, с тем чтобы установить начальный адрес для ОАМ 38. ОАМ 38 имеет емкость памяти 34 битов х 128, т.е. 128х34 битов, например, и способно хранить соответствующие данные объектов в отношении 128 объектов. Как показано на фиг. 10, эти данные объектов соответственно образованы из 34 битов в целом. В качестве данных объекта в них входят 9-битовые данные обозначения объекта, (данные наименования), 8-битовые данные вертикальной позиции, 9-битовые данные горизонтальной позиции и 1-битовые данные выбора размера объекта, а также 3-битовые данные цветной палитры, 1-битовые данные горизонтального и вертикального перескока, и 2-битовые данные представления приоритета или им подобные.

Как хорошо известно, данные объекта, показанные на фиг. 10, заранее установлены в ЗУ 14 данных программы, содержащейся в вышеописанной кассете ЗУ, т.е. внешнего ЗУ, в соответствии с содержанием игр, например. Дополнительно, данные объекта, считанные из ЗУ 14 данных программы, подаются на ОАМ 38 микропроцессором 10.

Декодер 40 адресов принимает сигнал считывания/записи R/W от микропроцессора 10 и адрес с шины адресов с тем, чтобы генерировать соответствующие сигналы OAW, /ODW, RAW, SZW и ITW из них. Сигнал OAW подается на регистр 36 адресов ОАМ, как его сигнал записи. Регистр 36 адресов ОАМ загружается первоначальным адресом, поданным на выход от микропроцессора 10 в ответ на сигнал OAW.

Схема 42 адресов ОАМ, включенная в схему 30 генерирования данных оживления изображения, в основном включает в себя счетчик адресов и возбуждается сигналом OAW. Схема 42 адресов ОАМ принимает первоначальный адрес от регистра 36 адресов ОАМ с тем, чтобы приращивать их в унисон с синхронизацией сигнала /ODW, тем самым посылая данные адреса для адресов последовательного обозначения в ОАМ 38 на схему 44 выбора адреса (см. фиг. 8). Схема 44 выбора адреса также принимает данные адреса от векторного RAM 46. Векторное RAM 46 хранит в себе адрес объекта, в отношении которого вынесено решение схемой 56 определения попадания в диапазон, что он в положении попадания в диапазон, как будет описано ниже. Схема 44 выбора адреса выбирает либо данные адреса, полученные от схемы 42 адресов ОАМ, либо данные адреса, полученные от векторного RAM 46, с тем чтобы послать результат выбора на ОАМ 38.

Сигнал /ODW от декодера 40 адресов посылается на схему 48 управления ОАМ как сигнал ее возбуждения. Схема 48 управления ОАМ подает на выход сигнал записи WE и данные для подачи на ОАМ 38, когда схема 48 управления ОАМ записывает данные от микропроцессора 10 в ОАМ 38.

Регистр 50 размеров является 3-битовым регистром и загружается любой одной из величин данных размера "000-101", приведенных в табл. 1, показанной ниже, которые представлены в форме 3-битовой индикации данных от D5 до D7, подаваемых от микропроцессора 10. Конкретно, когда сигналы адреса, данных и записи в отношении указания (спецификации) регистру 50 размеров поданы от микропроцессора 10, декодер 40 адресов подает на выход сигнал SZW. Регистр 50 размеров загружается данными размера в ответ на сигнал SZW. Данные размера из регистра 50 размеров подаются на декодер 52 размеров в схеме 30 генерирования данных оживления изображения. Декодер 52 размеров служит для декодирования посланных таким образом данных размера с тем, чтобы генерировать каждый из сигналов S8, S16, S32 и S64, указывающими на размеры объекта, которые (размеры) отличаются друг от друга.

Дополнительно, 2-битовый регистр 54 чередования принимает 1-битовые данные чередования, указывающие либо на чередование, либо на нечередование, данные OBJV SEL, которые определяют, будет ли 1 точка представлена (визуализирована) 1 строкой или 2 строками в момент чередования, от микропроцессора 10. Более конкретно, когда сигналы адреса, данных и записи в отношении выдачи указаний (спецификации) регистру 54 чередования переданы от микропроцессора 10, декодер 40 адресов подает на выход сигнал ITW. Затем регистр 54 чередования реагирует на сигнал ITW с тем, чтобы быть загруженным данными чередованиия и данными OBJV SEL.

В показанном варианте реализации может быть представлено или визуализировано 32 объекта с помощью одной строки максимум. Поэтому необходимо определить, какой объект из 128 объектов, способных быть визуализированными на одном экране, должен быть представлен следующей строкой. Для этого используются схема 56 определения попадания в диапазон и векторное RAM 46, показанные на фиг. 8. Таким образом, векторное RAM 46 имеет емкость памяти 7 бит х 32, т.е. 32х7 бит для указания количеств (номеров) объектов.

Схема 58 адресов векторного RAM главным образом включает в себя счетчик, и производит приращение адреса для векторного RAM 46 каждый раз, когда подается сигнал /INRANGE (ПОПАДАНИЯ В ДИАПАЗОН) от схемы 56 определения попадания в диапазон. По случаю, когда объекты, оказывающиеся в положении попадания в диапазон, не присутствуют в горизонтальной строке, схема 58 адресов векторного RAM посылает сигнал /NONOBJ (НЕТ ОБЪЕКТА), указывающий на его отсутствие, на схему 92 управления буферным RAM (см. фиг. 9), о чем будет сказано ниже. Как описано выше, 1 строка может визуализировать только 32 объекта максимум. Поэтому когда число объектов, оказывающихся в положении попадания в диапазон, достигает 32, схема 58 адресов векторного RAM посылает на выход сигнал INRANGE FULL (ПОПАДАНИЕ В ДИАПАЗОН ЗАПОЛНЕНО), для подачи на схему 56 определения попадания в диапазон. Соответственно, схема 56 определения попадания в диапазон прекращает подачу последующего выходного сигнала определения попадания в диапазон на схему 58 адресов векторного RAM.

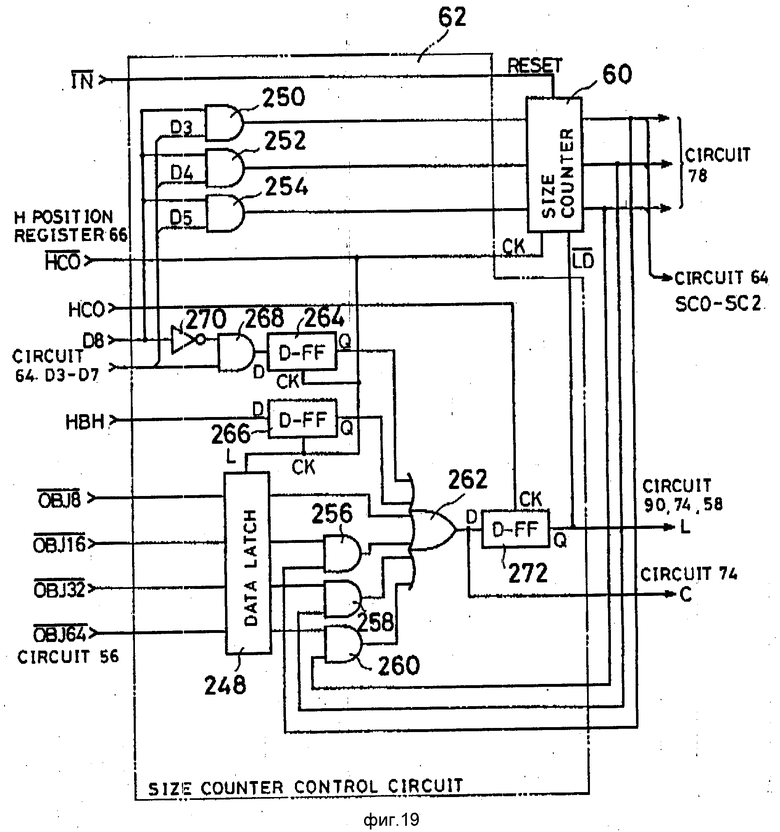

Счетчик 60 размера, показанный на фиг. 8, подает на выход данные SC, используемые для определения, какой символ из множества символов, составляющих объект, должен быть визуализирован при виде с левой стороны, когда необходимо представить объект. Счетчик 60 размера принимает данные исходной величины от схемы 62 управления счетчиком размеров, с тем, чтобы производить приращение исходной величины в ответ на сигнал /HCO, генерированный схемой 34 генерирования синхросигналов. Результат этого приращения подается на выход из счетчика 60 размеров, как вышеназванные данные SC, которые используются для вычисления адреса в арифметической схеме 64 горизонтального положения (здесь и далее сокращено "H"), о чем будет сказано ниже.

Схема 62 управления счетчиком размеров посылает на выход сигнал L, указывающий на синхронизацию в отношении загрузки данных горизонтального положения нового объекта, в схему 64 позиции H. Более конкретно, этот сигнал L является синхронизирующим сигналом для выполнения электрического процесса в отношении следующего объекта, и подается на схему 58 адресов векторного RAM. Схема 58 адресов векторного RAM реагирует на сигнал L с тем, чтобы производить приращение отрицательное (декремент) адреса векторного RAM. Таким образом, каждый адрес векторного RAM 46 изменяется при каждом сигнале L. Если сигнал L не был подан на выход из схемы 62 управления счетчиком размеров, функционирование для перевода каждого адреса в схеме 58 адресов векторного RAM в данные прекращается. Конкретно, когда используется большой объект, адрес в ОАМ 38, который должен использоваться, должен быть тем же самым, когда символы такого объекта электрически обрабатываются. Поэтому такой адрес в ОАМ 38 будет оставаться неизменным, пока все символы одного объекта не будут электрически обработаны в соответствии с сигналом L. По случаю, сигнал L может быть получен путем задержки сигнала C с D-FF, соответствующего первой стадии.

Как описано выше, данные о горизонтальной (H) позиции, данные о вертикальной (V) позиции, данные признака и данные наименования временно загружаются в ОАМ 38. Однако эти данные, считанные ОАМ 38, соответственно загружаются в 9-битовый регистр 66 H-позиции, 8-битовый регистр 68 V-позиции, 8-битовый регистр 70 признаков, и 9-битовый регистр 72 наименования соответственно под управлением схемы 74 управления регистром. Схема 74 управления регистром управляет синхронизацию загрузки каждого из регистров 66, 68, 70 и 72, в ответ на сигналы L и C от схемы 62 управления счетчиком размера.

Регистр 66 H-позиции посылает данные H-позиции HP на арифметическую схему 64 H-позиции. Дополнительно HP данные также посылаются на схему 62 управления счетчиком размера. Арифметическая схема 64 H-позиции выполняет арифметическую операцию по данным абсолютной величины НА, указывающих на горизонтальную (H) позицию объекта, и посылает полученные таким образом данные на схему 56 определения попадания в диапазон и схему 90 адресов буферного RAM, что описывается ниже, после чего данные используются как адрес буферного RAM 84. Арифметическая схема 64 H-позиции складывает данные, указывающие H-позицию, и данные SC из счетчика 60 размеров и посылает результат своего сложения на схему 62 управления счетчиком размеров.

Арифметическая схема 76 V-позиции принимает данные о вертикальной (V) позиции VP и сигнал V вертикального интервала и вычитает V-позицию объекта из позиции горизонтальной строки, которая сканируется в данный момент. Результат своего вычитания используется как данные для определения, должен или нет объект быть представлен следующей горизонтальной строкой. Результат вычитания подается на схему 56 определения попадания в диапазон и схему 78 управления сумматором адресов.

Схема 56 определения попадания в диапазон, которая описывается подробно ниже, определяет, должен или нет объект быть представлен или визуализирован следующей горизонтальной строкой, т.е. объект находится в положении попадания в диапазон на основе данных об H и V позициях, полученных таким образом, и данных о размере SR, данных чередования IR и данных признаков AR. Схема 56 определения попадания в диапазон производит определение в отношении того, находится или нет объект в положении попадания в диапазон 128 раз в течение одного периода горизонтального сканирования. Когда число объектов, находящихся в положении попадания в диапазон, достигает 32, как описано выше, схема 58 адресов векторного RAM посылает сигнал INRANGE FULL на схему 56 определения попадания в диапазон. Таким образом, схема 56 определения попадания в диапазон не посылает сигнал /INRANGE на схему 58 адресов векторного RAM после подачи на нее сигнала INRANGE FULL.

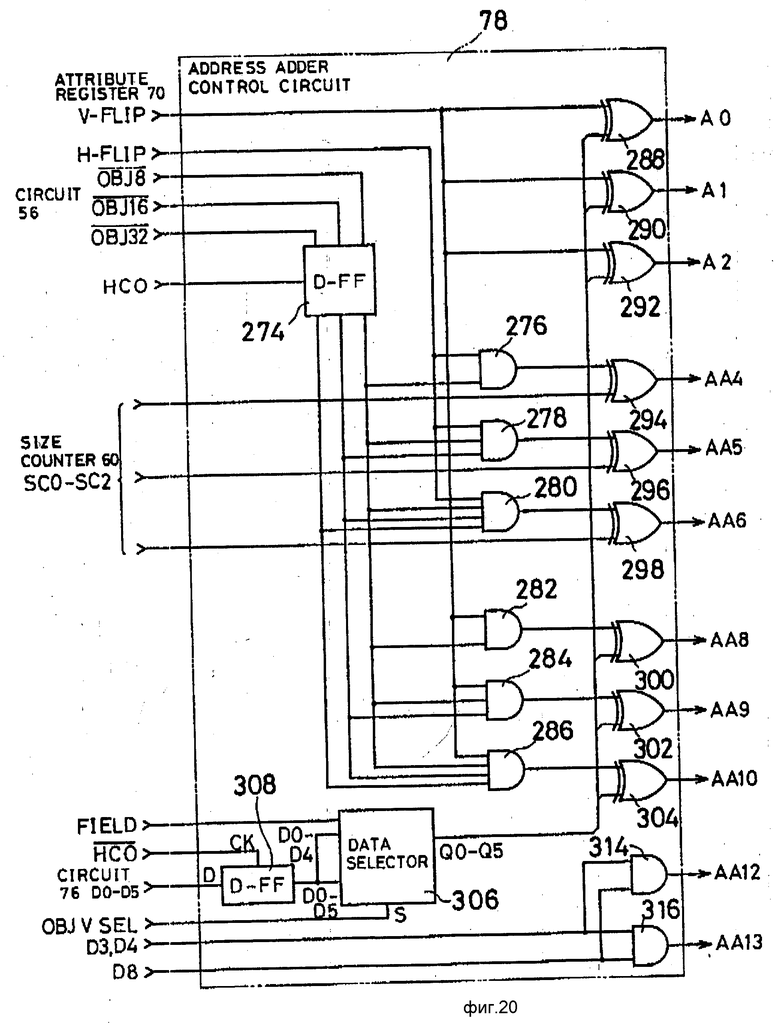

Схема 78 управления сумматором адресов обрабатывает поступающие данные, прежде чем сумматор 80 адресов произведет операцию сложения. Конкретно, схема 78 управления сумматором адресов принимает данные об H-позиции и данные об V-позиции, поступившие с арифметической схемы 64 H-позиции и арифметической схемы 76 V-позиции соответственно, а также принимает данные SR от регистра 50 размеров, данные IR от регистра 54 чередования и данные AR от регистра 70 признаков. Когда данные H-позиции представлены посредством H-переброса (обратное H), или данные V-позиции представлены посредством V-переброса (обратное V), схема 78 управления сумматором адресов изменяет величину, складываемую с другой величиной. Затем сумматор 80 адресов складывает вместе данные, поданные на выход от схемы 78 управления сумматором адресов, и данные кода объекта (которые соответствуют наименованию символа, т.е. опорный адрес помещается в верхнем положении при виде с левой стороны зоны 16а хранения данных символа ЗУ 16 видеоданных, показанного на фиг. 1), так чтобы создавать адрес для зоны 16а хранения данных символа. Таким образом, такой адрес подается на выход на схему 82 адреса/ЗУ видеоданных.

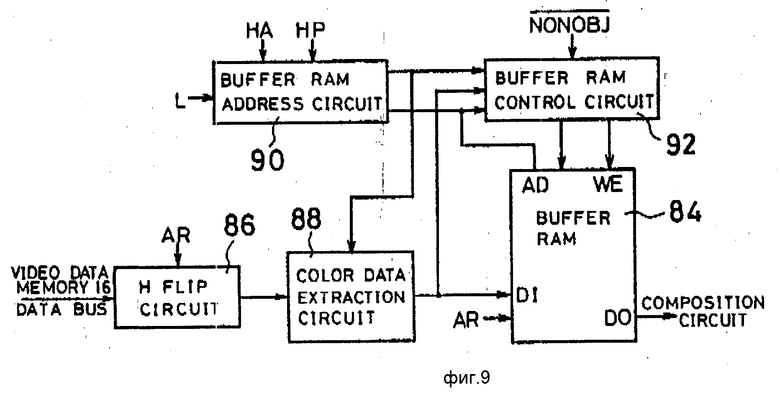

Буферное RAM 84, показанное на фиг. 9, имеет емкость памяти 256х9 бит, и временно хранит данные о палитре цвета, данные уровня приоритета и т.д. Схема 86 инвертирования H, которая электрически соединена с шиной данных, используемой для ЗУ 16 видеоданных, принимает данные цвета соответствующих точек (элементов изображения), считанных из зоны 16b хранения данных символа, с тем, чтобы инвертировать горизонтальное (H) направления для каждой точки на основе команды инвертирования, представленной данными AR, полученными от регистра 70 признаков. После этого схема 86 инвертирования H посылает данные цвета на схему 88 выделения данных цвета. Схема 88 выделения данных цвета собирает данные цвета, введенные в каждую из четырех цветовых ячеек для получения 4-битовых цветовых данных на точку, которые передаются на вход данных D1 буферного RAM 84. С другой стороны, так как данные цветовой палитры (3 бита) и данные уровня приоритета (2 бита) от регистра 70 признаков также подаются на буферное RAM 84, буферное RAM 84 хранит у себя 9-битовые данные на точку, как описано выше.

Схема 90 адресов буферного RAM принимает данные абсолютной величины HA адреса H от арифметической схемы 64 позиции H, и данные HP от регистра 66 H-позиции. Затем схема 90 адресов буферного RAM производит приращение адреса, подаваемое на выход от буферного RAM 84 до "0-255" в течение дисплейного периода (т.е. периода визуализации) и посылает таким образом приращенный адрес на буферное RAM 84. Таким образом, буферное RAM 84 считывает цветовые данные или им подобные в последовательности точек. Когда произведена запись данных в буферное RAM 84, схема 90 адресов буферного RAM создает адрес записи для буферного RAM 84 на основе данных абсолютной величины HA. Однако считывание или запись данных из и в буферное RAM 84 управляется схемой 92 управления буферным RAM. Более конкретно, схема 92 управления буферным RAM принимает сигнал /NONOBJ, генерированный схемой 59 адресов векторного RAM (см. фиг. 8), с тем, чтобы запретить запись данных в буферное RAM 84. Когда данные цвета указывают "прозрачность", схема 92 управления буферных RAM также запрещает запись данных в буферное RAM 84.

Теперь будет приведено подробное описание вышеизложенных соответствующих схем со ссылкой на фиг. с 11 до 24.

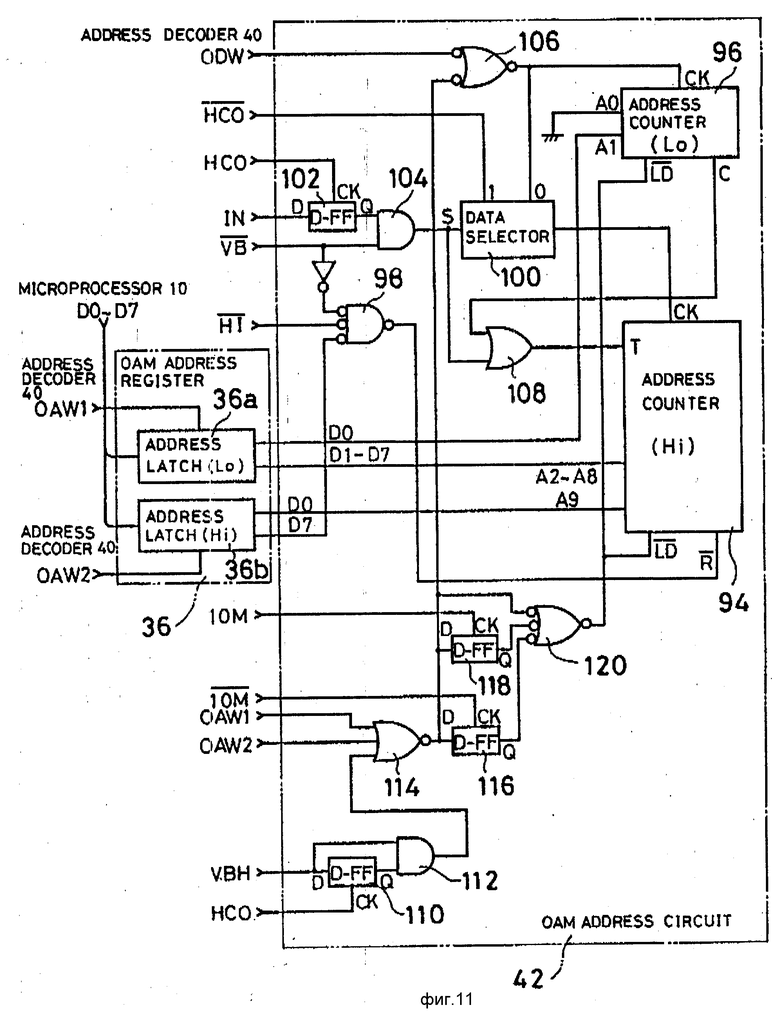

Схема 42 адресов ОАМ, показанная на фиг. 11, включает в себя счетчик 8-битовых адресов (Hi) 94 и счетчик 2-битовых адресов (Lo) 96. Счетчик адресов 94 принимает адресные входные сигналы с A2 по A8 от адресного фиксатора (Lo) 36а регистра 36 адресов ОАМ и адресный входной сигнал A9 от адресного фиксатора (Hi) 36b. Счетчик адресов 96 принимает адресный входной сигнал A1 от адресного фиксатора 36а. Адрес A1 используется для определения любого одного из 2 слов объекта, тогда как адреса с A2 по A8 используются для определения любого одного из 128 объектов. Логический элемент 98 НЕ И принимает выход D7 данных, поступающих от адресного фиксатора 36b, вместе с сигналами /HI и /VB (т.е. инвертирование VB), поступающие от схемы 34 генерирования сигналов синхронизации. Таким образом, выход D7 данных подается через логический элемент 96 НЕ И на вход R установления в исходное положение адресного счетчика 94. Когда D7 данных становится низким по уровню, адресный счетчик 94 устанавливается в исходное положение и начинает отсчет от нуля каждый раз, чтобы иметь возможность приращений. Как следствие, когда необходимо вынести решение, находится или нет объект в положении попадания в диапазон, объект, который прежде всего был считан и затем определен попадающий в диапазон, обрабатывается как при наличии наивысшего приоритера. Когда D7 данных составляет "1", адресный счетчик 94 не находится в исходном положении, данные, которые в конечном счете были введены из микропроцессора 10 (см. фиг. 1), устанавливаются как данные исходной величины, как она есть. Таким образом, объект, обозначенный такими данными исходной величины, получает наивысший приоритет.

Селектор 100 данных, который принимает сигнал /HCO, поступающий от схемы 34 генерирования синхросигнала, селективно посылает на адресный счетчик 94 синхроимпульсы, частоты которых отличаются друг от друга в течение периода вертикального запирания и другого периода, который не является периодом вертикального запирания. Более конкретно, так как выход D=FF 102, принимающий сигнал IN, посылаемый со схемы 34 генерирования синхросигнала, как входные данные, и сигнал HCO, посылаемый от схемы 34 генерирования синхросигнала, как синхроимпульс, посылается на вход логического элемента 104 И, и сигнал /VB, поступающий от схемы 34 генерирования синхросигнала, вводится в логический элемент 104 И, и логический элемент 104 И генерирует сигнал, который становится низким по уровню во время периода вертикального запирания. Селектор 100 данных реагирует на сигнал низкого уровня с тем, чтобы вносить решение, подан ли синхроимпульс, синхронизированный с сигналом /HCO, поступившим от схемы 34 генерирования синхросигнала, на синхронизатор адресного счетчика 94 или синхронизатор, синхронизированный с выборкой синхросигнала из микропроцессора 10, т.е. сигнала OAW от адресного декодера 40 (см. фиг. 7). Таким образом, адресный счетчик 94 принимает синхроимпульс, который синхронизирован с синхросигналом, при котором микропроцессор 10 приобретает доступ к адресному счетчику 94 в течение периода вертикального запирания, тогда как адресный счетчик 94 принимает синхроимпульс, синхронизированный с внутренним синхросигналом, в течение иного периода, нежели период вертикального запирания.

Выход логического элемента 104 И подается через логический элемент 108 ИЛИ на адресный счетчик 94, как возбуждающий входной сигнал Т его вместе с сигналом переноса C, подаваемого на выход от адресного счетчика 96.

Сигнал VBH, поступающий от схемы 34 генерирования сигнала синхронизации, подается на D-FF 110, как входные данные его, тогда как сигнал HCO от схемы 34 генерирования сигнала синхронизации подается на D-FF 110 как входной синхроимпульс его. Сигнал VBH также подается на выход D-FF 110 и логический элемент 112 И. Таким образом, выход логического элемента 112 И становится высоким (по уровню) при синхронизации сигнала HCO. Дополнительно выход логического элемента 112 И подается через логический элемент 114 НЕ-ИЛИ на вход данных каждого D-FF 116 и 118 вместе с сигналами OAW1 и OAW2, образованными адресным декодером 40. Сигнал /10М, поступающий от схемы 34 генерирования синхросигнала, подается на D-FF 116 как синхроимпульс его, тогда как сигнал 10М, поступающий от схемы 34 генерирования синхроимпульса, подается на D-FF 118 как синхроимпульс его. Выходы D-FF 116 и 118 подаются на вход логического элемента 120 НЕ-ИЛИ вместе с выходным сигналом логического элемента 114 НЕ-ИЛИ. Таким образом, логический элемент 120 НЕ-ИЛИ подает на выход числовые данные эквивалентные адресу на шину данных, когда микропроцессор 10 устанавливает каждый адрес ОАМ 38. Однако синхросигнал LD для загрузки числовых данных в адресный счетчик 94 подается на адресный счетчик 94.

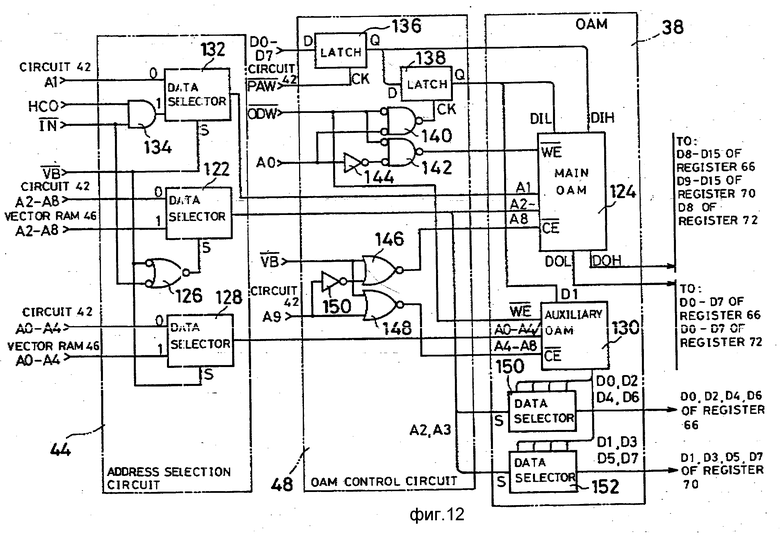

Схема 44 выборки адресов, показанная на фиг. 12 служит для выборки либо адресов с А2 по А8, подаваемых на выход от адресного счетчика (Hi) 94 схемы 42 адресов OAM, либо адресов с А2 до А8 из векторного RAM 46, с тем, чтобы их подать на основное ОАМ 124 ОАМ 38. Более конкретно, сигналы /VB и /IN, поступающие от схемы 34 генерирования синхросигнала, подаются через логический элемент 126 НЕ-ИЛИ на селектор 122 данных. Таким образом, селектор 122 данных посылает адреса с А2 по А8, поступающие от схемы 42 адресов ОАМ, на основное ОАМ 124 в течение периода вертикального запирания. Аналогичным образом, селектор 128 данных служит для выборки либо адресов с А0 по А4, поступивших от адресного счетчика (H) 94 и адресного счетчика (Lo) 96 в схему 42 адресов ОАМ, либо адресов с А0 по А4 из векторного RAM 46 в ответ на сигнал /VB, поступивший от схемы 34 генерирования синхросигнала с тем, чтобы послать его на вспомогательное ОАМ 130 ОАМ 38. Дополнительно, селектор 122 данных выбирает либо адрес А1 из счетчика адресов 96 схемы 43 адресов ОАМ, либо выход логического элемента И 134 в ответ на сигнал /VB, поступивший от схемы 34 генерирования синхросигнала. Два входа логического элемента 134 И принимают сигнал HCO и сигнал /IN, поступивший от схемы 34 генерирования синхросигнала. Таким образом, данные, поданные на выход от микропроцессора 10, записываются в ОАМ 38 во время периода вертикального запирания, тогда как более высокие или самые левые данные объекта DOH и более низкие или самые правые данные объекта DOL считываются из основного ОАМ 124, т.е. ОАМ 38 в ответ на внутренний синхроимпульс в течение иного периода, нежели периода вертикального запирания, чтобы подать на выход оттуда.

ОАМ 38 поделено на две секции, т.е. основное ОАМ 124 и вспомогательное ОАМ 130. Причина для этого в том, что шина данных для микропроцессора 10 из 8 бит, а данные объекта, загружаемые в ОАМ 38 из 34 бит, как описано выше. Конкретно, как показано на фиг. 10, 8-битовые данные загружаются в основное ОАМ 124 четыре раза, и остающиеся 2 бита (= от 34 до 32) группируются или умножаются на четыре с тем, чтобы быть 8-битовыми данными, которые затем загружаются во вспомогательное ОАМ 130. Таким образом, самый старший разряд 9-битовых Н-позиционных данных и 1-битовые данные выбора размера загружаются во вспомогательное ОАМ 130.

Схема 48 управления ОАМ включает в себя фиксатором 136 и 138 8-битовых данных, которые используются для записи данных объекта, образованных микропроцессором 10, в ОАМ 38. Конкретно, данные с D0 по D7 подаются на фиксатор данных 136, как его выходной сигнал, тогда как выход фиксатора данных 136 подается на фиксатор данных 138 как входной сигнал его. Фиксаторы данных 136 и 138 принимают как свой сигнал фиксатора сигнал /PAW, подаваемый на выход адресным декодером 40 (см. фиг. 7), и выход логического элемента 140 НЕ-И соответственно. Логический элемент 140 НЕ-И принимает адрес АО, поданный на выход схемой 42 адресов ОАМ, и сигнал /ODW, поданный на выход адресным декодером 40. Адрес АО инвертируется инвертором 144 с тем, чтобы подать на логический элемент 142 НЕ-И как выход его. Дополнительно логический элемент 142 НЕ-И принимает сигнал /ODW, упомянутый выше. Таким образом, когда адрес АО низкий (по уровню напряжения), фиксатор данных 138 фиксирует данные в ответ на сигнал /ODW. Когда адрес АО является высоким (по уровню напряжения), логический элемент 142 НЕ-И посылает сигнал записи на основное ОАМ 124, и более высокие и более низкие данные объекта DIH и DIL, которые фиксированы в фиксаторах данных 136 и 138 соответственно, записываются в основное ОАМ 124.

Так как вспомогательное ОАМ 130 не является 16-битовым типом, запись данных в ОАМ 130 производится путем возбуждения ОАМ 130. Так сигнал /ODW подается на вспомогательное ОАМ 130 как сигнал записи его, и данные объекта, которые фиксированы в фиксаторе данных 138, записываются во вспомогательное ОАМ 130.

По случаю, схема 48 управления ОАМ включает в себя два логических элемента 146 и 148 НЕ-ИЛИ. Логический элемент 146 НЕ-ИЛИ принимает адрес А9 схемы 42 адресов ОАМ, который инвертируется инвертором 150, и сигнал /VB, поступающий от схемы 34 генерирования синхросигнала. Дополнительно логический элемент 148 НЕ-ИЛИ непосредственно принимает адрес А9 и сигнал /VB. Таким образом, когда адрес А9 является высоким по уровню напряжения в течение периода вертикального запирания, логический элемент 148 НЕ-ИЛИ посылает возбуждающий сигнал на вспомогательное ОАМ 130. Когда он низкого уровня напряжения, логический элемент 146 НЕ-ИЛИ посылает возбуждающий сигнал на основное ОАМ 124. Более высокие данные объекта DOH, считанные из основного ОАМ 124, загружаются в регистр 68 V-позиций, регистр 70 признаков и регистр 72 наименования, тогда как более низкие данные объекта DOL, считанные оттуда, загружаются в регистр 66 H-позиций и регистр 72 наименования.

Как описано выше, специфические данные данных объекта загружаются во вспомогательное ОАМ 130 таким образом, что четыре объекта группируются или собираются. Поэтому селекторы 150 и 152 данных загружают 2 бита, которые принадлежат к 32-битовым данным объекта в основном ОАМ 124, в регистр 66 H-позиций и регистр 70 признаков в тот же период времени, когда происходит загрузка данных в основное ОАМ 124.

Схема 58 адресов векторного RAM, показанная на фиг. 13, включает в себя 5-битовый реверсивный счетчик, т.е. С/В счетчик 154 (С/В=суммирующий/вычитающий прим. переводчика). Данные, отсчитанные С/В счетчиком 154 подаются на адреса с А0 по А4 векторного RAM 46. Сигнал IN, поступающий от схемы 34 генерирования синхросигнала, посылается на вход данных D-FF 156, выход которого подается на вход данных D-FF 158. Сигналы HCO и 5M, поступающие от схемы 34 генерирования синхросигнала, подаются на D-FF 156 и 158 как входы синхроимпульсов их соответственно. Выход D-FF 158 подается на логический элемент 160 НЕ-И, как входной сигнал его вместе с сигналом HCO, и выход логического элемента 160 НЕ-И и выход логического элемента 162 НЕ-И подаются на логический элемент 164 НЕ-ИЛИ как два входных сигнала их. По случаю, сигналы /LB и /HCO, поступившие от схемы 34 генерирования синхросигнала, подаются на два входа логического элемента 162 НЕ-И. Дополнительно выход логического элемента 164 НЕ-ИЛИ подается на С/В счетчик 154, как его входной сигнал отсчета, т.е. его синхроимпульс. Таким образом, синхроимпульс С/В счетчика 154 определяется сигналом HCO, поступающим от схемы 34 генерирования синхросигнала.

Сигнал /LB, поступающие от схемы 34 генерирования синхросигнала, подается через инвертор 166 на С/В счетчик 154 как входной сигнал С/В для выборки, либо операции суммирования счетчика С/В 154, либо операции вычитания счета его. Таким образом, когда сигнал /LB высокого уровня, С/В счетчик 154 используется как суммирующий счетчик, в то время как он используется как вычитающий счетчик, когда этот сигнал низкого уровня.

Далее, сигналы 5М и HCO, поступающие от схемы 34 генерирования синхросигнала, подаются на вход логического элемента 168 НЕ-И, выход которого подается на логический элемент 170 НЕ-И вместе с сигналом /INRANGE, поступающих от схемы 56 определения попадания в диапазон. Затем, сигнал /INRANGE подается на вход данных D-FF 172, и выход логического элемента 168 НЕ-И подается на D-FF как его синхроимпульс. Выход D-FF 172 подается на селектор 174 данных в качестве его одного входного сигнала, и сигнал /LB подается на селектор данных 174 как его входной сигнал переключения. Дополнительно выход логического элемента 170 НЕ-И подается на RS-176, как его установленный входной сигнал /S, и сигнал /HI, поступающий от схемы 34 генерирования синхроимпульса, подается на RS-FF 176 как его входной сигнал /R установления исходного положения. Выход RS-FF 176 посылается на логический элемент 178 И как его входной сигнал. Либо сигнал /HBH, либо L, поступающий от схемы 34 генерирования синхросигнала, и выход D-FF 182 посылаются через логический элемент 180 ИЛИ на логический элемент 178 И как другие входные сигналы его.

Поэтому, когда сигнал /LB становится высоким по уровню напряжения во время периода, когда производится определение попадания в диапазон, C/B счетчик 154 возбуждается для выбора операции суммирования отсчета. Затем D-FF 172 генерирует возбуждающий сигнал каждый раз, когда сигнал /INRANGE, указывающий о состоянии попадания в диапазон, становится низким по уровню напряжения, и поэтому C/B счетчик 154 считает в прямом направлении синхроимпульсы, подаваемые на выход логическим элементом 164 НЕ-ИЛИ. Отсчитанная величина C/B счетчика 154 подается на векторное RAM 46 как адрес записи его. Когда C/B счетчик 154 считает в прямом направлении синхроимпульсы, и отсчитанная величина C/B счетчика 154, т.е. число объектов, попадающих в диапазон, достигает 32, способных визуализироваться одной строкой, логический элемент 186 и D-FF 188 генерируют сигнал INRANGE FULL. Как следствие схема 56 определения попадания в диапазон, обесточивается в ответ на сигнал INRANGE FULL. С другой стороны, когда сигнал /LB становится низким по напряжению, C/B счетчик 154 возбуждается для выбора операции обратного отсчета, после чего он отсчитывает в обратном направлении синхроимпульсы каждый раз, когда подается сигнал L от схемы 62 управления счетчиком размера. Для считывания объекта, попадающего в диапазон, отсчитанная величина C/B счетчика 154 подается на векторное RAM 46, как адрес считывания. Когда все объекты считаны, отсчитанная величина C/B счетчика 154 достигает "0", и сигнал переноса посылается на D-FF 182, тем самым обесточивая C/B счетчик 154.

Когда схема 56 определения попадания в диапазон производит начало операции определения попадания в диапазон, сигнал /HI, генерируемый схемой 34 генерирования сигнала синхронизации подается на вход установления в исходное состояние С/В счетчика 154, и также подается на RS-FF 176, как его входной сигнал установления в исходное положение. Если объект, попадающий в диапазон в последующем не детектируется, тогда выход RS-FF 176 остается низким по уровню напряжения. Затем выход RS-FF 176 проходит через D-FF 190 и D-FF 192, который в свою очередь подается на выход как сигнал /NONOBJ в ответ на сигнал HCO, поступивший от схемы 34 генерирования синхросигнала. Сигнал /NONOBJ подается на схему 92 управления буферным RAM (см. фиг. 9).

Схема 74 управления регистрами, показанная на фиг. 14, имеет логический элемент 194 НЕ-ИЛИ и логические элементы 196, 198 НЕ-И. Сигнал С, подаваемый на выход со схемы 62 управления счетчиком размеров (см. фиг. 8), и сигналы VB и IN, поступающие от схемы 34 генерирования синхросигнала, посылаются на входы логического элемента 194 НЕ-ИЛИ. На входы логического элемента 196 НЕ-И подается выход логического элемента 194 НЕ-ИЛИ и сигналы /5М и HCO, поступающие от схемы 34 генерирования синхросигнала, соответственно, тогда как на входы логического элемента 198 НЕ-И подаются сигнал L, посылаемый схемой 62 управления счетчиком размеров (см. фиг. 8), и сигналы 5М и HCO, поступающие от схемы 34 генерирования синхросигнала, соответственно.

Арифметическая схема 64 H-позиций включает в себя 8-битовый полный сумматор 200 в отношении одного, т.е. от А0 до А7, из входов, на который подается выход логического элемента 202 ИСКЛЮЧАЮЩЕЕ ИЛИ, и в отношении другого, т. е. от В3 до В5, из входов, на который подается выход логического элемента 204 И. По случаю, на остающийся вход из вышеназванных входов полного сумматора 200, подается потенциал заземления, т.е. "0" потенциал. Данные H-позиций от D0 до D7 от первого регистра 66а H-позиций регистра 66 H-позиций, подаются на один из входов логического элемента 202 ИСКЛЮЧАЮЩЕЕ ИЛИ вместе с входным сигналом переноса CIN, подаваемым от логического элемента 206 И. Таким образом, когда входной сигнал переноса CIN является высоким по уровню напряжения, данные с D0 и D7 инвертируются посредством логического элемента 202 ИСКЛЮЧАЮЩЕЕ ИЛИ, и в отношении другого, т.е. от В3 до В5, из входов, на который подается выход логического элемента 204 И. По случаю, на остающийся вход из вышеназванных входов полного сумматора 200, подается потенциал заземления, т.е. "0" потенциал. Данные H-позиций от D0 до D7 от первого регистра 66а H-позиций регистра 66 H-позиций, подаются на один из входов логического элемента 202 ИСКЛЮЧАЮЩЕЕ ИЛИ вместе с входным сигналом переноса CIN, подаваемый от логического элемента 206 И. Таким образом, когда входной сигнал переноса CIN является высоким по уровню напряжения, данные с D0 до D7 инвертируются посредством логического элемента 202 ИСКЛЮЧАЮЩЕЕ ИЛИ, и инвертированные таким образом данные подаются на полный сумматор 200, как входной сигнал с A0 до A7, упомянутый выше.

По случаю, логический элемент 206 Н принимает данные D8, посылаемые от второго регистра 66b H-позиций регистра 66 H-позиций, и выход логического элемента 208 ИЛИ. Когда данные D8 являются "1", горизонтальная (H) позиции объекта попадает в отрицательный (минусовой) район, как показано на фиг. 15, тогда как H-позиция объекта попадает в положительный /полюсовой/ район, как показано на фиг. 15. Конкретно, фактический экран монитора 22 (см. фиг. 1) для визуализации на нем объекта, соответствует правой половине всего экрана, если смотреть с точки пересечения координат (О, О), как показано на фиг. 15. Горизонтальная позиция представлена в диапазоне "0-255", т.е, "000H-OFFH" в рамках такого экрана дисплея. Однако в настоящем варианте реализации чтобы плавно визуализировать часть объекта в рамках дисплейного экрана от левого конца экрана, даже когда левый конец объекта находится вне экрана дисплея, воображаемый экран, определяемый левой половиной всего экрана монитора 2, предполагается, даже если объект визуализируется за диапазоном дисплейного экрана, и горизонтальная позиция может быть установлена даже при таком диапазоне. Горизонтальная позиция представлена в диапазоне "256-511", т.е. "100H-1FFH", когда объект представлен за диапазоном дисплейного экрана. Когда данные H-позиции D8 являются "0" в течение периода определения попадания в диапазон, данные с D0 по D7 непосредственно подаются на полный сумматор 200, как входной сигнал с A0 по A7 его. В это время входы с B3 по B5 становятся низкими по уровню напряжения в результате сигнала IN, подаваемого схемой 34 генерирования синхросигнала, который говорит о состоянии объекта, находящегося на стадии определения попадания в диапазон. Таким образом, выход полного сумматора 200 является суммой "D0-D7+0", и поэтому данные с D0 по D7 подаются на выход с полного сумматора 200 как они есть. Когда данные H-позиции D8 представляют "1", данные с D0 по D7 инвертируются логическим элементом 202 ИСКЛЮЧАЮЩЕЕ ИЛИ, и инвертированные таким образом данные подаются на полный сумматор 200, как входной сигнал его с A0 по A7. В то время входы с B3 по B5 фиксируются, чтобы быть низкого уровня по напряжению посредством сигнала IN, упомянутого выше. Таким образом, выход полного сумматора 200 представляет сумму "1 + D0 D7".

Когда сигнал HCO, поданный через логический элемент 208 ИЛИ от схемы 34 генерирования синхросигнала, высокого уровня по напряжению, и если применяется другой процесс вместо вышеописанного, либо "D0 D7 + 0", либо "D0 D7 + 1" полного сумматора 200 загружается в счетчик 60 размеров (см. фиг. 8), как исходная величина его в зависимости от либо "0", либо "1" данных H-позиций D8. Когда сигнал HCO низкого уровня напряжения, данные H-позиции с D0 по D7 подаются на полный сумматор 200, как входные сигналы его с A0 по A7, как они есть, и данные с SC0 по SC2, поданные на выход счетчиком 60 размеров, подаются на полный сумматор 200 как входные сигналы с B3 по B5 его. Поэтому результат сложения обеих данных подается на выход из полного сумматора 200.

Таким образом, причина для преобразования данных H-позиции в абсолютную величину в арифметической схеме 64 H-позиций состоит в том, что объект предназначается для визуализации с левого конца экрана монитора за исключением части объекта, которая вне дисплейного экрана монитора.

По случаю, арифметическая схема 76 V-позиций включает в себя 8-битовый полный сумматор 210 в отношении одного, т.е. от A0 до A7, из входов, на который подаются данные V-позиций с D8 по D15 регистра 68 V-позиций, инвертированные инвертором 212, и в отношении другого, т.е. с B0 по B7, из входов, на который подается сигнал с VD0 по VD7 со схемы 34 генерирования синхросигнала. Затем результат сложения обоих входов полным сумматором 210 подается на схему 78 управления сумматором адресов и схему 56 определения попадания в диапазон (см. фиг. 8), как данные о вертикальной (V) позиции объекта.

Регистр 50 размеров, показанный на фиг. 16, включает в себя первый, второй и третий регистры размеров 50a, 50b и 50c, каждый из которых принимает, как сигнал загрузки, сигнал SZW, посылаемый декодером 40 адресов (см. фиг. 7). Каждый из первого, второго и третьего регистров 50a, 50b и 50c, принимает данные с D0 по D7, поступающие от микропроцессора 10 (см. фиг. 1) по шине данных. Регистр 54 чередований имеет первый и второй регистры чередования 54a, 54b, каждый из которых принимает как сигнал загрузки сигнал ITW, посылаемый декодером 40 адресов (см. фиг. 7). Каждый из первого и второго регистров чередования 54a и 54b принимает данные с D0 по D7, посылаемые по шине данных от микропроцессора 10 (см. фиг. 1). Первый регистр размеров 50а загружается данными адреса BASE в зоне памяти объекта, и второй регистр размеров 50b загружается данными SEL. Дополнительно третий регистр 50с загружается данными размера SIZE. Первый регистр чередования 54а загружается данными чередования для принятия решения, будетли реализован другой дисплей или идентичный дисплей полями нечетной нумерации и полями четной нумерации. Второй регистр чередования 54b загружается данными OBJ VSEL.

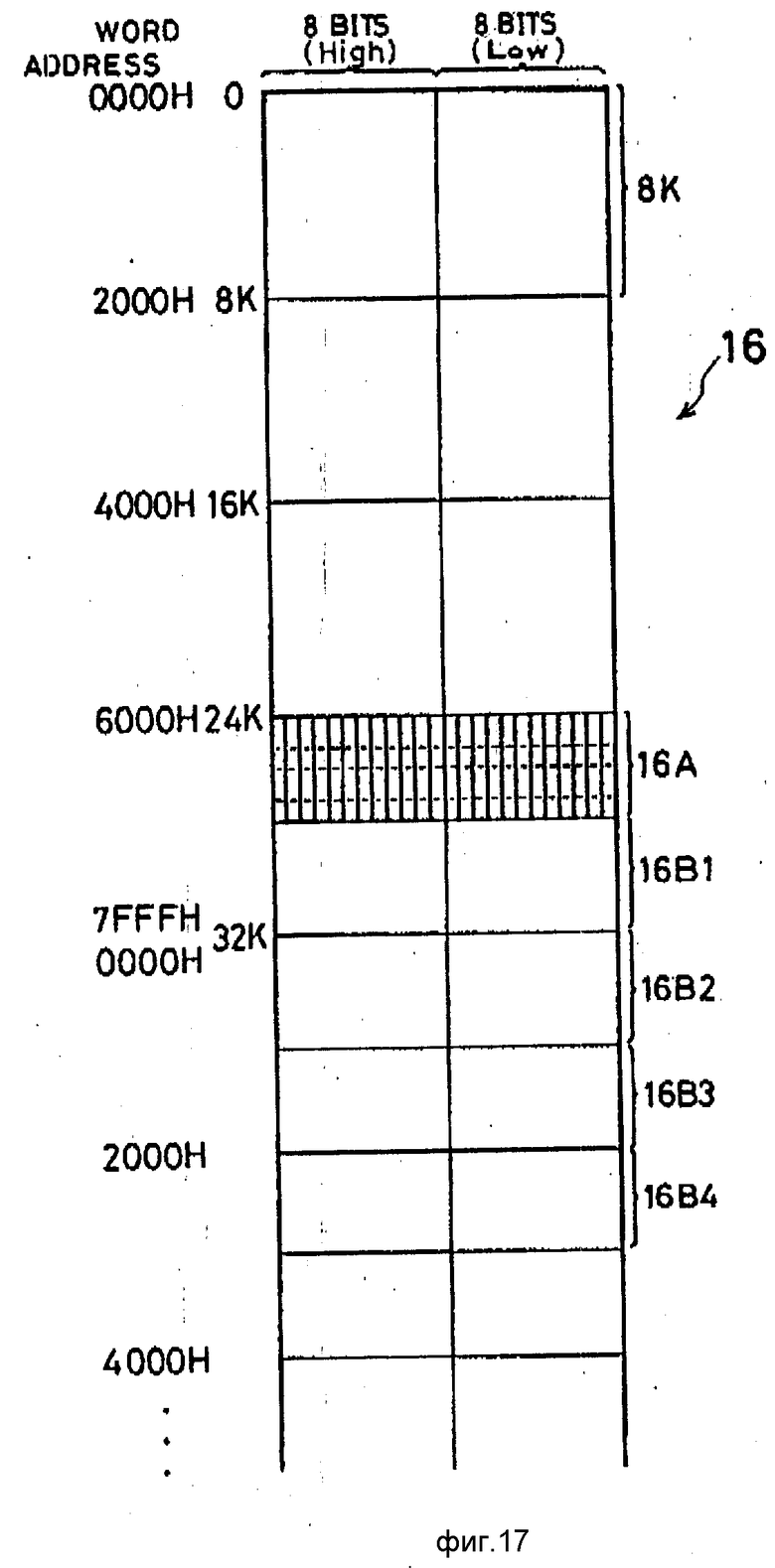

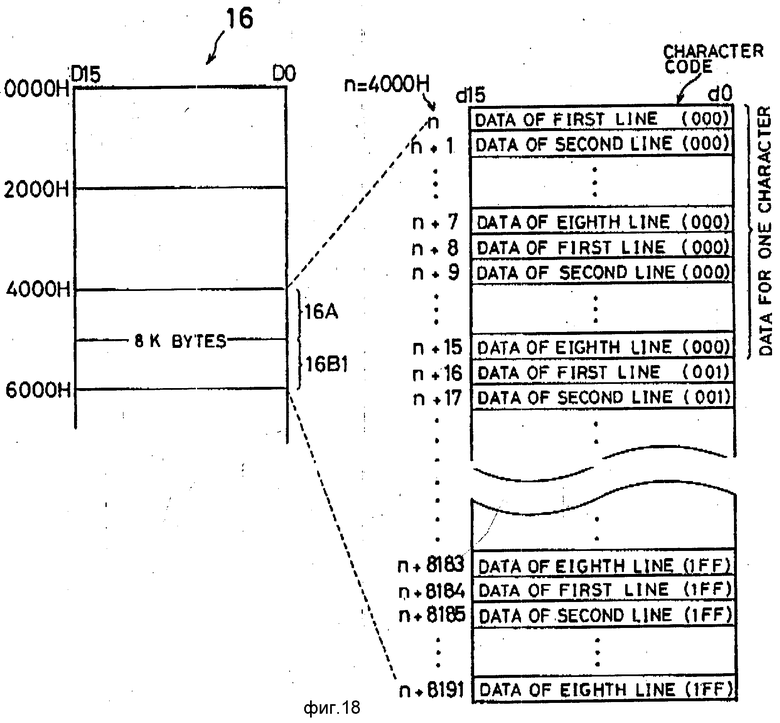

Данные BASE и SEL, загруженные в первый и второй регистры размеров 50a и 50b, используются для определения адресов в ЗУ 16 видеоданных для произвольной установки зоны хранения 16а фонового изображения и зоны хранения 16b данных символа ЗУ 16 видеоданных (см. фиг. 1), образованные в единый блок S RAM, как описано выше. Конкретно, ЗУ 16 видеоданных, показанное на фиг. 17 и 18, имеет емкость памяти 64 килобайт (слов), в которых выделенная 4-х килобайтная зона 16а предназначена для данных BASE, определяемых данными с D0 по D.

Дополнительно, другие зоны 16B1, 16B2, 16B3, каждая из которых представлена в форме 4 килобайт, и другая зона 16B4, которая также представлена в форме 4 килобайт, предназначены для данных SEL, определяемых данными D3 и D4. Тип объекта может изменяться только путем правильного объединения данных BASE и SEL и изменения 2 битов, определяющих данные SEL. Более конкретно, данные символа объекта, необходимые в некоторой сцене в игре, загружаются в любую одну из обозначенных зон 16А и других зон с 16B1 по 16B4, и данные символа объекта, необходимые в другой сцене, загружаются в одну из остающихся зон из числа зон с 16B1 по 16B4. Таким образом, тип объекта может быть легко изменен в отношении каждой сцены игры путем простого изменения 2 бит, представляющих данные SEL, и определения одной из остающихся зон из числа зон с 16B1 по 16B4, когда требуемый объект необходим.

3-битовые данные размера с D5 по D7, посылаемые третьим регистром размеров 50с, вводятся в декодер 52 размеров. Декодер 52 размеров декодирует 1-битовые данные выбора размера SIZE SEL, подаваемые с первого регистра признаков 70а (см. фиг. 14), включенного в регистр признаков 70, и данные размера с D5 по D7, с тем, чтобы подать на выход сигналы обозначения размеров S8, S16, S32, S64 соответственно от соответствующих логических элементов НЕ-ИЛИ 52а, 52b, 52c, 52d. Конкретно, когда сигнал S8 обозначения размера подан на выход от логического элемента НЕ-ИЛИ 52а, объект (образован одноблочным символом), представленный в форме горизонтальных х вертикальных 8х8 точек, будет выбран. Когда сигнал S16 обозначения размера подан на выход от логического элемента НЕ-ИЛИ 52b, объект (образован четырехблочным символом), представленный в форме горизонтальных х вертикальных 16 х 16 точек, будет выбран. Когда подан сигнал S32 обозначения размера от логического элемента НЕ-ИЛИ 52с, объект (образован шестнадцатиблочными символами), представленный в форме горизонтальных х вертикальных 64 х 64 точек, будет выбран.

Эти сигналы S8, S16, S32 и S64 обозначения размера управления сумматором адресов как сигналы /OBJ8, OBJ16, /OBJ32 и OBJ64 соответственно. Дополнительно, сигналы S8 и S16 обозначения размера подаются на селектор 214 данных, включенный в схему 56 определения попадания в диапазон, тогда как сигналы S32 и S64 обозначения размера подаются на селектор 216 данных. Далее, сигнал S64 обозначения размера подается на селектор 218 данных как один из двух его входов, а другой из его входов фиксирован на "1". Каждый из селекторов данных 214, 216 и 218 принимает данные чередования как сигнал выборки, который подается на выход от второго регистра чередований 54b, включенный в регистр чередований 54. Размер объекта изменяется в момент чередования и нечередования. Когда плотность точек увеличивается в момент чередования, например, размер объекта уменьшается. Соответственно, изменение размера, используемое как критерий определения попадания в диапазон на основе сигнала обозначения размера, поданного декодером 52 размеров, необходимо. Для выполнения операции определения попадания в диапазон в соответствии с различием размеров между объектами используются селекторы данных с 214 до 218.

Выход селектора данных 214 инвертируется инвертором 220, и инвертированный таким образом выход подается на один из двух входов логического элемента И 224 через логический элемент ИЛИ 222. Выход логического элемента И 226 подается через инвертор 222 на другой один из входов логического элемента И 224. Два входа логического элемента И 226 принимают сигнал обозначения чередования, поступающий от регистра чередований 54, и сигнал S8 обозначения размера, подаваемый через инвертор 228 от логического элемента НЕ-ИЛИ 52а. Данные V-позиции D3, поданные на выход от арифметической схемы 76 V-позиций, подается на другой один из выходов логического элемента И 224.

Выходы селекторов данных 216 и 218 подаются на логический элемент 230 И, как два из трех его входных сигналов. Данные о V-позиции D4, поданные на выход арифметической схемой 76 V-позиций, подаются на логический элемент И 230 на другой остающийся вход его. Дополнительно выход селектора данных 218 подается на логический элемент И 232 вместе с данными V-позиции D5, поступающими от арифметической схемы V-позиций. Выход логического элемента И 226 подается на логический элемент И 234 вместе с данными V-позиции D2, посылаемыми на выход арифметической схемой 76 V-позиций. Соответствующие выходы этих логических элементов И 224, 230, 232 и 234, инвертируются вместе с данными V-позиций D7, поданными на выход арифметической схемой 76 V-позиций, и таким образом инвертированные данные все подаются на логический элемент И 236 как его входные сигналы.

Далее выход логического элемента НЕ-ИЛИ 238 подается на логический элемент НЕ-И как его входной сигнал. Два входа логического элемента НЕ-ИЛИ 238 принимают данные H-позиции D8, посылаемые регистром 66 H-позиций, и выход логического элемента НЕ-И 240, которые все инвертируются. Логический элемент НЕ-И 240 принимает как входные сигналы выходы логических элементов НЕ-И 241, 242 и 244 и инвертирует каждые из данных об H-позиции D6 и D7, посылаемых регистром 66 H-позиций. Два входа логического элемента 241 НЕ-И принимают выход инвертора 228, используемый для приема сигнала S8 обозначения размера, и данных H-позиции D3, подаваемых регистром 66 H-позиций. Дополнительно, на три входа логического элемента НЕ-И 242 подаются данные об H-позиции D4, посылаемые регистром 66 H-позиций, и сигналы S16 и S32 обозначения размера. Далее на два входа логического элемента НЕ-И 244 подаются данные об H-позиции D5, посылаемые регистром 66 H-позиций, и сигнал S64 обозначения размера.

Выход логического элемента НЕ-ИЛИ 238 используется как сигнал, указывающий, находится или нет в положении попадания в диапазон в горизонтальном (H) направлении. Каждый из выходов логических элементов И 224, 230, 232 и 234, используется как сигнал, указывающий, находятся или нет каждые из данных D5 и D7, посылаемые арифметической схемой 76 V-позиций в положении попадания в диапазон в вертикальном (V) направлении.