Данное изобретение относится к процессорному устройству обработки и формирования видеоизображений, предназначенному для использования в телевизионной игровой установке (приставке) или подобном устройстве и позволяющему воспроизводить на телеэкране как движущееся изображение, так и изображение заднего плана.

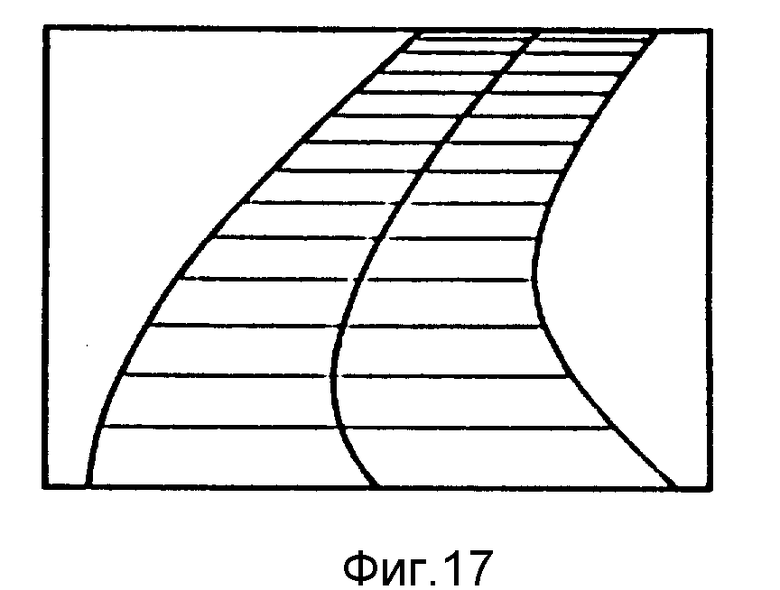

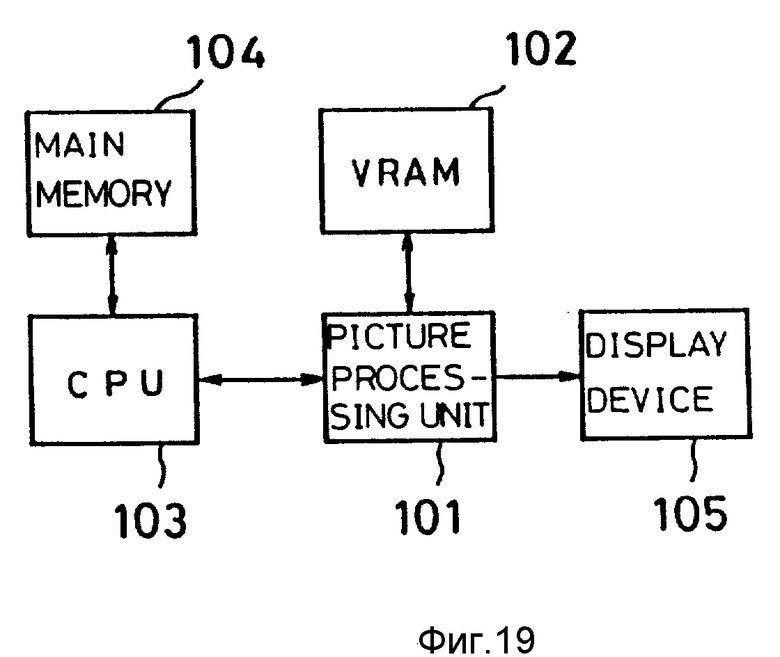

Известны устройства, обеспечивающие поворот движущегося изображения: см. , в частности, японскую патентную публикацию N 45225/1980 и выкладку изобретения в ведомственном бюллетене Патентного ведомства Японии N 113529/1976 (дубликат патента США N 4026555). В свою очередь, известны устройства, обеспечивающие поворот изображения заднего фона (см. схему, показанную на фиг. 17). В схему, представленную на фиг. 17, входит видеозапоминающее устройство VPAM 102 с произвольной выборкой данных (далее в русском тексте - ВЗУПВ), содержащее обычную резидентную РАМ-память (ЗУПВ) и центральный процессор CPV 103 (далее в тексте - ЦП), подключенные к процессорному блоку 101 обработки изображений. Оперативное (основное) запоминающее устройство 104 наряду с данными изображениями заднего фона и движущегося изображения запоминает служебные управляющие данные, используемые для контролируемого воспроизведения данных изображения; это ЗПУ подключено к центральному процессору 103. Данные изображений, записанные в оперативное ЗПУ 104, транслируются в ВЗУПВ 102 (VPAM 102) через процессор изображения 101. В соответствии с управляющими данными, поступающими от ЦП 103 (CPU 103), процессор изображения 101 считывает данные из видеозапоминающего устройства 102 и выводит эти данные на устройство отображения 105 в виде видеосигнала, по которому на устройстве 105 в соответствии с указанными данными формируется, воспроизводится видеоизображение. Адреса ВЗУПВ 102 соответствуют положениям по горизонтали и вертикали изображения, формируемого на дисплее (экране) 105. Вышеуказанные данные движущегося изображения или изображения заднего фона (в некоторых случаях движущееся изображение дополняет изображение заднего фона) записываются в соответствующие адреса ВЗУПВ 102.

При работе анализируемой известной телевизионноигровой установки при осуществлении поворота, увеличения или уменьшения размера соответствующего изображения заднего фона и его воспроизведении на телеэкране 105 в течение периода действия кадрового гасящего импульса по данным изображения центральный процессор 103 (CPU 103) осуществляет вычисление в соответствии с положением в горизонтальном направлении (ниже в тексте "положение по горизонтали, горизонтальное положение") и с положением в вертикальном направлении (ниже в тексте - "положение по вертикали, вертикальное положение") на экране дисплея (телевизора) 105 рабочих данных по первоначальному, исходному изображению заднего фона, хранящихся в ВЗУПВ 102, - горизонтальное и вертикальное положение (в случае, когда осуществляется поворот, увеличение или уменьшение изображения заднего фона) и записывает данные по первоначальному изображению заднего фона и адреса видеопамяти 102 (RAM 102), соответствующие вычисленным горизонтальному и вертикальному положениям. После этого процессор изображения 101 преобразует данные, записанные в ВЗУПВ 102, в видеосигнал и выводит его на устройство 105 видеоотображения в периоды строчной развертки.

Известны также устройства для увеличения или уменьшения размеров изображения заднего фона. Одно из таких устройств описано в выкладке патента, опубликованной в ведомственном бюллетене Патентного ведомства Японии за N 172088/1985 (дубликат патента США N 4754270).

Примечательно то, что технические средства, описанные в вышеупомянутой публикации японского патента N 45225/1980 и выкладке в бюллетене N 113529/1976, не могут быть использованы для поворота изображения заднего фона.

Далее следует сказать, что прототипное процессорное устройство, представленное на фиг. 17, имеет следующий недостаток: при повороте, увеличении или уменьшении изображения заднего фона и его воспроизведении центральный процессор 103 (CPU 103) должен вычислять горизонтальное и вертикальное положение. В результате производительность этого процессора уменьшается настолько, что он не способен осуществлять какую-либо другую видеообработку, а сам процесс обработки данных по повороту, увеличению или уменьшению изображения заднего фона растягивается на относительно большое время.

Кроме того, при осуществлении вышеупомянутой обработки информации по повороту, увеличению или уменьшению изображения заднего фона данные по этому изображению, записанные в ВЗУПВ 102, подвергаются перезаписи. Естественно, это не позволяет сохранить те данные по первоначальному (исходному) заднефоновому изображению, которые имелись перед обработкой по повороту, увеличению или уменьшению такого изображения. Здесь уместно привести следующий пример: при многократном последовательном повороте первоначального изображения заднего фона с угловым шагом 30o на полный оборот в 360o со временем ошибки вычислений по соответствующим пошаговым разворотам, суммируясь, становятся настолько большими, что воспроизводимое изображение заднего фона по координатному взаимоположению его участков будет отличаться существенным образом от первоначального изображения, при этом форма воспроизводимого изображения отличается от формы указанного первоначального изображения. Таким образом, существующая процессорная техника обработки видеизображений, не обеспечивая сохранения исходного изображения заднего фона (фидеофонограммы) как по форме, так и по положению, является малоэффективной и требует принципиального совершенствования.

В заключение следует указать на то, что устройство, описанное в выкладке японского патента в бюллетене Патентного ведомства Японии N 172088/1985, имеет тот принципиальный недостаток, что при повороте изображение заднего фона не может быть увеличено или уменьшено в масштабе, при этом обработка данных по повороту и увеличению или уменьшению изображения не может быть реализована одним и тем же аппаратным средством (электронной схемой).

В соответствии с вышеуказанным главной целью настоящего изобретения является разработка видеопроцессорного устройства, способного воспроизводить при обработке изображение заднего фона с той же формой, что и у первоначального изображения-сигналограммы, без каких-либо деформационных искажений до или после поворота.

Другая цель изобретения состоит в создании видеопроцессорного устройства, способного осуществлять обработку видеоинформации по поводу и/или увеличению или уменьшению изображения заднего фона с высоким быстродействием без перегрузки центрального процессора, воспроизводя первоначальное изображение без каких-либо деформаций.

Еще одной целью данного изобретения является разработка видеопроцессора, способного производить обработку информации по увеличению или уменьшению изображения заднего фона при одновременном осуществлении его поворота.

Настоящее изобретение характеризуется наличием в его составе следующих функциональных средств: запоминающего устройства, регистрирующего видеоданные по изображению заднего фона в адресе, соответствующем положению воспроизведения указанного изображения до обработки информации по повороту; исполнительного средства, задействующего на основе управляющих данных, формируемых для поворотной обработки информации, адрес вышеупомянутого запоминающего устройства, соответствующий положению воспроизведения изображения заднего фона после осуществления обработки информации по его повороту; считывающего средства для извлечения видеоданных, записанных в адрес запоминающего устройства, задействуемый упомянутым исполнительным средством; и генератора, формирующего видеосигнал на основе видеоданных, считываемых упомянутым считывающим средством.

В другом варианте исполнения в состав предложенного видеопроцессорного устройства могут входить запоминающее устройство для записи видеоданных по изображению заднего фона в адрес, соответствующий положению на экране указанного изображения перед осуществлением обработки данных по повороту и увеличению или уменьшению изображения; исполнительное средство для задействования в соответствии с управляющими данными, используемыми для обработки информации по повороту и увеличению или уменьшению указанного изображения, адреса запоминающего устройства-накопителя, соответствующего положению воспроизведения изображения заднего фона после осуществления хотя бы одного из вышеуказанных видов обработки данных по преобразованию изображения; считывающее средство для выборки видеоданных, записанных в адрес запоминающего устройства, задействуемый упомянутым исполнительным средством; генератор для формирования видеосигнала на основе видеоданных, считываемых упомянутым считывающим средством.

В вышеуказанной процессорной системе запоминающее устройство-накопитель записывает перед осуществлением обработки данных по повороту (и/или увеличению или уменьшению) изображения видеоданные в адрес, соответствующий положению изображения на экране перед обработкой по повороту (и/или увеличению и уменьшению масштаба).

Затем в процессе поворота (и/или увеличения или уменьшения) изображения исполнительное средство задействует адрес запоминающего устройства, соответствующий положению на экране изображения после осуществления обработки информации по повороту (и/или увеличению или уменьшению), в соответствии с управляющими данными, используемыми для указанной обработки, после чего считывающее средство считывает видеоданные, хранящиеся по указанному адресу запоминающего устройства, которое задействуется исполнительным средством, при этом генератор на основе видеоданных, считываемых упомянутым считывающим средством, генерирует соответствующий видеосигнал. Таким образом, видеосигнал формируется в соответствии с видеоданными, хранящимися в запоминающем устройстве, непосредственно во время осуществления по меньшей мере одной из операций обработки информации по повороту, увеличению или уменьшению изображения.

Данное изобретение позволяет воспроизводить с поворотом изображение заднего фона точно такой же формы, что и у первоначального, опорного изображения указанного фона, причем все это делается без деформаций как до, так и после поворота. Кроме того, информационная обработка по повороту и/или увеличению или уменьшению изображения заднего фона осуществляется с высокой скоростью без перегрузки центрального процессора и без искажения первоначального изображения заднего фона.

Вышерассмотренные и другие цели, положительные качества и отличительные признаки настоящего изобретения более полно и более наглядно будут раскрыты и проиллюстрированы в подробном описании существа предложенного, приводимом ниже. Это описание сопровождено поясняющими графическими материалами, краткое содержание которых анализируется непосредственно ниже.

На фиг. 1 приведена блок-схема телевизионной игровой установки (аппарата), решенная в соответствии с одним из вариантов исполнения данного изобретения.

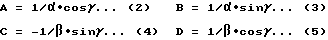

На фиг. 2 представлена схема, показывающая взаимосвязь между рабочей областью видеозапоминающего устройства с произвольной выборкой ВЗУПВ (VPAM) и областью воспроизведения изображения заднего фона на экране по данным такого изображения, записанным в ВЗУПВ 7 (VPAM 7).

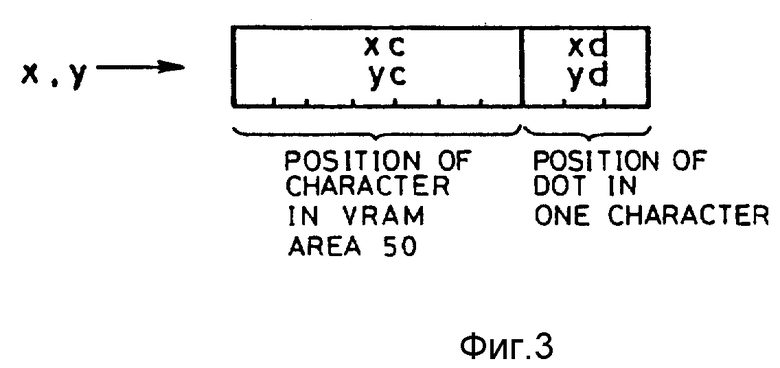

На фиг. 3 приведена диаграмма, показывающая битовую конфигурацию координат "X" и "Y", определяющих положение данных в области ВЗУПВ, показанной на фиг. 2.

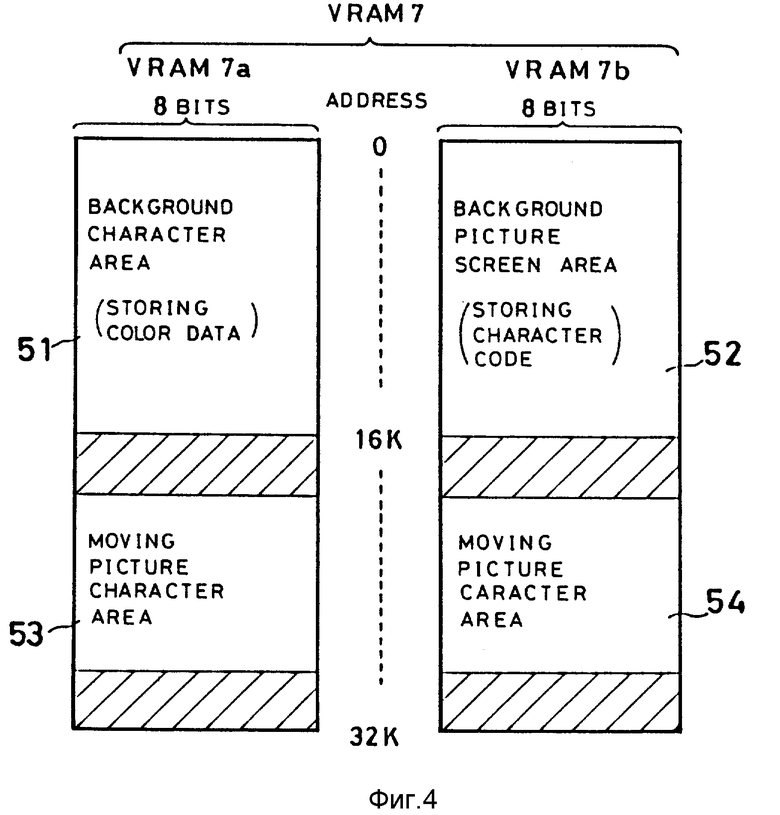

На фиг. 4 - схема, представляющая карту размещения информации и видеозапоминающем устройстве ВЗУПВ (VPAM).

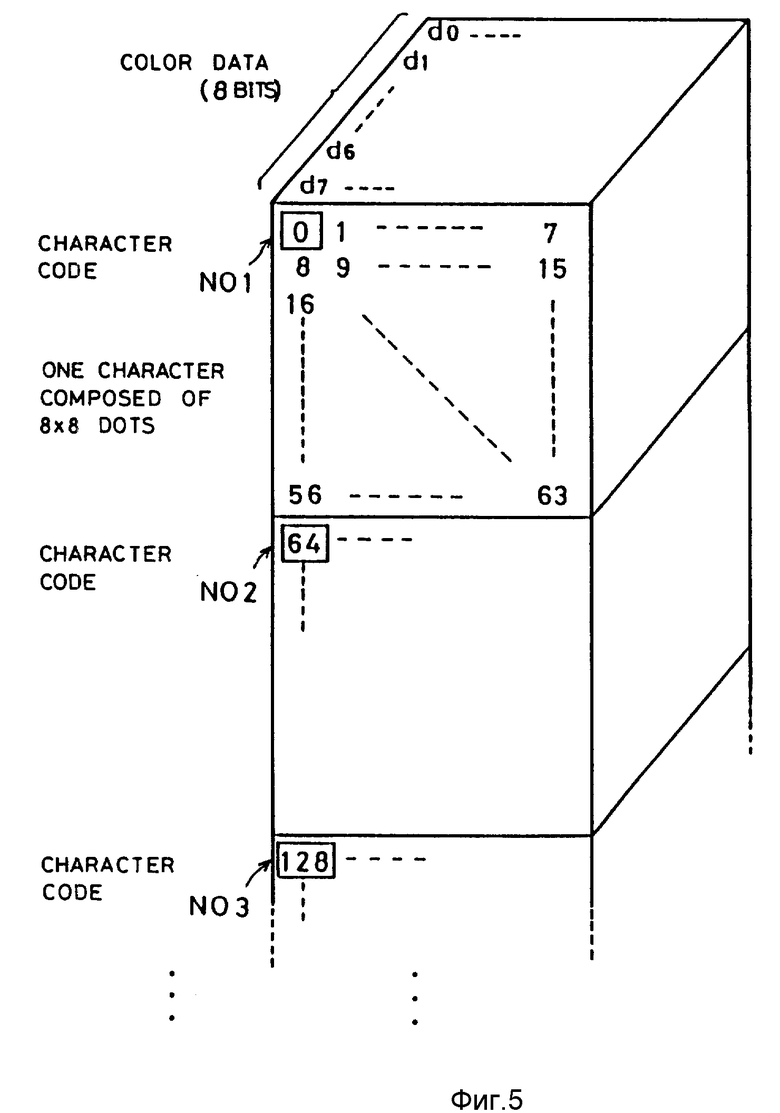

На фиг. 5 приведена схема, иллюстрирующая условия (порядок) записи и хранения видеоданных по цветному изображению заднего фона в ВЗУПВ, входящем в схему фиг. 1.

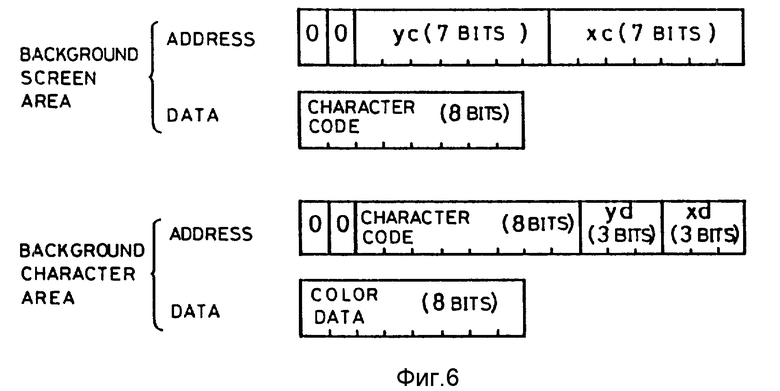

На фиг. 6 представлена диаграмма, показывающая битовые конфигурации адресов и данных в знаковой области изображения обратного фона и площади заднефонового изображения в ВЗУПВ, входящем в схему фиг. 1.

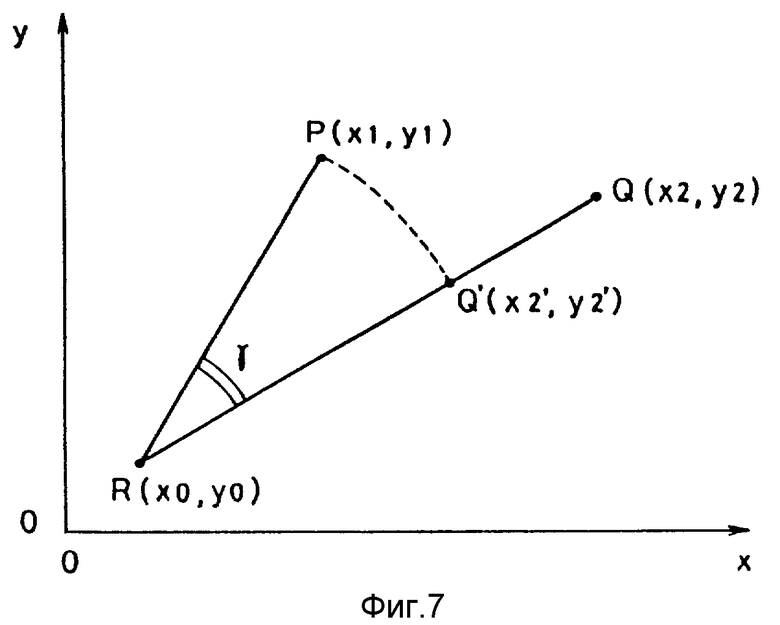

На фиг. 7 показан график, поясняющий принцип обработки данных по повороту и увеличению или уменьшению изображения заднего фона.

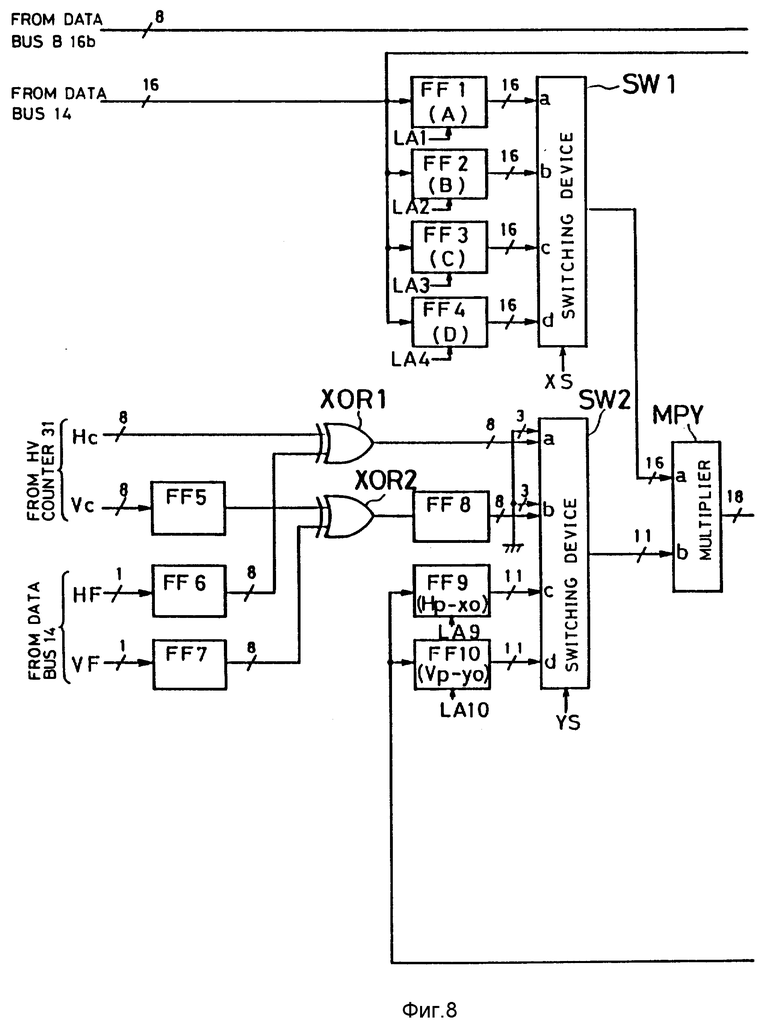

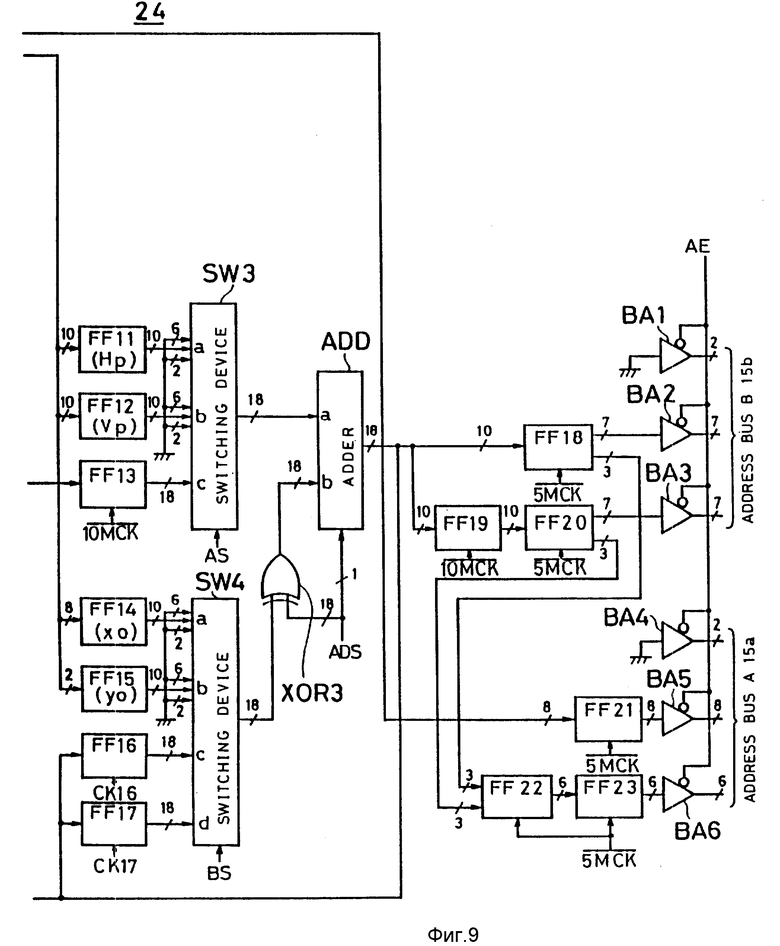

На фиг. 8, 9 приведена структурная (функциональная) схема управляющего устройства выборки адресов по данным изображения заднего фона.

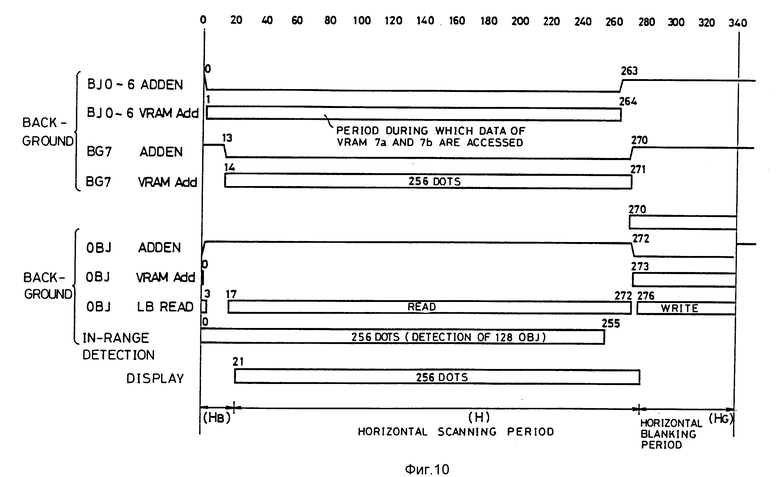

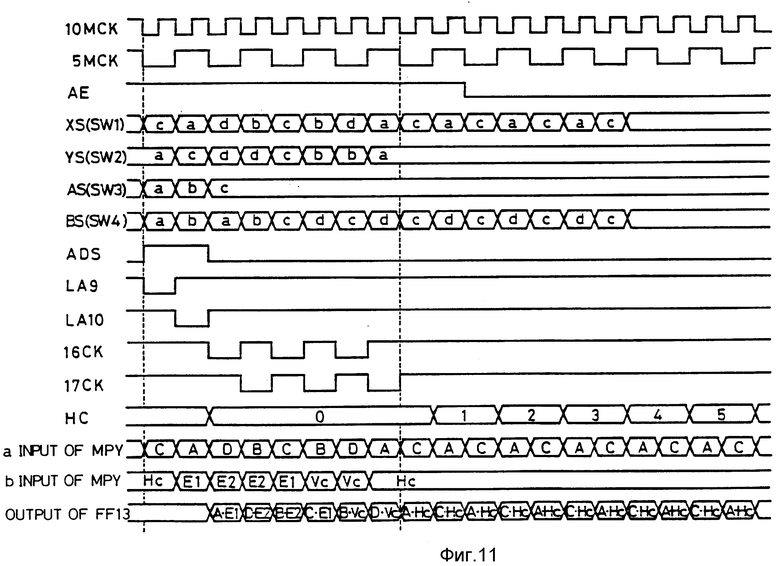

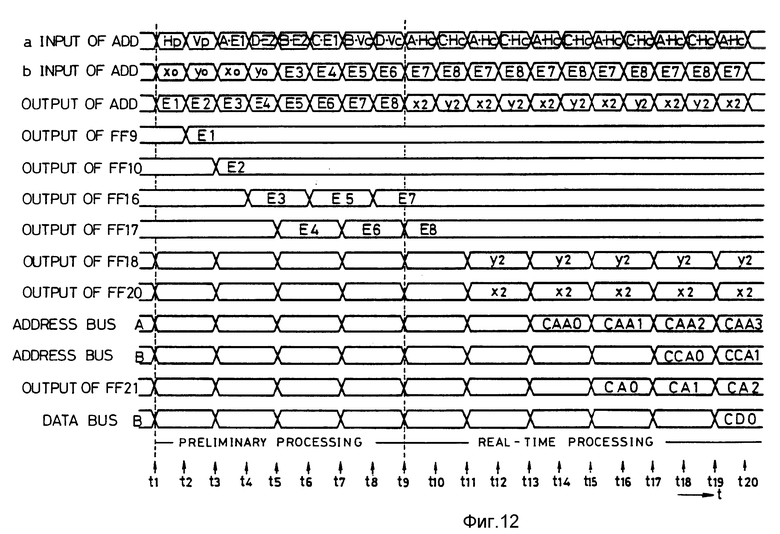

На фиг. 10 - 12 представлены временные диаграммы, поясняющие принцип действия вышеупомянутого управляющего устройства (схемы) выборки адресов видеоданных изображения заднего фона.

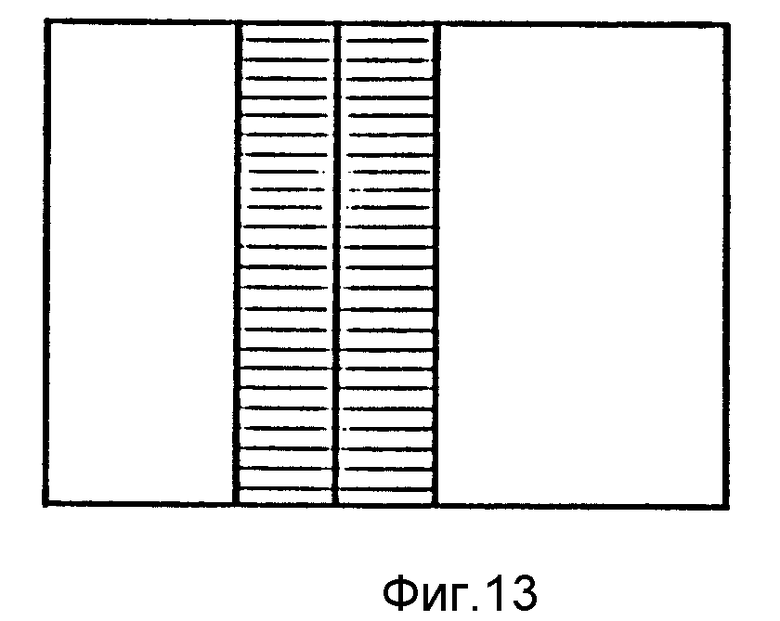

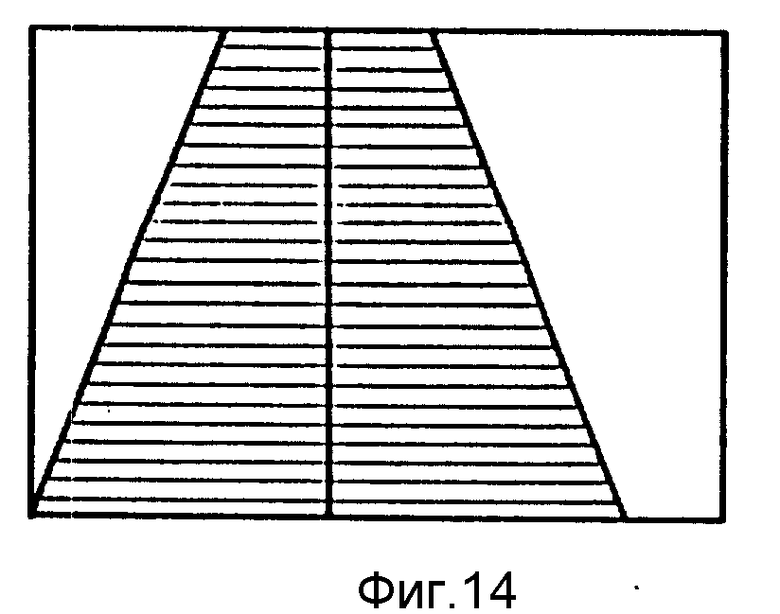

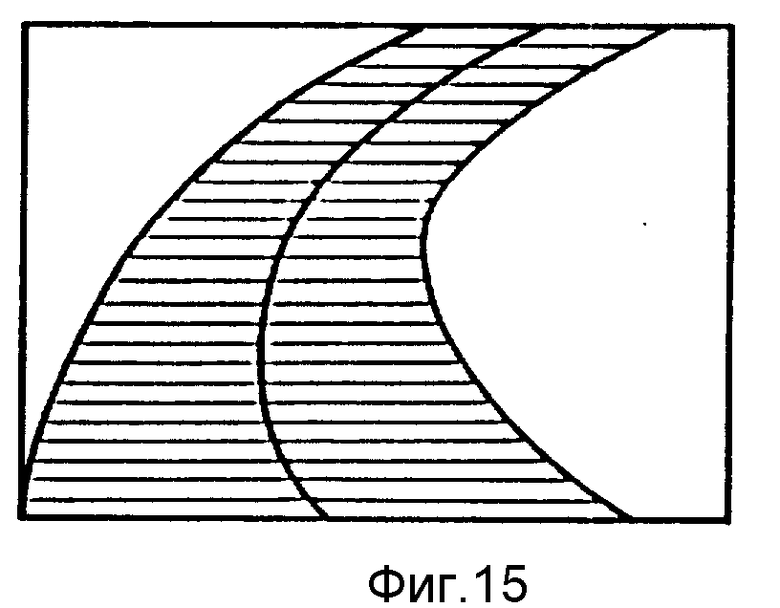

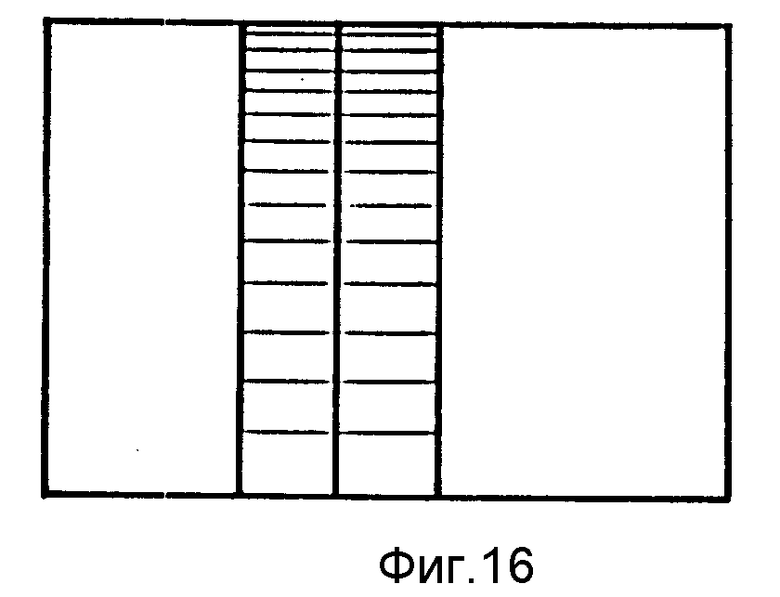

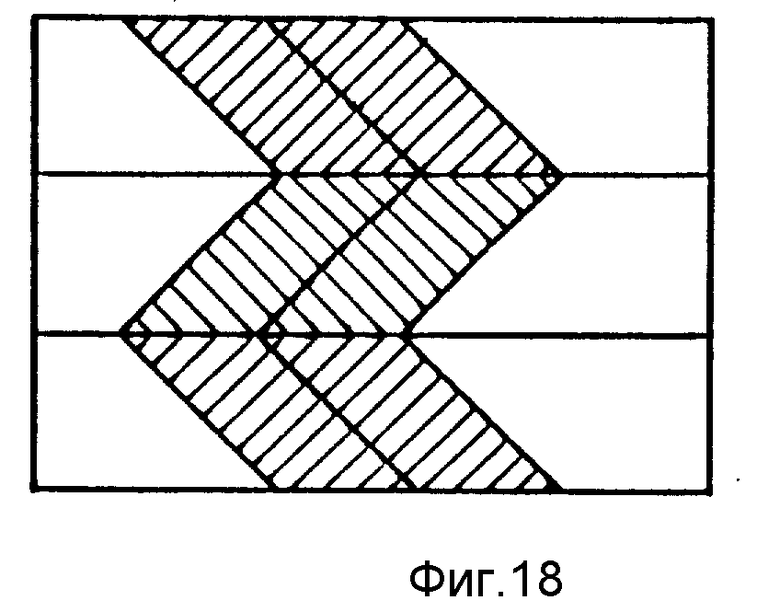

На фиг. 13 приведена схема, иллюстрирующая пример воспроизведения первоначального (оригинала) изображения заднего фона, в то время как на фиг. 14 - 18 приведены схемы, показывающие то же изображение, но в увеличенном, повернутом, уменьшенном или совместно трансформированном виде. И, наконец, на фиг. 19 изображена блок-схема телеигровой установки (приставки) известного стандартного типа.

Несмотря на то, что предпочтительный вариант исполнения изобретения рассматривается применительно к видеопроцессору для телевизионноигрового автомата, следует помнить, что, в принципе, изобретение применимо для видеопроцессоров самого различного назначения, в частности для персонального компьютера (ЭВМ) с неигровым назначением, который может быть подключен к электронно-лучевому дисплею с растровой разверткой, и т.п.

На фиг. 1 показана блок-схема телеигрового аппарата, представляющего собой один из вариантов исполнения данного изобретения.

Прежде чем перейти к анализу этой схемы, целесообразно сказать несколько слов об устройстве видеоотображения (дисплее), применяемом в данном случае. Обычно в качестве устройства видеоотображения в телеигровых аппаратах используется растрово-разверточный электронно-лучевой дисплей типа видеоконтрольного устройства с входными сигналами RGB (PCB - монитора; PCB - красно-зелено-синий) или стандартного телеприемника, если экран разделен на 256 • 256 точек (элементов изображения). Однако ввиду того, что изображение не может с достаточной точностью воспроизводиться на участках нескольких строк с верхней и нижней сторон экрана, что предопределяется кривизной поверхности электронно-лучевой трубки, фактически для воспроизведения по вертикали используются 224 точки. Следовательно, если один знак, являющийся минимальным элементом заднего фона (и/или движущегося изображения), состоит из 8 х 8 точек, тогда на экране одновременно может быть воспроизведено 32 х 28 = 896 знаков.

Рассматриваемый телеигровой аппарат устроен таким образом, что изображение заднего фона (т.е. неподвижное или медленно перемещающееся изображение), образующее, по существу, задний план, который не может изменяться индивидуально играющим (оператором), и подвижное изображение, которое перемещается оператором или же в результате автоматизированного управления от центрального процессора ЦП 2 (CPU 2), контролируются независимо. Этот игровой аппарат содержит блок 1 обработки изображений, выводящий на электронно-лучевой дисплей 8 видеосигнал в виде комбинации изображения заднего фона и движущегося изображения, воспроизводимых одновременно на указанном дисплее. Здесь уместно обратить внимание на то, что рассматриваемый телевизионный игровой аппарат (установка, приставка) отличается тем, что в состав процессорного блока 1 входит управляющая схема или блок 24 адресации изображения (элементов изображения) заднего фона, которая определяет адрес считывания видеоданных по изображению заднего фона из видеозапоминающего устройства с произвольной выборкой 7 (VPAM 7) при осуществлении информационной обработки по повороту и/или увеличению или уменьшению этого изображения и при этом только изменяет считываемый адрес, не затрагивания, не изменяя видеоданных, используемых при осуществлении поворота, увеличения или уменьшения размеров упомянутого изображения.

В схеме, представленной на фиг. 1, постоянное запоминающее устройство ПЗУ 3 (ROM), ЗУПВ (RAM) 4 и коммутационная панель 5 подключены к центральному процессору ЦП 2 (CPU 2), осуществляя разнообразный контроль за работой телеигрового аппарата через адресную шину 11, информационную шину данных 12 и управляющую шину 13.

ПЗУ 3 служит для записи, хранения программных данных, необходимых для управления рассматриваемым телеигровым аппаратом, данных, необходимых для выполнения программ (команд), и знаковых данных. Это запоминающее устройство размещается, к примеру, в кассете (не показана), вставляемой или извлекаемой из телеигрового аппарата. Программные данные включают в себя данные для определения типа подвижного знака и/или знака заднего фона, воспроизводимого на экране, времени, когда знак должен быть воспроизведен, и координатного положения его на экране, а также служебные данные, необходимые для поворота, увеличения или уменьшения изображения заднего фона, и т.п. В состав данных по движущемуся знаку (атрибутам отображения подвижного изображения) входят данные по горизонтальному положению (Hc : 8 бит), используемые для идентификации положения знака при горизонтали, данные по вертикальному положению (Vc: 8 битов), код знака (9 бит), определяющий тип знака, код цветовой палитры (3 бита), разрешающий кол (2 бита) для обозначения реверса знака по вертикали и горизонтали, код размера (1 бит) для идентификации размера точек, образующих знак, и приоритетные данные (2 бита) для обозначения приоритета подвижного изображения по отношению к изображению заднего фона. В качестве данных каждого знака изображения заднего фона используются знаковый код (8 битов) для идентификации типа знака; данные по цветности каждого из элементов изображения, образующих знак, и т.п. Совокупность знаков заднего фона отображается в комбинации, воспроизводящей изображение заднего фона (неподвижное или медленно перемещающееся кадровое изображение); в свою очередь, множество подвижных знаков при отображении воспроизводят движущееся изображение. Изображение заднего фона и движущееся изображение воспроизводятся на экране совмещено. Характерно то, что в состав данных, используемых для воспроизведения того или иного изображения заднего фона, входит код знака этого фона, соответствующий каждому адресу формируемого изображения и определяющий таким образом, какой из знаков заднего фона должен быть записан в тот или иной адрес из совокупности адресов по вертикальному и горизонтальному направлениям в задействуемой области 40 ВЗУПВ, а следовательно, и воспроизведен на экране в заданном положении (координатах), соответствующем используемому адресу.

ЗУПВ 4 используется как рабочая область вышеупомянутого центрального процессора ЦП 2. Клавишная панель 4 используется играющим для ввода информации по управлению движущимися знаками.

Далее следует указать, что в состав видеопроцессорного блока 1 входит интерфейс 21 центрального процессора. Интерфейс (устройство сопряжения) 21 подключен к ЦП 2 (CPU 2) через адресную шину 11, информационную шину 12 и управляющую шину 13. На выходе к блоку 1 подключаются генератор 6 опорного сигнала, видеозапоминающее устройство с производной выборкой ВЗУПВ 7 (VPAM 7), состоящее из двух ЗУПВ (7a, 7b), и ЭЛТ - дисплей (CRT) 8 типа видеоконтрольного устройства 8а с RGB - входными сигналами или стандартного телеприемника 8b.

Блок 1 обработки видеоизображений функционирует под управлением центрального процессора ЦП 2 и используется для трансляции видеоданных по движущемуся изображению и неподвижному изображению заднего фона в видеопамять ВЗУПВ 7 в течение периода гашения обратного хода кадровой развертки или же принудительно синхронизированно со считыванием видеоданных по движущемуся изображению и/или изображению заднего фона, записанных в ВЗУПВ 7, без изменения или извлечения видеоданных, получаемых в результате осуществления операций информационной обработки по повороту, увеличению или уменьшению изображения, что является отличительным признаком данного изобретения. В конечном итоге процессорный блок 1 преобразует видеоданные в RGB - видеосигнал (трехцветовой сигнал) и/или цветовой сигнал в системе НТСЦ с выводом его на дисплей.

Если говорить более точно, блок 1 обработки видеоизображения включает в себя интерфейс 21 центрального процессора; управляющий блок 22 адресации движущегося изображения; блок 24 адресации изображения заднего фона; интерфейс 27 видеопамяти ВЗУПВ; генератор 28 цветового сигнала. Все эти средства подключены к интерфейсу 21 центрального процессора ЦП 2 через информационную шину 14. Адресная шина 15 подключена к блоку адресации 22 движущегося изображения; одновременно с этим адресная шина 15 и информационная шина 16 подключены к управляющему блоку 24 адресации изображения заднего фона и к интерфейсу 27 ВЗУПВ. Адресная шина 15 и информационная шина 16 состоят из каналов или линий 15a, 15b и 16a, 16b, соответствующих двум видеозапоминающим устройствам 7a и 7b. К шине данных 16 подключены совместно блок 23 обработки данных движущегося видеоизображения и блок 25 обработки данных по изображению заднего фона. Видеообработка информации по движущемуся изображению осуществляется с помощью схемы (блока) адресации 22 и блока 23 обработки данных такого изображения; в свою очередь, обработка информации по видеоизображению заднего фона осуществляется управляющей схемой 24 адресации такого изображения и блоком 25 обработки видеоданных по заднему фону. Выходы блока 23 обработки данных по движущемуся изображению и блока 25 обработки данных по изображению заднего фона связаны с блоком 26 контроля приоритетов, выходной сигнал которого преобразуется в трехцветовой RGB - сигнал генератором 28 сигнала цветности; указанный сигнал поступает прямо на RGB - монитор 8а и одновременно преобразуется в полный цветовой видеосигнал НТСЦ - формата в НТСЦ - кодировщике 29, с выхода 9 которого НТСЦ - видеосигнал поступает на обычный телевизионный приемник 8b.

Помимо этого в процессорный блок 1 входит генератор 30 тактового сигнала и HV - счетчик 31. Генератор 30 формирует различные хронирующие сигналы в соответствии с тактовыми импульсами с частотой 21, 417 МГц, сигналом синхронизации по вертикали и сигналом синхронизации по горизонтали, которые поступают с выхода генератора 6 опорного сигнала. HV - счетчик 31 производит подсчет данных Hc и Uc для идентификации положений воспроизведения по горизонтали и вертикали в пределах зоны отображения 41 на экране дисплея, показанной на схеме фиг. 2; эта операция осуществляется в соответствии с тактовым сигналом, сигналом синхронизации по вертикали и сигналом синхронизации по горизонтали, поступающими с генератора 6 опорного сигнала.

На фиг. 2 представлена схема, иллюстрирующая взаимосвязь между зоной отображения на экране ЭЛТ-дисплея 8 и областью записи данных по изображению заднего фона в видеопамяти ВЗУПВ 7. Зона 41 воспроизведения (отображения) изображения на экране дисплея 8 представляет, к примеру, прямоугольник, образуемый 32 знаками в горизонтальном направлении (ширина: x) и 28 знаками по вертикали (длина: y). С другой стороны, если область 40 записи (хранения) данных по изображению заднего фона (далее в тексте - "область ВЗУПВ") не содержит таких данных на той части, которая не видна (не отображается) на экране с уменьшенными размерами, на последнем в черном цвете воспроизводится только та часть изобрежения заднего фона, которая реально видна, т.е. такое изображение по существу не воспроизводится. Далее, в том случае, когда изображение заднего фона при воспроизведении перемещается вверх и вниз, если видеоданные по такому изображению переписывать в реальном времени, плавное перемещение нельзя реализовать. В соответствии с этим область 40 ВЗУПВ должна быть в несколько раз больше рабочей зоны (зоны воспроизведения) 41 в вертикальном и горизонтальном направлениях. В рассматриваемом варианте рабочая область записи 40 ВЗУПВ состоит из 128 знаков в обоих x, y - направлениях (128 • 128 = 16384), так что горизонтальное и вертикальное положение может быть идентифицировано 7-битовыми адресными данными. Код знака обратного фона, подлежащего воспроизведению, записывается в адрес, определяемый соответствующими координатными данными по направлениям X и Y. При такой адресации начало зоны 40 ВЗУПВ задается в левом верхнем конце (углу) фиг. 2 и представляется как X = O и Y = O, в то время как положение отображения соответствующей точки в зоне 40 представляется координатно-адресной функцией P (X, Y). Далее, для определения положения 53 левого верхнего конца рабочей зоны 41 воспроизведения изображения на экране дисплея по области ВЗУПВ 40 используются опорные расстояния Hp и Vp (называемые ниже "смещением") в направлениях X и Y от начала указанной области. Координаты X и Y представляются соответствующими адресными данными XC и YC (7 бит каждое), обозначающими положение знака в области 40 ВЗУПВ, и Xα и Yα (3 бита каждый), идентифицирующими положение точки в одном знаке 52 (см. фиг. 3).

Видеопамять 7 состоит из двух рабочих секций ВЗУПВ 7a и 7b (RAM 7a и 7b) с одинаковой емкостью (см. фиг. 4). Каждое из ВЗУПВ 7a и 7b имеет адреса от 0 до 32К и может запоминать по каждому адресу 8-битовые данные.

Запоминающие устройства - ступени 7a и 7b разделены на области 51 - 54 для каждого 16К. Области 51 и 52, имея адреса 0-16К, используются для регистрации данных, связанных с изображением заднего фона; в свою очередь, области 53 и 54, имея адреса (16К + 1) - 32К, используются для записи данных, касающихся движущегося изображения (т.е. множества подвижно-знаковых данных, которые должны отображаться в течение временного периода записи в область 40 ВЗУПВ данных по изображению заднего фона). Если говорить более точно, область 51 в запоминающей ступени ВЗУПВ 7а используется как знаковая зона для записи данных цветности максимум по 256 знакам изображения заднего фона. Как показано на фиг 5, один знак представляется количеством битов информации, соответствующих 8 х 8 (длина x ширина) точкам и включает в себя 8-битовые данные цветности по каждой точке. Таким образом один знак имеет емкость запоминания в 512 бит (64 байта). Для каждого знака задается знаковый код. Участок 52 в памяти ВЗУПВ 7b используется для записи определенного числа бит, соответствующих 128 х 128 (длина x ширина) ячейками области 40 ВЗУПВ, показанной на фиг. 2, и служит в качестве зоны отображения, используемой для записи кода знаков изображения заднего фона в адрес, определяющийся координатами в вертикальном и горизонтальном направлениях. На фиг. 6 в качестве примера приведены форматы данных, записываемых в области 51 и 52 рассматриваемой памяти.

Рассматривая далее фиг. 1 - 6 в совокупности, следует дать характеристику работы функциональных элементов, входящих в схему фиг. 1. При управляющем воздействии центрального процессора ЦП 2 (CPU 2) его интерфейс 21 передает на интерфейс 27 запоминающего устройства с произвольной выборкой ВЗУПВ данные, касающиеся знака заднего фона и подвижного знака; эта операция осуществляется при прямом обращении к памяти в течение периода гашения обратного хода кадровой развертки или под действием внешней команды. Одновременно с этим генерируются блокировочные сигналы LA 1 - LA 4, LA 11, LA 12, LA 14 и LA 15 для передачи управляющих данных по повороту, увеличению или уменьшению изображения заднего фона в схему адресации 24 данных этого изображения. Данные по знаку (символу) заднего фона и знаку движущегося изображения записываются с опережением в ВЗУПВ 7 интерфейсом 27 этой памяти.

Управляющий блок 22 адресации данных движущегося изображения содержит атрибутивную память этого изображения, схему внутримассивного детектирования (поиска) и схему формирования данных адресации движущегося изображения, подробное описание которых имеется в патентных источниках, в частности в выкладке японского патента, опубликованной в ведомственном бюллетене Патентного ведомства Японии за N 118184/1984, автором изобретения по которому является заявитель настоящей патентной заявки. Атрибутивные (признаковые) данные по 128 подвижным знакам воспроизводимого изображения транслируются в упомянутую атрибутивную память из центрального процессора ЦП 2 через его интерфейс 21 и шину данных 14 и записываются в эту память в течение периода гашения обратного хода кадровой (полевой) развертки. Вышеупомянутая схема детектирования осуществляет поиск и выборку данных каждой строчки развертки, которая должна быть воспроизведена в следующем цикле реализации развертки по горизонтали, из массива данных, записанных в атрибутивную память движущегося изображения переднего плана. В свою очередь, схема адресных данных по движущемуся изображению формирует адрес памяти ВЗУПВ 7, определяющий обратное (перевернутое) положение в зоне 41 воспроизведения на экране дисплея, выводя этот адрес через адресную шину 15, когда V-триггераные (инвертированные) данные, получаемые в результате внутримассивного поиска и выборки по атрибутивным данным, имеют уровень "Н". С другой стороны, указанная схема выдает адрес памяти ВЗУПВ 7, соответствующий расположению видеознаковых данных в рабочей зоне воспроизведения 41 на экране дисплея, в указанное запоминающее устройство 7 через адресную шину 15 без каких-либо преобразований, когда V-триггерно инвертируемые данные выходят на уровень "L". С поступлением информации по адресу запоминающее устройство ВЗУПВ 7 выдает на схему 23 обработки данных по движущему изображению через информационную шину 16 данные цветности (4 бита на точку) указанного движущегося изображения, записанные в области 53 и 54 знаков этого изображения, соответствующих адресам, выданным со схемы формирования адресных данных на управляющую схему 22 адресации движущегося изображения. Далее, схема формирования адресных данных по движущемуся изображению подает непосредственно на схему 23 обработки информации по такому изображению Н-триггерно инвертируемые данные (1 бит), цветовые данные по элементу изображения (3 бита) и приоритетные данные (2 бита) из числа признаков данных подвижных знаков, выбранных в результате вышеупомянутого внутримассивного поиска.

Таким образом 10-битовые данные по каждой точке изображения, включающие в себя данные цветности, считанные из памяти ВЗУПВ 7, H- триггерные данные, данные по цветному элементу изображения и приоритетные данные, поступающие непосредственно с управляющего блока 22 адресации движущегося переднепланового изображения, вводятся в блок 23 обработки данных по указанному изображению, неся информацию по 256 точкам строчной развертки.

В процессе этого процессорный блок 23 производит оперативную запись данных по следующей строчке развертки, которые вводятся в течение периода гашения обратного хода строчной развертки, а затем оперативно записывает 9-битовые видеоданные по каждой точке, исключая H-триггерированные данные, входящие в состав данных с обратным порядком по отношению к порядку ввода, когда H-данные находятся на уровне "Н", с осуществлением Н-триггерной обработки. В свою очередь, указанный процессорный блок 23 осуществляет оперативную запись 9-битовых данных в порядке ввода, когда H-триггерируемые данные имеют уровень "L". Временно (оперативно) запомненные данные по одной строчке движущегося изображения выводятся на управляющую приоритетную схему 26 синхронизированно с горизонтальной разверткой и в соответствии с данными счета Hc, поступающими от HV - счетчиками 31.

В процессе информационной обработки данных по изображению заднего фона управляющая адресная схема 24 вычисляет текущий считывающий адрес (16 бит) знакового кода, ранее записанный на участке 52 в память 7b и соответствующий точке указанного изображения, причем такое вычисление осуществляется на основе данных по смещению Hp, Vp на экране и управляющих инструктивных данных, в состав которых входят H-триггерно инвертируемые данные HF и V-триггерные данные VF, которые поступают с ЦП 2, а также с учетом данных счета Hc и Vc, поступающих от HV-счетчика 31, засылая в конечном итоге адрес в память ВЗУПВ 7b через адресную шину 15b. Дополнительно следует указать, что во время обработки данных по повороту, увеличению или уменьшению изображения заднего фона управляющая адресная схема 24 вычисляет текущий считываемый адрес знакового кода, соответствующий точке изображения заднего фона; эта операция осуществляется на основе данных смещения Hp, Vp на экране, H-триггерных данных HF, V-триггерных данных VF и параметрических данных, включающих в себя рабочие константы A, B, C и D, используемые при обработке информации по повороту, увеличению или уменьшению изображения и задаваемые центральным процессором ЦП 2, а также данных счета Hc и Vc, поступающих от HV-счетчика 31. Вычисляемый адрес подается в видеопамять 7b. Сам алгоритм операционной обработки данных по повороту, увеличению или уменьшению изображения заднего фона будет рассмотрен несколько ниже применительно к фиг.7.

Далее следует указать, что управляющая схема 24 адресации данных изображения заднего фона осуществляет также определение считываемого адреса знакового кода, соответствующего одной точке указанного изображения, после осуществления обработки данных по перемещению изображения на экране; эта вычислительная операция производится на основе данных смещения Hp и Vp на экране, поступающих от ЦП 2. Одновременно с этим схема 24 вычисляет считываемый адрес знакового кода, соответствующий точке изображения заднего фона; эта операция осуществляется после H-триггерной обработки, когда H-триггерированные данные HF находятся на уровне "H". Помимо этого указанная схема производит расчет считываемого (текущего) адреса знакового имени, соответствующего точке изображения заднего фона после осуществления V-триггерной обработки, когда V-триггерированные данные VF находятся на уровне "H". Наиболее важные по значимости два бита 16-битовых данных по текущему адресу, вычисляемому задающей схемой 24 адресации изображения заднего фона, равны "00", в то время как менее приоритетные 14 битов указанных данных представляют собой позиционные данные Xc и Yc (7 бит каждое) по положению знака, соответствующие положению воспроизведения изображения заднего фона (см. фиг. 6).

Запоминающее устройство ВЗУПВ 7b выдает знаковый код, записанный в адрес, определяемый управляющей схемой 24 адресации данных заднего фона, на эту схему через шину данных 15b. Соответственно адресная схема (блок) 24 выдает в память ВЗУПВ 7a через адресную шину 24 адрес, содержащий наиболее значительные по приоритету два бита "00", восьмибитовый знаковый код и позиционные данные Yα (3 бита) и Xα (3 бита) по положению точки, соответствующему положению воспроизведения изображения заднего фона. Память ВЗУПВ 7a считывает 8-битовые данные по цветности, записанные в адрес, задаваемый управляющей схемой адресации 24, засылая их через шину данных 16a в процессорный блок 25 обработки данных по изображению заднего фона. Процессор 25 фиксирует (защелкивает) входящие данные цветности, составляющие 8 бит на точку, и затем выдает их на управляющую схему приоритетов 26, что реализуется на основе данных счета Hc, поступающих с выхода HV-счетчика 31.

Управляющая (задающая) схема 26 определяет приоритет между семибитовыми данными по движущемуся изображению, поступающему с блока 23 обработки таких данных, и восьмибитовыми данными по изображению заднего фона, поступающими с блока 25 обработки таких данных; установление приоритетности производится на основе данных по приоритету. С выхода схемы 26 на генератор 28 сигнала цветности поступает высокоприоритетные данные, выбранные из общей совокупности данных по движущемуся изображению и данных изображения заднего фона. К примеру, управляющая схема 26 приоритетов может "выдавать" на выход и далее на генератор 28 данные по изображению заднего фона, содержащие три наиболее важных бита "000" и восьмибитовые данные цветности, когда данные по приоритету составляют "00", и наоборот: выдавать на выход данные по движущемуся изображению переднего фона в суммарном формате 7 бит, содержащем 8-битовые данные по цветовой палитре и 4-битовые данные цветности, когда данные по приоритету равны "01".

Генератор 28 сигнала цветности имеет таблицу цветовой палитры, формируемую на основе ЗУПВ, имеющего восьмибитовые адреса и запоминающего данные по сигналу цветности, проступающие с ЦП 2 в указанную таблицу в течение периода гашения обратного хода кадровой развертки. В течение периода гашения обратного хода строчной развертки генератор 28 сигнала цветности считывает данные по сигналу цветности, хранящиеся в соответствующем адресе таблицы цветности, в соответствии с восьмибитовыми данными по движущемуся изображению или данными по изображению заднего фона, поступающими с блока 26 приоритетов, и затем преобразует данные сигнала цветности в трехцветовой RGB - сигнал (красный - зеленый - голубой) с 5 битами на каждый цвет. Сформированный таким образом RGB - сигнал поступает с генератора 28 на RGB - монитор (видеконтрольное устройство) 8a синхронизованно с данными счета Hc и Vc, поступающими от HV-счетчика 31, и одновременно на кодирующее устройство 29, работающее в системе НТСЦ. Устройство 29 осуществляет цифроаналоговое преобразование RGB - сигнал по каждому цвету с последующим переводом этого сигнала в полный цветовой видеосигнал НТЦС, который поступает на стандартный телеприемник 8b с выходной клеммы 9.

На фиг. 7 приведена схема, поясняющая принцип обработки данных по повороту, увеличению или уменьшению изображения заднего фона, осуществляемой схемой 24 адресации указанного изображения. На фиг. 7 X-координата каждой точки в горизонтальном направлении на экране ЭЛТ-дисплея 8, а Y-координата точки по вертикали. Здесь уместно отметить, что направление ординаты "Y" на фиг.7 обратно аналогичной координате на фиг.2.

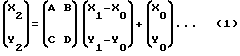

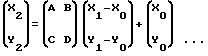

Примем за P(X1, Y1) координатное положение первоначального изображения заднего фона перед осуществлением схемой адресации 24 поворотной обработки и обработки по увеличению сил уменьшению указанного изображения и одновременно будем рассматривать Q(X'2, Y'2) в качестве координатного положения упомянутого изображения после поворота из первоначального положения вокруг точки R(X0, Y0) на угол γ (рад). Далее, примем Q(X2, Y2) за координаты изображения заднего фона после его увеличения или уменьшения относительно положения Q'(X'2, Y'2) с соответствующим масштабом α в направлении X и с масштабным пересчетом β в направлении Y при использовании в качестве координатной точки отсчета R(X0, Y0). В этом случае соотношение между координатами P, R и Q выражается следующей зависимостью (I):

В этом соотношении константы (параметры) A, B, C и D выражаются следующим образом:

В этом случае, когда изображение заднего фона подвергается только поворотному преобразованию без увеличения или уменьшения, α = β = 1 . В этом случае константы A, B, C и D выражаются как A= cosγ ... (6), B= sinγ ... (7) C= -sinγ ... (8) D= cosγ ...(9).

Далее, когда поворот изображения заднего фона не производится, а выполняется только увеличение или уменьшение его размеров, γ =0. в этом случае константы A, B, C и D выражаются по следующим формулам (10) - (12):

В формуле (1) координаты P (X1, Y1) первоначального изображения заднего фона описываются нижеприводными зависимостями (13) и (14) от вышеупомянутых значений смещений Hp и Vp в области 40 запоминающего устройства ВЗУПВ (см. фиг.2) и данных счета Hc и Vc на выходе VH - счетчика 31:

X1=Hp+Hc...(13), Y1=Vp+Vc...(14).

При подстановке формул (13, 14) в параметрическое выражение (1) переменные X2 и Y2 представляются следующими формулами (15) и (16):

X2=[Xо+(Hp-Xо)•A+(Vp-Yо) •B+VcB]+Hс•A... (15)

Y2=[Yо+(VpYо)•D+(Hp-Xо) •C+Vc•D]+Hc•C...(16)

В формулах (15) и (16) члены Hc•A и Hc•C изменяются от точки к точке на экране, в то время как другие члены (скобочные выражения) не изменяются на протяжении одной строчки развертки. Таким образом, члены Hc•A и Hc•C должны вычисляться для каждой точки на протяжении периода строчной развертки. С другой стороны, в этот период нет необходимости вычислять другие члены. Здесь следует указать, что вычисление указанных членов формул (15), (16) во времени является довольно труднореализуемым процессом, поскольку на каждую точку строчной развертки отводится очень малое время. Исходя из этого, рассматриваемые члены вычисляются в совокупности перед началом развертки соответствующей строчки (предварительная вычислительная обработка данных). В целях вычисления составляющих по заранее рассчитываемым формулам (15) и (16) в упрощенном варианте указанные формулы заменяются нижеприводимыми выражениями (17) - (24), расчет по которым ведется пошагово-численным методом:

E1 = Hp - Xо (17); E2 = Vp - Yо (18); E3 = Xо + E1 A (19)

E4 = Yо + E2 D (20); E5 = E3 - E2 B (21); E6 = E4 - E1 C (22)

E7 = E5 - Vc B (23); E8 = E6 - Vc D (24).

Далее следует обратиться к фиг. 8, 9, на которых представлена структурная схема вышеупомянутого задающего блока 24 адресации данных по изображению заднего фона. Этот блок оценивает координаты (X2, Y2) во время поворота, увеличения или уменьшения указанного изображения по матричному алгоритму с использованием вышеприведенного уравнения (1), формируя в конечном итоге соответствующие координатные данные, представляющие считываемый (текущий) адрес участка 52 экрана и считываемый адрес знакового участка 51.

В более точной формулировке адресная схема 24 включает в себя регистры FF 1 - FF 23, каждый из которых состоит из набора D-триггеров с задержкой. Каждый из этих регистров фиксирует (защелкивает) данные, поступающие на его входную клемму одновременно с сигналом блокировки (фиксации), выводя соответствующие данные на его выходную клемму. Помимо этого на входы регистров FF 13 - FF 19 поступают инвертированные тактовые (синхронизирующие) импульсы, формируемые в результате инвертирования импульса 10 МСК частотой 10,739 МГц, поступающего с выхода генератора 30 синхросигнала. В свою очередь, на входы регистров FF 18, FF 20, FF 21, FF 22 и FF 23 поступают инвертированные тактовые импульсы, формируемые в результате реверсивного обращения, преобразования тактового сигнала 5 МСК с частотой 5,369 МГц, формируемого генератором 30.

16-битовые данные по константам A, B, C и D, поступающие от ЦП 2 через интерфейс 21 центрального процессора и шину данных 14, защелкиваются соответствующим образом в регистрах FF 1 - FF 4 одновременно с приходом соответствующих сигналов блокировки LA 1 - LA 4. Фиксируемые данные передаются на входные клеммы a, b, c, d коммутатора (переключающего устройства) SW 1. Этот коммутатор производит селекцию поступающих данных, выбирая одно из них и передавая далее на входные клеммы умножителя MPY в соответствии с XS -сигналов, поступающих от генератора 30-тактового (синхро-) сигнала.

Данные счета Hc с выхода HV-счетчика 31 вводятся в логическую схему (ячейку) ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 1. Регистр FF 5 защелкивает (фиксирует) восьмибитовые данные счета Vc, поступающие с выхода HV-счетчика 31, направляя их далее на логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 2. В свою очередь, регистры FF 6 и FF 7 защелкивают соответственно однобитовые H-триггерированные данные HF и однобитовые V-триггерированные данные VF, поступающие от ЦП 2, с приходом задающего тактового импульса от того же центрального процесса, передавая на схемы ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 1 и XOR 2 соответственно H-триггерированные данные HF и данные из 8 битов, имеющие такой же уровень, и V-триггерированные данные VF плюс данные 8 битов, имеющие тот же уровень.

Принцип действия логических схем ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 1 и XOR 2 рассматривается ниже. Каждая из этих схем содержит восемь вентилей исключающего ИЛИ. На определенные входы вентилей схемы XOR 1 поступают соответствующие биты данных счета Hc, на другие выходы - соответствующие биты данных из регистра FF 6. В свою очередь, на часть входов восьми вентилей схемы XOR 2 поступают определенные биты данных счета Vc, на другие входы - соответствующие биты данных (числа) с регистра FF 7. Рассматриваемые вентили в составе логических схем XOR 1 и XOR 2 ИСКЛЮЧАЮЩЕЕ ИЛИ выполняют операцию строгой дизъюнкции по соответствующим двум входам, формируя на выходе восьмибитовые данные, которые поступают на входные клеммы a и b коммутатора SW 2, напрямую или через регистр FF 8. Переключающее устройство SW 2 имеет выходные клеммы с 11 разрядами каждая, при этом наиболее значимые по приоритету (весу) три разряда каждой входной клеммы a и b заземлены. Помимо этого рассматриваемое переключательное устройство имеет входные клеммы c и d, на которые поступают 11-разрядные данные с регистров FF 9 и FF 10 соответственно.

Регистр FF 9 защелкивает наименее приоритетные 11 битов (E1) 18-разрядных данных, поступающих от сумматора АДД; эта операция начинает реализоваться по переднему фронту сигнала блокировки (фиксации) LA 9, поступающего с выхода генератора 30 синхросигнала. Защелкиваемые данные подаются на входные клеммы c переключающего устройства SW 2. В свою очередь, регистр FF 10 защелкивает данные с наименьшими приоритетами 11 разрядами (E2) из числа 18-битовых данных, поступающих с упомянутого суммирующего устройства АДД; эта операция осуществляется с приходом переднего фронта сигнала блокировки (фиксации данных) LA 10 с выхода синхрогенератора 30. Защелкнутые данные поступают далее на входные клеммы d переключающего устройства SW 2. Это устройство производит селективную выборку одного из данных, приходящих на входные клеммы a, b, c, d, на основе YS сигнала, поступающего с выхода генератора 30 синхросигнала, подавая отселектированное число (данное) на входные клеммы b умножителя МРУ.

Множительное устройство МРУ производит умножение одного из данных A - D, приходящих на входные клеммы a, на одно из данных E1, E2 и Vc, поступающих на входные клеммы b, оценивая численно второй член в одном из выражений (19) - (24) и формируя на выходе данные, представляющие результат умножения и поступающие далее на входные клеммы c переключательного устройства SW 3 через регистр FF 13.

Регистр FF 11 защелкивает данные сдвига (смещения) Hp (10 битов) в направлении "x", поступающие от центрального процессора ЦП 2 (CPU 2); эта операция осуществляется с приходом переднего фронта задающего импульса. С выхода регистра FF 11 данные поступают на входные клеммы a переключающего устройства SW 3. В свою очередь, регистр FF 12 защелкивает данные сдвига Vp (10 битов) в направлении "y", поступающие от ЦП 2; эта операция также осуществляется с поступлением переднего фронта задающего импульса. С выхода регистра FF 12 данные выводятся на входные клеммы b коммутатора SW 3. Наиболее значимые по приоритету 6 разрядов и наименее значимые 2 разряда каждой из входных клемм a и b переключающего устройства SW 3 заземлены. Наименее значимые по приоритету два бита данных, поступающих на каждую из входных клемм переключающего устройства SW 3, соответствуют данным после десятичной запятой.

Переключающее устройство SW 3 селективно выбирает одно из данных, поступающих на входные клеммы a, b и c, в соответствии с сигналом AS, приходящим с выхода генератора 30, и подает отселектированное данное на входные клеммы сумматора АДД.

Регистр FF 14 защелкивает данные X0 по положению в направлении "x" изображения заднего фона. Эти данные поступают с ЦП 2 ( защелкивание осуществляется по наименее значимым восьми разрядам информационной шины 14). Операция защелкивания (фиксации) данных выполняется с приходом переднего фронта задающего тактового импульса. Затем полные данные в формате 10 битов, в состав которых входят два наиболее значимых по приоритету бита "00", и защелкнутые данные поступают на входные клеммы переключающего устройства SW 4. В свою очередь, регистр FF 15 защелкивает данные Yo по положению изображения заднего фона в направлении Y; эти данные поступают с ЦП 2 (наиболее значимые два бита превосходят вышеупомянутые данные Xo информационной шины 14) при появлении переднего фронта задающего импульса. На выход указанного регистра поступают данные в сумме 10 битов, содержащих восемь наиболее значимых по весу битов "00000000", и защелкнутые данные; все эти данные подаются на входную клемму b переключающего устройства SW 4. Наиболее значимые шесть разрядов и наименее значимые два разряда входных клемм a и b коммутатора SW 4 подключены на землю. Наименее значимые два бита данных, приходящих на каждую из входных клемм переключателя SW 4, представляют собой числовые значения после десятичной запятой.

Регистр FF 16 производит фиксационное защелкивание 18-разрядных данных, поступающих с выхода суммирующего блока АДД, по переднему фронту тактового импульса СК 16, поступающего от генератора 30 синхросигнала. Выход этого регистра связан с вводами c переключающего устройства SW 4. В свою очередь, регистр FF 17 осуществляет защелкивание 18-разрядных данных, поступающих с выхода сумматора АДД; эта операция инициализируется по переднему фронту тактового импульса СК 17, приходящего с выхода генератора 30 синхросигнала. Выходной сигнал регистра FF 17 подается на входные клеммы d переключающего устройства SW 4. Это устройство в ответ на поступление данных на его вводы a, b, c, d подает 18-битовые данные на схему ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 при поступлении сигнала BS с выхода синхросигнального генератора 30. Схема строгой дизъюнкции XOR 3 содержит 18 вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ. Определенные биты данных, поступающих в переключающее устройство SW 4, подаются на соответствующие входы вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом на другие входы поступает сигнал ADS с выхода синхрогенератора 30.

Далее, определенный один бит сигнала ADS вводится на клемму переноса сумматора АДД. При поступлении одного бита сигнала ADS на упомянутую клемму сумматора АДД, если этот сигнал имеет уровень "H", сигнал ADS, подаваемый на соответствующие другие входные клеммы вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ схемы XOR 3, представляет собой сигнал, в котором все 18 разрядов имеют уровень "H". Когда один бит сигнала ADS, подаваемый на клемму переноса сумматора АДД, имеет уровень "L", сигнал ADS, поступающий на другие входные клеммы вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ в логической схеме XOP 3, представляет собой сигнал, в котором все 18 разрядов имеют уровень "L". Логическая схема XOP 3 ИСКЛЮЧАЮЩЕЕ ИЛИ функционирует точно таким же образом, как схемы XOR 1 и XOR 2. Это означает, что схема XOR 3 осуществляет логическую операцию строгой дизъюнкции с данными, поступающими на одну из входных клемм, и данными, приходящими на другие входные клеммы, по отношению к каждому биту (разряду), выдавая результаты такого логического операционного действия на входные клеммы b суммирующего устройства АДД.

Сумматор АДД производит сложение обоих данных, поступающих на вводы a и b, и, кроме того, прибавляет единицу к результатам сложения в случае, когда на клемму переноса поступает сигнал ADS с уровнем "H". Далее следует указать, что независимо от результатов сложения 18-битовые данные записываются в регистры FF 16 и FF 17, данные по наименее значимым 11 битам записываются в регистры FF 9 и FF 10, 10-битовые данные - в регистры FF 18 и FF 19, а данные по наименее значимым восьми битам - в регистры FF 21.

При поступлении сигнала "H" на клемму переноса на схеме ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 и сумматоре АДД осуществляется операция вычитания выходных данных переключающего устройства SW 4 их выходных данных переключающего устройства SW 3. В свою очередь, с появлением на упомянутой клемме сигнала "L" обратная операция логической схемой XOR 3 и операция прибавления 1 сумматором АДД не осуществляются. Вместо этого проводится операция сложения выходных данных переключающего устройства SW 3 с выходными данными переключающего устройства SW 4. В рассматриваемом варианте процессора умножитель МРУ и сумматор АДД многократно осуществляют операции умножения или сложения двух данных (данное по координате, данное по константе или данное по результатам предыдущего операционного действия), поступающих при переключении с коммутатора SW 1 на коммутатор SW 4 с временным разделением и синхронизацией при последующем выполнении операций вычислений по формулам (17) - (24) и в заключении - операций по формулам (15) и (16) по соответствующим операционным циклам с задействованием соответствующих функциональных блоков. Примечательно то, что информационная обработка по повороту и/или увеличению или уменьшению изображения заднего фона может осуществляется с использованием общей операционной схемы при изменении константных данных.

Регистр FF 18 защелкивает поступающие на него десятиразрядные данные, формируя на их основе выходные данные Yc по наиболее значимым семи битам в виде адресных данных от третьего до восьмого бита по наиболее значимому разряду адресной шины 15b с проводкой этих выходных данных через трехпозиционный буферный усилитель (ниже в тексте -просто "буферный усилитель") ВА2; кроме того, регистр FF 18 выдает данные Yα по наименее значимым трем битам на регистр FF 22. Регистр FF 19 защелкивает 10-битовые данные, поступающие на его вход, выдавая их далее на регистр FF 20. Регистр FF 20 защелкивает поступающие на его 10-битовые данные, формируя на выходе данные Xc по наиболее значимым семи битам в виде адресных данных по наименее значимым семи разрядам адресной шины 15b с прохождением этих данных через буферный усилитель ВАЗ; кроме того, регистр FF 20 подает данные Xα по наименее значимым трем битам на регистр FF 22.

Регистр FF 21 защелкивает 8-битовые данные по знаковому коду, поступающие от запоминающего устройства ВЗУПВ 7b через информационную шину 16b, выдавая их далее в виде адресных данных от третьего до седьмого бита по наиболее значимому разряду адресной шины 15b через буферный усилитель ВА5. В свою очередь, регистр FF 22 защелкивает два трехбитовых данных Yα и Xα , поступающих на его вход, выдавая на выходе адресные данные по наименее значимым шести разрядам адресной шины 15a через регистр FF 23 и буферный усилитель ВА6.

Примечательно то, что входные клеммы по двум разрядам буферного усилителя ВА1 подключены на землю, в то время как его выходные клеммы (2 разряда) связаны с наиболее значимыми двумя разрядами адресной шины 15b. Аналогичным образом входные клеммы по двум разрядам буферного усилителя ВА4 подключены на землю, в то время как выходные клеммы (2 разряда) связаны с наиболее значимыми двумя разрядами адресной шины 15a.

На фиг. 10-12 представлены временные эпюры (гистограммы), поясняющие алгоритм информационной обработки по увеличению, уменьшению и/или повороту изображения заднего фона в рассматриваемой аппаратурной системе. На гистограмме фиг. 10 показаны период строчной развертки и период строчного гасящего импульса; на фиг. 11, 12 показаны периоды предобработки данных и части длительности обработки в реальном масштабе времени в случае, когда значение счетной величины H в качестве примера равно 9 - 17,5.

Ниже при рассмотрении в динамике фиг.1 - 12 дается подробное описание процесса обработки данных по увеличению, уменьшению и/или повороту изображения заднего фона, т. е. той информационной обработки, которая составляет существо притязаний изобретения, предопределяя его новизну. Описание сформулировано применительно к функционированию управляющего блока 24 адресации данных изображения заднего фона при осуществлении обработки одной строки развертки в случае, когда упомянутое заднефоновое изображение, ограниченное в зоне 41 дисплейного экрана на общей рабочей площади (области) 40 видеозапоминающего устройства ВЗУПВ (см. фиг.2), поворачивается вокруг опорной координатной точки P (Xo, Yo) на угол γ и увеличивается или уменьшается в масштабе α в направлении X и масштабе β в направлении Y (см. фиг.7).

При реализации рассматриваемой обработки видеоданных константы A, B, C и D, вычисленные заранее в центральном процессоре ЦП 2 по вышерассмотренным формулам (2) - (5) на основе α , β и γ , и параметрические данные, зависящие от этих констант и также вычисляемые заранее в упомянутом процессоре, вводятся в триггерные регистры FF 1 - FF 4 из ЦП 2 через его интерфейс 21 и шину данных 14, где и защелкиваются. В дополнение к этому с выхода ЦП 2 на входы триггерных регистров FF 1, FF 12, FF 14, FF 15, FF 6 и FF 7 через интерфейс 21 процессора и информационную шину 14 поступают вышеупомянутые данные по смещению (сдвигу) Hp и Vp на экране, данные Xo и Yo, представляющие ранее упоминавшиеся опорные координаты, а также H-инвертируемые данные HF и V - инвертируемые данные VF по изображению заднего фона; на указанных регистрах эти данные подвергаются фиксационному защелкиванию.

Далее осуществляется инвертирование данных Hc, поступающих от HV - счетчика 31; эта операция выполняется вентильной схемой XOR 1 ИСКЛЮЧАЮЩЕГО ИЛИ, с выхода которой данные попадают на вводы переключающего устройства SW 2, когда H-триггерируемые данные HF находятся на уровне "H". В свою очередь, эти же данные Hc при поступлении от счетчика HV 31 на входные клеммы коммутатора SW 2 проходят через логическую схему XOR 1 без изменения, когда данные HF имеют уровень "L". Далее, данные Vc, поступающие с HV-счетчика 31 и защелкиваемые в триггерном регистре FF 5 в процессе обработки строки развертки, реверсируются логической вентильной схемой ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 2 и подаются на регистр FF 8, который производит их защелкивание, когда V - инвертируемые данные VF находятся на уровне "H". С другой стороны, вышеуказанные данные Vc, поступая на триггерный регистр FF 8, проводятся через схему XOR 2 ИСКЛЮЧАЮЩЕЕ ИЛИ без какого-либо изменения и защелкиваются в регистре, если V - инвертируемые данные VF имеют уровень "L". Операции H- и V -триггерирования (уровневого инвертирования) изображения заднего фона реализуются при реверсировании состояния вышеупомянутых логических схем XOR 1 и XOR 2. Данные, выводимые с этих схем, индексируются как Hc и Vc независимо от того, были они реверсированы или нет (это сделано для упрощения описания).

Дополнительно следует указать, что заранее перед осуществлением обработки видеоданных по повороту, увеличению или уменьшению изображения заднего фона в зону 52, соответствующую участку отображения указанного изображения на экране, в память ВЗУПВ 7b (VRAM 7b) и в знаковую зону 51 заднефонового изображения в память ВЗУПВ 7a записываются соответственно данные по знаковому имени и данные по цветности первоначального изображения заднего фона.

На фиг.11, 12 для наглядности моменты времени, когда на выходе синхрогенератора 30 появляется задающий тактовый импульс 10 МСК с частотой повторения 10, 739 МГц (на гистограмме вместо апострофа над и за символом использован знак "/" перед символом), обозначены как t1, t2, t3,...,t20,... В этом случае на протяжении периода от момента времени t1 до момента t2 проводится предварительная обработка данных, смыслом которой является вычисление констант E1 - E8 и которая осуществляется в течение периода гашения обратного хода кадровой развертки и до периода формирования и выдачи видеосигнала с видеопроцессорного блока 1. Обработка после момента времени t9 - это обработка в реальном масштабе времени, осуществляемая синхронизованно с формированием и отображением сигнала изображения, который является по существу цифровым сигналом RGB - реплики видеосигнала; содержанием этой обработки является вычисление координат Q (X2, Y2) изображения заднего фона во время его поворота, увеличения или уменьшения в соответствии с константами, вычисленными в процессе предварительной обработки, и данными счета Hc и Vc; вывод и запись адреса зоны 52 отображения изображения заднего фона на экране в память ВЗУПВ 7b; и, наконец, запись адреса звуковой области 51 изображения заднего фона в память ВЗУПВ 7a на основе знакового кода, считываемого из зоны 52.

Во временной период от момента t1 и до момента t2 оба коммутатора SW 3 и SW 4 подключены на их входные клеммы a. В это время на входные клеммы a суммирующего устройства АДД от триггерного регистра FF 1 через переключающее устройство SW 3 поступают данные Hp. В свою очередь, на вводы b сумматора АДД от триггера FF 14 через коммутатор SW 4 и логическую ячейку ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 поступают данные Xo. При этом сигнал ADS находится на уровне "H". В таком режиме логическая вентильная схема XOR и сумматор АДД осуществляют вычитательную обработку данных по алгоритму, рассмотренному выше, с получением результирующих данных в виде E1 = (Hp - Xo), которые подвергаются дальнейшей обработке. Данные E1 поступают на вход триггерного регистра FF 9, где защелкиваются по переднему фронту задающего сигнала блокировки LA 9, в момент времени t2.

Во временной интервал от t2 до t3 переключающие устройства SW 1 и SW 2 подключены на их входные клеммы a и c соответственно. В это время на вводы a умножителя МРУ от регистра FF 1 через переключающее устройство SW 1 поступают данные A. В свою очередь, на входные клеммы b того же умножителя МРУ от регистра FF 9 через переключающее устройство SW 2 приходят данные E1. Множительное устройство выполняет операцию A•E1, формируя соответствующие выходные данные, которые поступают на триггерную схему FF 13, где и защелкиваются по переднему фронту задающего тактового импульса /10 МСК в момент времени t3.

Далее следует указать, что на протяжении временного интервала, начиная с времени t2 и до момента времени t3, оба переключающих устройства SW 3 и SW 4 закоммутированы на их входные клеммы b. В этом режиме на входные клеммы a сумматора АДД от триггерного регистра FF 11 через коммутатор SW 3 поступают данные Vp. С другой стороны, на вводы b того же сумматора от регистра FF 15 через переключающее устройство SW 4 и вентиль (схему) ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 поступают данные Yo. В это время сигнал ADS имеет "H"-уровень. В соответствии с этим логическая схема XOR 3 и суммирующее устройство АДД осуществляют вычитательную обработку данных по вышерассмотренному алгоритму, формируя на выходе данные E2 = (Vp - Yo). Данные E2 вводятся в регистр FF 10 и защелкиваются в нем в момент времени t3 с приходом переднего фронта задающего сигнала блокировки LА 10.

В следующий временной период t3 - t4 оба переключающих устройства SW 1 и SW 2 закоммутированы на их входные клеммы d. В это время на входные клеммы a умножителя МРУ от триггерной схемы FF 4 через переключающее устройство SW 1 поступают данные D. В свою очередь, на входные клеммы b умножителя от триггерной схемы FF 10 через переключающее устройство SW 2 поступают данные E2. Умножитель МРУ производит перемножение данных D•E2, формируя на выходе соответствующее множимое. Данные D•E2 вводятся в регистр FF 13, где они защелкиваются с приходом переднего фронта задающего тактового импульса /10 МСК в момент времени t4.

Дополнительно следует указать, что в течение временного интервала t3 - t4 коммутаторы SW 3 и SW 4 закоммутированы соответственно на их входные клеммы c и a. На входные клеммы a суммирующего устройства АДД от триггерной схемы FF 13 через переключающее устройство SW 3 поступают данные А•EI. Одновременно с этим на вводы b указанного сумматора от триггерной схемы FF 13 через переключающее устройство SW 4 и логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 подаются данные Xо. В это время сигнал ADS имеет уровень "L". При этом условии вентильная схема XOR 3 и сумматор АДД осуществляют аддитивную обработку данных по ранее рассмотренному алгоритму, формируя на выходе данные ЕЗ = (A•E1) + Xo, которые поступают на вход регистра FF 16, где осуществляется их защелкивание по переднему фронту тактового импульса /16 СК в момент времени t4.

В следующий период времени t4 - t5 переключающие устройства SW 1 и SW 2 подключены на их входные клеммы b и d соответственно. На входные клеммы a умножителя МРУ от триггерной схемы FF 2 через переключающее устройство SW 1 поступают данные B. В свою очередь, на входные клеммы b того же умножителя от регистра FF 10 через переключающее устройство SW 2 приходят данные Е2. Умножитель МРУ производит операцию перемножения B•E2, результирующие данные от которой вводятся в регистр FF 13, защелкиваются по переднему фронту тактового импульса /10 МСК, поступающему в момент времени t5.

В тот же временной интервал t4 - t5 переключающие устройства SW 3 и SW 4 закоммутированы на их входные клеммы c и b соответственно. При такой сетевой коммутации на входные клеммы a суммирующего устройства АДД от триггерной схемы FF 13 через переключающее устройство SW 3 поступают данные D•Е2. В свою очередь, на вводы b сумматора АДД от триггера FF 15 через коммутатор SW 4 и логическую вентильную схему ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 приходят данные Yo. В это время сигнал АD имеет уровень "L". В соответствии с этим схема XOR 3 и сумматор АДД осуществляют суммирование по ранее рассмотренному алгоритму, формируя в результате такой обработки данные Е4 = (D•Е2) + Yо, которые поступают на вход триггерной схемы FF 17, которая защелкивает эти данные по переднему фронту тактового импульса /17 СК в момент времени t5.

В следующий интервал времени t5 - t6 оба переключающих устройства SW 1 и SW 2 скоммутированы на их вводы c. В этом режиме на входные клеммы a умножителя МРУ от триггерного регистра FF 3 через коммутатор SW 1 поступают данные C. В свою очередь, на входные клеммы b того же умножителя от триггерного регистра FF 9 через переключающее устройство SW 2 вводятся данные Е1. Умножитель осуществляет операцию перемножения данных C•E1, результирующие данные которой поступают на вход триггерной схемы FF 13, где эти данные подвергаются фиксационному защелкиванию с приходом переднего фронта тактового импульса /10 МКС в момент времени t6.

В тот же временной интервал t5 - t6 два других переключающих устройства SW 3 и SW 4 скоммутированы на их входные клеммы c. При этом на вводы a суммирующего устройства АДД от триггерной схемы - регистра 13 через переключающее устройство SW 3 приходят данные B•E2. В свою очередь, на вводы b указанного сумматора от регистра FF 16 через переключающее устройство SW 4 и вентильную логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 3 поступают данные Е3. В это время сигнал АD имеет уровень "L". В соответствии с этим логическая схема-вентиль XOR 3 и сумматор АДД осуществляют аддитивную обработку данных по вышерассмотренному алгоритму, формируя выходные операционные данные Е5 = (В•Е2) + Е3, которые поступают на вход триггерного регистра FF 16, в котором эти данные защелкиваются с приходном переднего фронта тактового импульса 16 СК в момент времени t6.

На протяжении следующего временного интервала t6 - t7 оба переключающих устройства SW 1 и SW 2 закоммутированны на их входные клеммы b. При этом на вводы a умножителя МРУ от триггерной схемы-регистра FF 2 через переключающее устройство SW 1 приходят данные B. В свою очередь, на входные клеммы b указанного умножителя от триггерной схемы FF 8 через коммутатор SW 2 поступают данные Vc. Множительное устройство МРУ приводит операцию перемножения данных B•Vc, результирующие данные по которой вводятся в регистр FF 13, где защелкиваются по переднему фронту тактового импульса /10 МСК в момент времени t7.

В этот же временной период t6 - t7 два других коммутатора SW 3 и SW 4 подключены на их входные клеммы c и d соответственно. При этом условии на вводы a суммирующего устройства АДД от триггерной регистровой схемы FF 13 через переключающее устройство SW 3 поступают данные C•E1. В свою очередь, на входные клеммы b указанного сумматора от регистра FF 17 через переключающее устройство SW 4 и вентильную логическую схему XOR 3 ИСКЛЮЧАЮЩЕЕ ИЛИ приходят данные Е4. В это время сигнал АDS находится на "L" уровне. В соответствии с этим схема XOR 3 и сумматор АДД осуществляют операцию сложения данных по ранее рассмотренному расчетному алгоритму, формируя в результате такой обработки данные E6 = (C•E1) + E4, которые вводятся в триггерный регистра FF 16, который производит фиксационное защелкивание этих данных в момент времени t7 с приходом переднего фронта задающего импульса 17 СК.

В следующем временном интервале t7 - t8 переключающие устройства SW 1 и SW 2 скоммутированы на их входные клеммы d и b соответственно. На входные клеммы множительного устройства МРУ от триггерной схемы-регистра FF 4 через переключающее устройство SW 1 поступают данные D. В свою очередь, на входные клеммы b указанного умножителя из регистра FF 8 через переключающее устройство SW 2 вводятся данные Vc. Умножитель МРУ выполняет операцию перемножителя данных D•Vc, результаты которой вводятся в триггерную схему FF 13. Эта схема защелкивает поступающие данные D•Vc в момент времени t8 по переднему фронту тактового импульса /10 МСК.

В то же время на протяжении интервала t7 - t8 два других переключательных устройства SW 3 и SW 4 закоммутированы на их входные клеммы c. При этом на вводы a сумматора АДД от триггерной регистровой схемы 13 через переключающее устройство SW 3 поступают данные B•Vc. В свою очередь, на вводы b указанного сумматора от регистра FF 16 через коммутатор SW 4 и логическую вентильную схему XOR 3 ИСКЛЮЧАЮЩЕЕ ИЛИ приходят данные Е5. В это время сигнал АDS имеет уровень "L". В соответствии с этим вентильная схема XOR 3 и сумматор АДД производят операцию сложения данных по вышерассмотренному алгоритму, формируя операционные данные E7 = (B•Vc) + E5, которые вводятся в триггерный регистр FF 16, где эти данные защелкиваются по переднему фронту тактового импульса 16 СК в момент времени t8.

В следующий временной интервал t8 - t9 оба переключающих устройства SW 1 и SW 2 скоммутированы на их входные клеммы a. При этом на входные клеммы a множительного устройства МРУ от триггерного блока FF 1 через коммутатор SW 1 приходят данные A. В свою очередь, на входные клеммы b указанного умножителя от HV - счетчика 31 через вентильную логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ XOR 1 и переключающее устройство SW 2 поступают данные Hc. Умножитель МРУ выполняет операцию A•Hc, результирующие данные которой подаются на вход регистра FF 13, который защелкивает эти данные с появлением переднего фронта тактового задающего импульса /10 МСК в момент времени t9.

В тот же отрезок времени t8 - t9 два других переключающих устройства SW 3 и SW 4 подключены на их входные клеммы c и d соответственно. При этом на входы a суммирующего устройства АДД от триггерной схемы FF 13 через переключающее устройство SW 3 вводятся данные D•Vc. В свою очередь, на вводы b указанного сумматора от регистра FF 17 через переключающее устройство SW 4 и логическую вентильную схему XOR 3 ИСКЛЮЧАЮЩЕЕ ИЛИ приходят данные E6. В это время сигнал АDS имеет уровень "L". В силу этого схема XOR 3 и сумматор АДД проводят операцию сложения по вышерассмотренному алгоритму, формируя данные E8 = (D•Vc) + E6, которые вводятся в регистр FF 17, где защелкиваются по переднему фронту тактового импульса 17 СК в момент времени t9.

На этом предварительная обработка данных завершается. Таким образом, данные E7 фиксируются защелкиванием в регистре FF 16, а данные E8 - в регистре FF 17.

В последующем на протяжении временного интервала t9 - t10 переключающие устройства SW 1 и SW 2 закоммутированы на их входные клеммы c и a соответственно. При этом условии на входные клеммы a множительного устройства МРУ от триггерной схемы FF 3 через коммутатор SW 1 поступают данные C. В свою очередь, на входные клеммы b того же умножителя от HV - счетчика 31 через вентильную логическую схему XOR 1 ИСКЛЮЧАЮЩЕЕ ИЛИ и переключающее устройство поступают данные Hc. Умножитель МРУ осуществляют операционное действие С•Hc, засылая выходные данные на триггерный регистра FF 13, где эти данные защелкиваются по переднему фронту тактового импульса /10 МСК в момент времени t10.

Одновременно с этим в течение временного интервала t9 - t10 два других переключающих устройства SW 3 и SW 4 скоммутированы на их входные клеммы c. При этом на входные клеммы a сумматора АДД от триггерной схемы FF 13 через переключающее устройство SW 3 поступают данные A•Hc. В свою очередь, на входные клеммы b того же сумматора от регистра FF 16 через коммутатор SW 4 и вентильную схему XOR 3 ИСКЛЮЧАЮЩЕЕ ИЛИ приходят данные E7. В это время сигнал АDS имеет уровень "L". В соответствии с этим логическая схема XOR 3 и сумматор АДД реализуют операцию сложения данных (A•Hc) + E7, результатом которой являются данные X2. Данные X2 поступают на триггерную схему-регистр FF 19, которая защелкивает эти данные по переднему фронту тактового импульса /10 МСК, после чего эти данные вводятся в регистр FF 20 и защелкиваются в нем в момент времени t11 синхронно с приходом переднего фронта тактового импульса /5 МСК.

В следующий временной интервал t10 - t11 переключающие устройства SW 1 и SW 2 закоммутированы на их входные клеммы a. При этом на вводы a множительного устройства МРУ от триггерной схемы-регистра FF 1 коммутатор SW 1 поступают данные A. В свою очередь, на вводы b указанного умножителя от HV-счетчика 31 через вентильную логическую схему XOR 1 ИСКЛЮЧАЮЩЕЕ ИЛИ и переключающее устройство SW 2 приходят данные Hc. Умножитель МРУ производит перемножение данных A•Hc. Результат такого операционного действия поступает на вход регистра FF 13, который производит фиксационное защелкивание поступающих данных в момент времени t11 при поступлении переднего фронта тактового импульса / 10 МСК.

Одновременно с этим на протяжении временного периода t10 - t11 два других переключающих устройства SW 3 и SW 4 скоммутированы на их входные клеммы c и d соответственно. При этом на вводе a сумматора АДД от триггерной схемы FF 13 через переключающее устройство SW 3 поступают данные C•Hc. В свою очередь, на входы b упомянутого сумматора от регистра FF 17 через переключающее устройство SW 4 и логическую схему XOR 3 вводятся данные E8. В это время сигнал ADS имеет уровень "L". В соответствии с этим логическая схема XOR 3 ИСКЛЮЧАЮЩЕЕ ИЛИ и сумматор АДД осуществляют суммирующую обработку данных в виде (C•Hc) + E8, формируя результирующие данные Y2. Эти данные вводятся в регистр FF 18, где происходит из защелкивание в момент времени t11 по переднему фронту тактового импульса / 5 МСК.

При Hc = 0 данные X2 вычисляются в течение вышеупомянутого временного интервала t9 - t10, а данные Y2 - в интервале t10 - t11. На протяжении временного интервала после момента t11 данные X2 и Y2, когда данные Hc = 1 - 255, вычисляются точно таким же образом, как и их вычисление для одной строки развертки.

В момент времени t11 выходной сигнал AE синхрогенератора 30 падает по уровню, что приводит к задействованию трехпозиционных буферных усилителей BA1 - BA6. Далее, в период времени t11 и t13 с выхода буферного усилителя BA1 в память ВЗУПВ 7b через адресную шину 15b проводится адрес СААО в общей сложности из 16 бит, содержащих данные по наиболее значимым двум битам "00"; аналогичным образом в случае, когда Hc = 0, в указанную память поступают данные Yc и Xc по соответствующим наиболее значимым семи битам данных Y2 (10 битов) и данные X2 (10 битов), которые защелкиваются в триггерных регистрах FF 18 и FF 20. Видеопамять производит отбор адреса СААО с ее входа в момент времени t13. При Hc = 0 данные Yα и Xα по наименее значимым трем битам данных Y2 и X2 соответственно, которые защелкнуты в регистрах FF 18 и FF 20, пропускаются через регистр FF 22 и защелкиваются в регистре FF 23.

В течение временного интервала после t13 производится периодическое воспроизведение адресов САА1 - САА255, включающих данные Yc и Xc при Hc = 1 -255; эти адреса выводятся на ВЗУПВ 7b через адресную шину 15b в каждый период действия тактового импульса / 5 МСК. Далее, данные Yα и Xα , соответствующие определенным значениям данных Hc, защелкиваются в триггерной ячейке FF 23, поступая через триггер FF 22 вышерассмотренным образом.

Видеозапоминающее устройство (ступень) ВЗУПВ 7b реагирует на адреса САА0 - САА255, поступающие от управляющей схемы 24 адресации изображения заднего фона через адресную шину 15b, выдавая на выход 8-разрядные знаковые коды СА0 - СА255, "записываемые" по соответствующим адресам в регистр FF 21 в схему адресации 24 через шину данных 16b по каждому периоду тактовых импульсов / 10 МСК. Указанные 8-разрядные знаковые коды СА0 - СА255 защелкиваются в регистре FF 21.

В свою очередь, данные Yα и Xα (в сумме - 6 битов), соответствующие знаковым кодам, защелкиваются в регистре FF 23, как это было рассмотрено выше. При этом условии во временной период t15 - t17 шестнадцатиразрядный адрес ССА0, содержащий данные по наиболее значимым двум битам "00", восьмиразрядный знаковый код, защелкиваемый в регистре FF 21, и данные Yα и Xα (в сумме - 6 битов) при Hc = 0 выводятся на запоминающее устройство ВЗУПВ 7a (VRAM 7a) через трехпозиционные буферные усилители ВА4 - ВА6 и адресную шину 15a. Адрес САА0 вводится в ВЗУПВ 7a в момент времени t17.

В следующий временной интервал, начиная с t17, в ВЗУПВ 7a аналогичным образом поступают адреса ССА1 - ССА255; ввод этих адресных данных производится в течение временного интервала, когда Hc = 1 - 255, от схемы адресации 24 изображения заднего фона через адресную шину 15a.

Запоминающее устройство ВЗУПВ 7a, воспринимая адреса ССА0 - ССА255, поступающие от схемы адресации 24 через адресную шину 15a, выдает на выходе 8-разрядные данные цветности СД0 - СД255, записанные по соответствующим адресам, на процессор 25 обработки данных изображения заднего фона через шину данных 16b по каждому периоду тактовых импульсов (импульса) / 10 МСК.

Вышерассмотренная обработка данных по повороту, увеличению или уменьшению изображения заднего фона, касающаяся преобразований по одной строке развертки, осуществляется в целом по 244 строкам, состоящим из 28 знаков или символов (см. фиг. 2), позволяя в конечном итоге произвести указанные изменения изображения заднего фона на всей рабочей области 41 экрана дисплея.

Как отмечалось выше, схема 24 адресации изображения заднего фона вычисляет адреса САА0 - САА255, в которые в процессе поворота, увеличения или уменьшения указанного изображения вводятся знаковые коды, которые формируются в соответствии с константными данными A, B, C и D по указанным преобразованиям, поступающими от ЦП 2. На основе этого формируются комплексные адресные числа ССА0 - ССА255, каждое из которых содержит знаковый код (8 бит), снимаемый с выхода запоминающего устройства ВЗУПВ 7b, и данные Yα и Xα , что позволяет вывести данные по цветности из расчета 8 бит на точку непосредственно в процессе осуществления информационной обработки по повороту, увеличению/уменьшению заднефонового изображения из памяти ВЗУПВ 7a в процессор 25 обработки данных по указанному изображению. В последующем данные цветности (8 бит) изображения заднего фона защелкиваются в видеопроцессоре 25, а затем вводятся в схему 26 контроля приоритетов.

В свою очередь, из блока 23 обработки информации по переднефоновому движущемуся изображению в схему 26 контроля приоритетов вводятся семиразрядные видеоданные по указанному движущемуся изображению. Приоритетная схема 26 при поступлении данных по упомянутому изображению определяет приоритетность между данными движущегося и заднефонового изображений; это делается на основе двухразрядных приоритетных данных, входящих в состав видеоданных по движущемуся изображению, с подачей более высокоприоритетных данных по движущемуся изображению и изображению заднего фона на генератор 28 сигнала цветности. Генератор цветности 28 срабатывает при поступлении данных относительно высокого приоритета, преобразуя поступающие данные движущегося изображения или данные по изображению заднего фона в цифровой RGB-сигнал (трехцветовой сигнал) в 5 бит по каждому цвету. Сформированный таким образом цифровой RGB-сигнал подается на устройство видеоотображения (дисплей) 8 и кодировщик 29 НТСЦ стандарта, что осуществляется на основе данных счета Hc и Vc, поступающих от HV-счетчика 31. В результате вышерассмотренной обработки данных изображение заднего фона, формируемое в результате поворота, увеличения или уменьшения первоначального заднефонового изображения в соответствии с видеоданными, записанными в ВЗУПВ 7, и на основе данных по углу поворота γ и коэффициентам масштабирования α и β , поступающих от ЦП 2, воспроизводится на дисплее 8.