Устройство относится к вычислительной технике, в частности к управляющим вычислительным машинам (комплексам), применяемым в автоматизированных системах управления реального времени (АСУ РВ).

Известны устройства для сопряжения однородных вычислительных средств (1, 2, 3, 4), предназначенные для работы с универсальными ЭВМ или микропроцессорами через каналы или через общую память. Их недостатками является сложность и трудность использования в управляющем вычислительном комплексе АСУ РВ из-за необходимости наличия системы приоритетных прерываний, кроме того, данные, получаемые из вычислительного комплекса АСУ РВ для дальнейшей обработки другими вычислительными средствами, не имеют временных привязок для достаточной точности обработки в системе реального времени.

Прототипом предлагаемого изобретения является управляющий вычислительный комплекс [5] , состоящий из двух однородных ЭВМ, одна из которых работает в резерве по одинаковой программе с основной, причем программы в целях надежности жестко запрограммированы в долговременном запоминающем устройстве программ, а данные хранятся в основной памяти (оперативном запоминающем устройстве). Для того чтобы в случае необходимости ЭВМ, работающая по программе РЕЗЕРВНАЯ, могла переключиться на исполнение программы ОСНОВНАЯ, в ее оперативное запоминающее устройство (ОЗУ) периодически переписывается содержимое ОЗУ ЭВМ, работающей по программе ОСНОВНАЯ. Передача информации при этом происходит по магистрали прямого доступа к памяти по шине данных (ШД), причем для передачи информации из ОСНОВНОЙ ЭВМ в РЕЗЕРВНУЮ по команде УВУ 1а формируются сигналы ИГОвых и ИГ34, которые поступают в устройство прерывания программ (УПП) и вызывают прерывание в ОСНОВНОЙ ЭВМ, а сигнал ИГОвых поступает в виде ИГОвх по линии ИГО на РЕЗЕРВНУЮ ЭВМ и вызывает прерывание ее программы.

Недостатком прототипа является то, что он не позволяет обмениваться данными с ЭВМ других структур и архитектур, что ограничивает вычислительные возможности управляющего вычислительного комплекса АСУ РВ, создание же канала прямого доступа к памяти потребует создания приоритетной системы прерывании, что недопустимо для вычислительных комплексов АСУ РВ.

Сущность изобретения заключается в том, что в тракт обмена данными между двумя ЭВМ, работающими по программе ОСНОВНАЯ и РЕЗЕРВНАЯ, содержащим шину данных и линию импульса готовности к обмену введены счетчик слов, счетный вход которого соединен с линиями шины данных, запуск осуществляется с линии ИГО, счетчик слов одновременно является формирователем адреса записи, который через коммутатор адреса поступает в резервную память данных, куда по сформированному адресу записывается информация из шины данных, а считывание информации осуществляется по адресам, поступающим из шины данных других вычислительных средств (под другими вычислительными средствами понимаются ЭВМ и вычислительные системы другой структуры и архитектуры) через другой вход коммутатора адреса, работой которого управляет устройство управления, которое также формирует сигналы записи и чтения для резервной памяти, чтение данных из резервной памяти осуществляется в шину данных вычислительной системы, из которой поступил адрес чтения. Адреса чтения, их очередность и дешифрация данных осуществляются программными методами других вычислительных средств, сопрягаемых с управляющим вычислительным комплексом, кроме того, с помощью введенных генератора, счетчика, схемы ИЛИ и регистра выходных данных в выходных данных формируются разряды временной задержки, что позволит при дальнейшей обработке в других вычислительных системах повысить точность экстраполяции данных. Таким образом, предлагаемое устройство позволяет производить отбор данных, циркулирующих в вычислительном комплексе, и производить их обработку в других вычислительных устройствах, обладающих большей производительностью, что расширяет возможности обработки данных в вычислительном комплексе АСУ РВ, состоящем из двух одноранговых ЭВМ.

Сравнение с прототипом предлагаемого технического решения указывает на наличие существенных отличительных признаков и новых связей, влияющих на технический результат изобретения.

Новыми элементами устройства обмена данными управляющего вычислительного комплекса АСУ РВ с другими вычислительными средствами являются:

1) счетчик слов;

2) схема ИЛИ;

3) коммутатор адреса;

4) резервная память;

5) шина адреса канала ввода-вывода других вычислительных средств;

6) шина данных канала ввода-вывода других вычислительных средств;

7) устройство управления,

что позволяет сделать вывод о наличии критерия охраноспособности изобретения "новизна".

В известных технических решениях отличительные признаки не выявлены, что соответствует критерию охраноспособности "существенные отличия".

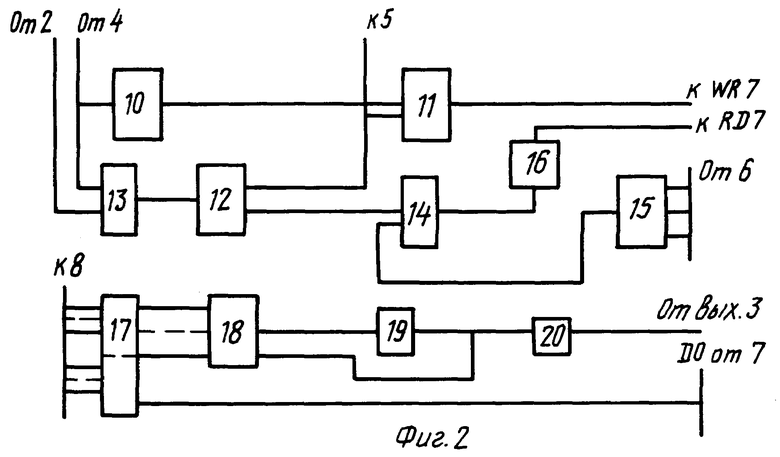

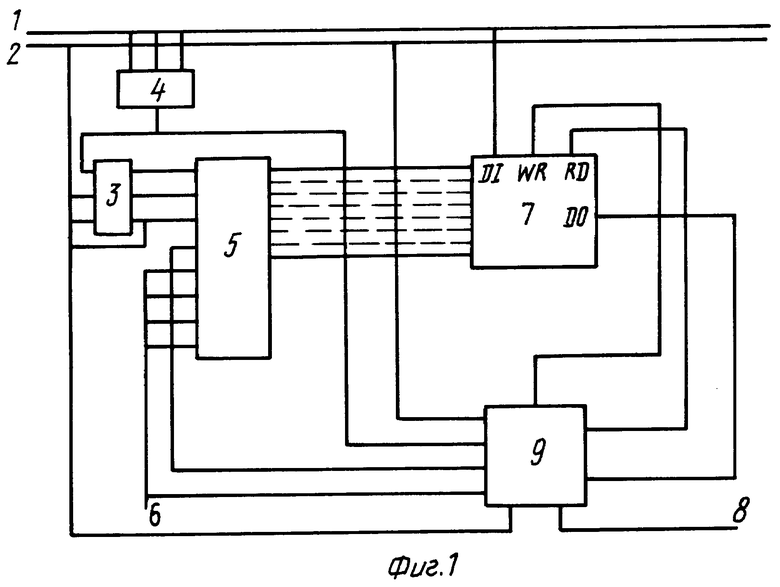

На фиг. 1 дана схема устройства обмена данными управляющего вычислительного комплекса АСУ РВ с другими вычислительными средствами; на фиг. 2 - устройство управления; на фиг. 3 - временная диаграмма работы устройства управления.

Устройство обмена данными управляющего вычислительного комплекса АСУ РВ с другими вычислительными средствами состоит из шины данных 1, линии импульса готовности к обмену (ИГО) 2 и введенного счетчика слов 3, счетный вход которого через схему ИЛИ 4 соединен с линиями шины данных, вход разрешения счета соединен с линией ИГО 2, а выходы с первыми входами коммутатора адреса 5, на другие входы которого подаются адреса чтения с шины адреса 6 канала ввода-вывода других вычислительных средств, выход его соединен с адресными входами резервной памяти 7, вход данных которой (DI) соединен с шиной данных вычислительного комплекса 1, а выход данных (DO) через устройство управления 9 соединен с шиной данных канала системы ввода-вывода других вычислительных средств 8. Работой предлагаемого устройства управляет введенное устройство управления 9, первый вход которого соединен с линией ИГО 2, второй вход соединен с выходом схемы ИЛИ 4, а первый выход соединен с коммутатором адреса 5, второй и третий выходы соединены с входом записи (WR) и чтения (RD) резервной памяти соответственно, третий вход соединен с линиями шины адреса другого вычислительного средства 6, четвертый вход соединен с последним выходом счетчика слов 3, пятый вход соединен с шиной выходных данных (DO) резервной памяти 7, а четвертый выход соединен с шиной данных канала ввода-вывода других вычислительных средств 8.

Введенное устройство управления 9, формирующее временную диаграмму (фиг. 3) состоит из одновибратора 10, вход которого соединен с выходом схемы ИЛИ 4, а выход с первым входом первой схемы И 11, второй вход которой соединен с единичным выходом триггера 12, а выход со входом разрешения записи (WR) резервной памяти 7, вход установки триггера (12) в единичное состояние соединен с выходом второй схемы И (13), входы которой соединены линией ИГО 2 и входом одновибратора 10. нулевой выход триггера соединен с первым входом третьей схемы И 14, второй вход которой соединен через схему ИЛИ 15 с шиной адреса 6, а выход через второй одновибратор соединен с входом сигнала чтения (RD) в резервной памяти 7, выход данных (DO) которой соединен с первым входом регистра выходных данных 17, со вторым входом которого соединены выходы счетчика времени запаздывания данных 18, счетный вход которого соединен с выходом генератора 19, вход которого соединен через третий одновибратор 20 с последним выходом счетчика слов 3 и со входом сброса счетчика времени запаздывания 18, а выходы регистра выходных данных соединены с шиной данных канала ввода-вывода других вычислительных средств 8.

Динамика работы устройства следующая.

С шины данных 1, по которой данные передаются из ЭВМ, работающей в режиме ОСНОВНАЯ, в ЭВМ, работающую в режиме РЕЗЕРВНАЯ, данные в качестве счетных импульсов через схему ИЛИ 4 подаются на счетный вход счетчика слов 3, вход разрешения счета которого соединен с линией ИГО 2, что позволяет формировать адреса записи, которые через первый вход коммутатора адреса 5 подаются на адресные входы резервной памяти 7, сигнал с линии ИГО 2, подается также на вход устройства управления 9, которое, используя его и сигнал с выхода схемы ИЛИ 4, формирует временную диаграмму (фиг. 3), управляя записью и чтением из резервной памяти. По сформированному с помощью счетчика слов адресу происходит запись данных с шины данных в резервную память 7, чтение данных из которой осуществляется по адресу, поступающему из шины адреса 6 канала ввода-вывода других вычислительных средств, на шину данных 8 в промежутки времени между циклами записи. Устройство управления 9 формирует временную диаграмму (см. фиг. 3) следующим образом: сигнал от схемы ИЛИ 4 совместно с положительным уровнем линии ИГО 2 через схему И 13 устанавливает триггер 12 в единичное состояние и запускает одновибратор 10, импульс которого, пройдя через схему И 11, служит в качестве сигнала разрешения записи (WR), при наличии сигналов на линиях шины адреса 6 и отсутствии сигналов на шине 1 и линии 2 через схему ИЛИ 15, схему И 14 и второй одновибратор 16 вырабатывается сигнал разрешения чтения из резервной памяти 7 в регистр выходных данных 8, при этом после каждого цикла записи с последнего провода счетчика слов 3 через третий одновибратор 20 происходит запуск генератора 19 и сброс счетчика времени запаздывания 18 для организации счета импульсов в счетчике времени запаздывания данных 18, который формирует вторую часть регистра выходных данных 17. Организация адресации и обработка полученных в другом вычислительном средстве из регистра выходных данных 17 через шину выходных данных организуется программным путем в другом вычислительном средстве.

Таким образом, предлагаемое устройство позволяет производить отбор данных из вычислительного комплекса АСУВ и производить их обработку на других более производительных вычислительных средствах, которые получают кроме данных и информацию об их запаздывании, что расширяет возможности по обработке данных в АСУ РВ.

Источники информации

1. Авторское свидетельство СССР N 1487058, кл. G 06 F 15/16, 1989.

2. Авторское свидетельство СССР N 1287167, кл. G 06 F 12/16, 13/16, 1987.

3. Авторское свидетельство СССР N 1474665, кл. G 06 F 15/16, 1989.

4. Каган Б.М., Мкртумян И. Б. Основы эксплуатации ЭВМ: Учеб. пособие для вузов. -М.: Энергоатомиздат, 1988. - стр. 150-153.

5. Ш01.01/Техническое описание: БЕ 231 004 ТО. - Свердловск, 1988. Лист 67-69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1989 |

|

SU1686453A1 |

| СИСТЕМА ДЛЯ ИНФОРМАЦИОННОГО ОБМЕНА С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2264655C2 |

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

Устройство относится к вычислительной технике, в частности к управляющим вычислительным машинам, применяемым в автоматизированных системах управления реального времени. Технический результат заключается в расширении функциональных возможностей управляющего вычислительного комплекса. Система содержит шину данных, линию импульса готовности к обмену, резервную память, счетчик слов, коммутатор адреса, схему ИЛИ, шину адреса канала ввода-вывода других вычислительных средств, шину выходных данных резервной памяти, шину данных канала ввода-вывода других вычислительных средств, устройство управления, которое состоит из первого одновибратора, первой схемы И, триггера, второй и третьей схем И, схемы ИЛИ, второго одновибратора, регистра выходных данных, счетчика времени запаздывания данных, генератора, третьго одновибратора. 1 з.п. ф-лы, 3 ил.

| Устройство обмена данными для магистральной многомашинной вычислительной системы | 1987 |

|

SU1571604A1 |

| SU 1487057 А1, 15.06.1989 | |||

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| US 5307468 A, 26.04.1994 | |||

| US 5325487 A, 28.06.1994. | |||

Авторы

Даты

2001-06-10—Публикация

1998-09-08—Подача