Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессора с видеоконтроллером в микро-ЭВМ с большой информативностью отображаемой информации.

Целью изобретения является упрощение устройства.

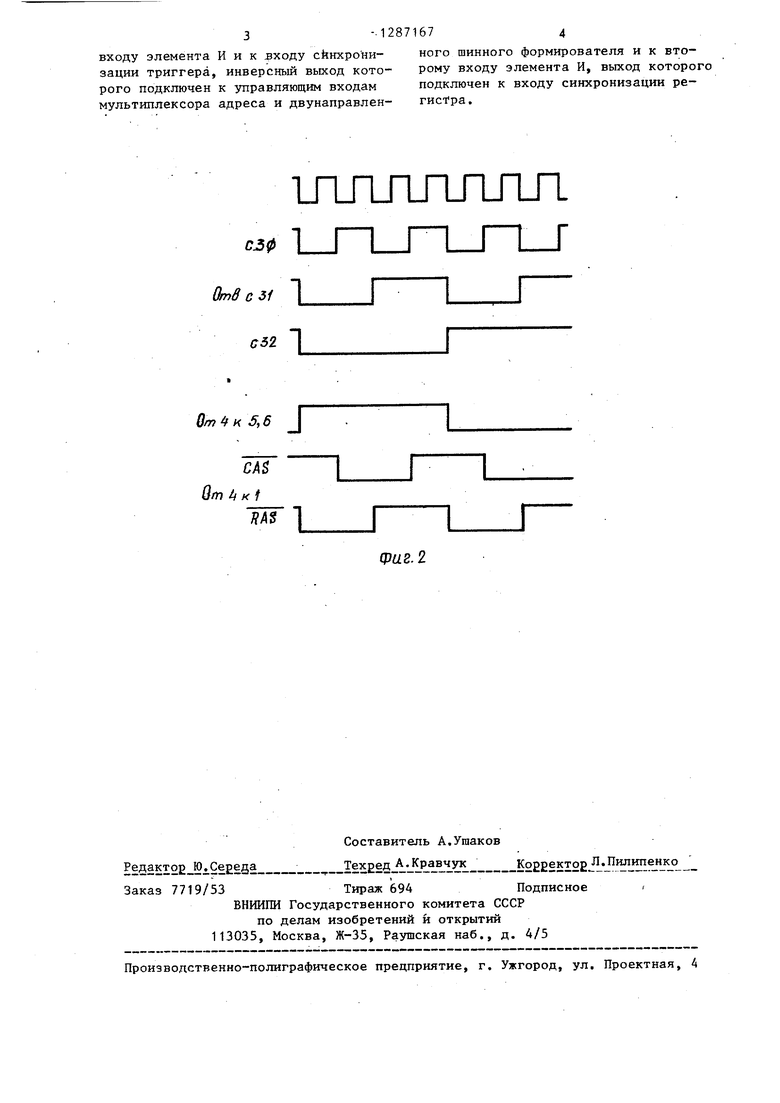

На фиг.1 приведена функциональная схема устройства и пример ее подклю- чения к видеоконтроллеру; на фиг.2 - временные диаграммы работы блока синхронизации.

Устройство (фиго1) содержит блок

1оперативной памяти, мультиплексор

2адреса, регистр 3, блок 4 синхронизации, триггер 5, элемент И 6, двунаправленный шинный формирователь 7. Видеоконтроллер 8 подключается к устройству через входы 9 и 10 данных и адреса и вход 11 запроса синхронного

доступа от второго процессора. Про- цессор подключается к устройству через вход-выход 12 данных, вход. 13 адреса и вход 14 запроса асннхронно1 доступа от первого процессора. В качестве второго процессора может быть использован видеоконтроллер КР 580ВГ75,

Под доступом к памяти подразуме- 1вается как цикл чтения, так и цикл записи в память.

Устройство работает следующим образом.

Видеоконтроллер 8 вьщает адрес на мультиплексор 2. Мультиплексор 2 подает на блок 1 либо адрес процессора, либо адрес видеоконтроллера. Переключение источника адреса производится триггером 5, на который поступает сигнал асинхронного запроса доступа процессора. Блок 4 обеспечивает формирование сигналов управления блока

1с удвоенной частотой. В отсутствие сигнала доступа от процессора адрес от видеоконтроллера 8 поступает в блок 1, откуда происходит выборка информации для видеоконтроллера 8 и ее запоминание в регистре 3. Видеоконтроллер 8 принимает данные с частотой отображения на экране индикатора. При поступлении сигнала асинхронного доступа от процессора мультиплексор

2производит подачу адреса с входа

13 адреса на блок 1, блокируя посредством элемента И 6 запись выбранной из блока 1 информации в регистр 3. При этом происходит переключение дву

направленного шинного формирователя 7 и выбранная из блока 1 информация поступает на вход-вьгход 12 данных Процессора. Тем самым на один такт чтения информации из блока 1 оперативной памяти видеоконтроллером 8 приходится два такта .обращения к блоку 1 , а в случае отсутствия доступа к видеопамяти QT процессора происходит двойная (дублирующая) запись информации в регистр 3. Когда же в один из этих двух тактов происходит обращение процессора в блок 1, блокировка записи в регистр 3 позволяет сохранять правильную информацию для выборки видеоконтроллера 8.

Таким образом, безконфликтный.обмен через память организуется при помощи незначительных аппаратньк за- трат.

Формула изобретения

Устройство для сопрялсения двух процессоров через общую память, содержащее блок оперативной памяти, мультиплексор адреса, регистр, элемент И, блок синхронизации и триггер, информационный вход которого является входом запроса асинхронного доступа от первого процессора устройства, первый и второй информационные входы мультиплексора адреса являются входами адреса от первого и второго процессоров устройства соответствен5

к входу адреса блока оперативной памяти, выход которого подключен к ин- 0 формационному входу регистра, выход которого является выходом данных на второй процессор устройства, тактовый вход блока синхронизации является входом запроса синхронного дост упа от второго процессора устройства, .отличающееся тем, что, с целью упрощения устройства, в него введен двунаправленный шинный формирователь, первый информационный вход-выход которого является входом-выходом данньк от первого процессора устройства, второй информационный вход-выход двунаправленного шинного формирователя соединен с выходом и информационным входом блока оперативной памяти, вход управления записью-считыванием которого подключен к первому выходу блока синхронизации, второй выход которого подключен к первому

0

5

3-.12871674

входу элемента И и к входу сйнхро ни-кого шинного формирователя и к вто- зации триггера, инверсный выход кото-рому входу элемента И, выход которого рого подключен к управляющим входамподключен к входу синхронизации ре- мультиплексора адреса и двунаправлен-гист ра.

шплпллл

Отв G51

С52 П

От к 5,6 J

Cf( Qm li Ki

JW

II

EESS SI2EJ2i EE S§Coставитель А.Угааков

Техред A.Кравчутс KoggeKTOg Л.Пилипенко

Заказ 7719/53Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора и видеоконтроллера | 1988 |

|

SU1522225A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1709325A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство сопряжения видеоконтроллера и процессора через общую память | 1989 |

|

SU1689964A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

Изобретение относится к области вычислительной техники и предназначено для сопряжения процессоров через общую память в микропроцессорных системах. Реализация устройства требует незначительных аппаратурных затрат за счет соответствующего построения цепей синхронизации. Устройство содержит блок 1 оперативной памяти, мультиплексор 2 адреса, регистр 3, блок 4 синхронизации, триггер 5, элемент И 6 и двунаправленный шинный формирователь 7. В качестве сопрягаемых процессоров могут использоваться процессор системы и видеоконтроллер 8, в этом случае конструкция блока 4 упрощается. Обращение видеоконтроллера 8 в блок 1 за выборкой происходит с частотой вдвое больщей, чем необходимо для поддержания заданной скорости выдачи видеосигнала видеоконтроллером 8. Этим исключаются конфликты при обмене и достигается высокое качество изображения при сохранении скорости работы процессора системы. 2 ил. // C3f,CSLC32 о ж (Л с фуг. J

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Technical Reference | |||

| Tandy Corp., USA, pp | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4400801, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-30—Публикация

1985-07-19—Подача