1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей.

Известен преобразователь двоичных чисел в десятичные, содержащий комбинационные сумматоры и дешифратор двоично-десятичного кода 1|.

Недостаток указанного преобразо.вателя состоит в больших аппаратурных затратах.

Наиболее -близким к предлагаемому по технической сущности является преобразователь двоичного кода в десятичный, содержащий два сумматора и первый корректирующий сумматор 2J.

Недостатки данного преобразователя также состоят в значительных аппаратных затратах и низком быстродействии.

Цель изобретения - упрощение преобразователя и повышение его быстродействия .

Поставленная цель достигается тем, что преобразователь двоичного кода в десятичнцй, содержащий два сумматора и первый корректирующий сумматор, дополнительно содержит первый и второй трехразрядные двоичнодесятичные преобразователи, второй и третий корректирующие сумматоры, а первый и второй сумматоры выполнены в виде треугольных суммирунлцих матриц, первые информационные входы которых соответственно соединены с первыми информационными выходами первого и второго трехразрядных двоично-десятичных преобразователей,

10 входы которых являются информационными входс ми преобразователя, второй информационный вход первой треугольной суммирующей матрицы соединен со вторым информационным выходом второ15го трехразрядного двоично-десятичного преобразователя, выходы переполнения первой треугольной суммирующей матрицы и первого трехразрядного двоично-десятичного преобразователя со20единены соответственно с первым и вторым входами переполнения второй треугольной суммирующей матрицы, выходы которой соединены с разрядными входами третьего корректирующего

25 сумматора, первый счетный вход которого соединен с выходом переполнения первого корректирующего сумматора, второй счетный вход - со входом jпятого разряда информационных входов 3Q преобразователя и с суммирующим входом первого корректирующего сумматора, информационные входы которого соединены с информационными выходами первой треугольной суммирующей матрицы, а выходы первого корректирующего сумматора соединены с информационными входс1ми второго корректирукадего сумматора, счетный вход которого соединен со входом первого разряда информационных входов преобразователя, ВЫХСЭДЫ второго и третьего КОрректирующих сумматоров являются выходами преобразователя.

Кроме того, первый и второй трехразрядные двоично-десятичные преобразователи содержат три элемента И, восемь элементов И-НЕ, элемент ИЛЙ-Н и элемент ИЛИ, выход которого является выходом переноса трехразрядного двоично-десятичного преобразователя, вход первого разряда которого соединен с первыми входами первого элемента И, элемента ИЛИ-НЕ и первого, второго и третьего элементов ИНЕ, вход второго разряда соединен с первыми входами второго элемента И, четвертого элемента И-НЕ и вторыми входами первого и третьего элементов И-НЕ и элемента ИЛИ-НЕ, вход третьего разряда трехразрядного двоичнодесятичного преобразователя соединен с первым входом третьего элемента И, вторыми входами второго и четвертого элементов И-НЕ и третьими входами третьего элемента И-НЕ и элемента ИЛИ-НЕ, выходы первого, второго,третьего и четвертого элементов И-НЕ соединены со входами пятого, шестого, седьмого и восьмого элементов И-НЕ соответственно, выходы которых являются информационными выходгиии трехразрядного двоично-десятичного, преобразователя, выход третьего элемента И-НЕ соединен со вторыми входами элементов И и третьими входами первого, второго и четвертого элементов И-НЕ, выход первого элемента И-НЕ соединен с третьими входами первого и второго элементов И, выход второго элемента И-НЕ соединен с четвертыми входом первого и третьи входом третьего элементов И, выход четвертого элемента И-НЕ соединен с четвертыми входами второго и.третьего элементов И, выходы шестого, седьмого и BOi-bMoro элементов И-НЕ соединены со входами Элемента ИЛИ, выходы элемента ИЛИ-НЕ и элементов И являют ся информационными выходами трехразрядного двоично-десятичного преобразователя.

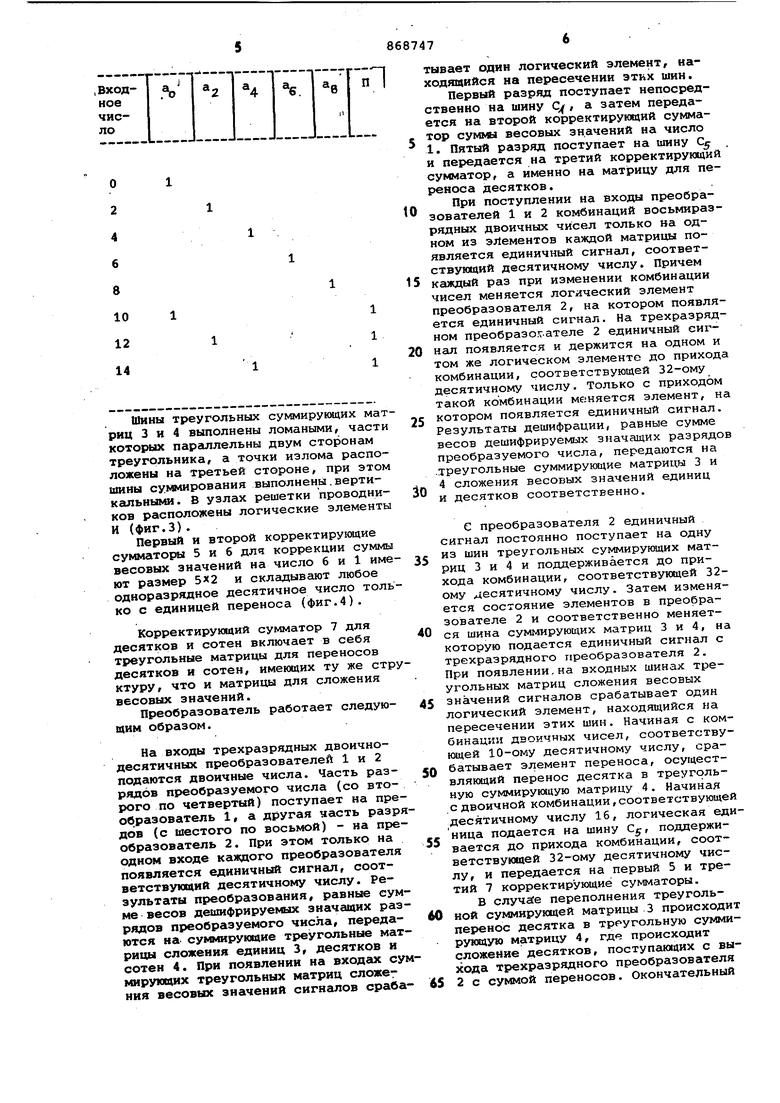

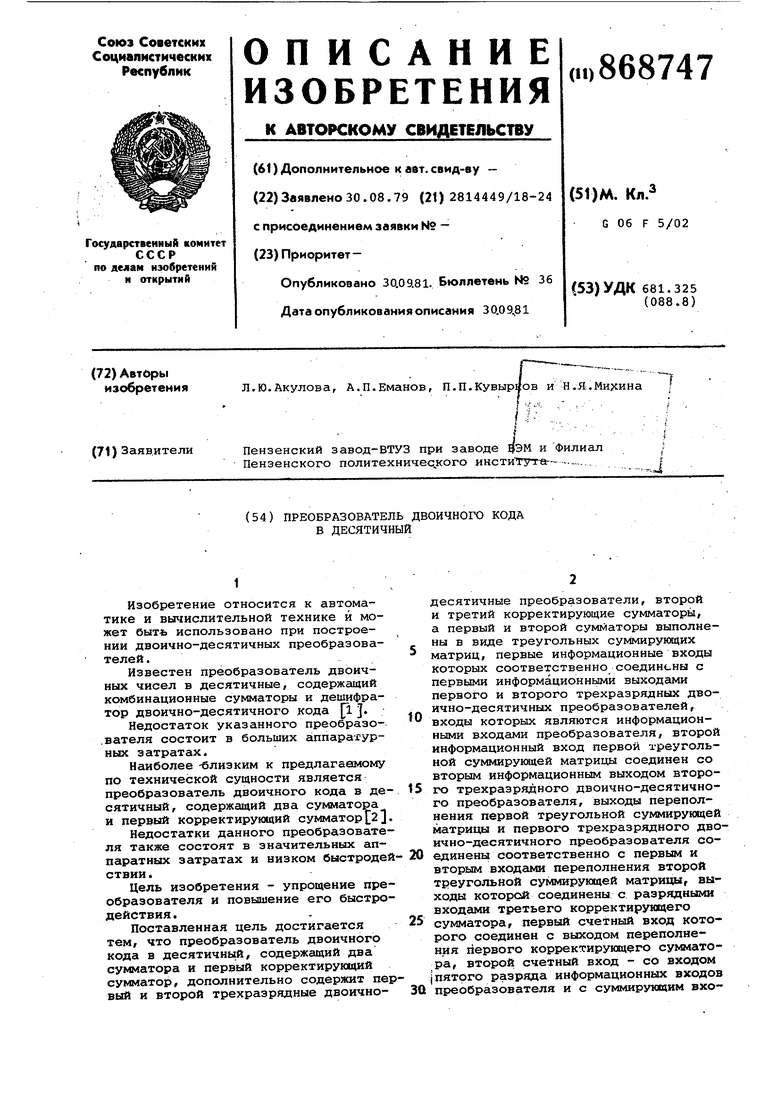

При этом треугольная суммирующая матрица состоит из элементов И, Причем первые входы (i,j)-ого элемента И, где i - номер строки, a..j - номер элемента И в строке (),(, где п - число разрядов слагаемого треугольной суммирующей матрицы,соединены со входом |-ого разряда первого слагаемса о, вторые входы (1, J ) ого элемента И, за исключением элементов И первой строки, соединены со входом (l+J-l)-oro разряда первого слагаемого треугольной суммирующей . матрицы, вторые входы элементов и первой строки соединены со входом j-oro разряда второго слагаемого,выJcoды (i, j ) -ых элементов И

(

являются разрядными информационными выходами треугольной суммирующей матрицы, выходы остальных элементов И являются выходами переноса треугольной суммирующей матрицы.

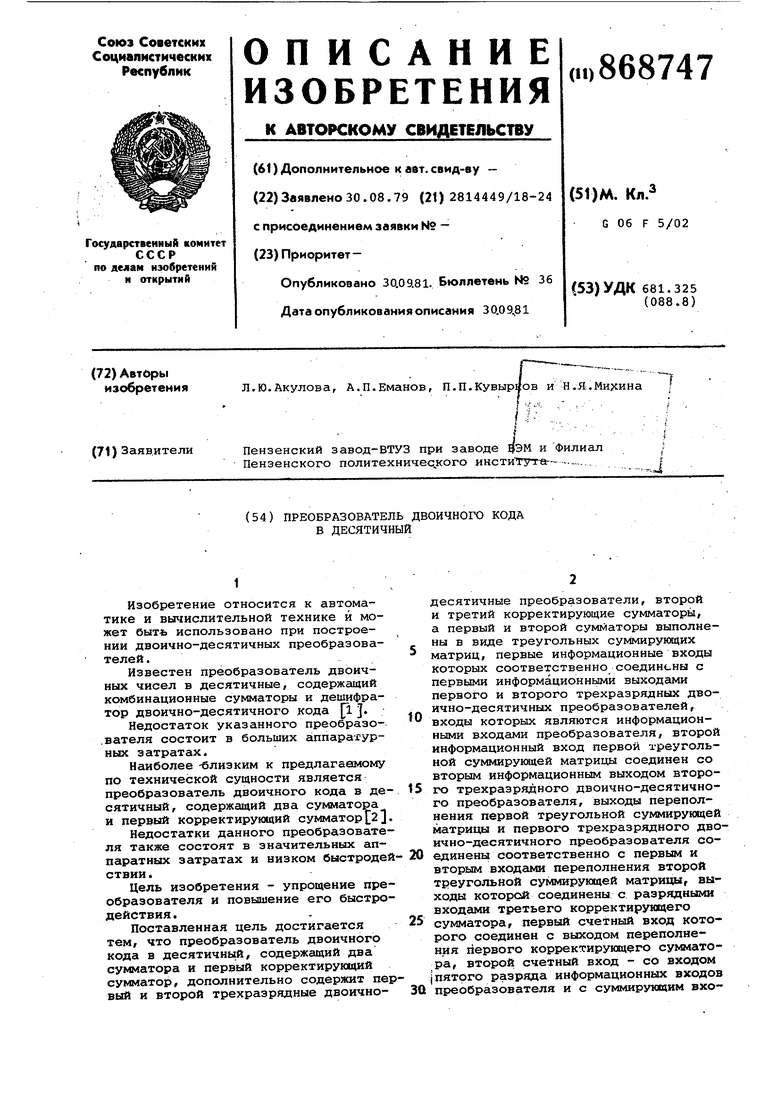

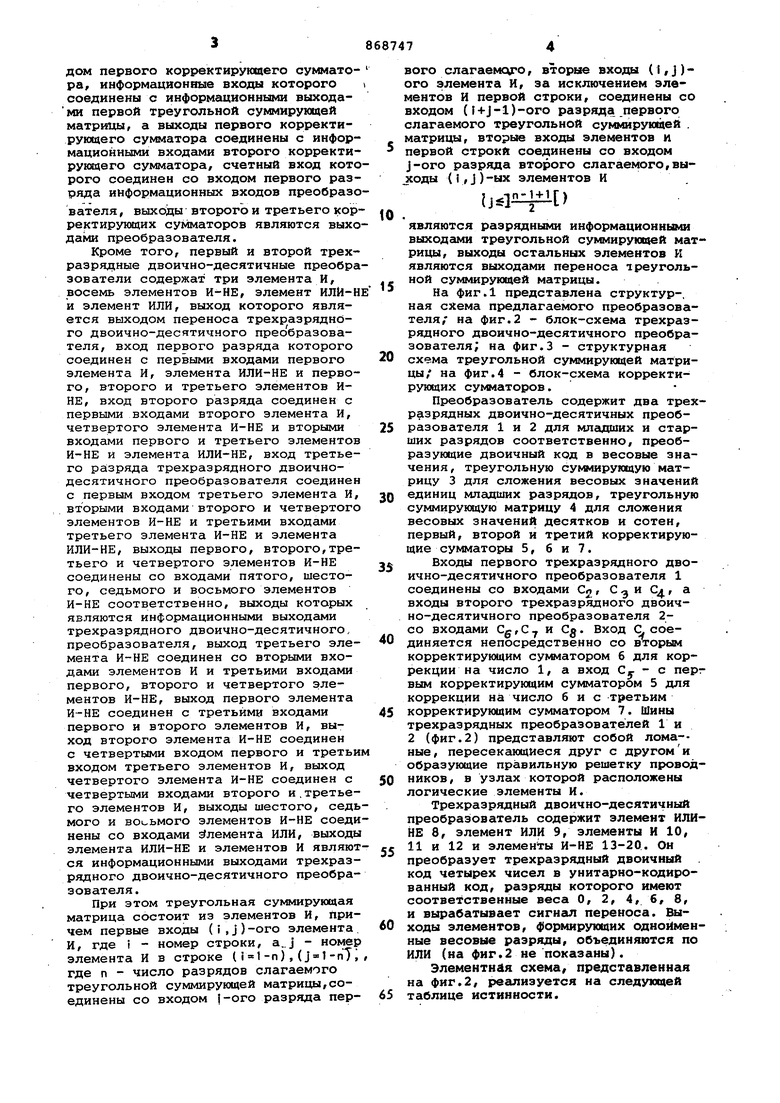

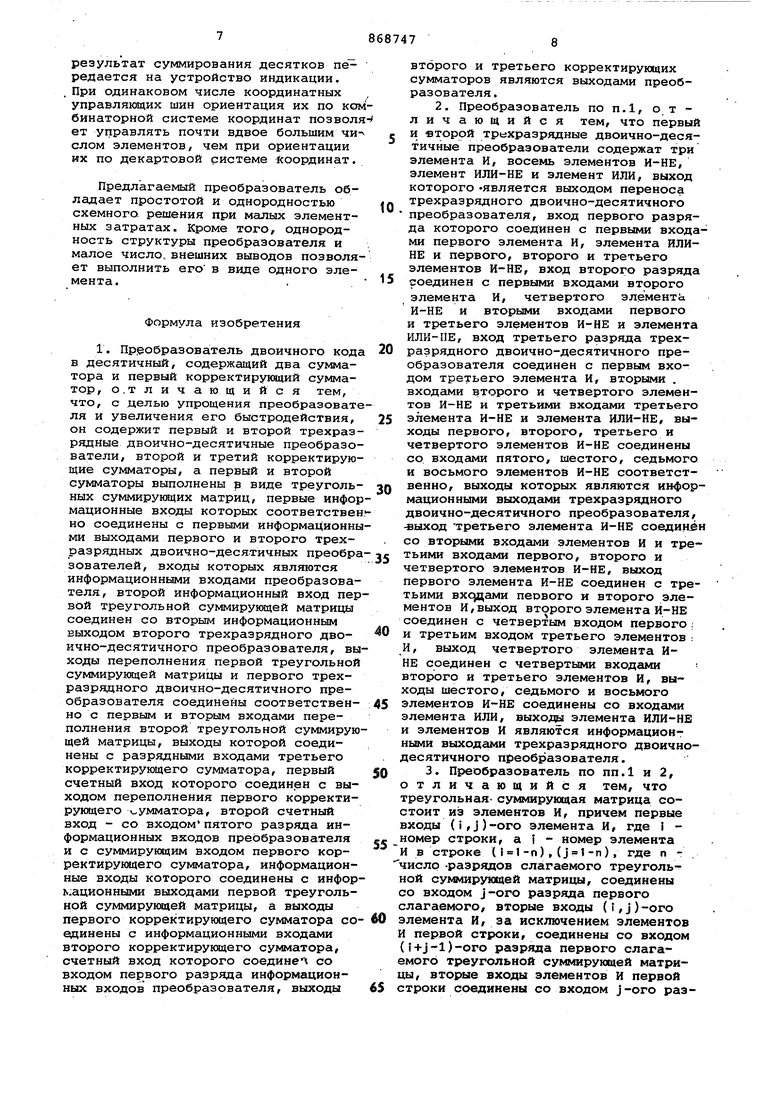

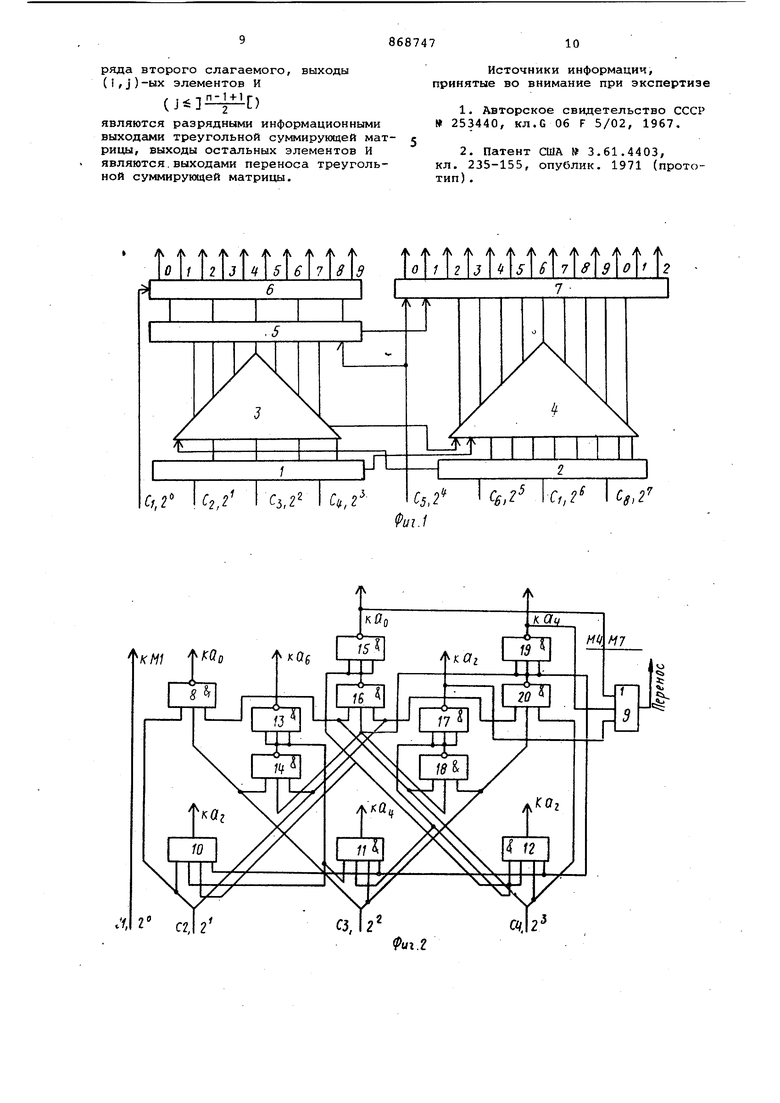

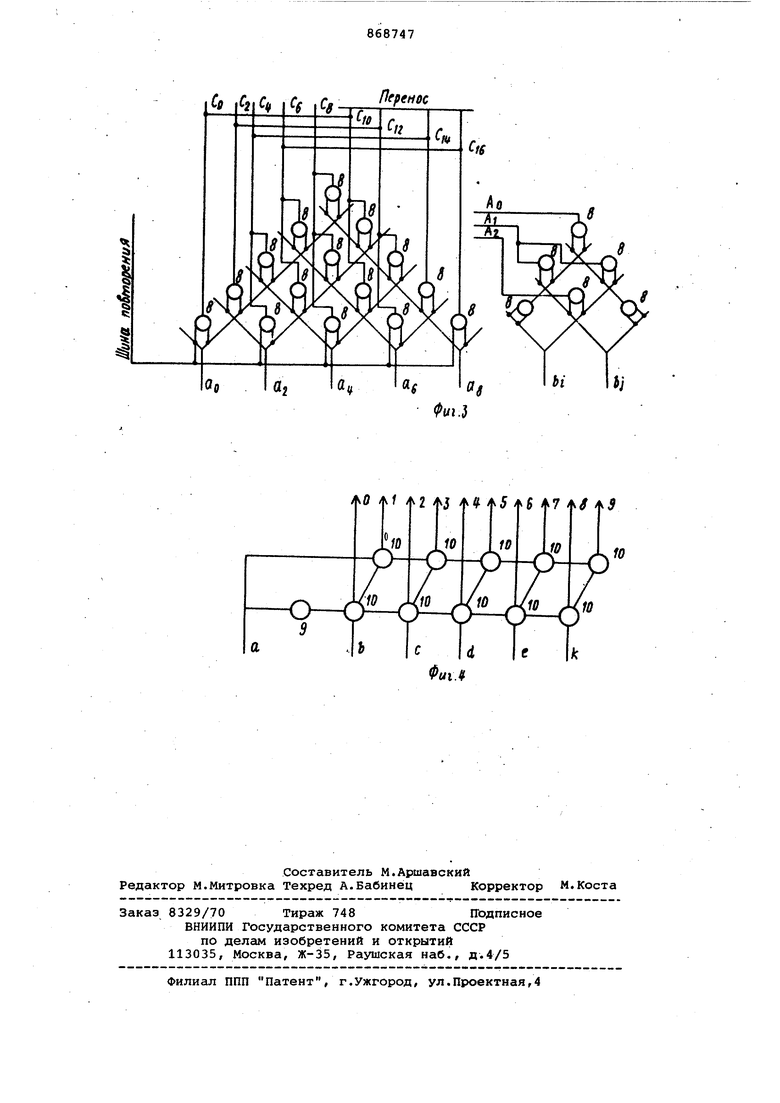

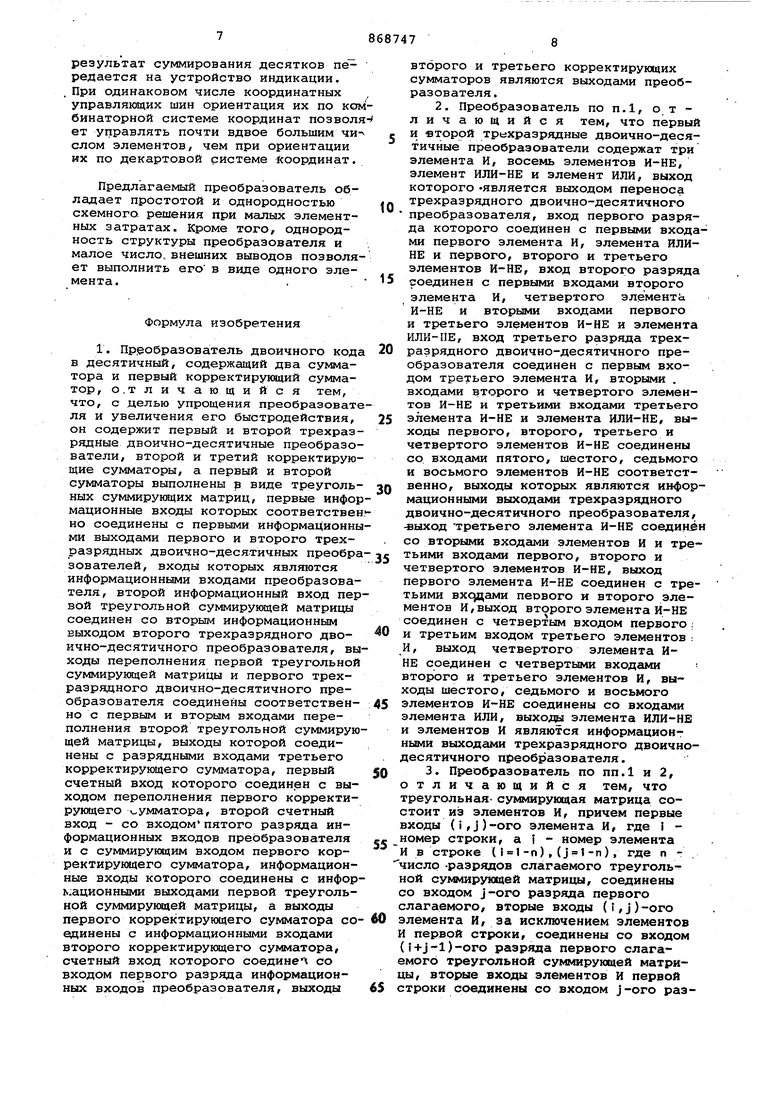

На фиг.1 представлена структур-, ная схема предлагаемого преобразователя/ на фиг.2 - блок-схема трехразрядного двоично-десятичного преобразователя; на фиг.З - структурная схема треугольной суммирующей матрицы/ на фиг.4 - блок-схема корректирующих сумматоров.

Преобразователь содержит два трехразрядных двоично-десятичных преобразователя 1 и 2 для млгщших и старших разрядов соответственно, преобразующие двоичный код в весовые значения, треугольную сукмирующую матрицу 3 для сложения весовых значений единиц младших разрядов, треугольную суммирующую матрицу 4 для сложения весовых значений десятков и сотен, первый, второй и третий корректирующие сумматоры 5, 6 и 7.

Входы первого трехразрядного двоично-десятичного преобразователя 1 соединены со входами Со, С о и Сд, а входы второго трехразрядного двоично-десятичного преобразователя 2со входами Cg,C и Cg. Вход (соединяется непосредственно со вторым корректирующим сумматором б для коррекции на число 1, а вход С-- - с пер вым корректирующим сумматором 5 для коррекции на число бис третьим корректирующим сумматором 7. Шины трехразр;1дных преобразователей 1 и 2 (фиг.2) представляют собой лома- ные, пересекающиеся друг с другоми образующие правильную решетку проводников , в узлах которой расположены логические элементы И.

Трехразрядный двоично-десятичный преобразователь содержит элемент ИЛИНЕ 8, элемент ИЛИ 9, элементы И 10, 11 и 12 и элементы И-НЕ 13-20. Он преобразует трехразрядный двоичный код четырех чисел в унитарно-кодированный код, разряды которого имеют соответственные веса О, 2, 4,6, 8, и вырабатывает сигнал переноса. Выходы элементов, формирующих одноименные весовые разряды, объединяются по ИЛИ (на фиг.2 не показаны).

Элементная схема, представленная на фиг.2, реализуется на следующей таблице истинности.

О

2

4

6

8

10

12

14

Шины треугольных суммирующих матриц 3 и 4 выполнены ломаными, части которых паргшлельны двум сторонам треугольника, а точки излома расположены на третьей стороне, при этом шины суммирования выполнены.вертикгшьными. В узлах решетки проводников расположены логические элементы И (фиг.З).

Первый и второй корректирующие сумматоры 5 и 6 длч коррекции суммы весовых значений на число 6 и 1 имеют размер 5X2 и складывают любое одноразрядное десятичное число только с единицей переноса (фиг.4).

Корректирующий сумматор 7 для десятков и сотен включает в себя треугольные матрицы для переносов десятков и сотен, имеющих ту же структуру, что и матрицы для сложения весовых значений.

Преобразователь работает следующим образом.

На входы трехразрядных двоичнодесятичных преобразователей 1 и 2 подаются двоичные числа. Часть разрядов преобразуемого числа (со второго по четвертый) поступает на преоб.разователь 1, а другая часть разрядов (с шестого по восьмой) - на преобразователь 2. При этом только на одном входе каядцого преобразователя появляется единичный сигнсш, соответствукщий десятичному числу. Результаты преобразования, равные сумме весов дешифрируемых значащих разрядов преобразуемого числа, передаются на суммирующие треугольные матрицы сложения единиц 3, десятков и сотен 4. При появлении на входгис суммирующих треугольных матриц сложет ния весовых значений сигналов срабатывает один логический элемент, находящийся на пересечении этих шин.

Первый разряд поступает непосредственно на шину С|, а затем передается на второй корректирующий сумма, тор суммы весовых значений на число 1. Пятый разряд поступает на шину С и передается на третий корректирующий сумматор, а именно на матрицу для переноса десятков.

При поступлении на входы преобраoзователей 1 и 2 комбинаций восьмиразрядных двоичных чисел только на одном из элементов каждой матрицы появляется единичный сигнал, соответствующий десятичному числу. Причем S каждый раз при изменении комбинации чисел меняется логический элемент преобразователя 2, на котором появляется единичный сигнал. На трехразрядном преобразо :.ателе 2 единичный сиг0нал появляется и держится на одном и том же логическом элементе до прихода комбинации, соответствующей 32-ому десятичному числу. Только с приходом такой комбинации меняется элемент, на котором появляется единичный сигнал.

5 Результаты дешифрации, равные сумме весов дешифрируемых значгидих разрядов преобразуемого числа, передаются на .треугольные суммирующие матрицы 3 и 4 сложения весовых значений единиц

0 и десятков соответственно.

е преобразователя 2 единичный сигнал постоянно поступает на одну из шин треугольных суммирующих мат5риц 3 и 4 и поддерживается до прихода комбинации, соответствующей 32ому десятичному числу. Затем изменяется состояние элементов в преобразователе 2 и соответственно меняет0ся шина суммирующих матриц 3 и 4, на которую подается единичный сигнал с трехразрядного преобразователя 2. При появлении.на входных шинах треугольных матриц сложения весовых значений сигналов срабатывает один

5 логический элемент, находяишйся на пересечении этих шин. Начиная с комбинации двоичных чисел, соответствующей 10-ому десятичному числу, срабатывает элемент переноса, осущест0вляющий перенос десятка в треугольную суммирующую матрицу 4. Начиная с двоичной комбинации,соответствующей десятичному числу 16, логическая единица подается на шину С, поддержи5

вается до прихода комбинации, соответствующей 32-ому десятичному числу, и передается на первый 5 и третий 7 корректирующие сумматоры. В случа:е переполнения треугольной суммирующей матрицы 3 происходит перенос десятка в треугольную суммирующую матрицу 4, где происходит сложение десятков, поступгиощих с выхода трехразрядного преобразователя

5 2 с суммой переносов. Окончательный результат суммирования десятков передается на устройство индикации. При одинаковом числе координатных управляющих шин ориентация их по ком бинаторной системе координат позвол ет управлять почти вдвое большим чи слом элементов, чем при ориентации их по декартовой системе координат. Предлагаемый преобразователь обладает простотой и однородностью схемного, решения при малых элементных затратах. Кроме того, однородность структуры преобразователя и малое число,внешних выводов позволя ет выполнить его в виде одного элемента. Формула изобретения 1. Преобразователь двоичного код в десятичный, содержащий два сумматора и первый корректирунвдий сумматор, о.тличающийся тем, что, с .целью упрощения преобразоват ля и увеличения его быстродействия, он содержит первый и второй трехраз рядные двоично-десятичные преобразо ватели, второй и третий корректирую щие сумматоры, а первый и второй сумматоры выполнены в виде треуголь ных суммирующих матриц, первые инфо мационные входы которых соответстве но соединены с первыми информационн ми выходами первого и второго трехразрядных двоично-десятичных преобр зователей, входы которых являются информационными входами преобразова теля, второй информационный вход пер вой треугольной суммирующей матрицы соединен со вторым информационным выходом второго трехразрядного двоично-десятичного преобразователя, вы ходы переполнения первой треугольной суммирующей матрицы и первого трехразрядного двоично-десятичного преобразователя соединены соответственно с первым и вторым входами переполнения второй треугольной суммирую щей матрицы, выходы которой соединены с разрядными входами третьего корректирующего сумматора, первый счетный вход которого соединен с выходом переполнения первого корректирукадего уммат.ора, второй счетный вход - со входомпятого разряда информационных входов преобразователя и с суммирующим входом первого корректирующего сумматора, информационные входы которого соединены с инфор кационными выходами первой треугольной суммирукнцей матрицы, а выходы первого корректирующего сумматора со единены с информационными входами второго корректируклдего сумматора, счетный вход которого соединеХ со входом первого разряда информационных входов преобразователя, выходы второго и третьего корректирующих сумматоров являются выходами преобразователя. 2. Преобразователь по п.1, о т личающийся тем, что первый и второй трехразрядные двоично-десятичные преобразователи содержат три элемента И, восемь элементов И-НЕ, элемент ИЛИ-НЕ и элемент ИЛИ, выход которого -является выходом переноса трехразрядного двоично-десятичного преобразователя, вход первого разряда которого соединен с первыми входами первого элемента И, элемента ИЛИНЕ и первого, второго и третьего элементов И-НЕ, вход второго разряда соединен с первыми входами второго элемента И, четвертого элемента И-НЕ и вторыми входами первого и третьего элементов И-НЕ и элемента ИЛИ-ПЕ, вход третьего разряда трехразрядного двоично-десятичного преобразователя соединен с первым входом третьего элемента И, вторыми . входами второго и четвертого элементов И-НЕ и третьими входами третьего элемента И-НЕ и элемента ИЛИ-НЕ, выходы первого, второго, третьего и четвертого элементов И-НЕ соединены со входами пятого, шестого, седьмого и восьмого элементов И-НЕ соответственно, выходы которых являются информационными выходскми трехразрядного двоично-десятичного преобразователя, -выход третьего элемента И-НЕ соединяй со вторыми входами элементов И и третьими входами первого, второго и четвертого элементов И-НЕ, выход первого элемента И-НЕ соединен с третьими входами первого и второго элементов И,выход второго элемента И-НЕ соединен с четвертым входом первого, и третьим входом третьего элементов: И, выход четвертого элемента ИНЕ соединен с четвертыми входами второго и третьего элементов И, выходы шестого, седьмого и восьмого элементов И-НЕ соединены со входами элемента ИЛИ, выходы элемента ИЛИ-НЕ и элементов И являются информационными выходами трехразрядного двоичнодесятичного преобразователя. 3. Преобразователь по пп.1 и 2, отличающийся тем, что треугольная- суммируняцая матрица состоит из элементов И, причем первые входы (i,j)-oro элемента И, где i номер строки, а f - номер элемента и в строке (),), где п - . число -разрядов слагаемого треугольной сум рующей матрицы, соединены со входом j-oro разряда первого слагаемого/ вторые входы (i,j)-oro элемента И, за исключением элементов и первой строки, соединены со входом (i+j-l)-oro разряда первого слагаемого треугольной суммирующей матриы, вторые входы элементов И первой троки соедииены со входом j-oro разряда второго слагаемого, выходы (,j)-ых элементов И

()

являются разрядными информационными выходами треугольной суммирующей матрицы, выходы остальных элементов И являются.выходами переноса треугольной суммирующей матрицы.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 253440, кл.С 06 F 5/02, 1967.

2.Патент США 3.61.4403,

кл. 235-155, опублик. 1971 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| "Одноразрядный десятичный сумматор в коде "5421" | 1988 |

|

SU1658143A1 |

| Устройство для умножения | 1988 |

|

SU1501046A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1987 |

|

SU1481897A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Аналого-цифровой сумматор | 1986 |

|

SU1316006A1 |

| Одноразрядный десятичный сумматор в коде "5421 | 1988 |

|

SU1575171A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

гл, пгл.. тлллллллллллл

Перенос

Pvi.

Авторы

Даты

1981-09-30—Публикация

1979-08-30—Подача