Предметом изобретения является двоичная сетевая система обучения, отличающаяся тем, что состоит из входного иерархического уровня, иерархического уровня соединения, первого иерархического уровня двоичных логических элементов с первыми аналогичными логическими элементами, второго иерархического уровня двоичных логических элементов со вторыми аналогичными логическими элементами и иерархического выходного уровня, в которой каждое условие соединения между соседними иерархическими уровнями ограничено односторонним направлением передачи со стороны их входа к выходу, и каждый уровень имеет независимые пути передачи (сигнала) без взаимных соединений, причем иерархический уровень соединения имеет средство для выбора любого одного из непосредственного соединения и соединения, осуществленного через инвертор, относящихся к путям передачи от соответствующих сигнальных устройств во входном уровне к соответствующим сигнальным устройствам в первом иерархическом уровне двоичных логических элементов в сети обучения.

Подробное описание изобретения

Область техники, к которой относится изобретение

Изобретение относится к двоичной системе обучения, применяемой в распознавании символов, управлении движением робота и ассоциативной памяти.

Уровень техники

Система обучения известна как нейронная сеть. Нейронная сеть представляет собой схему, состоящую из имеющих весовой коэффициент (взвешенных) элементов нейронных клеток (нейрона) в сети таким же образом, что и основные устройства обработки информации при функционировании нейронных клеток живого тела, причем нейронную сеть применяют, например, в распознавании символов, управлении движением робота и в ассоциативной памяти.

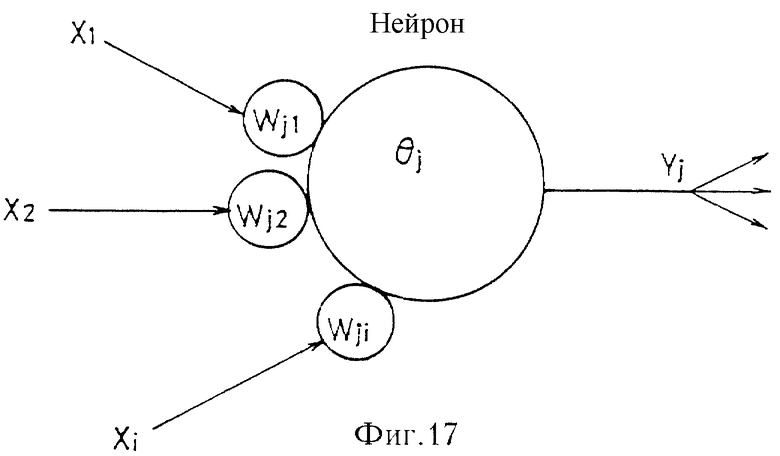

Нейрон NE, изображенный на фиг.17 в виде одного устройства, состоит из средства для приема входного сигнала от другого нейрона, средства для изменения входного сигнала согласно определенному правилу в средстве соединения, средства для ограничения порога его изменения и средства для выдачи измененного выходного сигнала. Дополнительно в средстве соединения с другим нейроном к устройству добавляют весовой коэффициент [Wij], указывающий мощность сигнала при соединении.

Условие соединения данного нейрона включает в себя соединение с возбуждением (Wij > 0), указывающее условие, при котором чем больше входной сигнал самого нейрона, тем больше входной сигнал от другого нейрона, и соединение с подавлением (Wij < 0), указывающее условие, при котором чем меньше входной сигнал самого нейрона, тем, наоборот, больше входной сигнал от другого нейрона. Тогда изменение этого весового коэффициента [Wij] и порогового значения θi приводят к измененному составу сети.

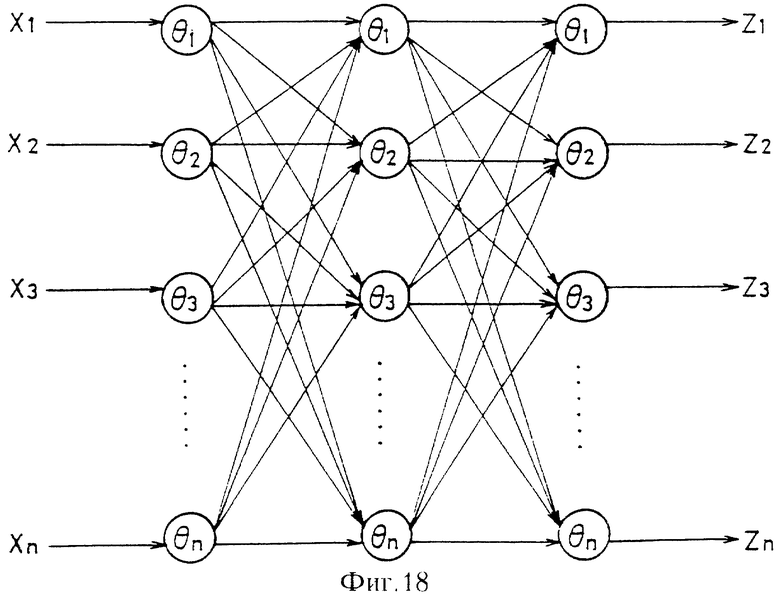

Фиг. 18 изображает нейтральную сеть, состоящую из нейрона NE, указанного выше, который включает в себя входной иерархический уровень, средний иерархический уровень и выходной иерархический уровень, причем каждый уровень не обладает каким-либо средством соединения, а в среднем уровне можно использовать множество уровней. Такая сеть осуществляет передачу (распространение) входного сигнала входного иерархического уровня к среднему уровню, и затем сигнал изменяют в нем в соответствии с коэффициентом связи, или весовым коэффициентом, и пороговым значением, а результирующий сигнал поступает на выходной уровень. В выходном уровне сигнал далее обрабатывают в качестве выходного сигнала Z посредством добавления какого-либо весового коэффициента и порогового значения.

Входной сигнал NEX в среднем и выходном уровнях подсчитывают по формуле 19, указанной ниже.

NEXj = ∑Wji•Xi+θj

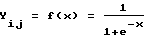

Затем входной сигнал NEX нейрона выходит после нелинейной обработки. Далее, выходной сигнал Yj или Zj в среднем и выходном уровнях получают с помощью Sigmoid коэффициента так, как в общем виде указано формулой 20.

Yj = 1/{1+exp(∑Wji•Xi+θj)}

В этом случае обучение предназначено для изменения весового коэффициента и порогового значения, чтобы уменьшить или установить, предпочтительно, равной нулю ошибку между реальным выходным сигналом Zj и заранее определенным выходным сигналом Tj (сигналом управления). Это значение изменения задается таким способом, чтобы использовать передачу сигнала ошибки в обратном направлении, и значение изменения в формуле, указанной выше, отлично для нейрона во входном иерархическом уровне или среднем уровне.

В аналоговых схемах, применяемых в указанной сети, интенсивность входного или выходного сигнала выражена в виде напряжения, весовой коэффициент нейрона выражен сопротивлением, существующим на каждой нейронной цепи, а выходной коэффициент нейрона (Sigmoid коэффициент) является коэффициентом распространения усилителя. И чтобы указать выходную и подавляющую пары между нейронами, выходной сигнал усилителя разделяют на два выходных сигнала, чтобы сформировать положительный или отрицательный сигнал посредством инвертирования на инверторе одного из выходных сигналов.

Указанная система, включающая в себя аналоговые схемы, имеет недостатки, перечисленные ниже.

а. Неверные операции элементов нейрона являются результатом температурных свойств.

b. Что касается управления ошибкой между реальным выходным сигналом Z и выходным сигналом управления Т, указанным выше, то схема проверки ошибки усложнена так же, как и затруднено сведение ошибки к нулю.

с. Использование усилителя вносит дополнительное усложнение и увеличивает размер схемы, время работы увеличивается и приводит к затруднению, заключающемуся в том, что сеть корпорации не получается.

Цифровые схемы для нейтральной сети предложены в опубликованной японской патентной заявке 108594/93. В этом случае все элементы нейрона состоят из логических элементов, не выполняющих неправильные операции из-за своих температурных свойств.

Однако система, имеющая цифровые схемы, указанные выше, связана с проблемами, описанными ниже.

А. Для распространения сигнала между соответствующими уровнями используют импульс, чтобы указать плотность импульсов (количество импульсов в единицу времени) в качестве величины аналогового сигнала. Соответственно, эта система не способна к сведению ошибок к нулю и тратит много времени на работу.

В. Объем каждого элемента нейрона велик, таким образом приводя к наибольшей и увеличенной конструкции нейтральной сети.

С. Во время обучения изменяющееся значение весового коэффициента и порогового значения должны управляться в соответствующих среднем и выходном уровнях с использованием предшествующего строения нейтральной сети.

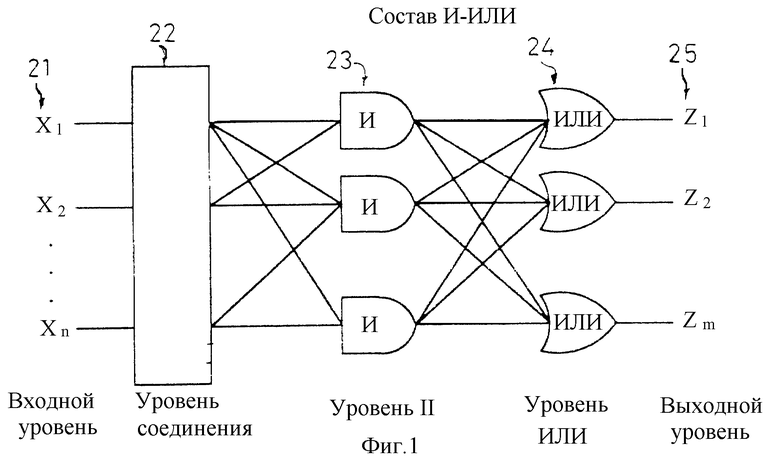

Чтобы решить проблемы, указанные выше, заявитель предлагал новую двоичную систему обучения, состоящую из логических элементов, как показано на фиг. 1 патентной заявки США 744299/96.

Сеть обучения состоит из входного иерархического уровня 21, имеющего множество двоичных входных выводов X1, Х2,...Хn, иерархического уровня соединения 22, первого уровня двоичных логических элементов (уровень И) 23 с множеством аналогичных логических элементов (например, логических элементов И), второго уровня двоичных логических элементов (уровень ИЛИ) 24 с множеством аналогичных логических элементов (например, логических элементов ИЛИ) и выходного иерархического уровня 25, причем соответствующие уровни не имеют никакого соединения внутри, и условие соединения между соседними уровнями ограничено только односторонним направлением от входного иерархического уровня до выходного иерархического уровня (поступательной передачей).

Пару в иерархическом уровне соединения между каждым из устройств входного иерархического уровня и каждым из устройств уровня И выбирают в соответствии с условиями соединения, указанными ниже.

(1) непосредственное соединение

(2) соединение через инвертор

(3) все соединения с [1]

(4) все соединения с [0]

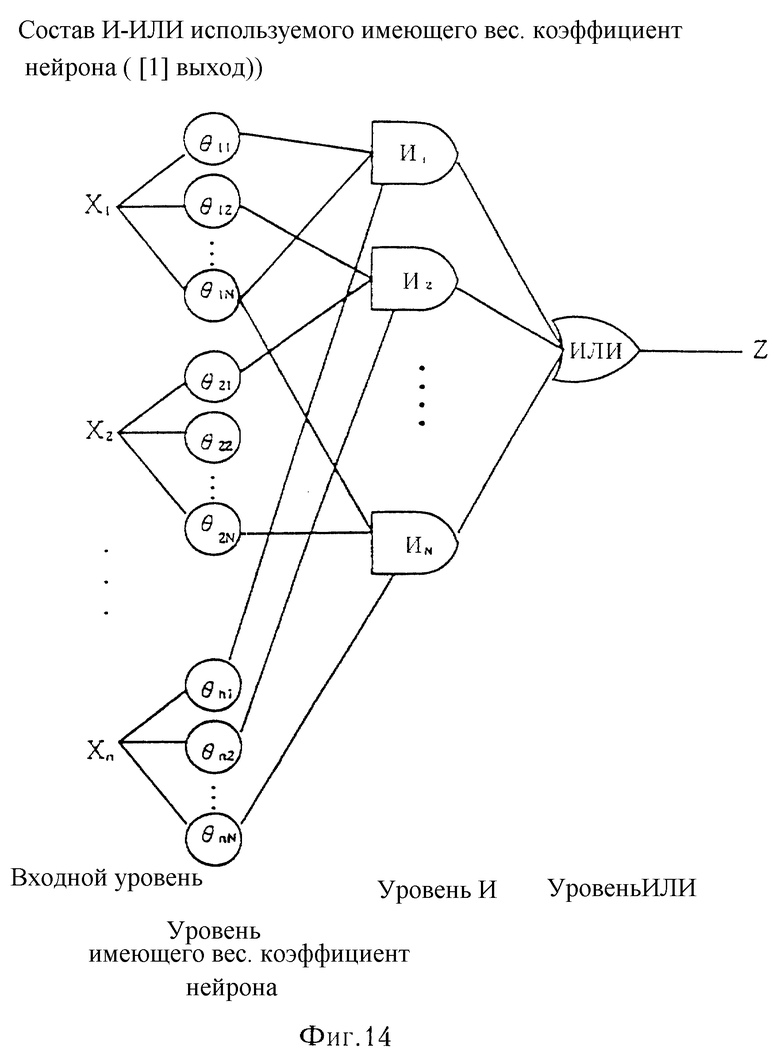

Иерархический уровень соединения, примененный к условиям соединения, указанным выше, может состоять из имеющих весовой коэффициент нейронов, и можно затем получить сеть обучения, которая показана на фиг.14.

В данном случае для упрощения объяснения на фиг.14 показаны только одно устройство уровня ИЛИ 24 и только один соответствующий вывод Z.

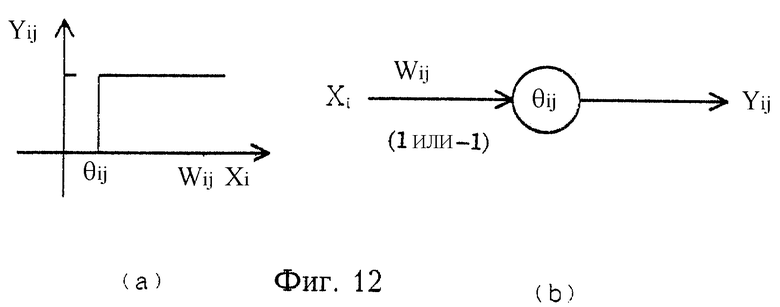

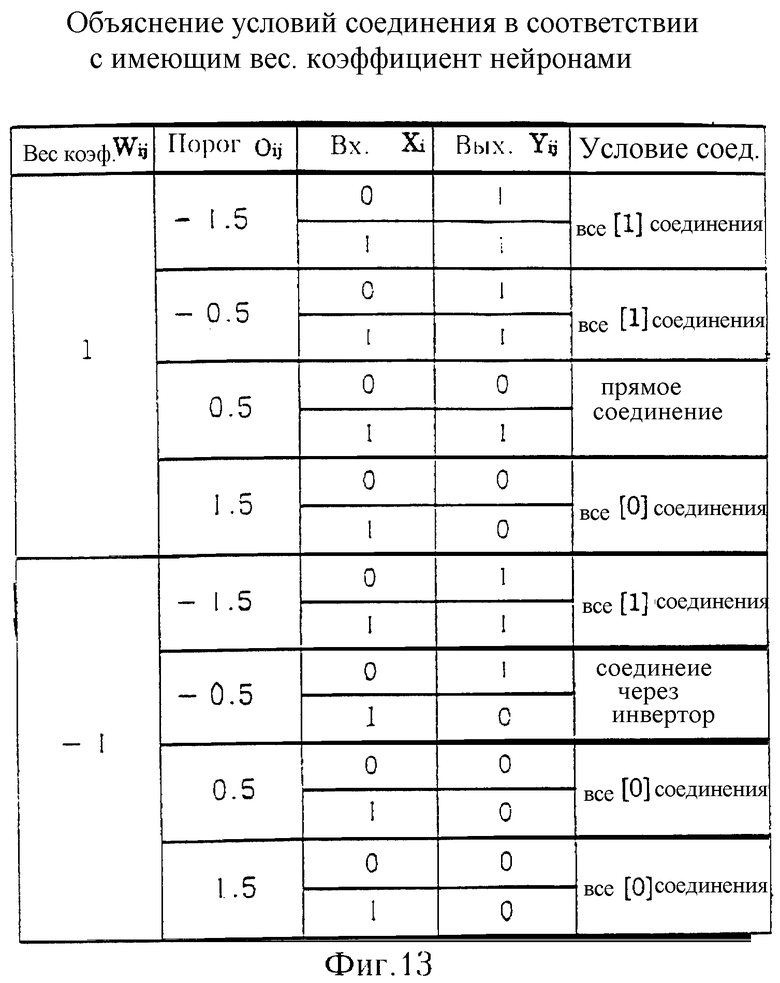

Имеющие весовой коэффициент нейроны NE, как показано на фиг.12, имеют один вход и один вывод, причем весовой коэффициент Wij от входного сигнала является одним из 1 или -1, а пороговое значение θij выбирают равным -1,5, -0,5, 0,5 и 1,5.

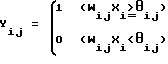

Тогда выходной сигнал Yij, заданный входным сигналом Xi, весовым коэффициентом Wij и пороговым значением θij, соответствует четырем условиям соединения, указанным выше. Выходной сигнал Yij рассчитывают по формуле 3 или формуле 4, приведенным ниже.

или

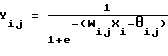

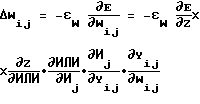

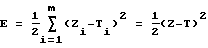

При обучении величина ошибки Е между реальным выходным сигналом Z и выходным сигналом управления Т может быть получена по формуле 5, как указано ниже.

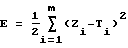

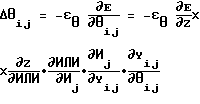

В этом случае обучение выполняют посредством управления весовым коэффициентом Wij и пороговым значением θij, аналогично предшествующей идее. Когда весовой коэффициент Wij и пороговое значение θij управляются в соответствии с ошибкой Е, снижающейся при самом высоком быстродействии, их значения управления ΔW и Δθ получают по формуле 1 или формуле 6.

или

εW,εθ являются положительными и рассчитывают, как указано ниже, по правилу обучения с использованием распространения сигнала ошибки в обратном направлении.

Выходной сигнал в этом случае является единственным, поэтому

Соответственно

Так как имеется связь Z=OR,

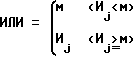

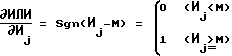

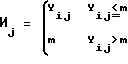

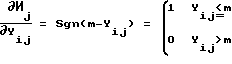

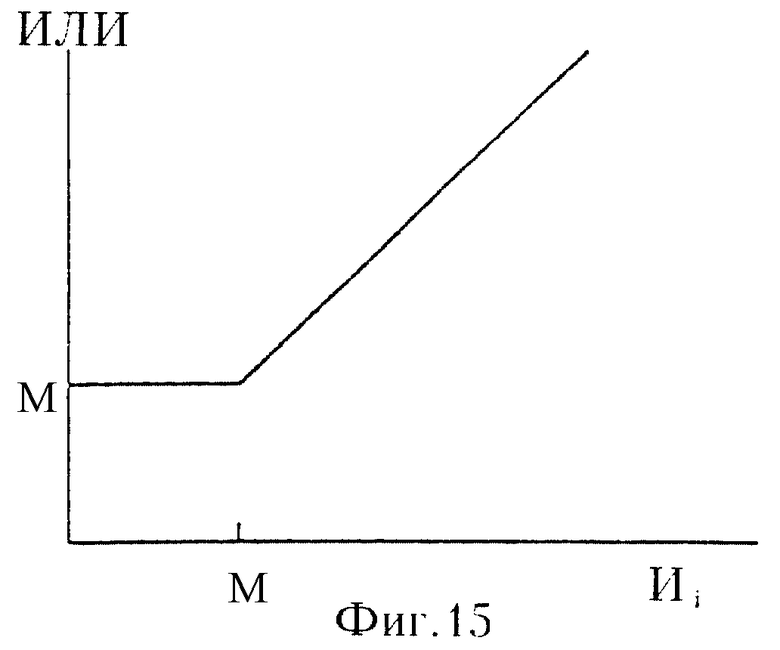

В результате сигнал на логическом элементе ИЛИ вычисляют с помощью коэффициента непрерывности, указанного ниже.

Здесь, М - максимальное значение при приблизительных входных сигналах без Иi, а именно

М = Мах(Иi, i = 1, 2, 3.., i ≠ j),

Фиг.15 указывает это фактическое значение. Тогда,

Аналогично, сигнал на логическом элементе И вычисляют с помощью коэффициента непрерывности, указанного ниже.

Здесь, м - минимальное значение при приблизительных входных сигналах без Иi, а именно m = Min(Иi, i = 1, 2, 3.., i ≠ j ).

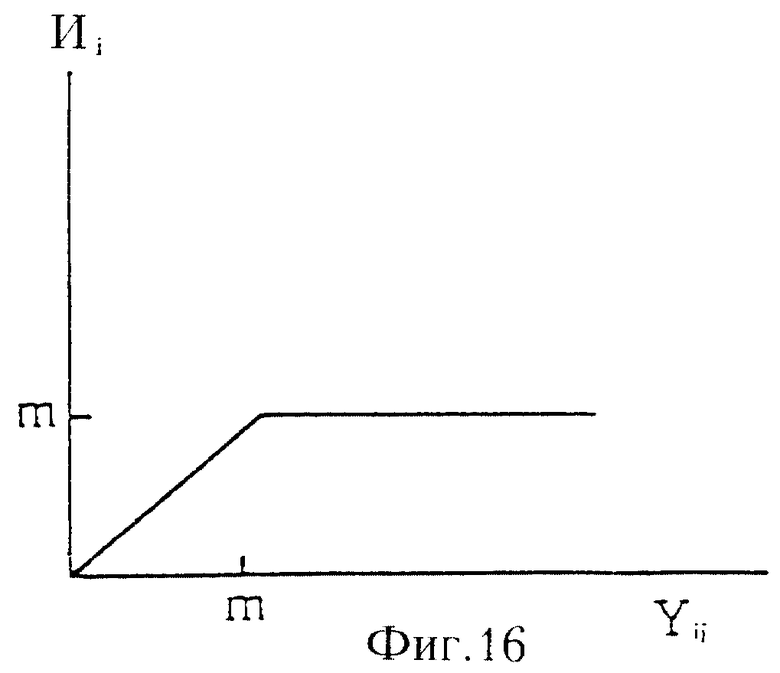

Фиг.16 указывает это фактическое значение. Тогда,

Наконец,

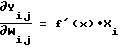

X = WijXi-θij

Тогда

Так как f'(x) > 0, то значения управления ΔW весового коэффициента Wij и порогового значения Δθ получают при f'(x) = 1, по формуле 17.

ΔWij = -εW(Z-T)Sgn(Иj-M)Sgn(m-Yij)Xi

Δθij = -εθ(Z-T)Sgn(Иj-M)Sgn(m-Yij)(-1)

Если εW = 2, εW, εθ = 1, то

ΔWij = -2(Z-T)Sgn(Иj-M)Sgn(m-Yij)Xi

Δθij = (Z-T)Sgn(Иj-M)Sgn(m-Yij)

В указанной формуле все значения являются двоичными, тогда значения управления указывают выходной сигнал Z, сигнал управления Т и выходные сигналы И, Иi, Yi и Xi в логической форме.

Как отмечено выше, этот случай описывает двоичную систему обучения, в которой NE включает в себя один входной сигнал и один выходной сигнал, и Wij, θj, Yij, ΔWij,Δdθij и т.д. являются двоичными обозначениями, так же, как выходной сигнал, Yij и NE соответствуют четырем условиям соединения, указанным выше, таким образом, операции обучения заключаются в управлении условиями соединения между соответствующими входными сигналами Xi входного иерархического уровня и соответствующими устройствами (И) первого иерархического уровня логических элементов. Соответственно, при выполнении этого сеть обучения имеет простой состав, время обучения значительно сокращается и, более конкретно, ошибка Е легко сводится к нулю.

Объекты изобретения

Однако сеть обучения, указанная выше и раскрытая в патентной заявке США, включает в себя четыре условия соединения, хотя выходы устройств иерархического уровня соединения соответствуют двоичному счету.

Если сеть обучения, работающая с использованием двух условий соединения, может быть получена в настоящее время, это приведет к более простому аппаратному построению устройств уровня соединения, схемы коррекции ошибки и предпочтительно всей сети обучения.

Соответственно, сеть обучения, указанная выше, должна быть дополнительно усовершенствована для упрощения строения сети.

Настоящее изобретение предлагает усовершенствование двоичной сетевой системы обучения так, чтобы обучение могло быть точно и быстро выполнено, а состав в наибольшей степени упрощен.

Сущность настоящего изобретения

Для решения различных проблем, указанных выше, настоящее изобретение предлагает двоичную систему обучения, отличающуюся тем, что она состоит из входного иерархического уровня, имеющего двоичные входы, иерархического уровня соединения, первого иерархического уровня двоичных логических элементов с первыми аналогичными логическими элементами, второго иерархического уровня двоичных логических элементов со вторыми аналогичными логическими элементами и иерархического выходного уровня так, чтобы сформировать сеть обучения, в которой каждое условие соединения между соседними иерархическими уровнями ограничено односторонним направлением передачи со стороны входа к выходу и каждый уровень имеет независимые пути (передачи сигналов) без взаимных соединений, причем иерархический уровень соединения имеет средство для выбора любого одного из непосредственного соединения и соединения, осуществленного через инвертор, относящихся к пути передачи от соответствующих устройств выдачи сигнала во входном уровне к соответствующим устройствам выдачи сигнала в первом двоичном иерархическом уровне логических элементов, таким образом, что выбранное соединение адаптировано для устранения или уменьшения соответствующих ошибок между первоначальными выходными сигналами в иерархическом выходном уровне и сигналами управления в сети обучения.

В настоящем изобретении двоичная система обучения, указанная выше, включает в себя способ, описанный ниже.

(1) Одно из условий соединения выбирают так, чтобы осуществлять обучение в случае, когда первоначальный выходной сигнал отличается от сигнала управления, и запрещать обучение в случае, когда оба сигнала, указанные выше, являются одинаковыми.

(2) Обучение осуществляют так, чтобы выбрать одно из условий соединения между устройствами выдачи сигнала во входном иерархическом уровне и устройствами выдачи сигнала в первом иерархическом уровне двоичных логических элементов в порядке выбора устройств от самого старшего до самого младшего в первом иерархическом уровне двоичных логических элементов, и для выбора всех входов в каждом устройстве одновременно или с самого старшего до самого младшего во входном иерархическом уровне.

(3) Обучение после выбора условия соединения с наиболее младшим устройством снова продолжают для наиболее старшего по мере необходимости.

В настоящем изобретении, включающем в себя двоичную систему обучения, указанную выше, первые и вторые логические элементы включают в себя множества логических элементов ИЛИ и схемы логических элементов И соответственно по их старшинству.

В двоичной системе обучения, указанной выше, первые и вторые логические элементы включают в себя множества логических элементов И и схемы логических элементов ИЛИ соответственно по их старшинству.

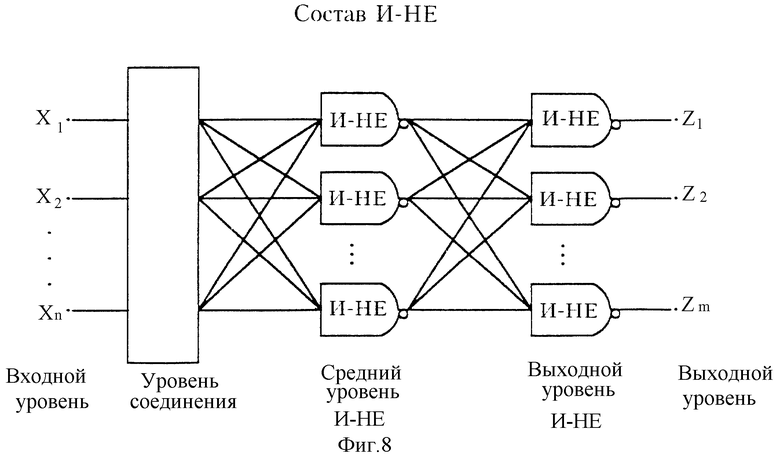

Далее, в двоичной системе обучения, указанной выше, первые и вторые логические элементы включают в себя множества логических элементов И-НЕ и схемы логических элементов И-НЕ соответственно.

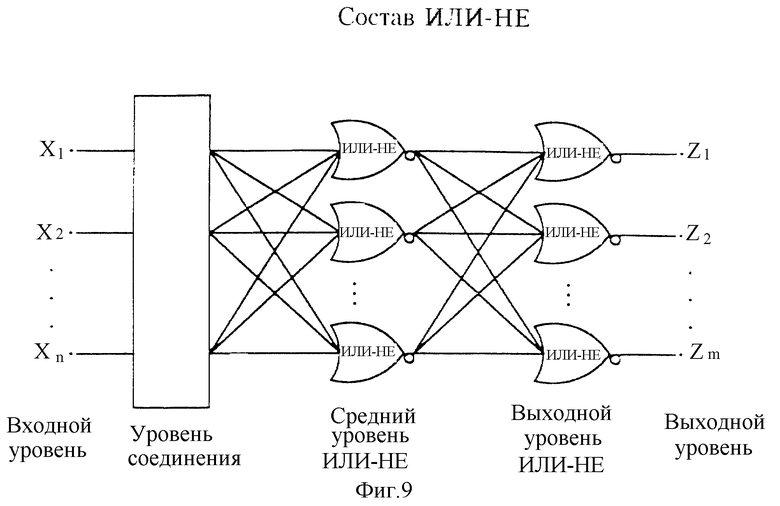

В другом случае указанной двоичной системы обучения первые и вторые логические элементы включают в себя множества логических элементов ИЛИ-НЕ и схемы логических элементов ИЛИ-НЕ соответственно.

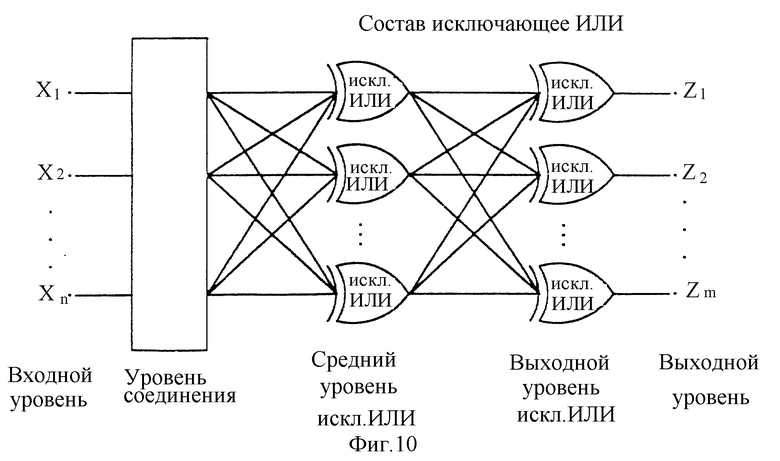

Наконец, в двоичной системе обучения первые и вторые логические элементы, включают в себя множества логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и схемы логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно.

Другие особенности и преимущества настоящего изобретения очевидны из нижеследующего описания со ссылкой на чертежи.

Варианты осуществления настоящего изобретения

Фиг. 1 изображает в виде блоков вариант осуществления настоящего изобретения, в котором двоичная система для сети обучения изображена состоящей из устройств уровня И и уровня ИЛИ.

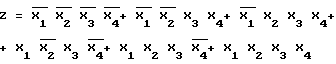

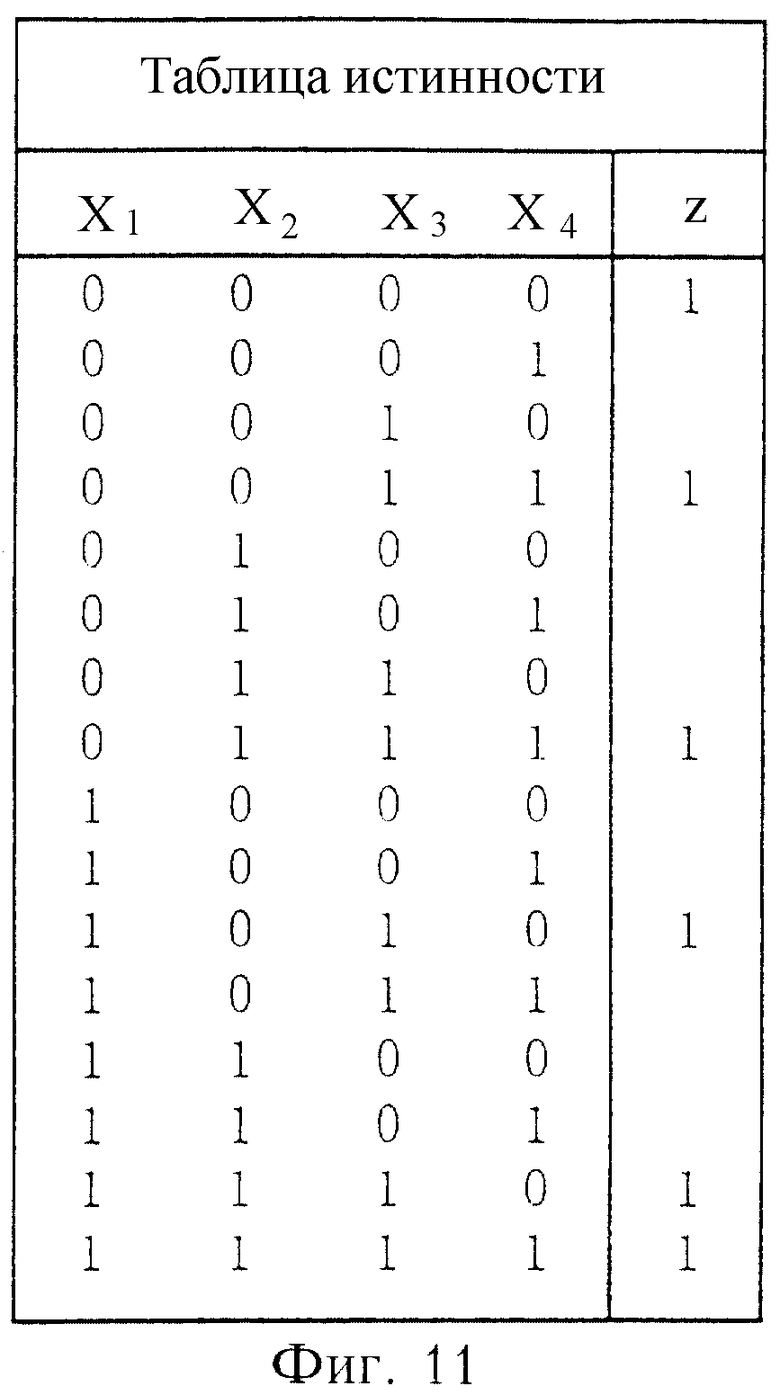

Фиг. 2 изображает логическую схему в соответствии с таблицей истинности, изображенной на фиг.11.

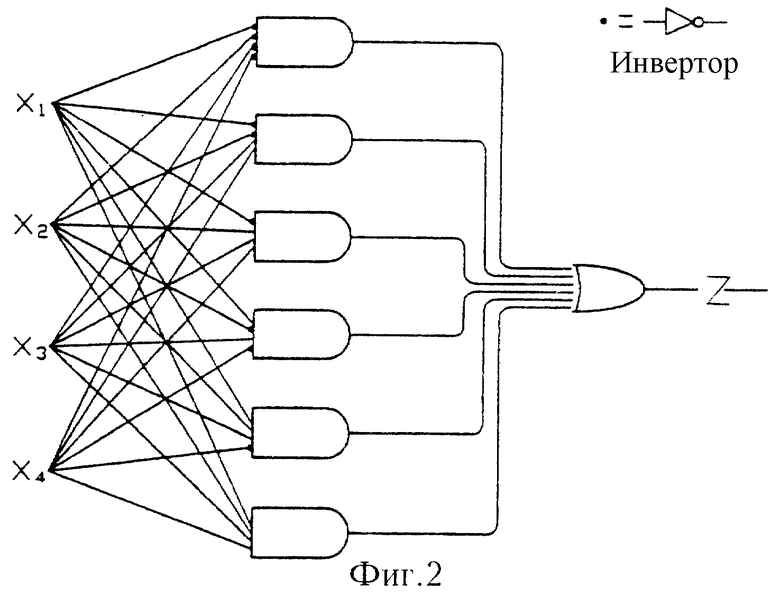

Фиг. 3 изображает сеть, имеющую только один выходной сигнал в качестве 1 бита.

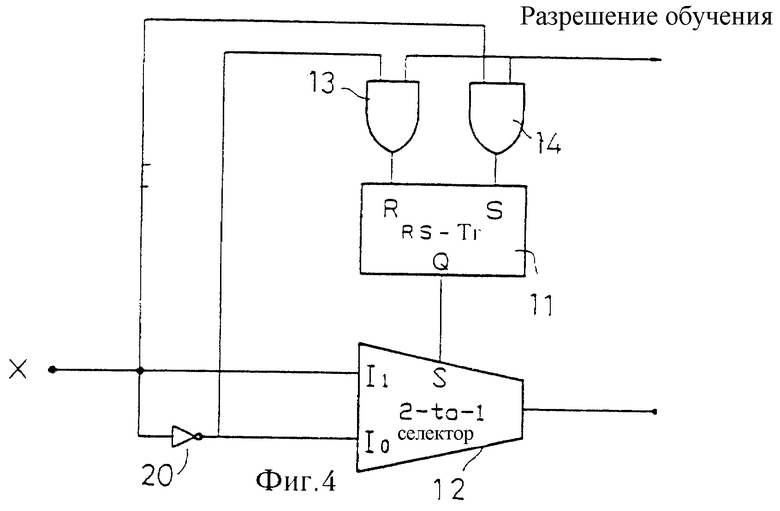

Фиг.4 изображает логическую схему для осуществления схемы соединения.

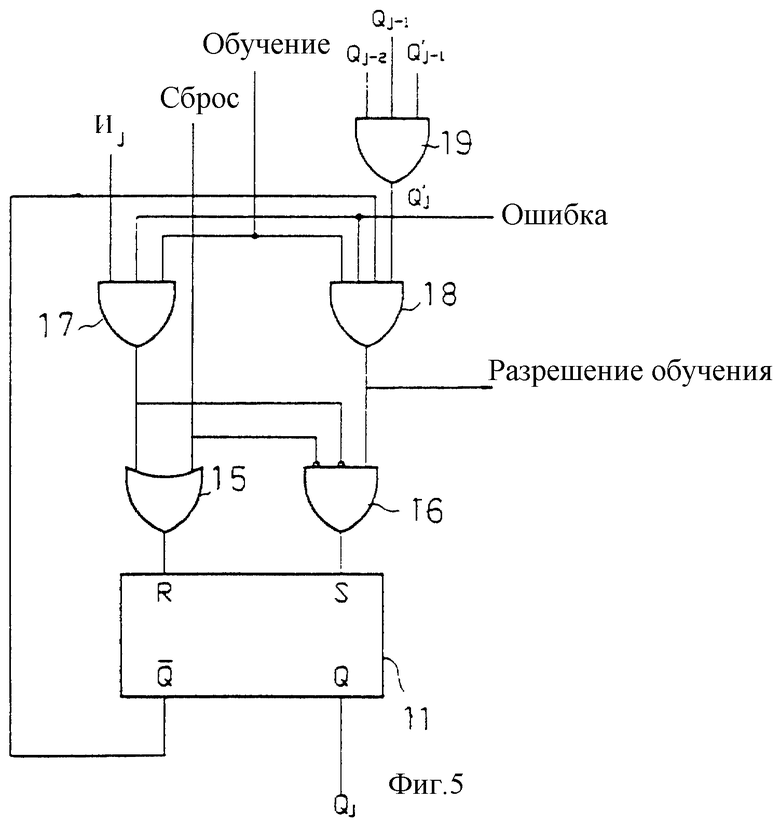

Фиг.5 изображает схему управления для операции обучения.

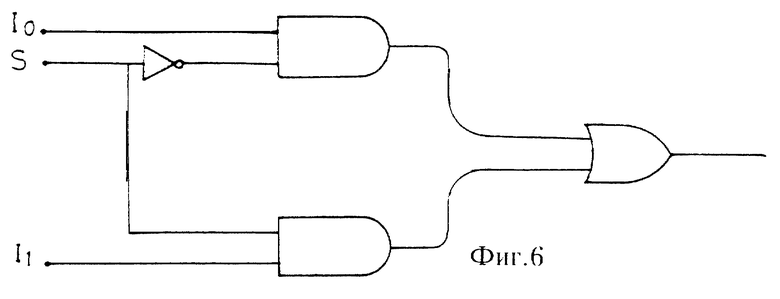

Фиг.6 изображает логическую схему селектора 2-в-1.

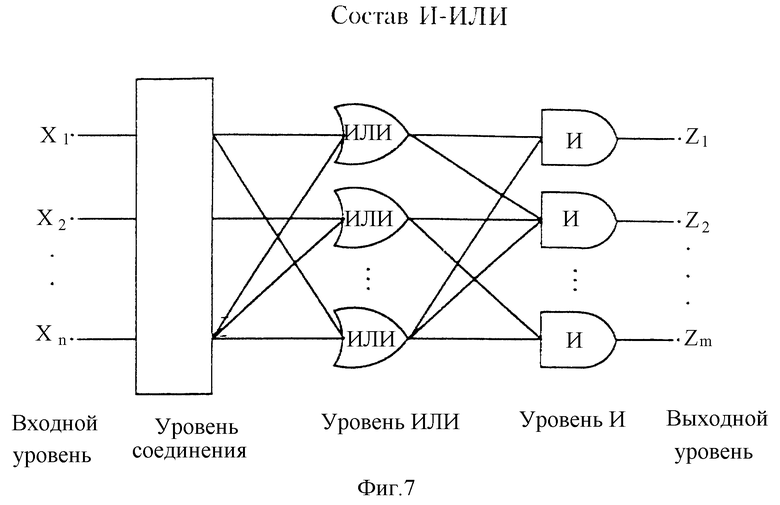

Фиг. 7 изображает в виде блоков сеть обучения с двоичной системой, включающей в себя иерархический уровень ИЛИ и иерархический уровень И.

Фиг. 8 изображает в виде блоков сеть обучения с двоичной системой, включающей в себя иерархический средний уровень И-НЕ и иерархический выходной уровень И-НЕ.

Фиг. 9 изображает в виде блоков сеть обучения с двоичной системой, включающей в себя иерархический средний уровень ИЛИ-НЕ и иерархический выходной уровень ИЛИ-НЕ.

Фиг.10 изображает в виде блоков сеть обучения с двоичной системой, включающей в себя иерархический средний уровень ИСКЛЮЧАЮЩЕЕ ИЛИ и иерархической уровень ИСКЛЮЧАЮЩЕЕ ИЛИ.

Фиг.11 изображает таблицу истинности для логического коэффициента.

На фиг.12 изображены (а) график, указывающий пороговый коэффициент имеющего весовой коэффициент нейрона, и (b) математическая иллюстрация имеющего весовой коэффициент нейрона.

Фиг. 13 поясняет условие соединения в соответствии с имеющим весовой коэффициент нейроном.

Фиг. 14 изображает сеть обучения с двоичной системой, в которой используется имеющий весовой коэффициент нейрон.

Фиг. 15 изображает график, приведенный для имеющего весовой коэффициент нейрона для логического элемента ИЛИ.

Фиг. 16 изображает график, приведенный для имеющего весовой коэффициент нейрона для логического элемента И.

Фиг.17 поясняет нейрон NE в качестве устройства.

И, наконец, фиг. 18 изображает нейтральную сеть, состоящую из изображенного нейрона NE.

Вариант осуществления настоящего изобретения в соответствии с усовершенствованной двоичной сетевой системой обучения раскрыт ниже со ссылками на чертежи.

Сеть обучения согласно настоящему изобретению подробно описана применительно к сети И-ИЛИ, в которой, как показано на фиг.1, первый двоичный логический элемент и второй двоичный логический элемент составляют иерархический уровень И и иерархический уровень ИЛИ соответственно.

А именно, сеть обучения включает в себя входной уровень 21, имеющий двоичные входы X1, Х2,..., Хn, иерархический уровень соединения 22, первый иерархический уровень двоичных логических элементов (уровень И) 23 с множеством логических устройств И, второй иерархический уровень двоичных логических элементов (уровень ИЛИ) 24 с множеством логических устройств ИЛИ и выходной уровень 25, имеющий выходы, соответствующие каждому устройству уровня ИЛИ 24.

В сети внутри каждого уровня не имеется никаких соединений, и связь между уровнями ограничена однонаправленным распространением (сигнала) от входного уровня 21 к выходному уровню 24 (поступательной передачей), при котором связь между уровнем И 23 и уровнем ИЛИ 24 является постоянной, и в качестве связи в уровне соединения 22 от каждого устройства входного уровня 21 к каждому устройству уровня И 23 выбирают любое одно из двух условий соединения, указанных ниже, для управления операцией обучения.

(1) непосредственное соединение

(2) соединение через инвертор

В этом случае иерархический уровень соединения 22 применяют, чтобы подсоединить каждое устройство входного уровня 21 к каждому устройству уровня И 23 соответственно.

Принцип этого варианта осуществления будет объясняться ниже на примере логического коэффициента из соотношения для логической переменной, указанной на фиг.

Эту формулу можно реализовать в виде логической схемы логическими элементами.

Соответственно, чтобы получить одни и те же относительно друг друга выходные сигналы Z согласно входным наборам (например, множество входных иллюстративных наборов), состоящим из X1, Х2,.... Xi, можно управлять условием соединения (в уровне соединения 22) между входным иерархическим уровнем 21 и иерархическим уровнем И 23.

Таким образом, операция обучения в сети обучения, которая показана на фиг. 1, выполняется посредством управления условием соединения в уровне соединения между каждым устройством входного уровня 21 и каждым устройством уровня И 23, чтобы обеспечить соответствие выходного сигнала Z при постоянном входном наборе с X1, Х2,..., Xi.

Так как в двоичной системе существует только два сигнала, соединение может быть получено или с помощью непосредственного соединения или посредством соединения через инвертор.

Чтобы осуществить связь с помощью двух соединений между входным уровнем 21 и уровнем И 23, а именно с помощью непосредственного соединения или с помощью соединения через инвертор, данная система определяет сигнал одним битом, например, устанавливая непосредственное подсоединение к 1 и подсоединение через инвертор к 0.

На фиг. 2 приведен случай, когда требуемых логических элементов имеется по меньшей мере 6, если входных наборов от (выводов) X1, Х2, Х3, Х4 имеется 6, когда входов - четыре и один выход Z.

В случае на фиг.1 достаточно создать первый уровень двоичных логических элементов, то есть уровень И 23, имеющий 2n-1 + 1 (а именно, половина 2n) устройств И, если входной уровень 21 включает в себя n частей входов в соответствии с входными наборами 2n-1 + 1 или меньше них, и выходной уровень 23 с одним и тем же выходным набором с Z1, Z2,..., Zn.

Указанный вариант осуществления объясняется схемами на фиг.1 следующим образом. Например, фиг.1 изображает сеть обучения, включающую в себя только один бит на выходе, в соответствии с сетью, показанной на фиг.3. Здесь элемент ИСКЛЮЧАЮЩЕЕ ИЛИ выдает сигнал ошибки, определяемый посредством реального выходного сигнала Z и выходного сигнала управления Т так, чтобы соответствующие входные сигналы X1,..., Хn через соответствующие схемы соединения подавались на логические элементы И 3, а затем на схему управления 4. В этом случае логический элемент Иj является одним из логических элементов И и передает сигнал к логическому элементу ИЛИ 2.

Схема соединения 5 принимает сигнал обновления для выбранного условия соединения от схемы управления 4 и обеспечивает распространение входного сигнала Х к логическому элементу И, или непосредственно к нему, когда он равен 1, или через инвертор, когда он равен 0.

На фиг. 4 приведена логическая схема для выполнения схемы соединения. В этом случае RS-Тг 11 является RS триггером, используемым для указания условия соединения между входом Х и логическим элементом И иерархического уровня И. Селектор [селектор 2-в-1] 12 используют, чтобы выбрать какое-либо одно из непосредственного соединения и соединения через инвертор между Х и И в соответствии с состоянием триггера RS-Тг 11.

Триггер RS-Тг 11 устанавливает на выходе сигнал 1, когда S = 1 и R = 0, он сбрасывается (в 0), когда S = 0 и R = 1, и сохраняет информацию о переданном сигнале, когда S=R=0. Соответственно, когда сигнал условия обновления в схеме управления 4 изменен на 1, состояние RS обновляется логическими элементами И 13 и 14, то есть, если Х равен 1, выходные сигналы "1" подаются на логический элемент И 14 и 0 - на логический элемент И 13 так, что RS-Тг 11 устанавливается в 1, и наоборот, если X равен 0, выходные сигналы "1" подаются на логический элемент И 13 и 0 - на логический элемент И 14 так, что RS-Тг 11 сбрасывается.

Селектор [селектор 2-в-1] 12 имеет два входа I0, I1 и вход выбора S. Если сигнал на входе S равен 0, то выбирают сигнал с входа I0, а если сигнал S равен 1, то выбирают сигнал с входа I1. Такой [селектор 2-в-1] 12 может использовать логическую схему, которая показана на фиг.6.

Соответственно, если значение входного сигнала Х равно 1, RS-Тг 11 устанавливается в 1 так, чтобы [селектор 2-в-1] 12 выбирал I1, тогда Х подсоединен непосредственно к логическому элементу И, а если значение входного сигнала Х равно 0, то RS-Тг 11 сбрасывается в 0 так, что [селектор 2-в-1] 12 выбирает I0, тогда Х подается на логический элемент И через инвертор 20.

Схема управления 4 является функциональной схемой для указания, какая из операций обучения будет осуществлена или не осуществлена в соответствии с выходными сигналами "обучение", сигналом "сброс", сигналом "ошибка", сигналом ИЛИ и сигналом И, и аналогично для выдачи сигнала состояния обновления (разрешение обучения) на схему соединения.

Перед операцией обучения схема управления 4 выдает сигнал "Сброс" для начальной установки состояний других схем в 0, то есть выходной сигнал всех логических схем устанавливается в 0.

В реальной операции обучения необходимо определить какое-либо одно из состояний, управляемых или нет входным сигналом X, выходным сигналом Z, сигналом управления Т и выходным сигналом логического элемента И, поскольку можно использовать правило обучения, конкретно указанное ниже.

(1) Система реализует операцию обучения, когда реальный выходной сигнал Z отличается от сигнала управления Т, но не тогда, когда они аналогичны. Сигнал ошибки получают обработкой реального выходного сигнала Z и сигнала управления Т (ИСКЛЮЧАЮЩЕЕ ИЛИ), то есть значение на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ равно 1 в качестве прямого (различного) состояния и равно 0 в качестве обратного (одинакового) состояния.

(2) Система реализует операцию обучения в схеме управления для управления каждым условием соединения в таком порядке, чтобы выбрать один из от самого старшего логического элемента И до самого младшего логического элемента И в уровне И, то есть в порядке И1, И2,.... Иn.

Фиг.5 изображает схему управления для осуществления такой системы обучения. В этом случае RS-Тг 11 связан с устройством Иj уровня И и используется в качестве RS-триггера для обучения. Когда выходной сигнал RS-Тг 11 равен 1, это указывает, что сигнал операции обучения передают на логический элемент И, и выходной сигнал логического элемента И определяется входным сигналом и условием соединения, а если выходной сигнал RS-Тг 11 равен 0, то выходной сигнал логического элемента И равен 0, что обычно не соответствует различным входным сигналам, то есть операция обучения остановлена.

RS-Тг сбрасывается в 0 логическим элементом ИЛИ и логическим элементом И, когда сигнал "Сброс" равен 1, то есть схема управления установлена в 0.

Во время операции обучения сигнал "Обучение" равен 1, и, если сигнал "Ошибка" равен 0, входной сигнал RS-Тг равен 0 из-за логического элемента ИЛИ 15, логического элемента И 16, 17 и 18 так, что RS-Тг сохраняет свое состояние (передачи сигнала), то есть система операции обучения не реализуется.

В то же время, если сигнал "Ошибка" равен 1, операция обучения разрешена. А именно, когда сигнал управления равен 1 и реальный выходной сигнал Z равен 0, сигнал "Ошибка" равен 1. В каждом условии обучения RS-Тг 11 выходной сигнал RS-Тг без его условия обучения включает в себя Q=0, то есть Q~=1 так, что RS-Тг выбран логическим элементом И 18, и первый один из RS-Тг без своего условия обучения, которое задано Qj-2, Qj-1, Q'j-1 и т.д., выбирается логическим элементом И 19.

Здесь, Qj-2 и Qj-1 являются выходным сигналом j-2 и выходным сигналом j-1 в RS-Тг и Q'j-1 является выходным сигналом логического элемента И, полученным с помощью Qj-1 и Qj-2. Когда выходной сигнал Иj равен 0, таким образом выбранный RS-Тг определен в соответствии с R=0 и S=1 так, что его RS-Тг устанавливается в 1, и аналогично выдает сигнал условия обновления (разрешение обучения).

Когда сигнал "Ошибка" равен 1, сигнал управления Т равен 0, и реальный выходной сигнал Z равен 0, логические элементы И, имеющие все выходные сигналы равными 1, выбираются логическим элементом И 17, и RS-Тг 1 сбрасывается в 0 принудительно, например, если Иj равен 1, то логическими элементами И 17, 16 и логическим элементом ИЛИ 15 RS-Тг принудительно сбрасывается в 0.

Поскольку вариант осуществления, описанный выше, раскрывает систему согласно настоящему изобретению, в сети обучения точно выполняется операция обучения для управления условием соединения между входами входного иерархического уровня 21 и соответствующими устройствами иерархического уровня И, и таких условий только два, то есть непосредственное соединение и через инвертор так, чтобы состав схемы проверки ошибки был более упрощен, а время обучения сокращалось до значения, близкого к предварительно заданному результату обучения. Действительно, ошибка между реальным выходным сигналом и сигналом управления точно приближается к 0.

В варианте осуществления, указанном выше, хотя первый уровень двоичных логических элементов и второй уровень двоичных логических элементов являются уровнем И и уровнем ИЛИ соответственно, настоящее изобретение не ограничено этим вариантом осуществления, а именно, как показано на фиг.7, 8, 9 и 10, первый двоичный логический элемент может быть уровнем ИЛИ с множеством логических элементов ИЛИ, средним уровнем И-НЕ с множеством логических элементов И-НЕ или средним уровнем ИСКЛЮЧАЮЩЕЕ ИЛИ с множеством логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и второй двоичный логический элемент может быть уровнем И с множеством логических элементов И, выходным уровнем И-НЕ с множеством логических элементов И-НЕ, выходным уровнем ИЛИ-НЕ с множеством логических элементов ИЛИ-НЕ, или выходным уровнем ИСКЛЮЧАЮЩЕЕ ИЛИ с множеством логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Промышленная применимость настоящего изобретения

Настоящее изобретение предлагает усовершенствованную двоичную систему для сети обучения, состоящую из входного иерархического уровня, имеющего двоичные входы, иерархического уровня соединения, первого иерархического уровня двоичных логических элементов с первыми аналогичными логическими элементами, второго иерархического уровня двоичных логических элементов со вторыми аналогичными логическими элементами и иерархического выходного уровня, чтобы сформировать сеть обучения, в которой каждое условие соединения между соседними иерархическими уровнями ограничено односторонним направлением передачи со стороны их входа к выходу, и каждый уровень имеет независимые пути передачи сигнала без взаимного соединения, причем иерархический уровень соединения имеет средство для выбора любого одного из непосредственного соединения и соединения, осуществленного через инвертор, относящихся к пути от соответствующих устройств выдачи сигнала во входном уровне к соответствующим устройствам выдачи сигнала в первом двоичном иерархическом уровне логических элементов в сети обучения.

Соответственно, состав схемы проверки ошибки дополнительно упрощается, и время обучения сокращается до значения, близкого к заданному результату обучения. Действительно, ошибка между реальным выходным сигналом и сигналом управления точно сводится к 0.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБЫ ОБУЧЕНИЯ В ДВОИЧНЫХ СИСТЕМАХ | 1997 |

|

RU2168713C2 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ С ИСПОЛЬЗОВАНИЕМ ПОДХОДА НА ОСНОВЕ НЕЙРОННОЙ СЕТИ | 2014 |

|

RU2595598C2 |

| АНАЛОГОВАЯ АППАРАТНАЯ РЕАЛИЗАЦИЯ НЕЙРОННЫХ СЕТЕЙ | 2020 |

|

RU2796649C2 |

| НЕЙРОННАЯ СЕТЬ КОНЕЧНОГО КОЛЬЦА | 2003 |

|

RU2279132C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИКЛ-ФИЛЬТРАЦИИ ДАННЫХ ИЗОБРАЖЕНИЯ | 1999 |

|

RU2154918C1 |

| СИСТЕМА И СПОСОБ ДЛЯ ИСКУССТВЕННОЙ НЕЙРОННОЙ СЕТИ, ИНВАРИАНТНОЙ К СДВИГУ | 2017 |

|

RU2656990C1 |

| СИСТЕМА УПРАВЛЕНИЯ И СПОСОБ УПРАВЛЕНИЯ ОКОМКОВАТЕЛЕМ | 2021 |

|

RU2813252C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ КОРРЕКЦИИ ОШИБОК В МОДУЛЯРНЫХ НЕЙРОКОМПЬЮТЕРАХ | 2003 |

|

RU2256213C2 |

| СИСТЕМА И СПОСОБ УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ МАТЕРИАЛА НА ОСНОВЕ ПРОГНОЗИРОВАНИЯ ТОЛЩИНЫ СЛОЯ МАТЕРИАЛА | 2021 |

|

RU2812444C1 |

| СПОСОБ КЛАССИФИКАЦИИ ЭЛЕКТРОЭНЦЕФАЛОГРАФИЧЕСКИХ СИГНАЛОВ В ИНТЕРФЕЙСЕ МОЗГ - КОМПЬЮТЕР | 2009 |

|

RU2415642C1 |

Изобретение относится к обучающим системам. Технический результат заключается в повышении точности и быстродействия. Двоичная система обучения состоит из входного иерархического уровня, имеющего двоичные входы, иерархического уровня соединения, первого иерархического уровня двоичных логических элементов с первыми логическими элементами, второго иерархического уровня двоичных логических элементов со вторыми логическими элементами и иерархического выходного уровня, причем каждое условие соединения между соседними иерархическими уровнями ограничено односторонним направлением передачи со стороны входа к выходу. 2 с. и 10 з.п. ф-лы, 18 ил.

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| ОБУЧАЮЩЕЕСЯ УСТРОЙСТВО | 0 |

|

SU200888A1 |

| US 4710898 А, 01.12.1987 | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

Авторы

Даты

2002-08-20—Публикация

1999-02-18—Подача