Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения функции адресной коммутации на два цифровых информационных выхода с уровнем транзисторно-транзисторной логики (ТТЛ) множества входных цифровых дифференциальных (разностных) сигналов

Uj = Uaj - Ubj (1)

в сложной помеховой обстановке при значительных величинах синфазной помехи

Ucj = (Uaj + Ubj)/2, (2)

искажающей обе компоненты

Uaj = Ucj +Uj/2, (3)

Ubj = Ucj - Uj/2, (4)

сигнала Uj, т.е. при высоких значениях (К>1) показателя помехоустойчивости

K = {M(Ucj/Uj}max, (5)

где j = 1,..., N - номер канала коммутируемого сигнала Uj,

изменяющийся от 1 до N включительно;

Uaj и Ubj - соответственно первая и вторая компонента сигнала Uj, измеряемая относительно общей шины (корпуса);

М(Х) - здесь и далее оператор выделения модуля величины X, заключенной в круглые скобки, т.е. в (5) величины Х=Ucj/Uj;

{Y}max - здесь и далее оператор выделения максимального значения величины Y, содержащейся в фигурных скобках, т.е. в (5) величины Y=M(Ucj/Uj);

/ - здесь и далее знак оператора арифметической операции деления.

Изобретение может использоваться, например, при построении многоканальных устройств для ввода последовательной информации в самосинхронизирующемся коде RZ с возвратом к нулю в режиме разделения во времени с помощью сигналов готовности (RDY) по протоколам на основе ГОСТ 18977-79 и РТМ 1495-75, имеющих широкое приложение в системах управления авиационной, судовой и прочей техники, расположенной, как правило, на подвижных объектах [1], в частности, при построении устройств для ввода информации типа [2].

В коде RZ каждый бит информации передается дифференциальным сигналом Uj в течение периода t=t1+t2 при t1=t2 так, что на входе коммутатора (приемника) сигнал в активной части t1 битового интервала t определяется величинами

Uj = (10±3) В при передаче логической 1, (6)

Uj = -(10±3) В при передаче логического 0, (7)

а в течение t2 времени возврата к нулю или при отсутствии передачи определяется величиной

Uj = ±1 В. (8)

В реальных условиях передача информации в бортовой аппаратуре происходит в сложной помеховой обстановке при синфазной помехе (2), могущей превышать по уровню полезный сигнал (6) или (7) в несколько раз. Это обусловило создание специализированной микросборки АП.004 Т53.430.006 ТУ для приема и декодирования "Кода последовательного 48 кГц" по двум каналам при высоком уровне синфазной помехи {M(Ucj)}max=15 В, т.е. при реальном показателе помехоустойчивости

Kp = 15/7>2. (9)

В этой связи на основе микросборок АП.004 легко построить коммутатор сигналов Uj кода RZ, содержащий N/2 микросборок АП.004 и два мультиплексора, например, на основе микросхем 1533КП8. Однако такой коммутатор будет иметь низкое быстродействие (т.е. может коммутировать сигналы Uj кода RZ частоты не более (48±12) кГц), фиксированный порог срабатывания (отпускания) и высокую стоимость, поскольку в настоящее время микросборка АП.004 стоит примерно 250 долларов.

В этой связи создание коммутатора цифровых дифференциальных сигналов с простыми установками как показателя помехоустойчивости (5), удовлетворяющего ограничению (9), так и порога обнаружения полезного сигнала "1" (6) или "0" (7), представляет, на наш взгляд, актуальную техническую задачу, разрешение которой позволит в целом повысить качество разрабатываемых многоканальных устройств для ввода информации в бортовой аппаратуре, например, устройств типа [2], поскольку их качество в значительной степени определяется основным показателем качества (5) именно коммутатора цифровых дифференциальных сигналов.

Действительно, известные коммутаторы сигналов типа [3], [4] и [5] не смогут обеспечить (например, два коммутатора по двум каналам) коммутацию сигнала (1) при ограничении (9), так как по каждому каналу могут передать сигнал при низком уровне помехи, т.е. при показателе (5) близком к нулю.

Из известных технических решений наиболее близким по технической сущности к предлагаемому является коммутатор цифровых дифференциальных сигналов, входящий в состав устройства для ввода информации [2] и образованный мультиплексором дифференциальных сигналов (содержит два мультиплексора-демультиплексора для адресной коммутации соответственно компонент Uaj и Ubj дифференциального сигнала Uj, описанного выражениями (1)-(4)), первым преобразователем уровней (содержит мультиплексор-демультиплексор с входными ограничительными резисторами и два детектора допусковых зон [6], каждый из которых выполнен на двух компараторах (микросхеме 521СА1) с выходами, объединенными по ИЛИ, причем выход мультиплексора-демультиплексора соединен с пороговыми входами обоих детекторов допусковых зон, выходы которых являются соответственно первым и вторым цифровыми информационными ТТЛ выходами коммутатора) и вторым преобразователем уровней для формирования пороговых напряжений детектирования сигналов Uj.

В процессе функционирования данного коммутатора первый детектор допусковой зоны вырабатывает сигнал "1" при сигнале Uaj (или Ubj) соответствующему сигналу (6), а второй детектор допусковой зоны вырабатывает сигнал "1" при сигнале Ubj (или Uaj) соответствующему сигналу (7). Таким образом, в данном коммутаторе детектирование кода RZ производится детекторами допусковых зон непосредственно по сигналам Uaj и Ubj, каждый из которых содержит помеху Ucj - см. выражения (2), (3) и (4). Следовательно, коммутатор устройства [2] может работать только при ограничении

M(Uj/2)>M(Ucj), (10)

т.е. характеризуется показателем помехоустойчивости

Kп= {M(Ucj/Uj}max<0,5, (11)

в несколько раз меньшим по сравнению со значением (9), требуемым для бортовой аппаратуры.

Основным недостатком коммутатора устройства [2] является низкая помехоустойчивость и аппаратурная сложность (каждый канал j имеет свой порог обнаружения сигнала (6) или (7) непосредственно по сигналу Uaj (или Ubj), содержащему помеху Ucj), обусловленные тем, что при его построении недостаточно полно учтена первичная исходная информация о коммутируемых сигналах Uj, компоненты которых маскируются помехами Ucj, описываемая, в частности, величинами и ограничениями типа (6)-(9).

Предлагаемым изобретением решается задача повышения помехоустойчивости коммутатора и его упрощения за счет как предварительной обработки каждого коммутируемого сигнала (ослабление его для исключения перегрузки линейных входов последующих электронных устройств, и заградительная фильтрация синфазной помехи), так и детектирования с помощью всего лишь двух порогов.

Для достижения этого технического результата в коммутатор цифровых дифференциальных сигналов, содержащий входы первых и вторых компонент цифровых дифференциальных сигналов, кодовый вход адреса коммутируемого канала, два цифровых информационных выхода, два компаратора и два мультиплексора-демультиплексора, адресные входы которых соединены с кодовым входом адреса коммутатора, дополнительно введены, два аттенюатора, формирователь положительного порогового напряжения, формирователь отрицательного порогового напряжения и дифференциальный усилитель, выход которого соединен с неинвертирующим и инвертирующим входами соответственно первого и второго компараторов, выходы которых соединены соответственно с первым и вторым цифровыми информационными выходами коммутатора, выходы формирователей положительного и отрицательного пороговых напряжений соединены соответственно с инвертирующим и неинвертирующим входами первого и второго компараторов, входы первых и вторых компонент цифровых дифференциальных сигналов коммутатора связаны через каналы первого и второго аттенюаторов с информационными входами первого и второго мультиплексоров-демультиплексоров соответственно, а информационные выходы первого и второго мультиплексоров-демультиплексоров соединены соответственно с неинвертирующим и инвертирующим входами дифференциального усилителя, причем каждый из аттенюаторов в каждом канале содержит делитель напряжения, образованный из двух резисторов, первый вывод первого из которых соединен с входом канала, а второй вывод первого резистора соединен с выходом канала и с первым выводом второго резистора, второй вывод которого соединен с общей шиной (корпусом).

Авторам неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение двух аттенюаторов, формирователя положительного порогового напряжения, формирователя отрицательного порогового напряжения и дифференциального усилителя) предлагаемого коммутатора, которые по сравнению с прототипом [2] обеспечивают ему повышение помехоустойчивости в несколько раз (более, чем в четыре раза) при меньших аппаратурных затратах.

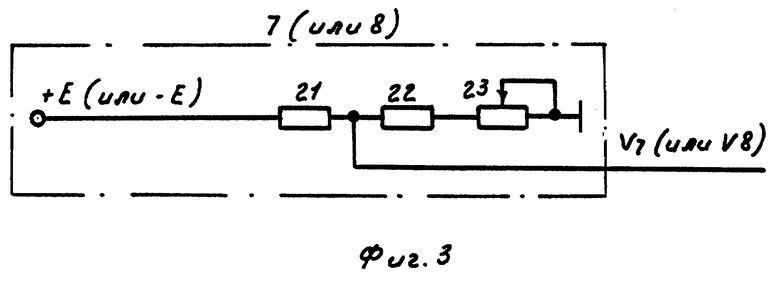

На фиг.1, 2 и 3 приведены электрические функциональные схемы коммутатора цифровых дифференциальных сигналов, первого (или второго) компаратора и формирователя положительного (или отрицательного) порогового напряжения соответственно, а на фиг.4 приведена электрическая функциональная схема эквивалентного дифференциального усилителя для расчета статического коэффициента Q передачи дифференциального напряжения Uj выбранного канала j на выход дифференциального усилителя, полученная заменой выбранных трактов прохождения сигналов Uaj и Ubj на неинвертирующий и инвертирующий входы дифференциального усилителя в виде соответствующих эквивалентных напряжений через соответствующие эквивалентные сопротивления.

Коммутатор цифровых дифференциальных сигналов (фиг.1) содержит первый 1 и второй 2 компараторы, первый 3 и второй 4 мультиплексоры-демультиплексоры, первый 5 и второй 6 аттенюаторы, формирователь 7 положительного порогового напряжения, выход которого соединен с инвертирующим входом первого компаратора 1, формирователь 8 отрицательного порогового напряжения, выход которого соединен с неинвертирующим входом второго компаратора 2, дифференциальный усилитель 9, выход которого соединен с неинвертирующим и инвертирующим входами первого 1 и второго 2 компараторов соответственно, первый и второй информационные цифровые выходы, являющиеся выходами первого 1 и второго 2 компараторов соответственно, кодовый вход адреса коммутируемого канала, соединенный с адресными входами первого 3 и второго 4 мультиплексоров-демультиплексоров, информационные выходы которых соединены соответственно с прямым и инверсным входами дифференциального усилителя 9, и входы первых и вторых компонент цифровых дифференциальных сигналов, связанные через каналы первого 5 и второго 6 аттенюаторов с информационными входами первого 3 и второго 4 мультиплексоров-демультиплексоров соответственно, причем каждый из аттенюаторов 5 и 6 в каждом канале содержит делитель напряжения, образованный из двух резисторов, первый вывод первого из которых соединен с входом канала, а второй вывод первого резистора соединен с выходом канала и первым выводом второго резистора, второй вывод которого соединен с общей шиной (корпусом).

Компаратор 1 (или 2) выполнен на основе схемы триггера Шмитта (см., например, в [7] рис. 3.546 на с.215) и содержит (фиг.2) операционный усилитель 10, пять резисторов 11-15, ускоряющий конденсатор 16 и четыре диода 17-20, причем инвертирующий и неинвертирующий входы компаратора 1 (или 2) соединены с первыми выводами первого 11 и второго 12 резисторов соответственно, инвертирующий вход операционного усилителя 10 соединен с вторым выводом первого резистора 11, анодом первого диода 17 и катодом второго диода 18, второй вывод второго резистора 12 соединен с катодом первого диода 17, анодом второго диода 18, первым выводом третьего резистора 13, первым выводом конденсатора 16 и неинвертирующим входом операционного усилителя 10, выход которого соединен с вторым выводом третьего резистора 13, вторым выводом конденсатора 16 и первым выводом четвертого резистора 14, второй вывод которого соединен с катодом третьего диода 19, анод которого соединен с выходом компаратора 1 (или 2), первым выводом пятого резистора 15 и катодом четвертого диода 20, анод которого соединен с общей шиной (корпусом), а второй вывод пятого резистора 15 соединен с шиной источника питания +5 В.

Формирователь 7 (или 8) положительного (или отрицательного) порогового напряжения (фиг. 3) содержит два постоянных резистора 21 и 22 и переменный резистор 23, причем выход формирователя 7 (или 8) соединен с первыми выводами первого 21 и второго 22 резисторов, второй вывод второго резистора 22 соединен с первым выводом переменного резистора 23, второй и третий выводы которого соединены с общей шиной (корпусом), а второй вывод первого резистора 21 соединен с шиной источника положительного (или отрицательного) напряжения.

Эквивалентный дифференциальный усилитель 24 (фиг.4) содержит два резистора 25 и 26 и дифференциальный усилитель 9, выход которого является выходом эквивалентного дифференциального усилителя 24, инвертирующий вход которого связан через первый резистор 25 с инвертирующим входом дифференциального усилителя 9, неинвертирующий вход эквивалентного дифференциального усилителя 24 связан через второй резистор 26 с неинвертирующим входом дифференциального усилителя 9, который является классическим дифференциальным усилителем (см., например, в [7] на с.166 рис.3.17) и содержит четыре резистора 27-30 и операционный усилитель 31.

Для N=8 (т.е. при п=3), +Е=+15 В, -Е=-15 В и условиях (6)-(9) составные части коммутатора (фиг.1-4) реализованы так, что операционные усилители (ОУ) 10 компараторов 1 и 2 и ОУ 31 дифференциального усилителя 9 выполнены на основе одной микросхемы 1401УД1 (содержит четыре ОУ), в качестве мультиплексора-демультиплексора 3 (или 4) использована микросхема 590КН6 (она позволяет адресно коммутировать напряжение с любого из восьми информационных входов на информационный выход в диапазоне от -Е=-15 В до +Е=+15 В при величине сопротивления открытого канала Rm=300 Ом), диоды 17-22м компараторов 1 и 2 реализованы на одной микросхеме (диодной матрице 2ДС627А), в качестве конденсатора 16 компаратора 1 (или 2) использован конденсатор типа К10-17а-М47-51 пФ±20%, в качестве переменного резистора 23 формирователя 7 (или 8) использован резистор типа С5-16ВА-0,25-300 Ом±10%, в качестве резисторов 27-30 использованы прецизионные резисторы типа С2-29В с одинаковыми номиналами 10 кОм±0,1%, в качестве первого и второго резистора (их величины обозначим через R1 и R2 соответственно) делителя каждого канала аттенюатора 5 (или 6) использованы миниатюрные (безвыводные) резисторы типа P1-12-0,25 с допуском ±2% и величинами R1=5,1 кОм и R2=2,7 кОм, а в качестве остальных резисторов (их величины далее обозначаются через Rq, где q - номер позиционного обозначения резистора на соответствующей схеме) используются резисторы P1-12-0,25 с допуском ±5% и величинами R11=10 кОм, R12=10 кОм, R13=10 мОм, R14=2,4 кОм, R15=8,2 кОм (см. фиг.2), R21=2,7 кОм, R22=240 Ом (см. фиг.3).

Описание функционирования коммутатора (фиг.1-4) далее ведется с помощью системы обозначений и положений, определенных в следующих пунктах.

1. На входах и выходах каналов аттенюатора 5 (или 6) сигналы описаны в виде векторов Ua[1:N] (или Ub[1:N]) и Va[1:N] (или Vb[1:N]) соответственно, число координат в каждом из которых равно N=8.

2. Формируемые на выходах соответствующих составных частей коммутатора аналоговые сигналы обозначим с помощью аббревиатуры Vq, где q - порядковый номер составной части в схеме, например, V9 - сигнал, действующий на выходе дифференциального усилителя 9.

3. С помощью метода эквивалентного генератора [8] величины эквивалентных напряжений на инверсном (V*bj) и прямом (V*aj) входах и величины эквивалентных резисторов 25 и 26 эквивалентного дифференциального усилителя 24 определены выражениями

V*bj = (Ubj х R2) / (R1 + R2), (12)

V*aj = (Uaj х R2) / (R1 + R2), (13)

R25 = R26 = [(R1 х R2) / (R1 + R2)] + Rm, (14)

где Rm - величина сопротивления открытого канала мультиплексора-демультиплексора 3 (или 4), т.е. микросхемы 590КН6;

R1 и R2 - величины сопротивлений соответственно первого и второго резисторов делителя канала j аттенюатора 5 (или 6);

х - здесь и далее знак оператора арифметической операции умножения.

4. Сигналы Vi и Vh (см. фиг.2), действующие соответственно на инверсном и прямом входах компаратора 1, определяются выражениями

Vi = V7, (15)

Vh = V9, (16)

а компаратора 2 - выражениями

Vi = V9, (17)

Vh = V8, (18)

5. Выходной цифровой информационный сигнал, действующий на выходе компаратора q=1 (или q=2) обозначим через Zq, т.е. Zq=1 соответствует напряжению Vq>2,4 В, a Zq= 0 - напряжению Vq<0,4 В, причем напряжение Vq формируется компаратором q из напряжения V10 двухсторонним диодным ограничителем, образованным резисторами 14 и 15 и диодами 19 и 20 (см. фиг.2).

6. В процессе функционирования компаратор q (q=1 или q=2) переключает цифровой сигнал Zq из "0 в 1" при условии

(Vh - Vi) - P > 0, (19)

или из "1 в 0" при условии

(Vh -Vi) - P < 0, (20)

где Р - ширина петли гистерезиса компаратора q, оцениваемая величиной

P = (V10max х R12) / (R12 + R13), (21)

где V10max - максимальное значение напряжения на выходе операционного усилителя 10 (фиг.2).

7. Поскольку [(Uaj х R2) / (R1+R2)] ≤ +Е, Uaj = Ucj + Uj/2 (см.(3)); то из формулы (5) получаем выражение для расчета показателя помехоустойчивости данного коммутатора

Кh = {[+E х (R1 + R2)] / {M(Uj)}min х R2} - [{M(Uj)max/(2 х {M(Uj)}min], (22)

где {M(Uj)}min и {M(Uj)}max - соответственно минимальное и максимальное значение модуля величины (6) (или (7)).

Предлагаемый коммутатор работает следующим образом.

По сигналам кода А[0:(n-1)]=A[0:2]=A0 A1 A2 (где Ai - разрядная цифра - "0 или 1" - разряда i=0, 1, 2 кода) адреса мультиплексор-демультиплексор 3 (или 4) вырабатывает напряжение V3 (или V4), близкое по величине к напряжению Vaj (или Vbj) адресуемого канала

j = 1 + A0 + 2 х A1 + 4 х A2. (23)

По напряжениям V3 и V4 (при R27=R28 и R29=R30) дифференциальный усилитель 9 вырабатывает напряжение V9 согласно выражению (см. в [7] с.166 и рис. 3.17)

V9 = (R29/R27) х (V3 - V4)]. (24)

Непосредственно из фиг.4 по аналогии с (24) определяем, что при R25=R26 (см. формулу (14)) величина V9, формируемая эквивалентным дифференциальным усилителем 24, определяется выражением

V9 = [R29/(R25 + R27)] х (V*aj - V*bj). (25)

преобразуя которое, с учетом выражений (3), (4) и (12)-(14), окончательно получаем

V9 = Q х Uj, (26)

Q = { R29 / {[(R1 х R2) / (R1 + R2)] + Rm + R27}} х [R2 / (R1 + R2)], (27)

где Q - статический коэффициент (положительное десятичное число) передачи компонент Uaj и Ubj сигнала Uj (см. (3) и (4) и (1)) на выход дифференциального усилителя 9.

Для описываемой реализации коммутатора (т.е. при R1=5,1 кОм, R2=2,7 кОм, R25=R26=(13,77/7,8) кОм, R27=R28=R29=R30=10 кOм, Rm=300 Ом, +Е=15 В, {M(Uj)} min=7 В и {M(Uj)}max=13 В) по формулам (27) и (22) соответственно получаем с округлением

U9 = 0,3 х Uj, (28)

Kh = 5. (29)

Из выражений (26) и (27) видно, что в идеальном случае синфазная помеха Ucj (2) на выходе дифференциального усилителя 9 отсутствует.

По напряжениям V9 и V7 (или V8) компаратор 1 (или 2) формирует цифровой сигнал Z1 (или Z2) согласно выражениям (19) и (20), детектируя полезный сигнал (6) (или (7).

Каждый из выходных цифровых информационных сигналов при цифровой обработке последующим устройством может быть нагружен на один ТТЛ вход, причем для этого устройства сигнал Z1 является сигналом последовательного кода принимаемой информации сопровождаемой далее синхросигналом

C = Z1 # Z2, (30)

где # - оператор логической операции ИЛИ на языке ABEL.

Сравнивая показатели (11) и (29), получаем

Kh / Kn > 10, (31)

что предлагаемый коммутатор имеет не менее, чем в 10 раз более высокую помехоустойчивость по сравнению с прототипом [2].

Сравним объемы оборудовании прототипа [2] и предлагаемого коммутатора с помощью формулы

G = G1 + G2 + G3, (33)

где G - объем оборудования устройства, оцениваемый в количестве эквивалентных корпусов, где за единицу измерения принят корпус микросхемы 590КН6, а остальные электронные компоненты сравниваются с единицей измерения по площади, занимаемой на печатной плате;

G1 - количество микросхем в устройстве;

G2 - объем оборудования, приходящийся на переменные резисторы типа СП5-16ВА, при условии, что двум резисторам соответствует один эквивалентный корпус;

G3 - объем оборудования, приходящийся на постоянные резисторы и конденсаторы, при условии, что 16 резисторам типа Р1-12-0,25 (или четырем резисторам типа С2-29В-0,25 и двум конденсаторам типа К10-17а-М47) соответствует один эквивалентный корпус.

Полагая, что в прототипе [2] второй преобразователь уровней выполнен в виде в виде восьми формирователей 7 или 8 пороговых напряжений (фиг.3), получаем

Gn = 5 + 4 + 2 = 11, (35)

Gh = 4 + 1 + 4 = 9, (36)

Gn / Gh = 11 / 9 = 1, 2 (2), (37)

что объем оборудования прелагаемого коммутатора примерно в 1,2 раза меньше объема оборудования прототипа [2].

Таким образом, по сравнению с прототипом [2] предлагаемый коммутатор, благодаря его существенным признакам, обладает более высокой помехоустойчивостью (см. оценку (31)) при меньшем объеме оборудования (см. оценку (37)).

Литература

1. Хвощ С.Т. и др. Организация последовательных мультиплексных каналов систем автоматического управления/ С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой; Под общ. ред. С.Т. Хвоща. - Л.: Машиностроение, Ленингр. отд-ние, 1989. - 271 с., ил. (С. 57-63: 1.9. Последовательные каналы информационного обмена в коде RZ).

2. А. с. CCCР 1786491 A1, G 06 F 13/00. Устройство для ввода информации /Д.Ю. Гусев и Ю.В. Крюков. Опубл. 07.01.1993. БИ 1.

3. А.с. СССР 661798, Н 03 К 17/80. Многоканальный коммутатор аналоговых сигналов А.А. Редкокаша. Опубл. 1979. БИ 17.

4. А.с. СССР 729844, Н 03 К 17/02, СССР. Коммутатор/ Ю.Н. Цыбин. Опубл. 1980. БИ 15.

5. Заявка 99108771/09 (009364) от 27.04.1999 с Решением о выдаче патента от 15.06.2000, МПК 7 G 06 F, G 06 F 13/00, G 06 F 11/18. Коммутатор цифровых сигналов / Е.Ф. Киселев и Ю.П. Палочкин.

6. Шило В.Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. - 2-е изд. , перераб. и доп. - М.: Сов. радио, 1979. - 368 с., ил. (На с. 229, рис.5.8 д - детектор допусковой зоны для сигнала Uc).

7. Хоровиц П. , Хилл У. Искусство схемотехники: В 2-х т. T.I. Пер. с англ. - 3-е изд., стереотип. - М.: Мир, 1986. - 598 с., ил. (На с. 166, рис. 3.17- дифференциальный усилитель, на с. 215, рис.3.54 б - триггер Шмитта).

8. Л. А. Бессонов. Теоретические основы электротехники (электрические цепи). - 9-е изд., перераб. и доп. - М.: Высшая школа, 1996. - 638 с., ил. (С.64-67: Метод эквивалентного генератора).

| название | год | авторы | номер документа |

|---|---|---|---|

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2003 |

|

RU2257005C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| КОММУТАТОР ЦИФРОВЫХ СИГНАЛОВ | 1999 |

|

RU2159006C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| МНОГОКАНАЛЬНЫЙ УЛЬТРАЗВУКОВОЙ УРОВНЕМЕР | 1992 |

|

RU2027978C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ С ПЕРИОДИЧЕСКОЙ КОРРЕКЦИЕЙ ДРЕЙФА | 2011 |

|

RU2480893C1 |

| УСТРОЙСТВО ДЛЯ ОХРАННОЙ СИГНАЛИЗАЦИИ | 1992 |

|

RU2050596C1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения функций адресной коммутации на два цифровых информационных выхода с уровнем транзисторно-транзисторной логики множества входных цифровых дифференциальных сигналов в сложной помеховой обстановке. Техническим результатом является повышение помехоустойчивости коммутатора и уменьшение объема его оборудования. Устройство содержит два компаратора, два мультиплексора-демультиплексора, два аттенюатора, формирователь положительного порогового напряжения, формирователь отрицательного порогового напряжения, дифференциальный усилитель. 4 ил.

Коммутатор цифровых дифференциальных сигналов, содержащий входы первых и вторых компонент цифровых дифференциальных сигналов, два цифровых информационных выхода, первый и второй компараторы, первый и второй мультиплексоры-демультиплексоры и кодовый вход адреса коммутируемого канала, соединенный с адресными входами первого и второго мультиплексоров-демультиплексоров, отличающийся тем, что он дополнительно содержит первый и второй аттенюаторы, формирователь положительного порогового напряжения, выход которого соединен с инверсным входом первого компаратора, формирователь отрицательного порогового напряжения, выход которого соединен с прямым входом второго компаратора, и дифференциальный усилитель, неинвертирующий и инвертирующий входы которого соединены с информационными выходами первого и второго мультиплексоров-демультиплексоров соответственно, выход дифференциального усилителя соединен с неинвертирующим и инвертирующим входами соответственно первого и второго компараторов, выходы которых соединены соответственно с первым и вторым цифровыми информационными выходами коммутатора, входы первых и вторых компонент цифровых дифференциальных сигналов которого связаны через каналы первого и второго аттенюаторов с информационными входами соответственно первого и второго мультиплексоров-демультиплексоров, причем каждый из аттенюаторов в каждом канале содержит делитель напряжения, образованный двумя резисторами, первый вывод первого из которых соединен с входом канала, а второй вывод первого резистора соединен с выходом канала и первым выводом второго резистора, второй вывод которого соединен с общей шиной (корпусом).

| Устройство для ввода информации | 1990 |

|

SU1786491A1 |

| Коммутатор двухпозиционных сигналов | 1977 |

|

SU653745A1 |

| Многоканальный коммутатор аналоговых сигналов | 1977 |

|

SU661798A2 |

| Коммутатор | 1977 |

|

SU729844A1 |

| Коммутатор аналоговых сигналов | 1977 |

|

SU738160A1 |

| Многоканальный коммутатор аналоговых сигналов | 1982 |

|

SU1034183A1 |

| ЕР 0438228 А2, 24.07.1991 | |||

| US 5281860 A, 25.01.1994 | |||

| ХВОЩ СТ., ДОРОШЕНКО В.В., ГОРОВОЙ В.В | |||

| Организация последовательных мультиплексных каналов систем автоматического управления | |||

| - Л.: Машиностроение | |||

| Ленинградское отделение, 1989, с.57-63. | |||

Авторы

Даты

2002-10-10—Публикация

2000-10-30—Подача