Изобретение относится к автоматике и вычислительной технике, предназначено для выполнения функции адресной коммутации множества входных цифровых сигналов нескольких типов на один информационный выход с уровнем ТТЛ и может быть использовано, в частности, при построении устройств для ввода информации в качестве адресуемого коммутатора разных типов импульсных и статических сигналов состояний датчиков каналов ввода, например четырех типов сигналов ("Разрыв/Корпус", ТТЛ, 27В/Разрыв, КМОП), определенных ГОСТ 18977-79.

В устройствах для ввода информации, например [1,2], ввод битовых данных осуществляется с помощью подключаемых циклически адресуемым коммутатором выборок сигналов состояний датчиков всех каналов ввода, число которых может доходить до 100 и выше.

Поскольку сигналы состояний датчиков могут существенно отличаться между собой по физическому представлению и временным параметрам, а число каналов ввода имеет тенденцию к возрастанию, то создание простого и быстродействующего коммутатора цифровых сигналов разных типов представляет, на наш взгляд, актуальную техническую задачу, разрешение которой позволит в целом повысить качество разрабатываемых устройств для ввода информации, например, типа [1,2].

Адресуемые коммутаторы сигналов находят широкое применение для передачи цифровых и аналоговых сигналов в устройствах автоматики и вычислительной техники [3-8] . Однако самые совершенные из них мультиплексоры [6] для коммутации цифровых ТТЛ сигналов и мультиплексоры-демультиплексоры [7] для передачи цифровых и аналоговых сигналов в диапазоне от -15 В до +15 В без привлечения дополнительных средств согласования не могут быть использованы в качестве коммутатора цифровых сигналов, определенных ГОСТ 18977-79.

Из известных технических решений наиболее близким к предлагаемому является коммутатор цифровых сигналов, входящий в состав устройства [2] и содержащий входной коммутатор, образованный блоком параллельных двухсторонних диодных ограничителей и мультиплексором-демультиплексором, преобразователь уровней, кодовые входы адреса и управления, информационный выход и сигнальные входы, число которых равно числу диодных ограничителей в блоке и каждый диодный ограничитель выполнен по схеме, описанной, например, в [9] и содержит первый и второй диоды ограничения сверху и снизу соответственно и резистор, первый вывод которого соединен с соответствующим сигнальным входом коммутатора, второй вывод резистора каждого диодного ограничителя соединен с соответствующим сигнальным входом мультиплексора-демультиплексора и с анодом и катодом первого и второго своих диодов соответственно, катоды первых диодов и аноды вторых диодов всех ограничителей соединены с шиной положительного источника питания и с общей шиной соответственно, кодовый вход адреса коммутатора соединен с адресным входом мультиплексора-демультиплексора, сигнальный выход которого соединен с информационным входом преобразователя уровней, кодовый вход управления коммутатора соединен с управляющим входом преобразователя уровней, выход которого является информационным выходом коммутатора.

Преобразователь уровней содержит два управляемых формирователя напряжений с переключаемыми выходными сопротивлениями и компаратор, причем формирователи напряжения выполнены на основе резисторов и транзисторных ключей разного типа проводимостей, входы (базы транзисторов) которых соединены с разрядными линиями кодового входа управления коммутатора, информационный вход преобразователя уровней соединен с выходом первого формирователя напряжения и с первым входом компаратора, выход второго формирователя напряжения соединен с вторым входом компаратора, выход которого является выходом преобразователя уровней.

Коммутатор [2] предназначен для выполнения функции адресной коммутации множества входных сигналов четырех типов стандарта ГОСТ 18977-79 на один информационный выход с уровнем ТТЛ.

Коммутатор [2] функционирует комбинационно так, что после каждого изменения кодов адреса и управления через время установления Tу вырабатывает на информационном выходе ТТЛ сигнал, соответствующий состоянию сигнального входа адресуемого канала ввода. Это осуществляется в процессе адресного подключения сигнального входа коммутатора через резистор диодного ограничителя и мультиплексор-демультиплексор на первый вход компаратора и выход первого формирователя напряжения (управляемого с линии младшего разряда кодового входа коммутатора) и задания порога срабатывания компаратора за счет управления вторым формирователем напряжения с линий двух старших разрядов кодового входа управления коммутатора.

Под каналом ввода здесь и далее имеется в виду канал связи [10], образованный выходом сигнала состояния датчика, проводной линией связи (ее длина по ГОСТ 18977-79 может доходить до L = 300 м) и сигнальным входом коммутатора, являющимся выходом канала ввода (связи).

Следовательно, коммутатор [2] является как частью более сложной системы (например, микропроцессорной системы обработки информации и управления), так и частью каналов ввода, и функционирование коммутатора [2] необходимо рассматривать с учетом всех системных существенных функциональных, динамических и конструктивных связей.

В качестве линий связи каналов ввода используют обычно экранированные провода или кабели с погонной емкостью между сигнальной жилой и экраном (корпусом), оцениваемой величиной Cп ≥ 100 пФ/м. Например [11], для кабеля КРЭТБ погонная емкость каждой жилы по отношению к другим жилам и к экрану составляет 250 пФ/м. В этой связи основным недостатком коммутатора [2] является его низкое быстродействие при адресации сигналов состояний датчиков "Разрыв/Корпус", подключенных к коммутатору через длинные линии связи, например при L = 300 м и Cп 100 пФ/м.

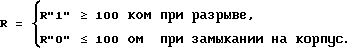

В указанных случаях этот недостаток коммутатора обусловлен длительной идентификацией сигнала "Разрыв/Корпус" при преобразовании в напряжение выходного сопротивления датчика этого сигнала, определяемого по стандарту ГОСТ 18977-79 выражением (1)

(1)

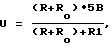

При адресации датчика сигнала "Разрыв/Корпус" через время Tу установления напряжение на первом входе компаратора стремится к величине (2)

(2)

где Rо - сопротивление резистора диодного ограничителя;

R1 - выходное сопротивление первого формирователя напряжения.

В установившемся режиме, например, при Rо = 1 кОм, R1 = 9 кОм получаем (3)

(3)

Однако при "Разрыве" (т.е. при R ≥ 100 кОм) на время установления напряжения (3) влияет емкость сигнального входа C = L•Cп, и время установления можно оценить по формуле

Tу = 2,2•L•Cп•(Rо+R1), (4)

т.е. при L = 300 м, Cп = 100 пФ, (Rо+R1) = 10 кОм получаем оценку

T1у = 660 мкс. (5)

Из (4) и (5) легко можно видеть, что повысить быстродействие коммутатора [2] при идентификации сигнала "Разрыв" можно лишь уменьшив величину сопротивления (Rо+R1), что в свою очередь повлечет за собой как увеличение рассеиваемой мощности в других каналах с типом сигнала 27 В/Разрыв, так и ухудшение массогабаритной характеристики коммутатора в целом. Действительно, при Rо = 1 кОм (или Rо = 10 кОм) резистор Rо должен быть одноваттным (или 0,125 Вт).

Кроме того, недостатком коммутатора [2] является то, что его преобразователь уровней выполнен неэкономно, поскольку для преобразования сигналов четырех типов преобразователь уровней управляется трехразрядным кодом.

Предлагаемым изобретением решается задача повышения быстродействия коммутатора и уменьшения его массы и габаритов за счет создания квазипостоянных условий преобразования комплексных сопротивлений в напряжения для всех входных сигналов типа "Разрыв/Корпус" и выборки всех типов входных сигналов с помощью стробов опроса.

Для достижения этого технического результата в коммутатор цифровых сигналов, содержащий входной блок параллельных двухсторонних диодных ограничителей, мультиплексор-демультиплексор, преобразователь уровней, кодовые входы адреса и управления, информационный выход и сигнальные входы, число которых равно числу диодных ограничителей во входном блоке, каждый из которых содержит первый и второй диоды ограничения сверху и снизу соответственно и резистор, первый вывод которого соединен с соответствующим сигнальным входом коммутатора, второй вывод резистора каждого диодного ограничителя соединен с соответствующим сигнальным входом мультиплексора-демультиплексора и с анодом и катодом первого и второго своих диодов соответственно, катоды первых диодов всех ограничителей соединены с шиной цепи питания положительного источника напряжения, кодовый адресный вход коммутатора соединен с адресным входом мультиплексора-демультиплексора, сигнальный выход которого соединен с информационным входом преобразователя уровней, управляющий вход которого соединен с кодовым входом управления коммутатора, дополнительно введены дешифратор, буферный передатчик, четыре элемента И-НЕ и вход стробов опроса, причем выход преобразователя уровней соединен с первым входом первого элемента И-НЕ, выход которого соединен с первыми входами второго и третьего элементов И-НЕ, диодные ограничители в блоке разделены на группы так, что в каждой группе аноды вторых диодов соединены между собой и через буферный передатчик связаны с соответствующим группе инверсным выходом дешифратора, адресные входы которого соединены с входами нескольких самых старших разрядов кодового входа адреса коммутатора, вход стробов опроса коммутатора соединен со стробирующим входом дешифратора и с вторыми входами первого и второго элементов И-НЕ, выход второго элемента И-НЕ соединен с первым входом четвертого элемента И-НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с вторым входом четвертого элемента И-НЕ и является информационным выходом коммутатора.

Авторам не известны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение дешифратора, буферного передатчика, четырех элементов И-НЕ и входа строба опроса, соединенного с вторыми входами первого и второго элементов И-НЕ и со стробирующим входом дешифратора, причем диодные ограничители во входном блоке разделены на группы так, что аноды вторых диодов соединены между собой и через буферный передатчик связаны с соответствующим группе инверсным выходом дешифратора) предлагаемого коммутатора, которые по сравнению с прототипом [2] повышают быстродействие коммутатора и уменьшают его массу и площадь, занимаемую им на печатной плате за счет создания квазипостоянных условий преобразования комплексных сопротивлений в напряжения для всех входных сигналов типа "Разрыв/Корпус" и выборки всех типов входных сигналов с по мощью стробов опроса.

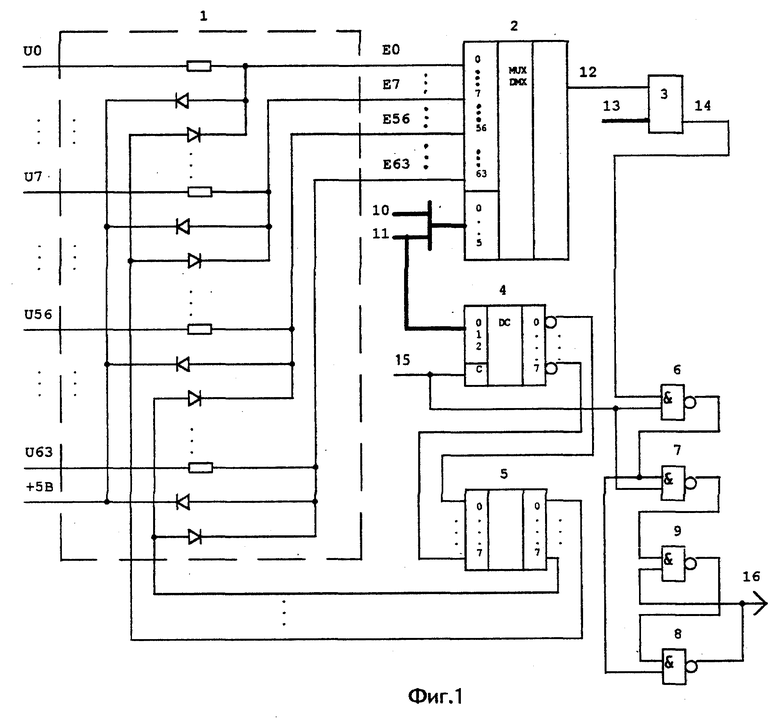

На фиг. 1 и 2 приведены функциональные схемы соответственно коммутатора цифровых сигналов и его преобразователя уровней для коммутации сигналов четырех типов ("Разрыв/Корпус", ТТЛ, 27 В/Разрыв, КМОП) при 64 сигнальных входах и разбивке блока диодных ограничителей на восемь групп по восемь ограничителей в каждой группе.

Коммутатор цифровых сигналов (фиг. 1) содержит входной блок 1 диодных ограничителей, мультиплексор-демультиплексор 2, преобразователь 3 уровней, дешифратор 4, буферный передатчик 5, первый 6, второй 7, третий 8 и четвертый 9 элементы И-НЕ, 64 сигнальных входа, соединенных с первыми выводами резисторов диодных ограничителей блока 1, причем второй вывод резистора каждого диодного ограничителя соединен с соответствующим сигнальным входом мультиплексора-демультиплексора 2 и с анодом и с катодом первого и второго своих диодов соответственно, катоды первых диодов всех ограничителей соединены с шиной цепи источника питания +5 В, диодные ограничители в блоке 1 разделены на восемь групп по восемь ограничителей так, что в каждой группе аноды вторых диодов ограничителей соединены между собой и связаны через передатчик 5 с соответствующим данной группе инверсным выходом дешифратора 4, кодовый адресный вход коммутатора, образованный трехразрядными входами 10 младших и трехразрядными входами 11 старших разрядов кода адреса, соединен с адресным входом мультиплексора-демультиплексора 2, сигнальный выход 12 которого соединен с информационным входом преобразователя 3, управляющий вход которого соединен с двухразрядным кодовым входом 13 управления коммутатора, выход 14 преобразователя 3 соединен с первым входом элемента 6 И-НЕ, выход которого соединен с первыми входами второго 7 и третьего 8 элементов И-НЕ, входы 11 старших разрядов кода адреса соединены с адресными входами дешифратора 4, вход 15 стробов опроса коммутатора соединен со стробирующим входом дешифратора 4 и с вторыми входами первого 6 и второго 7 элементов И-НЕ, выход второго элемента 7 И-НЕ соединен с первым входом четвертого элемента 9 И-НЕ, выход которого соединен с вторым входом третьего элемента 8 И-НЕ, выход 16 которого соединен с вторым входом четвертого элемента 9 И-НЕ и является информационным выходом коммутатора.

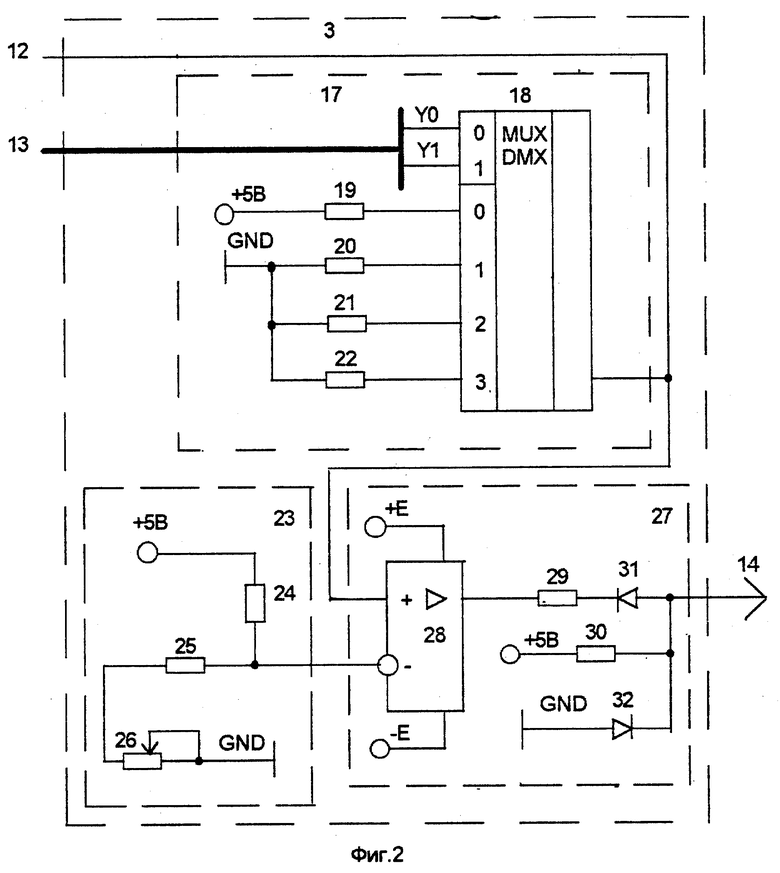

Преобразователь 3 уровней (фиг. 2) содержит управляемый формирователь 17 напряжения с переключаемым внутренним сопротивлением, образованный мультиплексором-демультиплексором 18 и резисторами 19-22, делитель 23 напряжения, образованный резисторами 24-26, и компаратор 27, содержащий операционный усилитель 28 и последовательно-параллельный двухсторонний диодный ограничитель, образованный резисторами 29 и 30 и диодами 31 и 32 ограничения напряжения на выходе 14 сверху и снизу соответственно в пределах уровней ТТЛ.

Составные части коммутатора (фиг. 1 и 2) реализованы следующим образом.

Каждая из восьми групп диодных ограничителей блока 1 выполнена на диодной матрице 2ДС628А (содержит дважды по восемь диодов для ограничения сверху и снизу соответственно), одном резисторном блоке Б19К-1-1-10 кОм ± 5%, содержащем семь резисторов, и одном резисторе С2-33Н-0,125-10 кОм ± 5%-А-Д-В.

Мультиплексор-демультиплексор 2 выполнен на девяти микросхемах 590КН6, первые восемь из которых параллельно адресуются с кодового входа 10 и коммутируют 64 информационных входа на восемь своих выходов, соединенных с информационными входами девятой микросхемы 590КН6, которая адресуется с кодового входа 11 и окончательно коммутирует один из 64 информационных входов мультиплексора-демультиплексора 2 на его выход 12.

В преобразователе 3 уровней (фиг. 2) мультиплексор-демультиплексор 18 выполнен на одной микросхеме 590КН6, резисторы 19-22, 24, 25, 29 и 30 типа C2-33H-0,125 имеют номиналы R19 = 68 кОм, R20 = 68 кОм, R21 = 3 кОм, R22 = 6,2 кОм, R24 = 3 кОм, R25 = 1 кОм, R29 = 3 кОм, R30 = 7,5 кОм, переменным резистором 26 является резистор СП5-16ВА-0,25-2 кОм ± 10%, операционным усилителем 28 - микросхема 544УД2А, а диодами 31 и 32 - диоды типа 2Д522Б.

В качестве дешифратора 4 и передатчика 5 использованы микросхемы 1533ИД7 и 1533АП5 соответственно, а элементы 6-9 И-НЕ реализованы на одной микросхеме 1533ЛА3.

Описание функционирования коммутатора ведется с помощью системы обозначений и положений, определенной в следующих пунктах.

1. Коды адреса и управления на входах 10, 11 и 13 обозначим через К10А = А0А1А2, К11А = А3А4А5, К13У = У0У1, где нулевой является младшим разрядом.

2. Напряжения на входах и выходах блока 1 обозначим через Ui и Ei соответственно, где индекс i = 0, ..., 63 определяется кодом адреса КА = А0... А5.

3. Напряжение на выходе 12 мультиплексора-демультиплексора 2 и напряжение на выходе делителя 23 обозначим через М12 и М23 соответственно.

4. Сигнал на входе 15 строба опроса обозначим через С15, причем под фронтом (или спадом) строба C15 понимается смена его логического уровня с "0" в "1" (или с "1" в "0").

5. Цифровые сигналы с уровнем ТТЛ, формируемые на выходах 14 и 16, обозначим через Х14 и Х16 соответственно.

6. Сопротивления каналов мультиплексоров-демультиплексоров 2 и 18 обозначим через R2 = 600 Ом и R18 = 300 Ом соответственно.

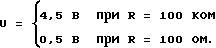

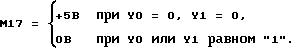

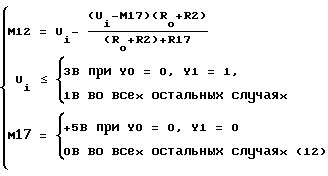

7. Внутренние сопротивление и напряжение формирователя 17 напряжения обозначим через R17 и М17 соответственно, причем (6)

(7)

(7)

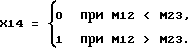

8. Компаратор 27 формирует цифровой сигнал X14 согласно выражению (8)

(8)

9. Динамика функционирования коммутатора (фиг. 1 и 2) по кодам К10А, К11А, К13У и стробу С15 организована так, что эти коды могут изменяться в течение только короткого времени TА ~100 нс после окончания фронта строба С15, в течение С15 = 1 триггер-защелка, собранный на элементах 6-9 И-НЕ, устанавливается в состояние Х16 = Х14 (см. (8)), которое фиксируется по спаду строба С15 и остается неизменным в течение С15 = 0.

В процессе функционирования коммутатора можно выделить два режима: режим Р1 преобразования внутренних сопротивлений сигналов состояний датчиков всех каналов ввода в напряжения, выполняемый при С15 = 0; режим Р2 опроса сигнала состояния датчика адресуемого канала ввода, выполняемый при С15 = 1.

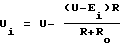

В режиме Р1 при С15 = 0 дешифратор 4 на всех своих восьми выходах формирует цифровые сигналы высокого ТТЛ уровня, которые через передатчик 5 и вторые диоды всех ограничителей блока 1 проходят на его выходы в виде напряжений Ei ~3 В, до уровня которых заряжаются все паразитные емкости C1пi, отнесенные к выходам блока 1 и сигнальным входам мультиплексора-демультиплексора 2. Через открытый канал мультиплексора-демультиплексора 2 (его сопротивление R2 = 600 Ом) одно из напряжений Ei проходит на выходы мультиплексоров-демультиплексоров 2 и 18 и первый (неинвертирующий) вход компаратора 27 в виде напряжения М12 ≅ Ei. Компаратор 27 формирует сигнал Х14 = 1, поскольку на второй (инвертирующий) его вход подано постоянное напряжение М23<М12 (см. (8)), выставляемое с помощью переменного резистора 26 в пределах от 1,25 В до 2,5 В. Поскольку М12 ≅ 3 В, то до этого уровня заряжается паразитная емкость С2п, отнесенная к выходам мультиплексоров-демультиплексоров 2 и 18 и первому входу компаратора 27. Кроме того, на входах блока 1 формируются напряжения Ui, которые в установившемся режиме определяются по формуле (9)

(9)

где U и R - внутренние напряжение и сопротивление сигнала датчика канала i = 0, ..., 63;

Rо = 10 кОм - величина сопротивления резистора любого ограничителя блока 1.

Из (9) видно, что при R << Rо Ui ~ U, а при "Разрыве" (т.е. при U = 0 и R ≥ 100 кОм) примерно через время (5) установится Ui ~ Ei ~ 3 В.

Таким образом, в режиме Р1 сначала по спаду строба С15 в триггере-защелке (элементах 6-9 И-НЕ) фиксируется выходной сигнал Х16 = Х14 (где Х14 - определяется выражением (8) в момент спада строба С15, затем при С15 = 0 паразитные емкости C1пi и C2п заряжаются до напряжений Ei ~ 3 В и М12 ~ 3 В, компаратор 27 выставляет сигнал Х14 = 1 согласно (8), а на входах блока 1 стремятся установиться напряжения Ui, определенные формулой (9) преобразования сопротивления R в напряжение.

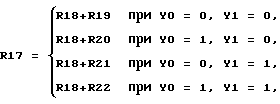

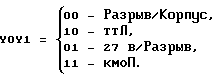

В режиме Р2 при С15 = 1 в течение времени TА ~ 100 нс на кодовых входах коммутатора устанавливаются коды адреса (К10А, К11А) и управления К13А = У0У1, причем К13У определяет тип адресуемого сигнала согласно выражению (10)

(10)

В течение С15 = 1 дешифратор 4 на одном из своих восьми выходов, адресуемом кодом К11А, формирует сигнал низкого уровня, который через передатчик 5 подключает к общей шине аноды вторых диодов только одной из восьми групп ограничителей блока 1. По коду (К10А, К11А) адреса выход одного из восьми ограничителей выбранной группы через мультиплексор-демультиплексор 2 подключается на выходы мультиплексоров-демультиплексоров 2 и 18 и первый вход компаратора 27. Если на адресуемом входе i = А0 + 2•А1 + 4•А2 + 8•А3 + 16•А4 + 32•А5 блока 1 присутствует сигнал Ui, соответствующий логической "1", то сигнал Х14 = 1 остается неизменным и триггер-защелка по сигналу С15 = 1 фиксируется в состоянии Х16 = Х14 = 1. В противном случае паразитные емкости C1пi и C2п будут разряжаться через разрядное сопротивление (11)

(11)

до величины М12 < М23, определяемой выражениями (12)

(12)

Время установления Tу напряжения М12 < М23 оценивается выражением

Tу = TА + TП + 2,2•(C1пi + C2п)•Rр, (13)

где TП - длительность времени переключения канала мультиплексора-демультиплексора 2 (или 18).

Наибольшим время (13) будет при У1 = 0, т.е. когда паразитные емкости C1пi и C2п разряжаются через сопротивление Rр ~ Rо = 10 кОм - см. (11) при R17 = 68 кОм.

При C1пi = C2п = 25 пФ, TА = 100 нс, TП = 300 нс и Rр = 10 кОм из (13) получаем, что через максимальное время

T2у = 1,5 мкс (14)

после установления С15 = 1 напряжение М12, определяемое выражениями (12), становится меньше напряжения М23, компаратор 27 и триггер-защелка переключаются из "1" в "0", и только после этого строб С15 переключается из "1" в "0", и коммутатор переходит в режим Р1 функционирования.

Таким образом, по каждому спаду строба С15 на выходе 16 коммутатора формируется сигнал Х16 выборки сигнала состояния датчика, адресуемого кодом "А0. . .А5" канала ввода, которая в течение С15 = 0 должна быть обработана в устройстве для ввода информации. В этой связи при использовании данного коммутатора цифровых сигналов в устройствах типа [1,2] вход строба опроса коммутатора необходимо соединить со счетным входом счетчика адреса, формирующего код "А0. ..А5" непосредственно [1] (или через блок памяти в [2]) и переключающегося по фронтам сигналов на его счетном входе.

Сравнивая (5) и (14), получаем

T1у/T2у = 440, (15)

что по сравнению с прототипом [2] предлагаемый коммутатор имеет в несколько сот раз более высокое быстродействие.

Кроме того, при количестве сигнальных входов 64 его блок 1 (содержит по восемь штук резисторов типа С2-33-0,125-10 кОм, резисторных блоков Б19К-1-1-10 кОм и диодных матриц 2ДС628А) имеет примерно в три раза меньшую массу и габариты по сравнению с блоком диодных ограничителей (содержит 64 одноваттных резисторов С2-33-1,0-1 кОм и восемь диодных матриц 2ДС628А) устройства [2].

Таким образом, по сравнению с прототипом [2] предлагаемый коммутатор благодаря его существенным признакам обладает более высоким быстродействием (см. оценку (15)) при меньшей массе и площади, занимаемой им на печатной плате.

Список литературы

1. А.с. 1086420, G 06 F 3/00, СССР. Устройство для ввода информации / В. А.Сечкин, В.И.Юлдашев. Опубл. 1984. Бюл. N 44.

2. А. с. 1540544, G 06 F 13/00, СССР. Устройство для сопряжения электронной вычислительной машины с дискретными датчиками / Ю.В. Крюков, А.В. Кузнецов. - Опубл. 1988 - прототип.

3. А.с. 653745, H 03 K 17/78, СССР. Коммутатор двухпозиционных сигналов / А.Г. Тищенко, Т.А. Караева, А.А. Яковенко. Опубл. 1979. Бюл. N 11.

4. А.с. 661798, H 03 K 17/60, СССР. Многоканальный коммутатор аналоговых сигналов / А.А.Редкокаша. Опубл. 1979. Бюл. N 17.

5. А. с. 729844, H 03 K 17/02, СССР. Коммутатор / Ю.Н. Цыбин. Опубл. 1980. Бюл. N 15.

6. Пухальский Г.И. Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах. Справочник. - М.: Радиосвязь, 1990. - 304 с.: "Мультиплексоры", с. 103-109.

7. Пухальский Г. И. , Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах, Справочник. - М.: Радио и связь, 1990. - 304 с.: "Мультиплексоры-демультиплексоры", с. 109-113.

8. Функциональные устройства судовых автоматизированных систем / Б.В. Бруслиновский, М. Н. Катханов и др. - Л.: Судостроение, 1991. - 336 с.: "Адресуемые узлы коммутации", с. 253-256.

9. Ерофеев Ю. Н. Импульсные устройства. - 3-е изд. перераб. и доп. М.: Высш. шк., 1989. - 527 с.: "Двухсторонний диодный ограничитель (рис. 3.76)", с. 154-156.

10. Микроэлектронные устройства автоматики / А.А. Сазонов, А.Ю. Лукичев, В. Т. Николаев и др.; Под ред. А.А. Сазонова. - М.: Энергоатомиздат, 1991. - 384 с.: "Электрические линии связи", с. 288-298; "Виды паразитной связи", с. 301-304.

11. Белоруссов Н.И. и др. Электрические кабели, провода и шнуры. Справочник / Н. И. Белоруссов, А.Е. Саакян, А.И. Яковлева. Под ред. Н.И. Белоруссова. - 5-е изд., перераб. и доп. - М.: Энергоатомиздат, 1988. - 536 с.: "Кабель гибкий экранированный ТРЭТБ", с. 271-272.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2190927C2 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2003 |

|

RU2257005C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| УСТРОЙСТВО ДЛЯ СЪЕМА, РЕГИСТРАЦИИ И АНАЛИЗА ЭЛЕКТРОФИЗИОЛОГИЧЕСКИХ СИГНАЛОВ И БЛОК ЗАЩИТЫ ОТ АВАРИЙНЫХ ТОКОВ ПАЦИЕНТА | 1995 |

|

RU2102004C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 2004 |

|

RU2261470C1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| МНОГОКАНАЛЬНЫЙ УЛЬТРАЗВУКОВОЙ УРОВНЕМЕР | 1992 |

|

RU2027978C1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

Изобретение относится к автоматикe и вычислительной технике и предназначено для использования в системах, выполняющих адресную коммутацию множества цифровых сигналов. Техническим результатом является повышение быстродействия. Коммутатор содержит дешифратор, входной блок параллельных двухсторонних диодных ограничителей, ограничитель входного блока, резистор, мультиплексор-демультиплексор, буферный передатчик, преобразователь уровней, четыре элемента И-НЕ. 2 ил.

Коммутатор цифровых сигналов, содержащий дешифратор, входной блок параллельных двухсторонних диодных ограничителей, число сигнальных входов коммутатора равно числу параллельных двухсторонних диодных ограничителей во входном блоке, каждый из упомянутых ограничителей входного блока содержит первый и второй диоды ограничения сверху и снизу соответственно, резистор, первый вывод которого соединен с соответствующим сигнальным входом коммутатора, второй вывод резистора каждого из упомянутых ограничителей соединен с анодом первого своего диода, катоды первых диодов упомянутых ограничителей входного блока объединены, отличающийся тем, что он дополнительно содержит мультиплексор-демультиплексор, буферный передатчик, преобразователь уровней, четыре элемента И - НЕ, причем второй вывод резистора каждого из упомянутых ограничителей входного блока соединен с соответствующим сигнальным входом мультиплексора-демультиплексора и с катодом второго своего диода, катоды первых диодов соединены с шиной цепи питания источника положительного напряжения, кодовый адресный вход коммутатора соединен с адресным входом мультиплексора-демультиплексора, сигнальный выход которого соединен с информационным входом преобразователя уровней, управляющий вход которого соединен с кодовым входом управления коммутатора, причем выход преобразователя уровней соединен с первым входом первого элемента И - НЕ, выход которого соединен с первыми входами второго и третьего элементов И - НЕ, упомянутые ограничители во входном блоке разделены на группы так, что в каждой группе аноды вторых диодов соединены между собой, инверсные выходы дешифратора через буферный передатчик связаны с анодами вторых диодов соответствующих групп, адресные входы дешифратора соединены с входами старших разрядов кодового адресного входа коммутатора, вход стробов опроса коммутатора соединен с стробирующим входом дешифратора и с вторыми входами первого и второго элементов И - НЕ, выход второго элемента И - НЕ соединен с первым входом четвертого элемента И - НЕ, выход которого соединен с вторым входом третьего элемента И - НЕ, выход которого соединен с вторым входом четвертого элемента И - НЕ и является информационным выходом коммутатора.

| Коммутатор двухпозиционных сигналов | 1977 |

|

SU653745A1 |

| Многоканальный коммутатор аналоговых сигналов | 1982 |

|

SU1034183A1 |

| US 5900767 A, 04.05.1999 | |||

| EP 0438228 A2, 24.07.1991. | |||

Авторы

Даты

2000-11-10—Публикация

1999-04-27—Подача