Изобретение относится к области вычислительной техники, предназначено для приема цифрового дифференциального сигнала последовательного самосинхронизирующегося двоичного кода (ПДСК) с последующим преобразованием в выходной сигнал ОХ приема бита кода и формированием выходных синхросигналов паузы ОРХ, начала паузы ОРС и битовой синхронизации ОСХ с помощью входной непрерывной последовательности тактовых импульсов IC, и может быть использовано при построении любых синхронных автоматов с памятью для ввода асинхронных данных в ряде ДПСК, в частности может использоваться в качестве полного синхронного декодера трехуровневого кода RZ с возвратом к нулю по ГОСТ 18977-79 и РТМ 1495-75, или в качестве синхронного формирователя сигнала ОХ приема бита кода и синхросигналов ОРХ, ОРС, ОСХ для любого двухуровневого ДПСК, например манчестерского по ГОСТ 26765.52-87 (зарубежные стандарты MIL-STD-1533B и MIL-STD-1773), биимпульсного или Миллера по ГОСТ 27232-87 и т.п.

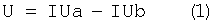

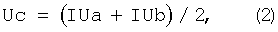

Устройство может использоваться, в частности, при построении одноканальных или многоканальных устройств для ввода информации с помощью цифрового дифференциального (разностного) сигнала

в системах проводной связи в сложной помеховой обстановке при значительных величинах синфазной помехи

искажающей обе компоненты

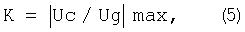

сигнала U (1), т.е. при высоких значениях показателя помехоустойчивости

где |X|max - оператор выделения максимального значения модуля величины X=Uc/Ug;

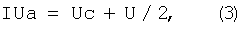

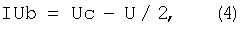

IUa и IUb - соответственно первая и вторая компоненты сигнала U (1), измеряемые относительно общей шины (корпуса) устройства;

Ug=|U|min - модуль минимального информационного значения сигнала U (1).

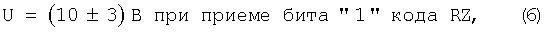

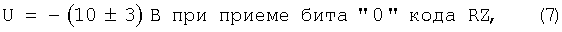

В коде RZ по ГОСТ 18977-79 и РТМ 1495-75 (см., например, [1, с.57-54]) каждый бит информации передается дифференциальным сигналом U (1) в течение битового периода Т=Т1+Т2 так, что в информационном полупериоде Т1=Т/2 периода Т битовой синхронизации на входах приемника значение сигнала (1) определяется соотношениями

а в течение полупериода Т2=Т2/2 возврата к нулю или в течение паузы

значение сигнала (1) на входах приемника определяется выражением

U∈[-1В, +1В],

где Т - период следования импульсов битовой синхронизации передачи информации в коде RZ сигналом (1).

На основании (6) и (7) для сигнала U (1) кода RZ по определению получаем

Известно [2, с.41], что практически никакие методы экранирования и разнесения проводов линий цифровой связи от энергетических проводов не могут гарантировать отсутствие в линии связи наводок. Это означает, что полезный сигнал U (1) всегда существует совместно с помехами, и задача заключается в гарантированном, т.е. с определенным запасом устойчивости, выделении сигнала на фоне помех. С учетом реальной естественной помеховой обстановки в [2] считают, что условием бесперебойной работы аппаратуры является сигнал наводки в линии связи, не превышающий |Uc|≈10÷20 В.

Однако в общем случае эта величина синфазной помехи для многих применений может быть явно заниженной [3, с.283], например известен измерительный усилитель с допустимым уровнем синфазной помехи до 50В [3, с.279, рис.7.7 г].

Таким образом, для сигнала U (1) кода RZ, описанного соотношениями (6)÷(9), величину |Uc|max и показатель К (5) можно оценить величинами

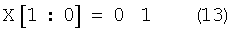

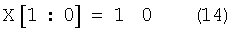

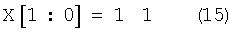

Для любого из указанных выше ДПСК после помехоустойчивого приема сигнал U (1) первоначально преобразуется однозначно в двухразрядный цифровой сигнал, который в прямом коде Х[1:0]=Х1 Х0 означает следующее:

возврат к нулю или пауза в коде RZ и пауза в любом другом ДПСК,

прием бита "0" в любом ДПСК,

прием бита "1" в любом ДПСК,

запрещенная комбинация в любом ДПСК, но возможная, кроме кода RZ, как переходная в течение некоторого времени из-за гистерезисной характеристики приемника сигнала (1) при переключении с приема (13) или (14) на прием (14) или (13) соответственно.

Далее сигнал Х[1:0] вводится в цифровую систему (сложный асинхронный или синхронный автомат с памятью), которая функционирует обычно по непрерывной последовательности тактовых импульсов IC единого системного тактового генератора, по отношению к частоте которого сигнал (1) (т.е. сигнал Х[1:0]) является асинхронным. Таким образом, при вводе в цифровую систему возникает необходимость синхронизации и преобразования асинхронного цифрового сигнала Х[1:0] с помощью тактовых импульсов IC единого системного тактового генератора.

Здесь следует отметить, что в асинхронной системе синхронизация (изменение состояния асинхронного автомата с памятью при установленных входных информационных сигналах) производится с помощью соответствующих синхроимпульсов (при формировании с помощью IC длительность синхроимпульса совпадает с длительностью t0 нулевой IC=0 или t1 единичной IC=1 фазы периода TIC=t0+t1 тактовых импульсов IC), а в синхронной системе синхронизация (изменение состояния синхронного автомата с памятью при установленных входных информационных сигналах) осуществляется логически по функции "И", т.е. по фронтам (переходам из "0" в "1") или срезам (переходам из "1" в "0") тактовых импульсов IC и соответствующим синхросигналам, установленным до прихода фронта или среза IC, причем длительность каждого синхросигнала обычно кратна числу периодов TIC.

В настоящее время и на длительную перспективу основным методом обработки информации в цифровых системах является синхронный метод тактирования по фронтам или срезам единого генератора тактовых импульсов с помощью синхросигналов (см., например, [4, с.121-123: 3.5. Введение в проблематику и методику проектирования автоматом с памятью]).

На основании изложенного выше можно сказать, что создание устройства для приема, преобразования и синхронизации цифрового дифференциального сигнала (1) для ввода информации в синхронную цифровую систему с требуемыми характеристиками (необходимыми функциональными возможностями, быстродействием и помехоустойчивостью, удовлетворяющей условию (11)) для сигнала любого двухуровневого или трехуровневого ДПСК, описанного соотношениями (12)÷(15) при приемлемых аппаратурных затратах, представляет актуальную техническую задачу, решение которой позволит в целом повысить качество разрабатываемых синхронных цифровых систем для ввода и обработки информации, являющихся составными частями современных информационно-измерительных комплексов.

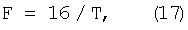

Известно устройство, являющееся частью технического решения [5] и содержащее демодулятор, входы цифрового дифференциального сигнала U (1) кода RZ, являющиеся входами демодулятора, генератор одиночных импульсов, специализированный счетчик, четыре выхода и тактовый вход сигнала IC, соединенный с тактовыми входами генератора и счетчика, выход сигнала Х1 последовательного кода, являющийся первым выходом устройства и информационным выходом демодулятора, выход асинхронного сигнала Z битовой синхронизации которого соединен с асинхронными входами генератора и счетчика, второй выход, соединенный с выходом генератора и являющийся выходом синхроимпульса СХ1 битовой синхронизации, третий выход, являющийся синхросигналом готовности GCP при обнаружении паузы, соединенный с первым выходом счетчика, и четвертый выход, соединенный с вторым выходом счетчика и являющийся синхроимпульсом PC паузы.

В процессе функционирования устройство по сигналу U (1) на первом выходе формирует сигнал Х1 последовательного 32-разрядного двоичного кода принимаемой информации, на втором выходе синхроимпульсы СХ1 битовой синхронизации, на третьем выходе синхросигнал готовности GCP длительности TIC для чтения введенного с систему 32-разрядного слова, на четвертом синхроимпульс PC паузы, формируемый по окончании GCP и предназначенный для установки системы в исходное состояние для приема следующего 32-разрядного слова сообщения.

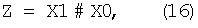

В течение паузы сигналы X1=0, СХ1=0, а в течение информационной части Т1 каждого битового периода Т (см. описание (12)÷(15) кода RZ) приема 32-разрядного слова сигналы Х1=0 и Z=1 при приеме (13) бита "0" или Х1=1 и Z=1 при приеме (14) бита "1", причем Z является асинхронным сигналом битовой синхронизации и формируется демодулятором согласно выражению

где # - на языке ABEL оператор операции ИЛИ.

При поступлении на входы устройства сигнала U (1) кода RZ в течение каждого битового периода Т=Т1+Т2 при приеме 32-разрядного слова работу устройства можно описать следующим образом.

В течение полупериода Т1 сигнал Z=1 асинхронно сбрасывает счетчик, а по фронту (переходу из "0" в "1") сигнала Z=1 генератор каждый раз с помощью входных тактовых импульсов IC, следующих, например, с частотой

формирует единичный синхроимпульс СХ1=1 битовой синхронизации.

После приема каждого слова в течение каждой паузы демодулятор вырабатывает сигналы Х1=0 и Z=0, а после начала паузы счетчик через время обнаружения паузы ТОП≈4·Т формирует сначала один синхросигнал готовности GCP для чтения введенного в систему 32-разрядного слова, а затем формирует синхроимпульс PC паузы, устанавливающий систему в исходное состояние для приема следующего слова сообщения.

Основным недостатком устройства [5] является ограниченность функциональных возможностей, поскольку оно ориентировано на работу с сигналом U (1) только кода RZ.

Известно устройство, являющееся частью технического решения [6] и содержащее приемник-декодер, обнаружитель паузы, два элемента НЕ, триггер, входы цифрового дифференциального сигнала U (1) кода RZ, соединенные с входами приемника-декодера, вход кода порога обнаружения паузы Р[5:0] и тактовый вход, соединенные соответственно с кодовым и тактовым входами обнаружителя, выходы инверсного потенциального сигнала ONPX паузы и инверсного синхроимпульса ONPC начала паузы, являющиеся первым и вторым выходами обнаружителя соответственно, выход сигнала ОХ последовательного кода, соединенный с выходом триггера, инверсный асинхронный вход установки которого через первый элемент НЕ связан с выходом сигнала Х1 приемника-декодера, и выход инверсного сигнала ONZ битовой синхронизации, соединенный с входом асинхронной установки обнаружителя в режим обнаружения и выходом второго элемента НЕ, вход которого соединен с выходом асинхронного сигнала Z битовой синхронизации приемника-декодера и тактовым входом триггера, информационный вход которого соединен с шиной Логического "0" устройства.

В течение паузы приемник-декодер вырабатывает сигналы Х1=0 и Z=0, на выходах устройства установлены сигналы ОХ=0 (или ОХ=1), ONZ=!Z=1 (где !=N - на языке ABEL оператор операции НЕ), ONPX=0, ONPC=1.

При поступлении информации в начале каждого полупериода Т1 при Х1=1 триггер по сигналу NX1=0 с выхода первого элемента НЕ асинхронно фиксируется в ОХ=1, а при Х1=0 триггер по фронту сигнала Z=1 сбрасывается в ОХ=0. В течение Т1 сигнал ONZ=0 асинхронно устанавливает обнаружитель в режим обнаружения (в счетчик обнаружителя записывается код порога обнаружения Р[5:0]), а по фронту сигнала ONZ (по срезу сигнала Z, т.е. переходу Z из "1" в "0") с устройства считывается значение последовательного бита ОХ информации, установленного в триггере согласно приему бита "1" (14) или приему бита "0" (13).

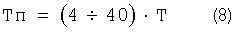

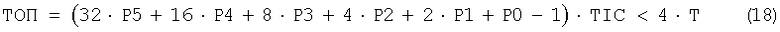

С наступлением паузы обнаружитель при условии (17) в зависимости от кода порога Р[5:0]=Р5Р4Р3Р2Р1Р0 через время обнаружения паузы (ТОП)

генерирует по IC=1 синхроимпульс начала паузы ONPC=0, и после его окончания выставляет потенциальный сигнал паузы ONPX=0, где TIC - период входных тактовых импульсов IC устройства.

Основным недостатком устройства [6] также является ограниченность функциональных возможностей, поскольку оно ориентировано на работу с сигналом U (1) только кода RZ.

Следует отметить, что демодулятор устройства [5] эквивалентен приемнику-декодеру устройства [6], в качестве которого в настоящее время целесообразно использовать микросхему 1567АП1 [2, с.80-83] - двухканальный приемник последовательного кода RZ по ГОСТ 18977-79 (ARING), предназначенный для приема двух дифференциальных цифровых сигналов при |Uc|≤15B с разрешаемой коммутацией любого из них на два цифровых выхода с открытым коллектором: выход Х1 - информации и выход Z (16) - синхронизации. В этой связи существенным недостатком устройства [5] или [6] является также низкая помехоустойчивость, поскольку его показатель К=(15/7) явно не удовлетворяет условию (11).

Из известных технических решений наиболее близким по технической сущности к предлагаемому является устройство [7], содержащее приемник-преобразователь, входы первой и второй компонент цифрового дифференциального сигнала (1), являющиеся первым и вторым входами приемника-преобразователя соответственно, элемент И, счетчик, три элемента ИЛИ, элемент И-НЕ, тактовый вход тактовых импульсов IC, являющийся первым входом элемента И-НЕ, кодовый вход кода порога Р[5:0] обнаружения паузы, являющийся информационным кодовым входом счетчика, и пять выходов, первый из которых является выходом инверсного сигнала ONX1 приема "1" кода и соединен с первым входом элемента И и первым выходом приемника-преобразователя, второй выход которого является выходом инверсного сигнала ONX0 приема "0" кода и соединен с вторым выходом устройства и вторым входом элемента И, выход которого является выходом инверсного сигнала ONZ (сигнал Z определен согласно (16)) и третьим выходом устройства, который соединен с инверсным асинхронным входом записи счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, четвертый выход устройства является выходом инверсного синхроимпульса ONPC начала паузы и соединен с выходом второго элемента ИЛИ, второй вход которого соединен с вычитающим счетным входом счетчика и выходом элемента И-НЕ, второй вход которого соединен с пятым выходом устройства инверсного потенциального сигнала ONPX паузы и выходом третьего элемента ИЛИ, второй вход которого соединен с выходом младшего разряда счетчика, причем приемник-преобразователь содержит два входа, два компаратора, первый и второй выходы, являющиеся выходами первого и второго компараторов соответственно, два ограничителя напряжений и четыре делителя напряжений, выходы первого и второго из которых соединены с первым и вторым входами первого ограничителя и с инвертирующим и неинвертирующим входами первого компаратора соответственно, инвертирующий и неинвертирующий входы второго компаратора соответственно соединены с выходами третьего и четвертого делителей и первым и вторым входами второго ограничителя, первый вход приемника-преобразователя соединен с первыми входами первого и четвертого делителей, первые входы второго и третьего делителей соединены со вторым входом приемника-преобразователя, вход отрицательного напряжения смещения которого соединен со вторыми входами первого и третьего делителей, общая шина (корпус) приемника-преобразователя соединена со вторыми входами второго и четвертого делителей, каждый из делителей содержит два резистора, первый вход, соединенный с первым выводом первого резистора, выход, соединенный с первым входом первого резистора и вторым входом второго резистора, и второй вход, соединенный со вторым выводом второго резистора, а каждый из ограничителей содержит два диода, первый вход, соединенный с анодом первого диода и катодом второго диода, и второй вход, соединенный с катодом первого диода и анодом второго диода.

Первый компаратор с первым и вторым делителями (или второй компаратор с третьим и четвертым делителями) образуют триггер Шмитта, а каждый из компараторов может быть выполнен, например, на основе интегрального компаратора с открытым коллекторным выходом (в частности, на интегральной микросхеме К554СА3) и двух резисторах так, что первые выводы обоих резисторов соединены с выходом интегрального компаратора, являющегося выходом первого (или второго компаратора), неинвертирующий и инвертирующий входы которого являются соответственно неинвертирующим и инвертирующим входами интегрального компаратора, неинвертирующий вход которого соединен со вторым выводом первого резистора, а второй вывод второго резистора соединен с шиной источника питания +5В.

Показатель помехоустойчивости К (5) устройства [7] определяется при Ug=7B параметрами приемника-преобразователя и при сопротивлении R1=10 кОм первого и сопротивлении R2=2 кОм второго резистора каждого делителя напряжений приемника-преобразователя показатель K≈11, т.е. устройство [7] по помехоустойчивости с запасом удовлетворяет условию (11).

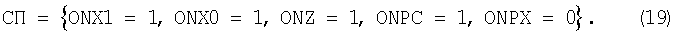

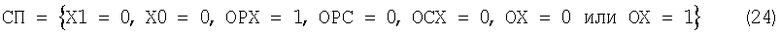

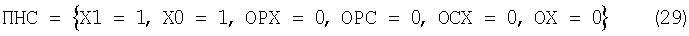

В течение паузы устройство [7] находится в состоянии паузы (СП)

При поступлении информации, например, в коде RZ в течение каждого полупериода Т1 устройство формирует асинхронные сигналы ONZ=0, ONX0=0 при приеме бита "0" (13) (или ONX1=0 при приеме бита "1" (14)). По каждому ONZ=0 в счетчик записывается код порога Р[5:0] обнаружения паузы, а в начале поступления информации по первому ONZ=0 сигнал ONPX асинхронно переключается из "0" в "1".

С наступлением паузы содержимое С[5:0] счетчика по срезу каждого тактового импульса IC начинает уменьшаться от начального значения С[5:0]=Р[5:0]=Р5Р4Р3Р2Р1Р0, и через время ТОП (18) на выходе второго элемента ИЛИ генерируется по IC=1 синхроимпульс ONPC=0 начала паузы, по окончании которого счетчик переходит в "000000", на выходе третьего элемента ИЛИ формируется сигнал ONPX=0 паузы, и устройство [7] переходит в СП (19).

Основным недостатком устройства [7] является ограниченность его функциональных возможностей, обусловленная как отсутствием преобразования асинхронного инверсного двухразрядного сигнала NX[1:0] в одноразрядный сигнал ОХ приема бита кода с учетом возможности появления запрещенной комбинации (15) в течение нескольких периодов TIC, так и не полнотой синхронизации приема, поскольку синхросигнал ОСХ битовой синхронизации не формируется, сигнал ONPX не является синхросигналом (переключение ONPX из "0" в "1" осуществляется асинхронным сигналом ONZ=0), сигнал начала паузы формируется в виде синхроимпульса ONPC=0 длительности IC=1, т.е. длительности t1 единичной фазы входных тактовых импульсов IC.

Предлагаемым изобретением решается задача комплексного расширения функциональных возможностей устройства за счет преобразования входного цифрового дифференциального сигнала U (1) в выходной одноразрядный сигнал ОХ приема бита кода с учетом возможности появления запрещенной комбинации (15) из-за гистерезисной характеристики приемника-преобразователя при переключении с приема (13) или (14) соответственно на прием (14) или (13) и формирования выходных синхросигналов паузы ОРХ с длительностью, кратной целому числу длительности TIC, начала паузы ОРС длительности TIC и битовой синхронизации ОСХ длительности TIC с помощью входных тактовых импульсов IC с периодом TIC.

Для достижения этого технического результата в устройство для приема, преобразования и синхронизации цифрового дифференциального сигнала, содержащее приемник-преобразователь, входы первой и второй компонент цифрового дифференциального сигнала, являющиеся первым и вторым входами приемника-преобразователя соответственно, двоичный счетчик, первый элемент И, элемент И-НЕ, кодовый вход порога обнаружения паузы, являющийся информационным кодовым входом счетчика, тактовый вход и четыре выхода, введены второй и третий элементы И, два элемента НЕ и четыре триггера, тактовые входы первого и второго триггеров соединены соответственно с первым и вторым прямыми выходами приемника-преобразователя, тактовый вход устройства соединен с тактовыми входами третьего триггера и счетчика снабженного инверсными входами разрешения счета и записи и являющегося синхронным, первый выход устройства является выходом синхросигнала паузы и соединен с входом разрешения счета счетчика и выходом первого элемента И, первый вход которого соединен с выходом второго элемента И и первым входом третьего элемента И, выход которого соединен с вторым выходом устройства, являющегося выходом синхросигнала начала паузы, третий выход устройства является выходом синхросигнала битовой синхронизации и соединен с выходом третьего триггера и через первый элемент НЕ связан с входами установки первого и второго триггеров, входом разрешения записи счетчика и одним из входов второго элемента И, остальные входы которого соединены с выходами старших разрядов счетчика, выход младшего разряда которого соединен с вторым входом первого элемента И и через второй элемент НЕ связан с вторым входом третьего элемента И, шина Логического "0" устройства соединена с информационными входами первого и второго триггеров, выход первого триггера соединен с входом установки четвертого триггера и первым входом элемента И-НЕ, выход которого соединен с информационным входом третьего триггера, входы установки и сброса которого соединены с шиной Логической "1" устройства и входами сброса первого и второго триггеров, выход второго триггера соединен со вторым входом элемента И-НЕ и входом сброса четвертого триггера, выход которого соединен с четвертым выходом устройства, являющегося выходом сигнала приема бита кода, причем входы установки и сброса всех триггеров являются инверсными и асинхронными.

Автору неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение второго и третьего элементов И, двух элементов НЕ и четырех триггеров) предлагаемого устройства, которые (по сравнению с прототипом [7]) комплексно расширяют его функциональные возможности за счет преобразования входного сигнала в выходной одноразрядный сигнал ОХ приема бита кода и формирования выходных синхросигналов паузы ОРХ с длительностью, кратной целому числу длительности TIC, начала паузы ОРС длительности TIC и битовой синхронизации ОСХ длительности TIC с помощью входных тактовых импульсов IC с периодом TIC.

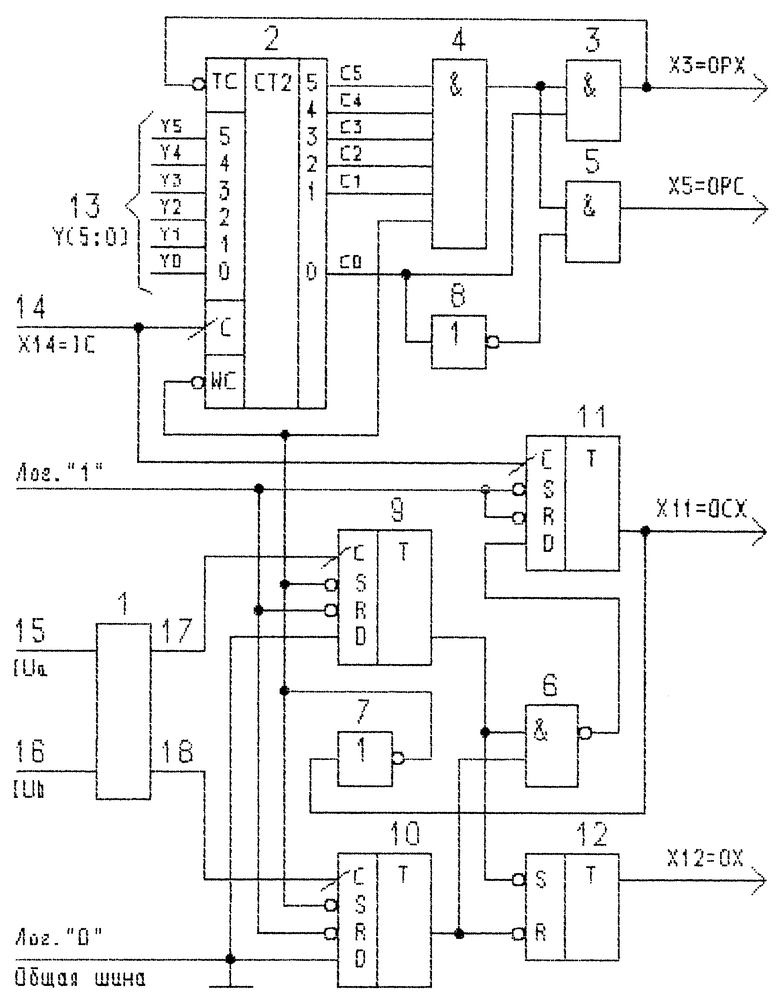

На чертеже приведена функциональная электрическая схема устройства для приема, преобразования и синхронизации цифрового дифференциального сигнала, содержащего приемник-преобразователь 1, двоичный синхронный шестиразрядный счетчик 2, первый 3, второй 4 и третий 5 элементы И, элемент 6 И-НЕ, первый 7 и второй 8 элементы НЕ, четыре триггера с первого 9 по четвертый 12, шестиразрядный кодовый вход 13 порога обнаружения паузы, являющийся информационным кодовым входом счетчика 2, тактовый вход 14, входы 15 и 16 первой и второй компонент цифрового дифференциального сигнала, являющиеся соответственно первым и вторым входами приемника-преобразователя 1, четыре выхода, первый 17 и второй 18 прямые выходы приемника-преобразователя 1, соединенные с тактовыми входами первого 9 и второго 10 триггеров соответственно, первый выход устройства является выходом синхросигнала паузы и соединен с инверсным входом разрешения счета счетчика 2 и выходом первого элемента 3 И, первый вход которого соединен с выходом второго элемента 4 И и первым входом третьего элемента 5 И, выход которого соединен со вторым выходом устройства, являющегося выходом синхросигнала начала паузы, третий выход устройства является выходом синхросигнала битовой синхронизации и соединен с выходом третьего триггера 11 и через первый элемент 7 НЕ связан с входами установки первого 9 и второго 10 триггеров, инверсным входом разрешения записи счетчика 2 и одним из входов второго элемента 4 И, остальные входы которого соединены с выходами старших разрядов счетчика 2, выход младшего разряда которого соединен с вторым входом первого элемента 3 И и через второй элемент 8 НЕ связан со вторым входом третьего элемента 5 И, шина Логического "0" устройства соединена с информационными входами первого 9 и второго 10 триггеров, выход первого триггера 9 соединен с входом установки четвертого триггера 12 и первым входом элемента 6 И-НЕ, выход которого соединен с информационным входом третьего триггера 11, тактовый вход которого соединен с тактовым входом счетчика 2 и тактовым входом 14 устройства, шина Логической "1" которого соединена с входами сброса первого 9 и второго 10 триггеров и входами установки и сброса третьего триггера 11, выход второго триггера 10 соединен со вторым входом элемента 6 И-НЕ и входом сброса четвертого триггера 12, выход которого соединен с четвертым выходом устройства, являющегося выходом сигнала приема бита кода, причем входы установки и сброса триггеров 9÷12 являются инверсными и асинхронными.

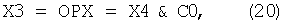

При одноканальном вводе в качестве приемника-преобразователя 1 предлагаемого устройства может быть использован приемник-преобразователь прототипа [7], дополненный двумя элементами НЕ, входы которых соединены с выходами компараторов приемника-преобразователя прототипа, а выходы этих элементов НЕ являются выходами 17 и 18 приемника-преобразователя 1, на которых формируются разрядные цифры кода Х[1:0]=Х1 Х0=Х17 Х18.

При многоканальном вводе в режиме разделения во времени в качестве приемника-преобразователя 1 предлагаемого устройства может быть непосредственно использован коммутатор цифровых дифференциальных сигналов [8], который для каждого сигнала (1), выбранного комбинационно по коду адреса канала, на выходах 17 и 18 вырабатывает сигналы кода Х[1:0]=Х1 Х0=Х17 Х18. При сигнале (1), соответствующем коду RZ, коммутатор [8] имеет показатель К=5, удовлетворяющий условию (11).

Как синхронный автомат с памятью шестиразрядный синхронный счетчик 2 может быть реализован, например, на двух четырехразрядных счетчиках ИЕ10 - микросхемах любой из серий 533, 555, 1533, 1554 и согласующем элементе НЕ, для подключения через него инверсного входа разрешения счета счетчика 2 к прямым входам разрешения счета и переноса первого счетчика ИЕ10, выход переноса которого соединен с входами разрешения счета и переноса второго счетчика ИЕ10, вход Логической "1" счетчика 2 (не показан) соединен с инверсными асинхронными входами сброса обоих счетчиков ИЕ10 и информационными входами двух старших разрядов второго счетчика ИЕ10, тактовый вход 14 счетчика 2 соединен с тактовыми входами обоих счетчиков ИЕ10, инверсные входы разрешения записи которых соединены с инверсным входом разрешения записи счетчика 2, два старших и четыре младших разрядных входов кодового входа 13 кода Y[5:0] счетчика 2 связаны с двумя старшими и четырьмя младшими разрядными выходами его кодового выхода кода С[5:0] через второй и первый счетчики ИЕ10 соответственно.

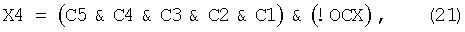

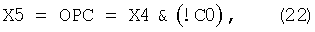

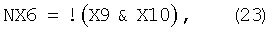

Обозначим через Y[5:0]=Y5Y4Y3Y2Y1Y0 и С[5:0]=С5С4С3С2С1С0 соответственно коды на кодовом входе 13 и кодовом выходе счетчика 2, Х3÷Х5 - сигналы на выходах элементов 3÷5 при Х3=ОРХ и Х5=ОРС, NX6÷NX8 - сигналы на выходах элементов 6÷8 при NX7=!OCX и NX8=!CO, X9÷X12 - сигналы на выходах триггеров 9÷12 при Х11=ОСХ и Х12=ОХ, Х14=IC - тактовые импульсы на тактовом входе 14, Х17=Х1 и Х18=Х0 - сигналы на выходах 17 и 18, определенные сигналами кода Х[1:0]=Х1 Х0=Х17 Х18 согласно (12)÷(15), причем сигналы Х3, Х4, Х5 и NX6 формируются по логическим формулам

где "&", "!=N" - на языке ABEL операторы операций "И" и "НЕ" соответственно.

Синхронный счетчик 2 с помощью синхросигнала ОРХ=Х3 паузы, инверсного синхросигнала NX7=!OCX битовой синхронизации и тактовым импульсам Х14=IC функционирует так, что при NX7=0 по фронту тактового импульса Х14 в счетчик 2 записывается с кодового входа 13 код порога Y(5:0) обнаружения паузы, и он переходит в исходное состояние C[5:0]=Y[5:0] обнаружения паузы. При NX7=1 и Х3=ОРХ=0 по фронту каждого тактового импульса Х14 содержимое счетчика 2 увеличивается на "1", а при NX7=1 и ОРХ=1 счетчик 2 находится в состоянии С[5:0]=111111 обнаружения паузы, сохраняется в этом состоянии до очередного перевода его в исходное состояние по фронту Х14 при NX7=0.

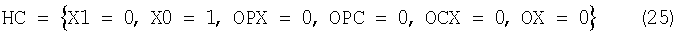

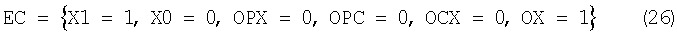

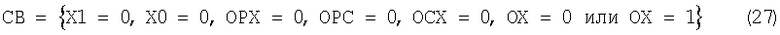

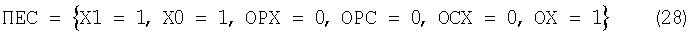

Функционирование предлагаемого устройства как автомата с памятью для трехуровневого кода RZ с возвратом к нулю или любого двухуровневого ДПСК (полностью определенных с помощью выражений (12)÷(15) с учетом запрещенной комбинации (15) для двухуровневого ДПСК) можно описать как последовательность переходов из состояния паузы (СП)

в нулевое состояние (НС)

или в единичное состояние (ЕС)

из НС (25) или ЕС (26) при обработке кода RZ в состояние возврата (СВ) к нулю

а при обработке любого двухуровневого ДПСК из НС (25) в переходное единичное состояние (ПЕС)

с последующим асинхронным переходом в ЕС (25), или из ЕС (25) в переходное нулевое состояние (ПНС)

с последующим асинхронным переходом в НС (25).

Кроме того, после окончания передачи слова (или сообщения) в любом коде устройство из НС (25) или ЕС (26) переходит сначала в СВ (27), а затем в СП (24).

С учетом изложенного выше опишем функционирование устройства по сигналу U (1) (однозначно определяет асинхронный кодовый сигнал Х[1:0]=Х17 Х18, описанный соотношениями (12)÷(15)) при приеме (вводе) сообщения сначала для трехуровневого кода RZ с возвратом к нулю, а затем для любого двухуровневого ДПСК (манчестерского, Миллера и т.п.).

В коде RZ в каждом битовом интервале Т=Т1+Т2 приема ПДСК в информационной части полупериода Т1 код Х[1:0]=0 1 при приеме "0" (13) (или код Х[1:0]=1 0 при приеме "1" (14)), а в течение полупериода Т2 при возврате к нулю или в течение паузы Тп (8) код Х[1:0]=0 0.

В начале ввода каждого сообщения в коде RZ устройство из СП (24) при приеме бита "0" (или "1") сигнал Х18=Х0 (или Х17=Х1) переключается на время Т1 в "1" и фронтом сбрасывает триггер 10 (или 9) в Х10=0 (или Х9=0). По сигналу Х10=0 (или Х9=0) триггер 12 сбрасывается в ОХ=0 (или устанавливается в ОХ=1) в состояние, совпадающее с принимаемым в коде RZ битом "0" (или "1"), элемент 6 И-НЕ формирует сигнал NX6=1, по которому триггер 11 по ближайшему фронту тактовых импульсов Х14=IC устанавливается и формирует выходной синхросигнал Х11=ОСХ=1 битовой синхронизации. Элемент 7 НЕ вырабатывает инверсное значение NX7=!OCX=0 синхросигнала ОСХ, по которому синхросигнал паузы сбрасывается в ОРХ=0, каждый из триггеров 9 и 12 асинхронно фиксируется в "1", в счетчик 2 разрешается запись кода Y[5:0], элемент 6 И-НЕ вырабатывает сигнал NX6=0, и по следующему фронту Х14=IC триггер 11 сбрасывается в Х11=0, счетчик 2 переходит в исходное состояние C[5:0]=Y[5:0] обнаружения паузы, и устройство переходит в НС (25) (или ЕС (26)). Далее по истечении времени Т1 сигнал Х0=Х18 (или Х1=Х17) переключается из "1" в "0", и устройство переходит в СВ (27). Далее при приеме каждого бита "0" (13) (или бита "1" (14)) кода RZ все описанные выше процессы перехода в НС (25) (или ЕС (26)) повторяются при ОРХ=0 с асинхронным переходом в полупериоде Т2 в СВ (27).

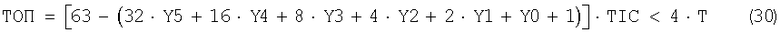

В начале каждой паузы устройство всегда находится в СВ (27), причем с наступлением паузы после окончания последнего выходного синхросигнала ОСХ=1 битовой синхронизации счетчик 2 оказывается в исходном состоянии C[5:0]=Y[5:0] обнаружения паузы, переходит в последний раз из НС (25) (или ЕС (26)) в СВ (27). Далее каждый раз при ОРХ=0 и NX7=!OCX=1 по фронту каждого тактового импульса Х14=IC содержимое счетчика 2 увеличивается на "1" так, что при условии (17) через время обнаружения паузы

элемент 5 И согласно (22) формирует синхросигнал ОРС=1 начала паузы, после окончания которого элемент 3 согласно (20) формирует синхросигнал ОРХ=1 паузы, и устройство оказывается в состоянии СП (24) до поступления на устройство первого сигнала Х18=Х0=1 (или Х17=Х1=1) приема бита "0" (13) (или бита "1" (14)) очередного сообщения в коде RZ.

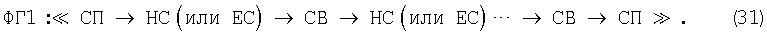

При вводе сообщения в коде RZ функционирование устройства в целом можно описать от СП (24) до СП (24) функциональным графом 1 (ФГ1)

Легко видеть, что при приеме асинхронного цифрового сигнала U (1) сообщения в коде RZ предлагаемое устройство является декодером кода RZ, так как сигнал Х12=ОХ приема бита представляет собой последовательный двоичный код сообщения, каждый бит которого сопровождается синхросигналом Х11=ОСХ битовой синхронизации, а конец передачи и пауза между сообщениями отмечаются синхросигналами начала паузы ОРС (22) и паузы ОРХ (20) соответственно.

В процессе приема сигнала Х[1:0]=Х17 Х18 любого двухуровневого ПДСК устройство может находиться в любом из шести состояний (24)÷(29), причем СВ (27) однозначно указывает на последующий переход в СП (24).

В начале приема каждого сообщения в любом двухуровневом ПДСК устройство находится в СП (24), и при вводе первого бита "0" (13) (или бита "1" (14)) сигнал Х18=Х0 (или Х17=Х1) переключается из "0" в "1" и фронтом сбрасывает триггер 10 (или 9) в Х10=0 (или Х9=0). По сигналу Х10=0 (или Х9=0) триггер 12 сбрасывается в ОХ=0 (или устанавливается в ОХ=1) - состояние, совпадающее с принимаемым битом "0" (или "1") в ПДСК, элемент 6 И-НЕ формирует сигнал NX6=1, по которому триггер 11 по ближайшему фронту тактовых импульсов Х14=IC устанавливается и формирует выходной синхросигнал Х11=ОСХ=1 битовой синхронизации. Элемент 7 НЕ вырабатывает сигнал NX7=!OCX=0, по которому синхросигнал паузы сбрасывается в ОРХ=0, каждый из триггеров 9 и 12 асинхронно фиксируется в "1", в счетчик 2 разрешается запись кода Y[5:0], элемент 6 И-НЕ вырабатывает сигнал NX6=0. По следующему фронту Х14=IC триггер 11 сбрасывается в Х11=0, счетчик 2 переходит в исходное состояние C[5:0]=Y[5:0] обнаружения паузы, и устройство переходит в НС (25) (или ЕС (26)). Далее при наличии информации устройство будет непрерывно переходить из НС (25) по фронту сигнала Х17=1 в ПЕС (28) с последующим асинхронным переходом в ЕС (26) по срезу сигнала Х18=0, и наоборот по фронту сигнала Х18=1 в ПНС (29) с последующим асинхронным переходом в НС (25) по срезу сигнала Х17=0. В процессе каждого такого перехода триггер 12 сбрасывается в ОХ=0 (или устанавливается в ОХ=1) - состояние, совпадающее с принимаемым битом "0" (или "1") в ПДСК независимо от появления запрещенной комбинации (15) в ПЕС (28) или ПНС (29). При NX6=1 по ближайшему фронту Х14=IC формируется выходной синхросигнал Х11=ОСХ=1 битовой синхронизации выходного сигнала ОХ приема бита кода, и при NX7=!OCX=0 по следующему фронту Х14=IC в счетчик 2 записывается код C[5:0]=Y[5:0] порога обнаружения паузы согласно (30).

С наступлением паузы после окончания последнего выходного синхросигнала ОСХ=1 битовой синхронизации счетчик 2 оказывается в исходном состоянии C[5:0]=Y[5:0] обнаружения паузы. Затем переходит из НС (25) (или ЕС (26)) в СВ (27), и при ОРХ=0 и NX7=!OCX=1 по фронту каждого тактового импульса Х13=IC содержимое счетчика 2 увеличивается на "1". Через время (30) элемент 5 И формирует выходной синхросигнал начала паузы ОРС (22), после окончания которого элемент 3 И формирует синхросигнал паузы ОРХ (20), и устройство оказывается в состоянии СП (24) до поступления на устройство первого бита "0" (или "1") очередного сообщения в двухуровневом ПДСК.

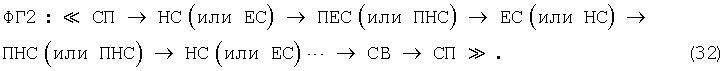

Аналогично (31), при вводе сообщения в любом двухуровневом ПДСК функционирование устройства в целом можно описать от СП (24) до СП (24) функциональным графом 2 (ФГ2)

Таким образом, при вводе сообщения по сигналу U (1) в любом двухуровневом ПДСК предлагаемое устройство является формирователем сигнала ОХ приема бита кода и синхросигналов ОРХ, ОРС, ОСХ.

Непосредственно из описания прототипа [7] и данного устройства следует, что предлагаемое устройство благодаря его существенным признакам по сравнению с прототипом обладает значительно расширенными функциональными возможностями за счет обеспечения формирования на выходах сигнала ОХ приема бита кода, неизмененного в течение каждого ОСХ=1, и синхросигналов ОРХ паузы, ОРС начала паузы и ОСХ битовой синхронизации.

Благодаря существенным признакам предлагаемое устройство может быть использовано при построении любых синхронных автоматов с памятью для ввода асинхронных данных в ряде ДПСК, в частности может использоваться в качестве полного синхронного декодера трехуровневого кода RZ с возвратом к нулю, или в качестве синхронного формирователя сигнала приема бита и синхросигналов паузы, начала паузы и битовой синхронизации для любого двухуровневого ДПСК, например манчестерского, Миллера и т.п.

Литература

1. Хвощ С.Т и др. Организация последовательных мультиплексных каналов систем автоматического управления. Машиностроение. Ленингр. отд-ние, 1989, 271 с., ил.

2. Основы организации систем цифровых связей в сложных иформационно-измерительных комплексах. В.А.Ацюковский, В.Г.Бобров, А.Л.Невдяева и др. М.: Энергоатомиздат, 2001. - 96 с. ил. (Б-ка энергетика).

3. Гальперин М.В. Электронная техника: Учебник. - М.: ФОРУМ: ИНФРА-М, 2003, 304 с.: ил. (Серия "Профессиональное образование").

4. Угрюмов Е.П. Цифровая схемотехника. СПб.: БХВ-Петербург, 2001, 528 с., ил.

5. А.с. СССР 1068927, G 06 F 3/04. Устройство для ввода информации. Л.П.Горохов, Р.Ю.Хальфан и В.А.Генина. Опубл. 1984. Бюл. №3.

6. Патент РФ на изобретение 2207614, G 06 F 3/00. Устройство для ввода информации. Киселев Е.Ф., Крюков Ю.В, Тимофеев С.С., Ремешков Ю.И. Опубл. 2003. БИ №18.

7. Патент РФ на изобретение 2203520, Н 03 М 5/16. Устройство для приема и преобразования цифрового дифференциального сигнала. Киселев Е.Ф., Зуев А.И. - Опубл. 2003. БИ №12. (Прототип).

8. Патент РФ на изобретение 2190927, Н 03 К 17/16, G 06 F 13/00, 3/00. Коммутатор цифровых дифференциальных сигналов. Киселев Е.Ф., Зуев А.И. Опубл. 2002. БИ №28.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ АСИНХРОННОГО ЦИФРОВОГО СИГНАЛА | 2004 |

|

RU2279181C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ ДВУХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2005 |

|

RU2290755C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОДОВОГО СИГНАЛА | 2007 |

|

RU2345479C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2285333C1 |

Изобретение относится к вычислительной технике и может быть использовано для приема и преобразования цифрового дифференциального сигнала. Технический результат заключается в комплексном расширении функциональных возможностей устройства за счет преобразования входного цифрового дифференциального сигнала в выходной сигнал приема бита кода и формирования выходных синхросигналов паузы с длительностью, кратной целому числу длительности TIC, начала паузы длительности TIC, и битовой синхронизации длительности TIC с помощью входной непрерывной последовательности тактовых импульсов IC с периодом TIC. Для этого приемник содержит приемник-преобразователь, двоичный счетчик, три элемента И, два элемента НЕ, элемент И-НЕ, четыре триггера, кодовый вход обнаружения паузы, тактовый вход, входы первой и второй компонент цифрового дифференциального сигнала и четыре выхода. 1 ил.

Устройство для приема, преобразования и синхронизации цифрового дифференциального сигнала, содержащее приемник-преобразователь, входы первой и второй компонент цифрового дифференциального сигнала, являющиеся первым и вторым входами приемника-преобразователя соответственно, двоичный счетчик, первый элемент И, элемент И-НЕ, кодовый вход порога обнаружения паузы, являющийся информационным пороговым входом счетчика, тактовый вход и четыре выхода, отличающееся тем, что оно дополнительно содержит второй и третий элементы И, два элемента НЕ и четыре триггера, тактовые входы первого и второго триггеров соединены соответственно с первым и вторым прямыми выходами приемника-преобразователя, тактовый вход устройства соединен с тактовыми входами третьего триггера и счетчика, снабженного инверсными входами разрешения счета и записи и являющегося синхронным, первый выход устройства является выходом синхросигнала паузы и соединен с входом разрешения счета счетчика и выходом первого элемента И, первый вход которого соединен с выходом второго элемента И и первым входом третьего элемента И, выход которого соединен с вторым выходом устройства, являющегося выходом синхросигнала начала паузы, третий вход устройства является выходом синхросигнала битовой синхронизации и соединен с выходом третьего триггера и через первый элемент НЕ связан с входами установки первого и второго триггеров, входом разрешения записи счетчика и одним из входов второго элемента И, остальные выходы которого соединены с выходами старших разрядов счетчика, выход младшего разряда которого соединен с вторым входом первого элемента И и через второй элемент НЕ связан с вторым входом третьего элемента И, шина Логического «0» устройства соединена с информационными входами первого и второго триггеров, выход первого триггера соединен с входом установки четвертого триггера и первым входом элемента И-НЕ, выход которого соединен с информационным входом третьего триггера, входы установки и сброса которого соединены с шиной Логической «1» устройства и входами сброса первого и второго триггеров, выход второго триггера соединен со вторым входом элемента И-НЕ и входом сброса четвертого триггера, выход которого соединен с четвертым выходом устройства, являющегося выходом сигнала приема бита кода, причем входы установки и сброса всех триггеров являются инверсными и асинхронными.

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| Устройство приема тональных сигналов | 1991 |

|

SU1793560A1 |

| Устройство приема тональных сигналов | 1989 |

|

SU1700769A1 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| US 6195783 А, 27.02.2001 | |||

| Система подачи жидкого топлива на сжигание | 1988 |

|

SU1562602A1 |

| Монорельсовый тягач | 1984 |

|

SU1255490A1 |

Авторы

Даты

2006-06-27—Публикация

2004-12-28—Подача