Устройство относится к технике связи и может быть использовано для приема данных с забойной телеметрической системы, использующей циклически повторяющиеся пакеты цифровых данных.

Известно устройство синхронизации по циклам, являющееся наиболее близким по технической сущности и достигаемому результату (авторское свидетельство 1755387, опубликованное в бюл. 30 за 1992 г. по MKИ H 04 L 7/08), которое содержит генератор тактовых импульсов, два распределителя импульсов, два блока элементов И, блок декодирования синхросигнала, накопитель информации, элемент ИЛИ, регистр сдвига, соединенные между собой определенным образом.

Недостатком известного устройства является то, что данное устройство не обеспечивает надежный прием данных при большой разнице частот передатчика и приемника, а также получаемые данные с забойной телеметрической системы являются недостоверными.

Техническим результатом, на достижение которого направлено создание данного изобретения, является повышение достоверности приема данных за счет уменьшения ошибки определения фазы сигнала, вызванной различием частот генераторов сигналов на передающем и принимающем концах линии связи.

Поставленный технический результат достигается тем, что в устройство синхронизации по циклам, содержащее последовательно соединенные генератор тактовых импульсов, первый распределитель импульсов, первый блок элементов И, второй вход которого является информационным входом устройства, блок декодирования синхросигнала, элемент ИЛИ, второй распределитель импульсов, второй блок элементов И, накопитель информации, регистр сдвига, информационный вход которого соединен с вторым входом первого блока элементов И, а выход регистра сдвига соединен через второй блок элементов И с входами накопителя информации, вход сигнала считывания которого связан с соответствующим выходом второго распределителя импульсов, а выходы блока декодирования подключены к входам элемента ИЛИ, в него дополнительно введены четыре элемента И, два элемента НЕ, источник опорного напряжения, компаратор уровня, счетчик синхросигналов, счетчик тактов, счетчик интервала коррекции, вычислительный блок и регистр однобайтовый, причем выход элемента ИЛИ соединен с первым входом компаратора уровня и с первыми входами первого и второго элементов И, а выход источника опорного напряжения соединен со вторым входом компаратора уровня, выход которого соединен со вторым входом первого элемента И и через первый элемент НЕ - с вторым входом второго элемента И, выходы первого и второго элементов И подключены к входам счетчика синхросигналов, выход генератора тактовых импульсов соединен с первым входом счетчика тактов и с первым входом счетчика интервала коррекции, второй вход счетчика тактов соединен со вторым выходом счетчика синхросигналов, а второй вход счетчика интервала коррекции соединен с первым выходом вычислительного блока, один вход которого соединен с выходом счетчика тактов, а другой вход вычислительного блока подключен к первому выходу счетчика синхросигналов, при этом второй выход вычислительного блока соединен с входом регистра однобайтового, выход которого соединен с вторым входом третьего элемента И и с входом второго элемента НЕ, выход которого соединен с вторым входом четвертого элемента И, при этом выход счетчика интервала коррекции соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к одному и другому корректирующим входам генератора тактовых импульсов.

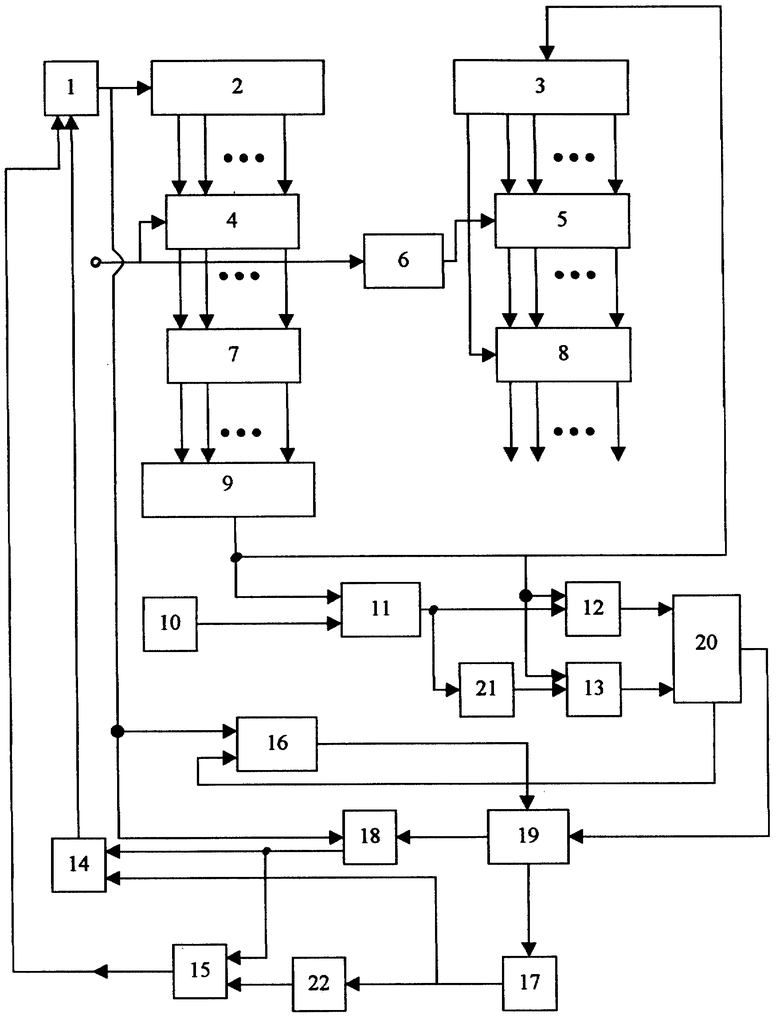

На чертеже представлена блок-схема устройства синхронизации по циклам.

Устройство синхронизации по циклам содержит генератор тактовых импульсов 1, два распределителя импульсов 2 и 3, два блока элементов И 4 и 5, регистр сдвига 6, блок декодирования синхросигнала 7, накопитель информации 8, элемент ИЛИ 9, источник опорного напряжения 10, компаратор уровня 11, элементы И 12,13, 14 и 15, счетчик тактов 16, регистр 17 однобайтовый, счетчик 18 интервала коррекции, вычислительный блок 19, счетчик 20 синхросигналов, элементы НЕ 21 и 22.

Генератор тактовых импульсов 1 связан со входом первого распределителя 2 импульсов, выход которого соединен с входом первого блока 4 элементов И, выходы последнего подсоединены с входом блока декодирования 7, который своим выходом связан с входами элемента ИЛИ 9.

При этом выход элемента ИЛИ 9 соединен с входом второго распределителя 3 импульсов, выход которого подключен к входу второго блока элементов И 5, другой вход последнего связан с выходом регистра сдвига 6.

Выход второго блока элементов И 5 соединен с входом накопителя информации 8.

Выход элемента ИЛИ 9 также связан с первым входом компаратора уровня 11 и с первыми входами элементов И 12 и 13.

Выходы элементов И 12 и 13 подключены к входам счетчика 20 синхросигналов.

А выход генератора 1 тактовых импульсов соединен с первым входом счетчика 16 тактов и с первым входом счетчика 18 интервала коррекции.

При этом второй вход счетчика 16 тактов связан со вторым выходом счетчика 20 синхросигналов, а выход счетчика 18 интервала коррекции соединен с первыми входами первого 14 и второго 15 элементов И, выходы которых подключены соответственно к одному и другому корректирующим входам генератора тактовых импульсов 1.

Один вход вычислительного блока 19 подключен к входу регистра 17 однобайтового, выход последнего связан со вторым входом третьего элемента И 14 непосредственно, а через элемент НЕ 22 - с вторым входом четвертого элемента И 15. Выходы элементов И 14 и 15 являются корректирующими входами генератора 1 тактовых импульсов.

Работает устройство следующим образом.

Информационный сигнал поступает на вход первого блока элементов И 4. Первый распределитель импульсов 2 находится в произвольном состоянии до обнаружения синхросигнала блоком 7 декодирования сигнала. В момент обнаружения синхросигнала второй распределитель 3 импульсов приводится в начальное состояние сигналом с выхода элемента ИЛИ 9. При этом снятие информации с регистра сдвига 6 через второй блок элементов И 5 тактируется вторым распределителем 3 импульсов, приведенным в синфазное состояние с принимаемым сигналом.

В момент получения синхросигнала с выхода элемента ИЛИ 9 поступает сигнал, который через элементы И 12 и 13 осуществляет увеличение содержимого счетчика 20 синхросигналов на 1 или его сброс в зависимости от соотношения сигналов на компараторе 11 поступающих с выхода элемента ИЛИ 9 и с источника опорного напряжения 10.

С компаратора 11 сигнал поступает на элемент И 12 непосредственно, а на элемент И 13 через элемент НЕ 21.

При этом, если уровень синхросигнала меньше установленного в источнике 10 опорного напряжения порога, то счетчик 20 синхросигналов сбрасывается. А если уровень синхросигнала больше установленного в источнике 10 опорного напряжения порога, то в счетчик 20 синхросигналов записывается 1. До тех пор, пока счетчик 20 синхросигналов находится в состоянии 0, т.е. сброса, на его первом выходе, соединенном с входом счетчика 16 тактов, присутствует напряжение, удерживающее счетчик 16 тактов в положении "сброс".

При поступлении на счетчик 16 тактов с генератора 1 первого синхросигнала производится запуск счетчика 16 тактов импульсом со счетчика 20 синхроимпульсов.

После того как в счетчике 20 произойдет запись накопленных синхросигналов N (где N=3..10 выбирается экспериментальным путем), то на другом выходе счетчика 20 синхросигналов, связанном со входом вычислительного блока 19, формируется импульс запуска вычислительного блока 19, по которому поступает накопленное число тактов в счетчике 16 тактов.

В вычислительном блоке 19 производится вычисление кода коррекции К по формуле

где N - число накопленных сигналов в счетчике 20 синхросигналов;

Т - ожидаемое количество тактов генератора 1 тактовых импульсов;

С - количество тактов, записанных в счетчике 16 тактов.

Полученный модуль кода коррекции К записывается в счетчик 18 интервала коррекции, тактируемый импульсом с генератора 1 тактовых импульсов.

После этого счетчик 18 интервала коррекции на выходе начинает вырабатывать импульс каждые К тактов генератора 1 тактовых импульсов.

Импульс со счетчика 18 интервала коррекции через элементы И 14 или 15 поступает на корректирующие входы генератора 1 тактовых импульсов.

Данный импульс проходит либо через элемент И 14, либо элемент И 15 в зависимости от состояния регистра 17, выход которого соединен со входом элемента И 14 непосредственно, а с входом элемента И 15 через элемент НЕ 22.

С вычислительного блока 19 в регистр 17 однобайтовый записывается знак числа К - кода коррекции.

При поступлении на корректирующий вход генератора 1 импульса с выхода элемента И 14, на выходе генератора 1 появляется дополнительный импульс. А при поступлении на другой корректирующий вход генератора 1 импульса с выхода элемента И 15 на выходе генератора 1 следующий выходной импульс подавляется.

Таким образом, средняя частота генератора 1 приводится в соответствие с частотой генератора формирователя данных передатчика (не показан) что приводит к уменьшению ошибки определения фазы сигнала, и, как следствие, повышается надежность приема данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| СКВАЖИННЫЙ ПРИБОР ДЛЯ ИЗМЕРЕНИЯ И ПЕРЕДАЧИ ЗАБОЙНЫХ ПАРАМЕТРОВ СКВАЖИНЫ В ПРОЦЕССЕ БУРЕНИЯ | 2000 |

|

RU2189444C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЗАБОЙНОЙ ИНФОРМАЦИИ | 2001 |

|

RU2206738C1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство синхронизации по циклам | 1988 |

|

SU1755387A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| Устройство для синхронизации по циклам | 1983 |

|

SU1172052A1 |

Изобретение относится к технике связи и может быть использовано для приема данных с забойной телеметрической системы, использующей циклически повторяющиеся пакеты цифровых данных. Технический результат - повышение достоверности приема данных за счет уменьшения ошибки определения фазы сигнала, вызванной различием частот генератора сигналов на передающем и принимающем концах линии связи. Устройство дополнительно содержит четыре элемента И, два элемента НЕ, источник опорного напряжения, компаратор уровня, счетчик синхросигналов, счетчик тактов, счетчик интервала коррекции. 1 ил.

Устройство синхронизации по циклам, содержащее последовательно соединенные генератор тактовых импульсов, первый распределитель импульсов, первый блок элементов И, второй вход которого является информационным входом устройства, блок декодирования синхросигнала, элемент ИЛИ, второй распределитель импульсов, второй блок элементов И, накопитель информации, регистр сдвига, информационный вход которого соединен с вторым входом первого блока элементов И, а выход регистра сдвига соединен через второй блок элементов И с входами накопителя информации, вход сигнала считывания которого связан с соответствующим выходом второго распределителя импульсов, а выходы блока декодирования подключены к входам элемента ИЛИ, отличающееся тем, что в него дополнительно введены четыре элемента И, два элемента НЕ, источник опорного напряжения, компаратор уровня, счетчик синхросигналов, счетчик тактов, счетчик интервала коррекции, вычислительный блок и регистр однобайтовый, причем выход элемента ИЛИ соединен с первым входом компаратора уровня и с первыми входами первого и второго элементов И, а выход источника опорного напряжения соединен со вторым входом компаратора уровня, выход которого соединен со вторым входом первого элемента И и через первый элемент НЕ с вторым входом второго элемента И, выходы первого и второго элементов И подключены к входам счетчика синхросигналов, выход генератора тактовых импульсов соединен с первым входом счетчика тактов и с первым входом счетчика интервала коррекции, второй вход счетчика тактов соединен со вторым выходом счетчика синхросигналов, а второй вход счетчика интервала коррекции - с первым выходом вычислительного блока, один вход которого соединен с выходом счетчика тактов, а другой вход вычислительного блока подключен к первому выходу счетчика синхросигналов, при этом второй выход вычислительного блока соединен с входом регистра однобайтового, выход которого соединен с вторым входом третьего элемента И и с входом второго элемента НЕ, выход которого соединен с вторым входом четвертого элемента И, при этом выход счетчика интервала коррекции соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к одному и другому корректирующим входам генератора тактовых импульсов.

| Устройство синхронизации по циклам | 1988 |

|

SU1755387A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| US 3591720 А, 06.07.1978 | |||

| US 4361898 А, 30.11.1982 | |||

| Устройство для измерения переменного магнитного поля | 1977 |

|

SU654918A1 |

Авторы

Даты

2002-11-10—Публикация

2000-10-20—Подача