Изобретение относится к вычислительной технике, а именно к специализированным вычислительным устройствам, залдиты от ошибок внешней памяти ЦВМ (накопителей на магнитных лентах, дисковой и оптической памяти ).

Известно устройство цикловой синхронизации для внешней памяти, сорержащее дешифратор синхрокомбинаций, регистры сдвига, преобразователь кода, решающий блок, блок сравнения, блок памяти и формирователь импульсов 11.

недостатком этого устро.йства является невозможность достаточного . надежного вхождения вэсинхронизм менее чем за четыре цикла.

Наиболее близким к изобретению является устройство цикловой синхронизации для внешней памяти, содержащее узел обнаружения ошибок с детектором синхросигнала , последовательно соединенные блок счетчиков и пороговый блок, дешифратор, коммутатор генератор импульсов, сумматор и регистр задержки, в котором передаваемая последовательность формируется в виде суммы по модулю два двух последовательностей : информационного кодового слова и дополнительной последовательности, переводящей кодовое слово в смежный класс, соответствующий номеру кодового слова в сообщении. Узлом обнаружения ошибок в принятой последовательности выделяются номера кодовых слов сообщения, которые записываются в блок счетчиков, по одновременному переполнению большинства которых пороговый блок вырабатывает сигнал циклового фазирования. Из регистра задержки, длина которого выбира-. ется равной длине сообщения, по . цикловому синхронизму последовательно считываются кодовые слова сообщения 2 J.

Недостатком устройства является необходимость хранения всего сообщения до образования сигнала его циклового фазирования, в силу чего не представляется возможным осуществление вхождения в цикловый синхронизм в начале сообщения, что снижает быстродействие устройства, а также может привести к неправильному декодированию первых кодовых слов и потере адресной части формата в заголовке записи.

Цель изобретения - повьциение быстродействия устройства путем повьшения скорости вхождения в цикловый синхронизм.

Поставленная цель достигается тем, что в устройство цикловой синхронизации для внешней памяти, содержащее селектор синхросигналов,

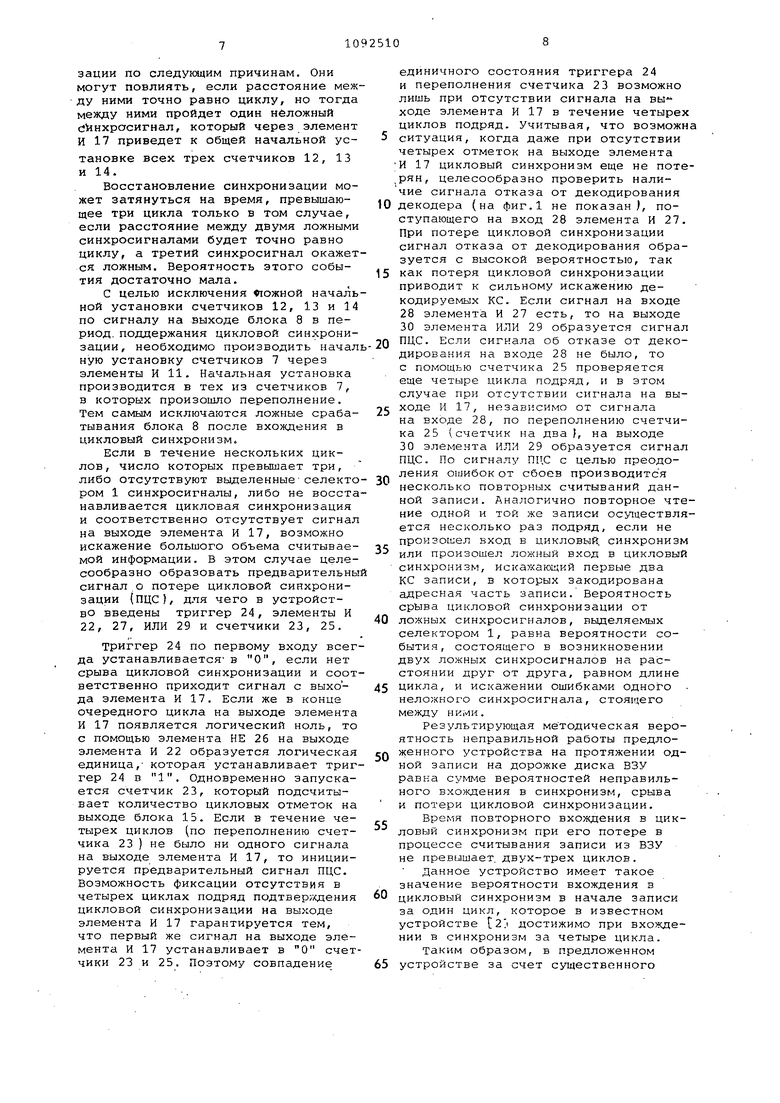

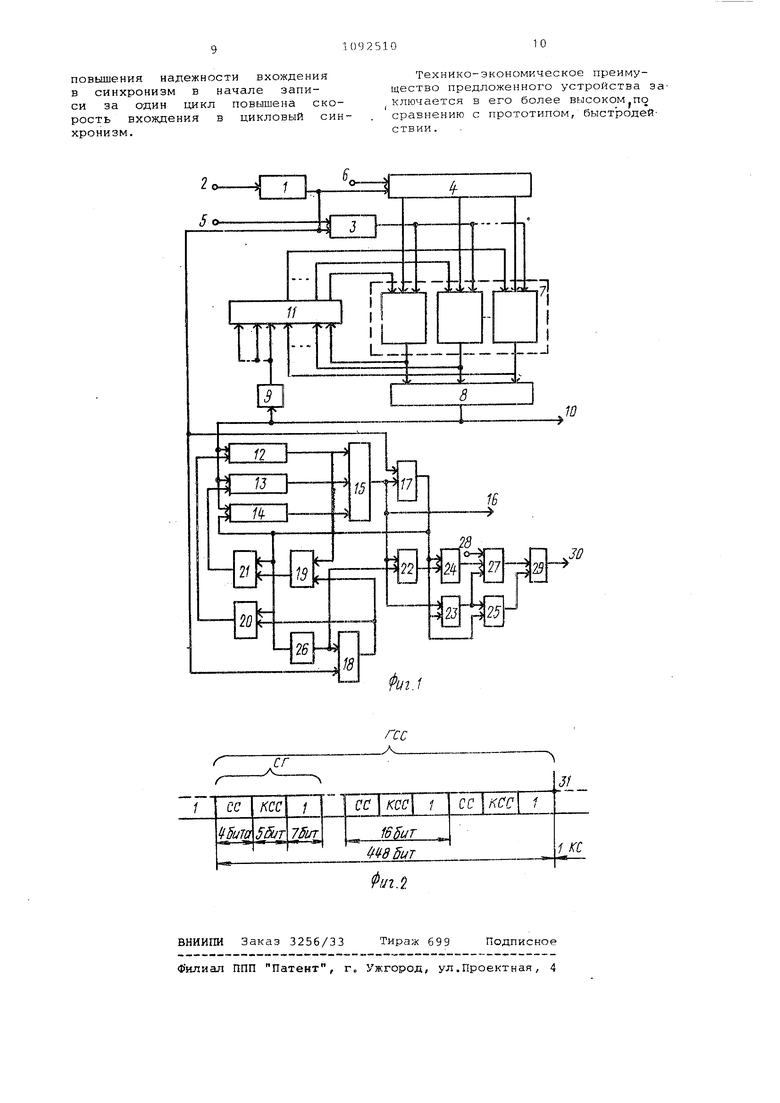

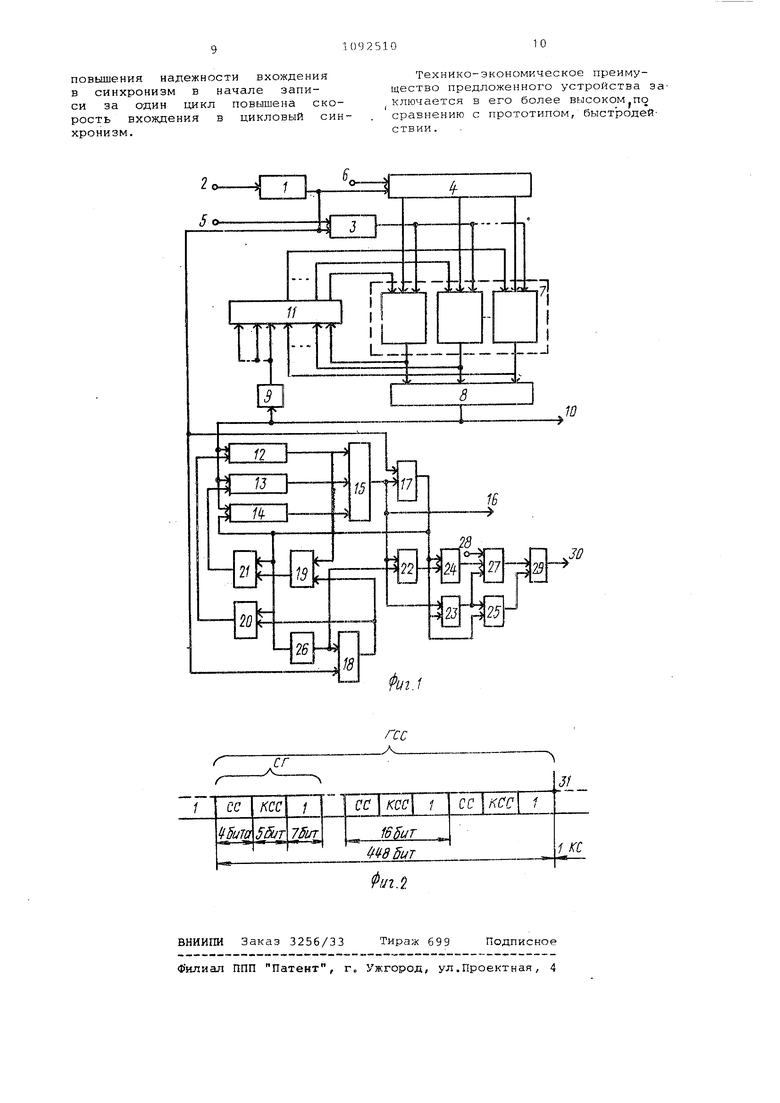

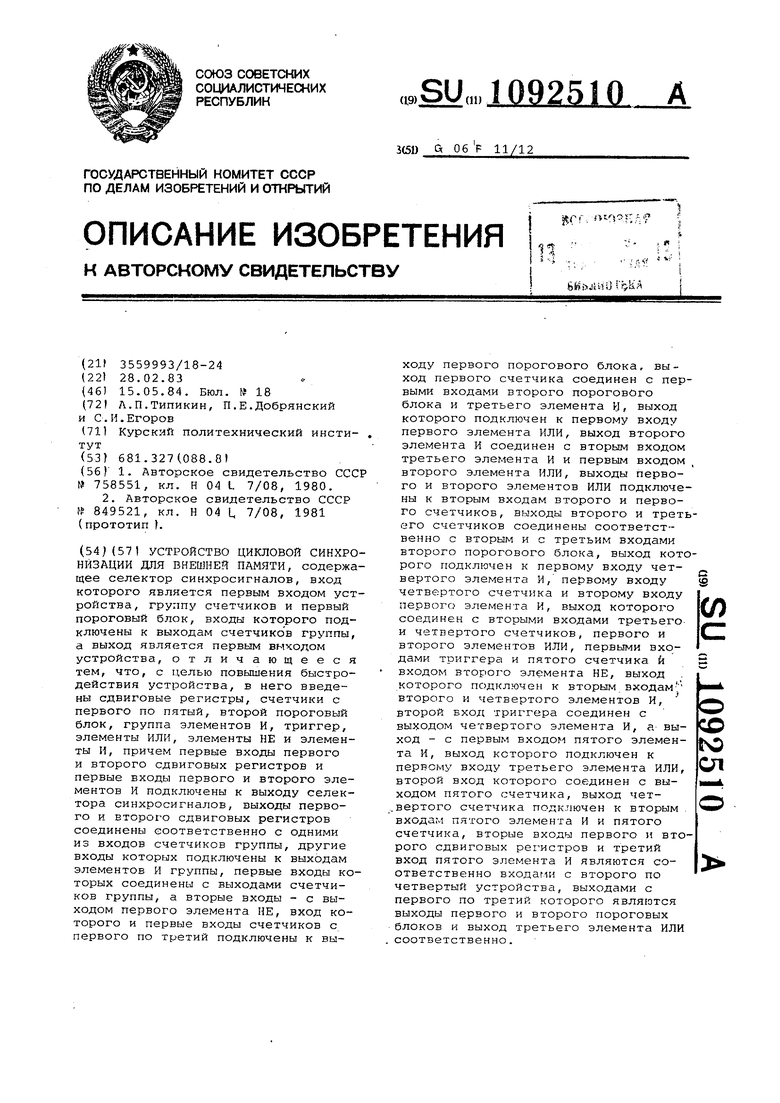

вход которого является первым входо устройства, группу счетчиков и первый пороговый блок, входы которого подключены к выходам счетчиков группы, а выход является первым выходом устройства, введены сдвиговые регистры, счетчики с первого по пятый, второй пороговый блок, группа элементов И, триггер, элементы ИЛИ, элементы НЕ и элементы И, причем первые входы первого и второго сдвиговых регистров и первые входы первого и второго элементов И подключены к выходу селектора синхросигналов, выходы первого и второго сдвиговых регистров соединены соответственно с одними из входов счетчиков группы, другие входы которых подключены к выходам элементов И группы, первые входы которых соединены с выходами счетчиков группы, а вторые входы - с выходом первого элемента НЕ, вход которого и первые входы счетчиков с первого по третий подключены к выходу первого порогового блока, выход первого счетчика соединен с первыми входами второго порогового блока и третьего элемента И, выход которого подключен к первому, входу первого элемента ИЛИ, выход второго элемента И соединен с вторым входом третьего элемента И и первьом входом второго элементаИЛИ.выходы первого и второго элементов ИЛИ подключены к вторым входам второго и первого счетчиков, выходы второго и третьего счетчиков соединены соответственно со вторым и с третьим входами второго порогового блока, выход которого подключе к первому входу четвертого элемента И,, первому входу четвертого счетчика и второму входу первого элемента И, выход которого соединен с вторым входами третьего и четвертого счетчиков, первого и второго элементов ИЛИ, первыми входами триггера и пятого счетчика и входом второго элемента НЕ, выход которого подключен вторым входам второго и четвертого элементов И, второй вход триггера соединен с выходом четвертого элемента И, а выход - с первым входом пятого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом пятого счетчика, выход четвертого счетчика подключен к вторым входам пятого элемента И и пятого счетчика, вторые входы, первого и второго сдвиговых регистров и третий вход пятого элемента И являются соответственно входами с второго по четвертый устройства, выходами с первого по третий которого яоляются Btjxozuj neppoio и второго пороговых блоков и Bhjxo.n третьего элемента ИЛИ соответственно. На фиг.1 приведена структурная схема предложенного устройства; на фиг.2 - формат группы синхросигналов (ГСС), поясняющий работу устрой .ства. Устройство содержит селектор 1 синхросигналов, первый вход 2 устройства, первый 3 и второй 4 сдвиго вые регистры, второй 5 и третий 6 входы устройства, группу счетчиков 7, первый пороговый блок 8,первый элемент НЕ 9, первый выход 10 устройства, группу элементов И 11, первый 12, второй 13 и третий 14 счетчики, второй пороговый блок 15 с выходом 16. элементы И с первого по третий 17, 18 и 19, второй 20 и первый 21 элементы ИЛИ, четвертый элемент И 22, четвертый сметчик 23, триггер 24, пятый счетчик 25, второ элемент НЕ 26, пятый элемент И 27 с входом 28 и третий элемент ИЛИ 29 с выходом 30. Выходы устройства подключаются на входы блока управ пения декодера (на фиг.1 не показан). На фиг,2 обозначена цикловая отметка 31. Число счетчиков 7 и порог блока 8 должны определяться параметрами применяемого в декодере кода, законом распределения ошибок и требов ниями к надежности цикловой синхронизации . Все блоки устройства реализуются по известным схемам и на типовых элементах средней степени интеграци расширенной серии интегральных схем (ИС ) типа К 155. Селектор 1 синхросигнала построе по известной схеме на трехразрядном счетчике. Сдвиговые регистры 3 и 4 построены на ИСК155ИР1. Счетчики 7 12, 13, 14 построены по известной схеме двоичного счетчика с применением ИСК155 ИЕ7. Счетчики 23 и 25 представляют собой двоичные счетчик построенные на ИС К155 ИЕ5. Пороговые блоки 8, 15 построены на основе известного принципа реализации булевых функций с применением ПЗУ, эл менты И, ИЛИ, НЕ и триггер построен на известных логических элементах ИС К155. На фиг.2 приведен формат ГСС при длине кодового слова (КС) четыреста сорок восемь бит. На фиг.2 обозначены СС - синхросигнал, КСС - код синхросигнала, СГ синхрогруппа, ГСС - группа синхросигналов, 1КС - первое кодовое сло. во записи. Перед первым КС записывается сле дующая ин|Е)Ормация. Вначале записывается несколько десятков байт логических единиц для входа тактового генератора в тактовый синхронизм, а затем, в пределах длины блока одного КС, записывается ГСС. В формате ГСС размещаются двадцать восемь СГ длиной по шестнадцать бит. В каждой синхрогруппе записываются: в начале синхрогруппы-, СС длиной четыре бита/ затем - КСС расстояния начала синхрогруппы до первого бита первого КС (точка 31 на фиг.2), причем длина КСС, равная пяти битам, соответствует количеству синхрогрупп до оуметки 31 и отражает только пять старших разрядов расстояния в битах до отметки 31, а младшие четыре разряда указывать нет смысла ввиду того, что длины каждой синхрогруппы одинаковы и кратны степени двойки/ затем остальные семь бит заполняются -единицами для поддержания тактового синхронизма. Устройство работает следующим образом. Устройство предназначено для защиты от ошибок накопителей на магнитных лентах, дисковых и оптических внешних запоминающих устройств (ВЗУ ЦВМ и построено для работы с блоками кодовых слов (кС), разделенных синхросигналом длиной четыре бита и записанными на носитель информации, обладающий высокой помехоустойчивостью самосинхронизирующимся способом записи, известным как модифицированная частотная модуляция (МФМ - записьК Вхождение в цикловый синхронизм осуществляется путем ар1ализа специальной группы синхросигналов (ГСС, фиг.2, записываемой в начале каждой записи перед первым КС. В ГСС длиной не более одного КС с большой из- . быточностью записываются периодически расположенные синхросигналы и коды их расстояний до первого бита первого КС записи. По одновременному переполнению большинства счетчиков группы счетчиков расстояний устройство обеспечивает минимальное время достаточно надежного вхождения в синхронизм за один цикл в начале каждой записи на дорожке носителя информации. На вход 2 (фиг.) устройства поступает в последовательном коде считываемая с дорожки носителя информация в виде модифицированной частотно-модулированной (МФМ) последовательности сигналов, состоящей из нескольких байт единиц, группы синхросигналов и кодовых слов, разделенных синхросигналами длиной четыре бита. На вход 5 устройства поступает такая же, но демодулированная в потенциальный код, последовательность сигналов. Селектором 1 выделяется первый неискаженный ошибками синхросигнал длиной четыре бита. В момент выделения синхросигнала На выходе селектора 1 образуется сигнал, по которому производится запись логической единицы, -поланной

на вход б регистра 4, в его vшaдший разряд. Этот же сигнал разрешает запись кода синхросигнала в регистр 3 в течение пяти тактов. По сигналу на выходах регистра 4 осуществляется запись кода, накопленного в регистре 3, впять старших разрядов первого иэ счетчиков 7 и запускается этот счетчик 7. После этого селектором 1 выделяется следующий не искаженный ошибками синхросигнал, вновь ос лцествляется запись кода синхросигнала в регистр 3, в младший разряд регистра 4 заносится единица, а предыдущая единица сдвигается в следующий разряд. В результате разрешается перезапись содержимого регистра 3 в пять старших разрядов второго из счетчиков 7 и запускается этот счетчик. Процесс повторяется после выделения каждого синхросигнала селектором 1. В результате запускаются все счетчики 7. Несмотря на то, что они были запущены в разное время, переполнение их должно произойти одновременно, если коды выделенных синхросигналов, записанные в сметчики 7 как их начальные установки, не были искажены ошибками. По одновременному переполнению определенного числа счетчиков 7, аревышающего порог срабатывания блока 8, на выходе 10 образуется сигнал цикловой отметки, соответствующей точке 31 (Аиг,2), т„е. началу первого бита первого КС Выбором соответствующего числа счетчиков 7 и порога срабатывания блока 8 обеспечивается высокая надежность вхождения в цикловый синхронизм за один цикл при искажении ошибками определенной части синхрогрупп группы синхросигналов.

В дальнейшем цикловый синхронизм поддерживается и восстанавливается счетчиками 12, 13 и 14, блоком 15, элементами И 17, 18 и 19, элементами ИЛИ 20 и 21, элементами НЕ 9 и 26, элементами И 11, которые контролируют и осуществляют повторное вхождение в цикловый синхронизм за время не более двух-трех циклов.

По сигналу входа в цикловый синхронизм, образованному на первом выходе 10 устройства, запускаются все три счетчика 12, 13 и 14, предварительно установленные в начальное состояние. По одновременному переполнению всех трех или двух из трех счетчиков 12, 13 и 14, на выходе блока 15 появляется сигнал, определяющий начало очередного КС. Если в этот же момент времени детектором синхросигнала, был выделен синхросигнал, разделяющий группы соседних КС, тс на выходе элемента И 17 формируется сигнал (логическая единица f-подтверждения правильности отсчета очередкого цикла. По этому сигналу происходит установка в начальное состонние непосредственно счетчика 14, а через элементы ИЛИ 21 и 20 - счетчиков 13 и 12 соответственно. И так длее в конце каждого цикла в процесс поступления очередных КС.

Если же на выходе элемента И 17 не образуется логическая единица, т это является сигналом ошибки в цикловой синхронизации. Автоматическое восстановление цикловой синхронизации осуществляется эа два-три цикла путем анализа двух подряд выделенны селектором 1 синхросигналов, разделяющих группы КС.

Сигнал р выделении селектором 1 первого жб синхросигнала проходит через элементы И 18 и ИЛИ 20 и устанавливает в начальное состояние счетчик 12. Это ргшносильно сдвигу во времени начала цикла, отсчитываемого счетчиком 12. Эта операция может сразу же привести к васстановлению синхронизма, если его потеря вызвана сбоем двух из трех счетчиков 12 13 и 14. Если же ошибка была вызвана неправильным отсчетом цикла счетчиками 12, 13 и 14 одноЕфеменно, то окончательное восстановление синхронизма осуиествляется по второму выделенному синхоосигнаj yi Если сигнал о выделении этого jEiToporo синхросигнала поступает с селектора 1 после первого синхросигнала спустя ровно один цикл, то он проходит через элементы И 18 и 19 и элементы ИЛИ 21 и 20 на начальную установку счетчиков 12 к 13. Это приводит к тому, что следугсщий очередной цикл будет сдвинут и по его окончании, по одновременному переполнению двух из трех счетчиков 12, 13 и 14 на выходе блока 15 появится сигнал цикловой отметки совпадающий с третьим синхросигналом, вьщеленным селектором 1. Таким образом, цикловый синхронизг может быть восстановлен за два цикла. Если в первом из них произошел сбой, то два синхросигнала, обрамляющие второй цикл, приведут к установлению правильной работы счетчиков 12, 13 и 14 в третьем цикле. Если после ошибки первый выделенный синхросигнал был ложным, то второй неложный синхросигнал изменит начало цикла только всчетчике 12. Тогда третий неложный синхросигнал приведет к восстановлению синхронизации. В этом случае время восстановления увеличивается до трех циклов. Таким образом, появление одного ложного синхросигнала не приводит к срыву синхронизации. Появление двух ложных синхросигналов также не приводит к срыву синхронизации по следующим причинам. Они могут повлиять, если расстояние меж ду ними точно равно циклу, но тогда между ними пройдет один неложный с 1нхрасигнал, который через элемент И 17 приведет к общей начальной установке всех трех счетчиков 12, 13 и 14. Восстановление синхронизации может затянуться на время, превышающее три цикла только в том случае, если расстояние между двумя ложными синхросигналами будет точно равно циклу, а третий синхросигнал окажет ся ложным. Вероятность этого события достаточно мала. С целью исключения «южной началь ной установки счетчиков 12, 13 и 1 по сигналу на выходе блока 8 в период, поддержания цикловой синхрони зации, необходимо производить начал ную установку счетчиков 7 через элементы И 11. Начальная установка производится в тех из счетчиков 7, в которых произошло переполнение. Тем самым исключаются ложные сраба тывания блока 8 после вхождения в цикловый синхронизм. Если в течение нескольких циклов, число которых превышает три, либо отсутствуют выделенные-селект ром 1 синхросигналы, либо не восст навливается цикловая синхронизация и соответственно отсутствует сигнал на выходе элемента И 17, возможно искажение большого объема считывае мой информации. В этом случае целе сообразно образовать предварительн сигнал о потере цикловой синхронизации (ПЦС), для чего в устройство введены триггер 24, элементы И 22, 27, ИЛИ 29 и счетчики 23, 25. триггер 24 по первому входу всег да устанавливается в О, если нет срыва цикловой синхронизации и соот ветственно приходит сигнал с выхода элемента И 17. Если же в конце очередного цикла на выходе элемента И 17 появляется логический ноль, то с помощью элемента НЕ 26 на выходе элемента И 22 образуется логическая единица,- которая устанавливает трих гер 24 в 1. Одновременно запускается счетчик 23, который подсчитывает количество цикловых отметок на выходе блока 15. Если в течение четырех циклов (по переполнению счетчика 23 ) не было ни одного сигнала на выходе элемента И 17, то инициируется предварительный сигнал ПЦС. Возможность фиксации отсутствия в четырех циклах подряд подтвер/хдения цикловой синхронизации на выходе элемента И 17 гарантируется тем, что первый же сигнал на выходе элемента И 17 устанавливает в О счет чики 23 и 25. Поэтому совпадение единичного состояния триггера 24 и переполнения счетчика 23 возможно лишь при отсутствии сигнала на вы ходе элемента И 17 в течение четырех циклов подряд. Учитывая, что возможна ситуация, когда даже при отсутствии четырех отметок на выходе элемента И 17 цикловый синхронизм еще не потерян, целесообразно проверить наличие сигнала отказа от декодирования декодера (на фиг.1 не показан ), поступающего на вход 28 элемента И 27. При потере цикловой синхронизации сигнал отказа от декодирования образуется с высокой вероятностью, так как потеря цикловой синхронизации приводит к сильному искажению декодируемых КС. Если сигнал на входе 28 элемента И 27 есть, то на выходе 30 элемента ИЛИ 29 образуется сигнал ПЦС. Если сигнала об отказе от декодирования на входе 28 не было, то с помощью счетчика 25 проверяется еще четыре цикла подряд, и в этом случае при отсутствии сигнала на выходе И 17, независимо от сигнала на входе 28, по переполнению счетчика 25 (счетчик на два |, на выходе 30 элемента ИЛИ 29 образуется сигнал ПЦС. По сигналу ПЦС с целью преодоления ошибок от сбоев производится несколько повторных считываний данной записи. Аналогично повторное чтение одной и той же записи осуществляется несколько раз подряд, если не произошел вход в цикловый, синхронизм или произошел ложный вход в цикловый синхронизм, искажающий первые два КС записи, в которых закодирована адресная часть записи. Вероятность срыва цикловой синхронизации от ложных синхросигналов, выделяемых селектором 1, равна вероятности события, состоящего в возникновении двух ложных синхросигналов на расстоянии друг от друга, равном длине цикла, и искажении ошибками одного неложного синхросигнала, между ними. Результирующая методическая вероятность неправильной работы предложенного устройства на протяжении одной записи на дорожке диска ВЗУ равна сумме вероятностей неправильного вхождения в синхронизм, срыва и потери цикловой синхронизации. Время повторного вхождения в цикловый синхронизм при его потере в процессе считывания записи из ВЗУ не превышает, двух-трех циклов. Данное устройство имеет такое значение вероятности вхождения в цикловый синхронизм в начале записи за один цикл, которое в известном устройстве t2i достижимо при вхождении в синхронизм за четыре цикла. Таким образом, в предложенном устройстве за счет существенного

повышения надежности вхождения в синхронизм в начале записи за один цикл повышена скорость вхождения в цикловый синхронизм.

Технико-экономическое преимущество предложенного устройства заключается в его более высоком по сравнению с прототипом, быстродействии.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации внешних блоков памяти | 1985 |

|

SU1254457A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство для синхронизации по циклам | 1990 |

|

SU1709547A2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

Г

СГ

гсс А

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для цикловой синхронизации | 1978 |

|

SU758551A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для цикловой синхронизации | 1978 |

|

SU849521A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-05-15—Публикация

1983-02-28—Подача