Настоящее изобретение относится к видео ОЗУ (оперативное запоминающее устройство), выполненных в качестве двухпортовой памяти, и, конкретнее, к видео ОЗУ, которое приспосабливается к высокоскоростному системному тактовому сигналу, и способу вывода из него последовательных данных.

С увеличением числа портативных компьютеров, таких как переносные компьютеры (ноутбук), видео ОЗУ теперь очень широко используются в компьютерах. Видео ОЗУ является двухпортовой памятью, которая может быть асинхронно использована путем добавления функции регистра данных, способного передавать данные на высокой скорости в функцию нормального динамического ОЗУ. Видео ОЗУ и способ его работы раскрыты в патенте США N 4498155, названном "Полупроводниковое запоминающее устройство на интегральной схеме с последовательной матрицей и с матрицей случайной выборки" и поданном 5 февраля 1985 г. Такое видео ОЗУ разработано так, чтобы быть способным подключать порт динамического ОЗУ к ЦП (центральному процессору) и порт высокоскоростного ОЗУ - к периферии, такой как ЭЛТ (электроннолучевая трубка) или видеокамера, так что оно имеет широкую область применения. Чтобы разнообразить его функцию и хранить большее количество информации, разработано видео ОЗУ с высокой степенью интеграции.

В высококачественной графической системе от каждого устройства требуется работа в ответ на высокую частоту для того, чтобы эффективно выполнять графическое согласование между компьютером и его пользователем. Таким образом, внутренние схемы в видео ОЗУ также должны работать в ответ на высокоскоростной системный тактовый сигнал, подаваемый из системы. Это зависит от того, могут ли данные, переданные через линию ввода/вывода (1/0) данных внутри видео ОЗУ, откликаться на системный тактовый сигнал.

Наиболее близким к рассматриваемым изобретениям является метод для ввода-вывода данных, описанный в кн. Казаринова Ю.М. и др. "Применение микропроцессоров и микроЭВМ в радиотехнических системах". М., Высшая школа, 1988, стр. 30.

Целью настоящего изобретения является обеспечение видео ОЗУ, которое способно передавать данные на высокой скорости из регистра данных на внешнее устройство дисплея.

Другой целью настоящего изобретения является обеспечение видео ОЗУ, которое способно минимизировать время рабочего цикла, определенное последовательным тактовым сигналом.

Другой целью настоящего изобретения является обеспечение видео ОЗУ, которое способно уменьшить период каждого последовательного тактового импульса. Другой дополнительной целью настоящего изобретения является обеспечение видео ОЗУ, которое способно минимизировать время рабочего цикла путем вывода данных, хранящихся в регистре данных, когда предварительно заряжается линия последовательного ввода/вывода, относящаяся к следующим данным.

Еще одной дополнительной целью настоящего изобретения является обеспечение способа вывода последовательных данных из видео ОЗУ, которое выводит данные, хранящиеся в регистре данных, когда предварительно заряжается линия последовательного ввода/вывода, относящаяся к следующим данным.

Изобретения поясняются чертежами.

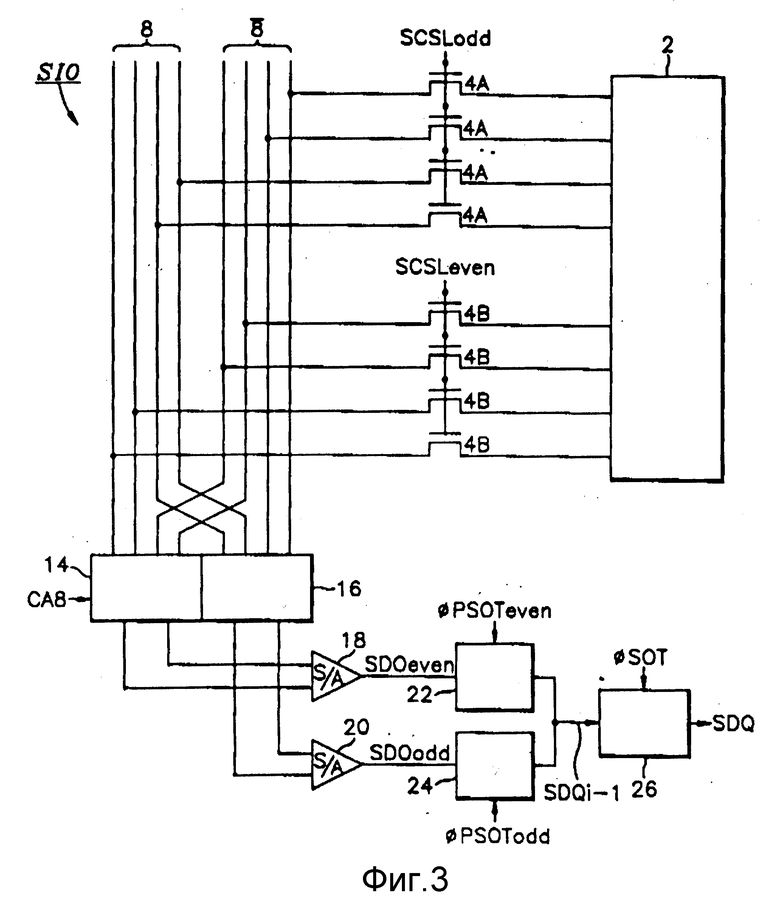

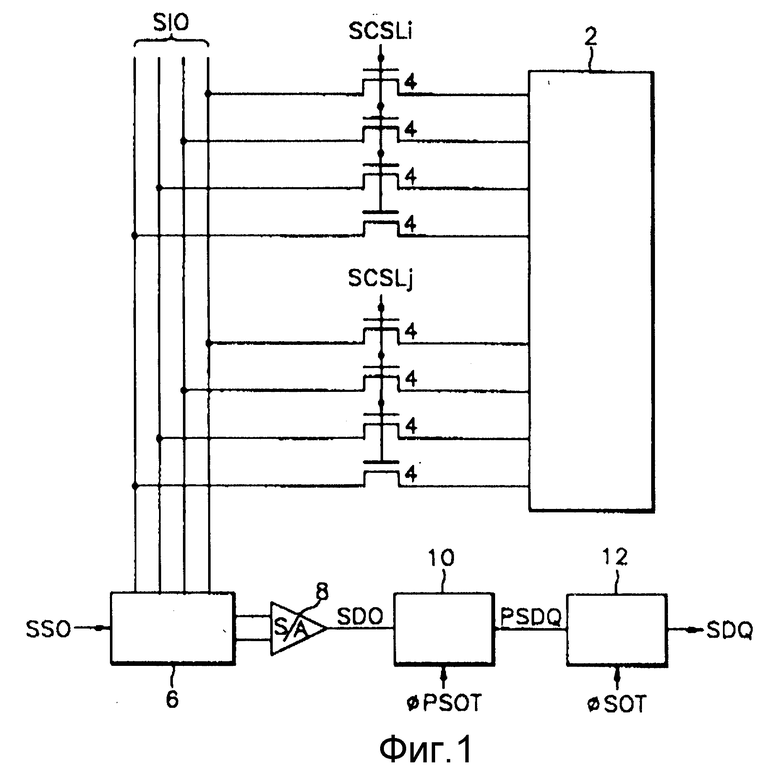

Фиг. 1 и 3 иллюстрируют вывод данных видео ОЗУ в соответствии с изобретениями.

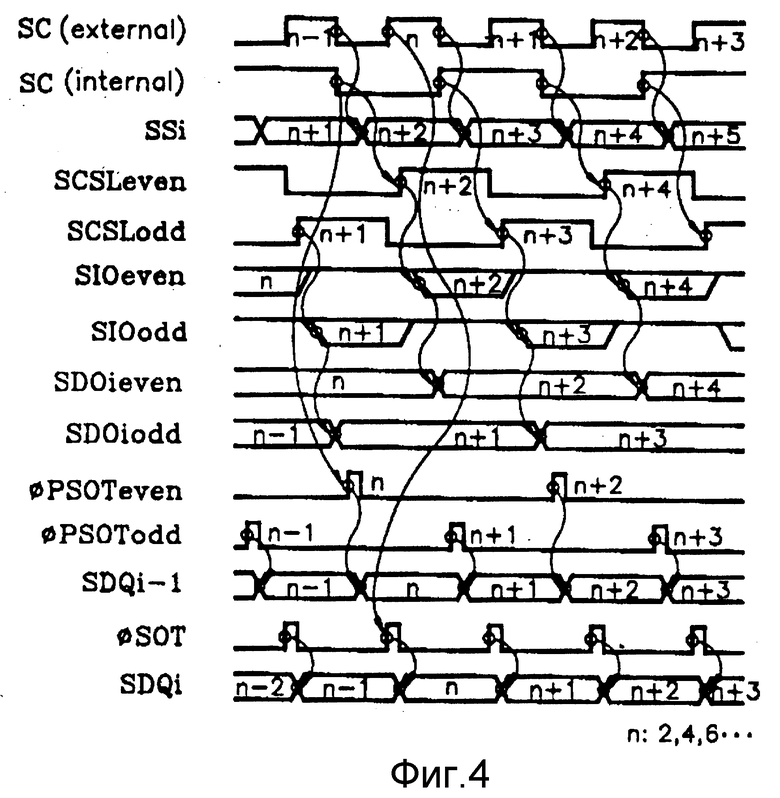

Фиг. 2 и 4 представляют временные диаграммы работы устройства.

На фиг. 1 вентиль 4 столбца для передачи данных функционирует между регистром данных 2 и линией SIOO (последовательного ввода/вывода). Последовательный вентиль 4 столбца имеет четыре последовательных вентиля столбца, обычно управляемых линией SCSLi выбора последовательного столбца, и четыре последовательных вентиля столбца, обычно управляемых линией SCSLj выбора последовательного столбца. Линия последовательного ввода/вывода состоит из четырех линий для приема данных, переданных с четырех последовательных вентилей столбца, в ответ на единственное разрешение сигнала выбора последовательного столбца. Данные на линии SIO последовательного ввода/вывода мультиплексируются через мультиплексор 6 и усиливаются через усилитель 8 считывания. Выход усилителя считывания подается на блок 10 фиксации (защелки), который управляется управляющим сигналом ⊘ PSOT, а выход блока 10 фиксации связан с блоком 12 фиксации и вывода, который управляется управляющим сигналом ⊘ SOT и затем выводит данные на выход. Процесс функционирования поясняется фиг. 2. Последовательный адрес увеличивается на падающем фронте последовательного тектового сигнала SC. Соответствующая линия выбора последовательного столбца отпирается на основе последовательного адреса. С отпиранием линии выбора последовательного столбца данные, хранящиеся в регистре 2 данные, выводятся на линию последовательного ввода/вывода, и усилитель 8 считывания тем самым выдает усиленный сигнал SDO. Как показано на фиг. 2, сигнал SDO, выработанный на падающем фронте n-ого последовательного тактового импульса C, фиксируется на падающем фронте (n+1)-го последовательного тактового импульса с помощью управляющего сигнала, а затем выдается как достоверные данные на нарастающем фронте (n+2)-го последовательного тактового импульса SC.

В соответствии с настоящим изобретением видео ОЗУ, имеющее регистр данных, который выводит последовательные данные в ответ на ввод последовательного адреса, синхронизированного с последовательным тактовым импульсом, содержит первую линию ввода/вывода данных для передачи данных, которые синхронизированы с четными последовательными адресами и затем выводятся из регистра данных, и вторую линию ввода/вывода данных для передачи данных, которые синхронизированы с нечетными последовательными адресами и затем выводятся из регистра данных.

Кроме того, в соответствии с настоящим изобретением способ вывода последовательных данных видео ОЗУВ, имеющего регистр данных, который выводит последовательные данные в ответ на ввод последовательного адреса, синхронизированного с последовательным тактовым импульсом, содержит первую операцию передачи данных, которые синхронизированы с четным последовательным адресом и затем выводятся из регистра данных на первую линию ввода/вывода данных, вторую операцию передачи данных, которые синхронизированы с нечетным последовательным адресом и затем выводятся из регистра на вторую линию ввода/вывода данных, - третью операцию синхронизации и фиксации данных, переданных из первой операции с четным последовательным адресом, четвертую операцию синхронизации и фиксации данных, переданных из второй операции с нечетным последовательным адресом, и пятую операцию синхронизации последовательных данных, фиксированных в третьей и четвертой операции последовательным тактовым импульсом, и затем выдачи синхронизированных последовательных данных на внешнее устройство.

Схема согласно фиг. 3 содержит регистр 2 данных, линию SIO последовательного ввода/вывода, имеющую 8 линий для передачи данных, считанных из регистра 2 данных, четыре вентиля 4A столбца, сформированных между линией SIO последовательного ввода/вывода и регистром 2 данных и переключаемых линиями SCSLOdd выбора последовательного столбца, которые выбираются нечетным адресом, для передачи данных из регистра 2 данных на четыре линии последовательного ввода/вывода, выбранных нечетным адресом; и четыре вентиля 4B столбца, сформированных между линией SIO последовательного ввода/вывода и регистром 2 данных и переключаемых линиями SCSLeven выбора последовательного столбца, которые выбираются четным адресом, для передачи данных из регистра 2 данных на четыре линии последовательного ввода/вывода, выбранных четным адресом, мультиплексоры 14 и 16 для мультиплексирования восьми линий последовательного ввода/вывода, реагирующих на логическое состояние ("низкое/высокое") CA8, усилитель S/A 18 считывания линии ввода/вывода для усиления выходного сигнала с выхода мультиплексора 14, который подключен к четырем линиям последовательного ввода/вывода, выбранных четным адресом, и усилитель S/A 20 считывания линии ввода/вывода для усиления выходного сигнала с мультиплексора 16, который входом подключен к четырем линиям последовательного ввода/вывода, выбранных нечетным адресом, четный блок 22 фиксации для фиксации выходного сигнала SDOeven усилителя S/A 18 считывания линии ввода/вывода под управлением сигнала ⊘ PSOTeven; нечетный блок 24 фиксации для фиксации выходного сигнала S ⊘ OOdd усилителя S/A 20 считывания линии ввода/вывода под управлением сигнала ⊘ PSOTodd и блок 26 фиксации и вывода для фиксации и вывода соответствующих выходных сигналов четного блока 22 фиксации нечетного блока 24 фиксации на внешнее устройство в ответ на управляющий сигнал ⊘ SOT. Как показано на фиг. 3, линия SIT последовательного ввода/вывода состоит из восьми линий, четыре из которых выбираются адресом 8 и остальные четыре адресом 8. Две из четырех линий последовательного ввода/вывода, выбранных адресом 8, и две из других четырех линий последовательного ввода/вывода, выбранных адресом 8, подаются на мультиплексор 14 четных, а остальные четыре линии SIO последовательного ввода/вывода данных подаются на мультиплексор 16 нечетных. На фиг. 3 единственный регистр 2 данных имеет две независимые линии последовательного ввода/вывода, которые выбираются различными адресами. Из-за ее выборочной работы время рабочего цикла может быть уменьшено, и это будет описано ниже.

На фиг. 4 приведена временная диаграмма, показывающая временные отношения между соответствующими управляющими сигналами схемы по фиг. 3. Со ссылками на фиг. 4 теперь будет описан процесс функционирования схемы по фиг. 3. Видео ОЗУ по настоящему изобретению способно синхронизироваться высокоскоростным последовательным тактовым сигналом, выводя таким образом последовательные данные путем выполнения независимых считывающих операций соответственно для нечетных и для четных адресных данных. Как показано на фиг. 3 и 4, четный блок 22 фиксации и нечетный блок 24 фиксации соответственно управляются сигналами ⊘ PSOTeven и ⊘ PSOTodd, которые поочередно возбуждаются каждые два периода последовательного тактового сигнала SC, и их соответствующие выходные сигналы подаются на блок 26 фиксации и вывода в ответ на управление от сигналов ⊘ PSOTeven и ⊘ PSOTodd. С возбуждением управляющего сигнала, синхронизируемого на нарастающем фронте каждого периода последовательного тактового импульса SC, данные выводятся из блока 26 фиксации и вывода на внешнее устройство. На основе такой работы, когда четыре из восьми линий SIO последовательного ввода/вывода выполняют считывающие действия для вывода данных к периферии, остальные четыре линии SIO последовательного ввода/вывода выполняют предварительный заряд и выравнивание, а когда остальные четыре линии SIO последовательного ввода/вывода выполняют считывающие действия для вывода данных к периферии, первые четыре линии выполняют предварительный заряд и выравнивание. В результате возможно синхронизировать с последовательным тактовым импульсом SC каждый их период и затем вывести последовательные данные.

Способ вывода последовательных данных по настоящему изобретению теперь будет описан в сравнении с традиционным способом. Как видно из фиг. 2, в каждом цикле линия SCSL выбора последовательного столбца должна предварительно заряжаться и выравниваться для единственного последовательного адреса, так как соответствующая линия последовательного ввода/вывода выбирается каждый цикл. Однако, как видно из фиг. 4, когда линия SIO последовательного ввода/вывода избирательно выбирается соответственно четному или нечетному адресу, соответствующая линия SIO последовательного ввода/вывода предварительно заряжает и выравнивает линию SCSL выбора последовательного столбца только в соответствующем цикле. На фиг. 2 линия SCSL выбора последовательного столбца должна управляться собственным импульсом для того, чтобы выполнить предварительный заряд и выравнивание, однако на фиг. 4 линия SCSL выбора последовательного столбца преобразуется только с помощью адреса. Мультиплексоры 14 и 16 работают для подключения соответствующей линии последовательного ввода/вывода к усилителям считывания линии ввода/вывода в зависимости от логического состояния последовательного адреса CA8. Все управляющие сигналы, соответствующие четным номерам, работают в случае, когда CA8 находится в логическом состоянии "низко", а все управляющие сигналы, соответствующие нечетным номерам, работают в случае, когда CA8 находится в логическом состоянии "высоко".

Как описано выше, видео ОЗУ по настоящему изобретению имеют независимые пути вывода последовательных данных соответственно для четного адреса и нечетного адреса, выводя, таким образом, последовательные данные каждый период последовательного тактового сигнала. Следовательно, возможно уменьшить время работы цикла видео ОЗУ и передавать данные на ЭЛТ на высокой скорости. Кроме того, возможно уменьшить промежуток времени между соответствующими периодами системного тактового импульса.

Изобретение относится к видеооперативным запоминающим устройствам и может быть использовано в качестве двухпортовой памяти. Техническим результатом является повышение быстродействия. Первое видео ОЗУ содержит мультиплексоры, линии последовательного ввода/вывода данных, вентили столбца и усилители считывания. Во втором видео ОЗУ дополнительно содержатся средства фиксации и средства фиксации и вывода. Согласно способу передают данные, которые синхронизированы с четным и нечетным адресами, синхронизируют их и c последующей синхронизацией зафиксированных данных с последовательным тактовым импульсом. 3 c.п. ф-лы, 4 ил.

| Казаринов Ю.М | |||

| и др | |||

| Применение микропроцессоров и микроЭВМ в радиотехнических системах | |||

| - М.: Высшая школа, 1988, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| US 4498155 A, 06.02.85. | |||

Авторы

Даты

1999-03-20—Публикация

1995-03-30—Подача