(Л

С

Изобретение относится к вычислительной технике и предназначено в первую очередь для ввода цифровой телеметрической информации в процессор информационно- управляющих систем, но может быть использовано также и для ввода информации, предварительно записанной на носитель, в процессор системы обработки. Цель изобретения - повышение достоверности работы устройства за исключения потерь вводимых данных при считывании дополнительной информации. Устройство содержит блок памяти, мультиплексор, счетчики и триггеры записи и считывания, два буферных регистра, сумматор, регистр уставки, схему сравнения, три элемента И, две линии задержки, инвертор, триггер выбора информации, две шины готовности, шину выбора информации. 1 ил.

Изобретение относится к вычислительной технике и предназначено для ввода цифровой информации в процессор информационно-управляющих систем реального времени.

Известно устройство для сопряжения источника информации с процессором, содержащее блок памяти буферный регистр, регистр уставки, сумматор, схему сравнения, счетчики и триггеры записи и чтения, две линии задержки, элементы И, НЕ 1. Данное устройство обеспечивает накопление в блоке памяти заданного объема информации, оповещение процессора о моментах начала и конца заполнения блока памяти, а также пословный и поблочный ввод информации R процессор.

Недостатком данного устройства является то, что процессор не имеет доступа к информации о текущем заполнении блока

памяти и, следовательно, не может эффективно вести вычислительный процесс.

Наиболее близким по технической сущности к з аявляЪмому стр6%УвуТТвл яется техническое решение, описанное в авт. св. № 1689958. В дополнение к вышеописанному основному изобретению устройство содержит второй буферный регистр, информационные входы которого подключены к выходам сумматора, выходы - к входным шинам интерфейса процессора а вход занесения информации - к выходу второй линии задержки, второй и третий элементы И и триггер выбора информации, к R-входу которого подключена шина выбора, S-вхо- ду - шина чтения и вторые входы вгороги и третьего элементов И, Прямой выход триггера выбора информации соединен с первым входом второго элемента И, а инверсный - с первым входом третьего элеVI

О

сл о

мента И. Выходы второго и третьего элементов И соединены с входами разрешения первого и второго буферных регистров соответственно. В исходном состоянии триггер выбора информации находится в состоянии 1, разрешая прохождение синхроимпульсов чтения на вход разрешения первого буферного регистра. При сбросе этого триггера данная цепь блокируется и открывается другая для прохождения синхроимпульса чтения на вход разрешения второго буферного регистра. Возврат триггера в исходное состояние происходит по заднему фронту синхроимпульса. Таким образом, по получении команды на смену вида информации устройство обеспечивает однократную выдачу на входные шины интерфейса процессора вместо вводимых данных дополнительной информации о текущем заполнении блока памяти устройства.

Однако при считывании дополнительной информации с второго буферного регистра происходит установка в 1 триггера чтения и соответственно в первый буферный регистр выводится очередное слово данных, при этом предыдущее еще не считанное процессором слово данных пропадает. Это происходит вследствие сохранения возможности поступления на S- вход триггера чтения синхроимпульса при сброшенном триггере выбора информации.

Цель изобретения - повышение достоверности работы устройства за счет исключения потерь вводимых данных при считывании дополнительной информации.

Поставленная цель достигается тем, что в устройстве сопряжения источника информации с процессором, содержащем блок памяти, информационные входы которого соединены с входными шинами устройства, адресные входы - с выходами мультиплексора, а вход управления -с входом установки в ноль триггера записи, входом занесения второго буферного регистра и выходом второй линии задержки, вход которой связан с первым входом первого элемента И и инверсным выходом триггера записи, выходы блока памяти подключены к информационным входам первого буферного регистра, вход занесения которого связан со счетным входом счетчика чтения, первой шиной готовности и инверсным выходом триггера чтения, прямой выход которого через первую линию задержки связан с вторым входом первого элемента И, выход которого подключен к R-входу триггера чтения, шина записи связана с S-входом триггера записи, прямой выход которого связан Со счетным входом счетчика записи, кроме

того, выходы триггера записи подключены к управляющим входам мультиплексора, а выходы счетчика чтения - к первым входам мультиплексора и схемы сравнения, выходы

счетчика записи соединены с вторыми входами мультиплексора, схемы сравнения и сумматора, первые входы которого связаны с выходами регистра уставки, а выходы - с информационными входами второго буфер0 ного регистра, причем выход переноса сумматора подключен к второй шине готовности, а входы регистра уставки - к выходным шинам интерфейса процессора, кроме того, выход схемы сравнения связан

5 с входами уставки в ноль обоих счетчиков и входом элемента НЕ, выход которого соединен с третьим входом первого элемента И, R-вход триггера выбора связан с шиной выбора, S-вход последнего - с вторыми входа0 ми второго и третьего элементов И, первые входы которых связаны с прямым и инверсным выходами того же триггера соответственно, а выходы - с входами разрешения соответственно первого и второго буфер5 ных регистров, выходы которых объединены поразрядно и подключены к входным шинам интерфейса процессора, выход второго элемента И соединен с S-входом триггера чтения, а R-вход триггера выбора информа0 ции - с шиной чтения.

В связи с отсутствием в известных технических решениях признаков, сходных с признаками, отличающими заявляемое устройство от прототипа, заявляемое решение

5 соответствует критерию существенные отличия.

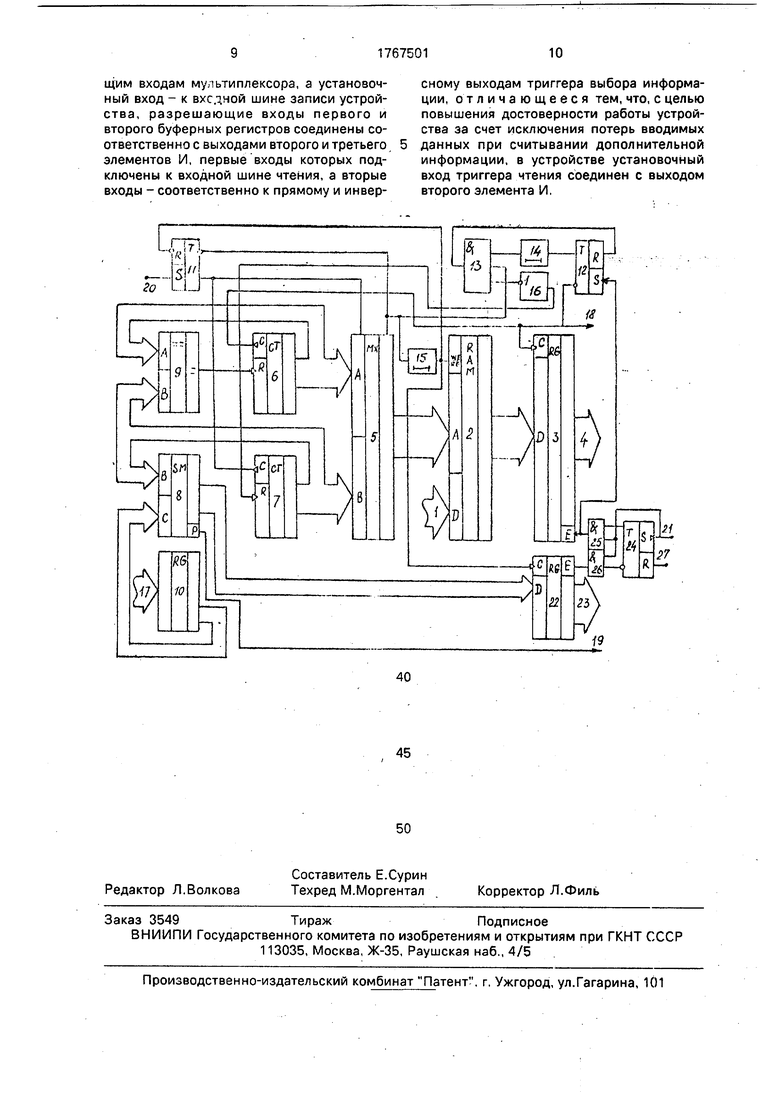

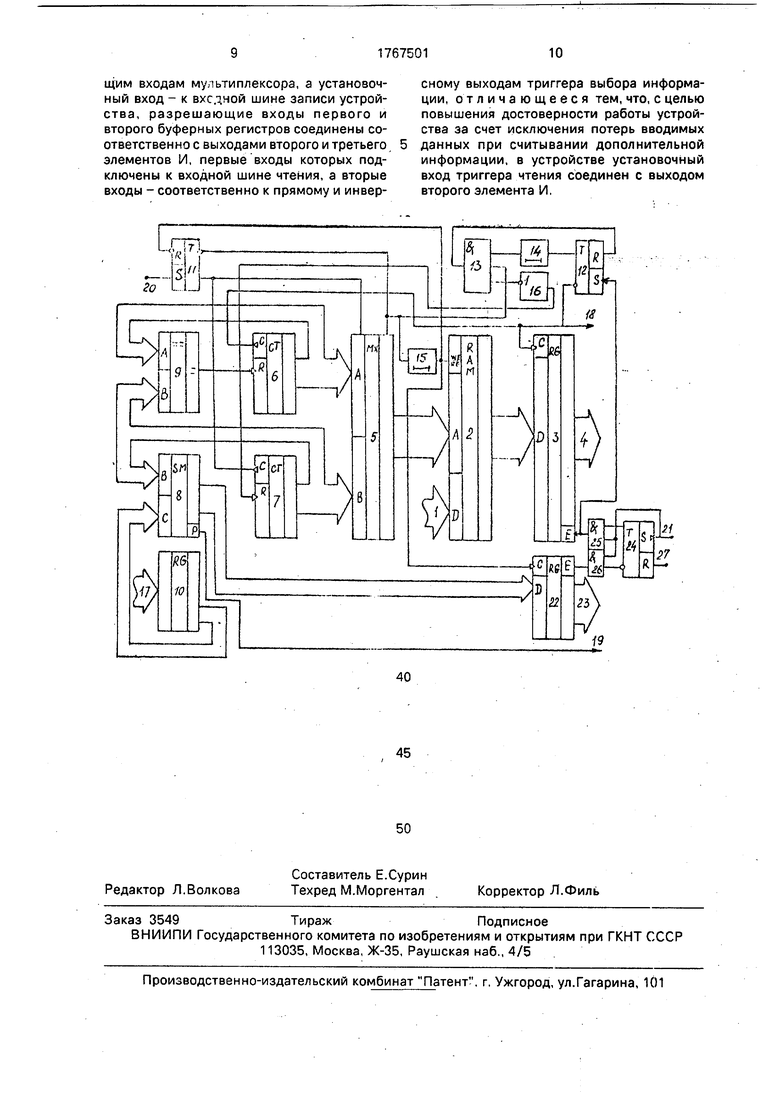

На чертеже изображена функциональная схема предложенного устройств.

Устройство содержит информационные

0 входы 1, блок 2 памяти, первый буферный регистр 3, выходные шины 4 мультиплексор 5, счетчик 6 чтения, счетчик 7 записи, сумматор 8, схему 9 сравнения, регистр 10 уставки, триггер 11 записи, триггер 12 чтения,

5 первый элемент И 13, первую 14 и вторую 15 линии (элементы) задержки, элемент НЕ 16, входные шины 17, первую 18 и вторую 19 шины готовности, шины записи 20, чтения 21. второй буферный регистр 22, выходные

0 шины 23, триггер 24 выбора информации, второй 25 и третий 26 элементы, шины 27 выбора.

Буферные регистра 3 и 22 имеют трех- стабильные выходы. Линия 14 обеспечивает

5 задержку при переходе сигнала с О в 1, а линия 15-от 1 к О.

Информационные входы 1 соединены с информационными входами блока 2 памяти, адресные входы которого связаны с выхода- ми мультиплексора 5, а выходы - о информационными входами первого буферного регистра 3. Выходные шины буферных регистров 3 и 22 объединены поразрядно и подключены к входным шинам интерфейса процессора. Входы управления подключением выходов буферных регистров 3 и 22 подключены к выходам второго 25 и третьего 26 элементов И соответственно. Первые информационные входы мультиплексора 5 соединены с первыми входами схемы 9 сравнения и выходами счетчика 6 чтения. Выход схемы 9 сравнения подключен к входам установи в ноль счетчиков 6, 7 и к входу элемента НЕ 16, выход которого подключен к третьему входу элемента И 13. Вторые информационные входы мультиплексора 5 соединены с вторыми входами схемы 9 сравнения, сумматора 8 и выходами счетчика 7 записи. Первые входы сумматора 8 подключены к выходам регистра 10 уставки, входы последнего через входные шины 17 подключены к выходным шинам интерфейса процессора. Выходы сумматора 8 соединены с информационными входами второго буферного регистра 22, причем выход переноса сумматора подключен к второй шине 19 готовности. S-вход триггера 11 записи связан с шиной 20 записи устройства. Выходы триггера 11 соединены с управляющими входами мультиплексора 5, причем прямой выход триггера 11 соединен также со счетным входом счетчика 7 записи, а инверсный-с первым входом первого элемента И 13 и через вторую линию 15 задержки подключен к управляющему входу блока 2 памяти, входу занесения второго буферного регистра 22 и R-входу триггера 11 записи. S-вход триггера 12 чтения соединен с выходом второго элемента И 25, S-вход триггера 24 выбора информации связан с вторыми входами элементов И 25, 26 и шиной 21. Прямой выход триггера 12 чтения через линию 14 задержки соединен с вторым входом первого элемента И 13, выход которого подключен к R-входу триггера 12, инверсный выход последнего подключен к первой шине 18 готовности, входу занесения первого буферного регистра 3, счетному входу счетчика 6 чтения. Прямой выход триггера 24 соединен с первым входом второго элемента И 25, инверсный-с первым входомтреть- его элемента И 26, а R-вход - с шиной 27 выбора.

Устройство работает следующим образом.

В исходном состоянии счетчики 6 и 7 и триггер 11 находятся в состоянии О, триггеры 12 и 24 - в состоянии 1, выходы регистров 3, 22 находятся в третьем состоянии, т. е. отключены от шин интерфейса

процессора. Логический элемент И 13 заперт логическим нулем с элемента НЕ 16. Мультиплексор 5 подключен на направление счетчика 6 чтения. В регистр 10 уставки

занесен из процессора дополнительный код глубины заполнения блока 2 памяти. На шинах 18 и 19 готовности логический ноль. Вторая шина 19 готовности включена в систему прерывания процессора.

0 При поступлении на вход устройства 1 первого информационного слова синхроимпульс его сопровождения поступает на шину 20 записи устройства и устанавливает триггер 11 записи в состояние 1. Триггер

5 11 переключает мультиплексор 5 на направление счетчика 7 записи и через вторую линию 15 задержки подает команду записи на управляющий вход блока 2 памяти, а затем устанавливает себя (триггер 11) в исходное

0 состояние О. Элемент И 13, находящийся в цепи чтения, на время операции записи блокируется сигналом с инверсного выхода триггера 11 записи. Задний фронт сигнала с прямого выхода триггера 11 поступает на

5 счетный вход счетчика 7 записи, наращивает его состояние на единицу, подготавливая тем самым следующий адрес. Передний фронт сигнала с инверсного выхода триггера 11 через линию 15 задержки поступает на

0 вход занесения регистра 22 и тем самым в регистр с выхода сумматора 8 переписывается код числа свободных ячеек в блок 2 памяти. Вследствие наличия разных кодов на входах схемы 9 сравнения на ее выходе

5 появится логический ноль, который через элемент 16 НЕ откроет элемент И 13, сигнал с выхода последнего установит в ноль триггер 12 чтения. Передний фронт сигнала с инверсного выхода триггера 12 чтения по0 ступит на вход занесения буферного регистра 3 и информация из блока 2 памяти перепишется в регистр 3, при этом на первой шине 18 готовности появится логическая единица, сообщая процессору о

5 наличии информации в устройстве. Второе и последующие информационные слова, поступающие на вход устройства, числом не более, чем задано в регистре 10 уставки, будут обработаны устройством аналогич0 ным образом. В этот период процессор, если он освободился от решения других задач, анализирует состояние первой шины 18 готовности и в случае наличия логической единицы на последней процессор выдает по

5 шине 21 чтения импульс приема, который устанавливает триггер 12 чтения в состояние 1, а состояние 1 триггера 24 подтверждает, при этом импульс проходит через открытый логической единицей с прямого выхода триггера 24 элемент И 25 на

S-вход триггера 12 и на управляющий вход регистра 3, подключая последний на время действия импульса к входным шинам интерфейса процессора, который считываете них информацию. Прямой выход триггера 12 чтения через первую линию 14 задержки выставляет запрос на выход очередного слова из блока 2 памяти в буферный регистр 3, а инверсный выход триггера 12 передним фронтом сигнала модифицирует счетчик 6. Если в блоке 2 памяти есть хоть одно слово и в этот момент не идет операция записи, т. е. триггер 11 записи находится в состоянии О, то сигнал с выхода элемента И 13 сбрасывает в ноль триггер 12 чтения, который тем самым заносит очередное слово из блока 2 памяти в буферный регистр 3.

При съеме последнего слова с буферного регистра 3 код счетчика 6 чтения совпадает с кодом счетчика 7 записи и на выходе схемы 9 сравнения появится сигнал равенства, который своим передним фронтом установит в ноль счетчики 6 и 7 и через элемент НЕ 16 заблокирует элемент И 13. Триггер 12 чтения останется в состоянии 1, а первая шина 18 готовности - в состоянии О.

Если процессор занят решением других задач и не анализирует состояние первой шины 18 готовности, то при заполнении блока 2 памяти до уровня, заданного в регистре 10 уставки, на выходе переноса сумматора 8, который вычитает из кода счетчика 7 записи код, хранящийся в регистре 10 уставки, возникает логическая единица, которая по второй шине 19 готовности поступает в систему прерываний процессора и вызывает на выполнение программу приема из устройства. Последняя, как было описано выше, считывает информацию из устройства до конца. Если процессору необходимо знать, через какой интервал времени заполнится блок 2 памяти устройства и появится сигнал прерывания, что необходимо перед запуском программы, прерывание которой запрещено, то процессор выдает импульс по шине 27 выбора и устанавливает триггер 24 в состояние О, логическая единица с инверсного выхода триггера 24 открывает элемент И 26, а логический ноль с прямого выхода триггера 24 блокирует элемент И 25. Таким образом, при поступлении на шину 21 импульса приема к входным шинам интерфейса процессора будет подключен второй буферный регистр 22 и в процессор поступит код числа свободных ячеек блока 2 памяти устройства.

При этом вследствие блокировки элемента И 25 исключается возможность поступления синхроимпульса приема на

S-вход триггера чтения и вывода очередного слова данных в первый буферный регистр, в котором хранится предыдущее еще не считанное процессором слово данных. Применение данного технического решения позволяет исключить потери вводимых данных при считывании дополнительной информации.

Ф о р м у л а и з о б р е т е н и я

Устройство для сопряжения источника информации с процессором, содержащее триггер записи и триггер чтения, прямые выходы которых соединены соответственно

со счетным входом счетчика записи и входом первого элемента задержки, схему сравнения и мультиплексор, первые информационные входы которых соединены с выходом счетчика чтения, счетным входом

соединенного с инверсным выходом триггера чтения, первой выходной шиной готовности устройства и входом занесения первого буферного регистра, элемент НЕ, второй буферный регистр, сумматор, регистр уставки,

блок памяти, три элемента И и триггер выбора информации, входы сброса и установи которого соединены соответственно с входными шинами выбора информации и чтения устройства, выходы первого и второго буфарных регистров образуют выходную информационную шину устройства, а их информационные входы подключены соответственно к выходу блока памяти и информационному выходу сумматора, выход

переноса которого является второй выходной шиной готовности устройства, вторые информационные входы схемы сравнения и мультиплексора соединены с выходом счетчика записи и первым информационным

входом сумматора, вторым информационным входом соединенного через регистр уставки с входной шиной задания глубины заполнения памяти, адресный и информационный входы блока памяти соединены соответственно с выходом мультиплексора и входной информационной шиной устройства, вход сброса триггера чтения соединен с выходом первого элемента И, первый, второй и третий входы которого подключены

соответственно к инверсному выходу триггера записи и выходам первого элемента задержки и элемента НЕ, входом соединенного с выходом схемы сравнения и входами сброса счетчиков чтения и записи, вход занесения второго буферного регистра соединен с управляющим входом блока памяти, входом сброса триггера записи и через второй элемент задержки с инверсным выходом триггера записи, прямой и инверсный выходы которого подключены к управляющим входам мультиплексора, а установочный вход - к входной шине записи устройства, разрешающие входы первого и второго буферных регистров соединены соответственно с выходами второго и третьего элементов И, первые входы которых подключены к входной шине чтения, а вторые входы - соответственно к прямому и инверсному выходам триггера выбора информации, отличающееся тем, что, с целью повышения достоверности работы устройства за счет исключения потерь вводимых данных при считывании дополнительной информации, в устройстве установочный вход триггера чтения соединен с выходом второго элемента И,

| Устройство для сопряжения источника информации с процессором | 1988 |

|

SU1571601A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника информации с процессором | 1989 |

|

SU1689958A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-10-07—Публикация

1990-05-21—Подача