Предлагаемое изобретение относится к области электронной вычислительной техники, в частности к технике цифровой фильтрации, и может быть использовано при разработке цифровых фильтров.

Известен способ цифровой фильтрации сигналов [1], основанный на последовательном преобразовании (сложении) входных двоичных кодов и формировании выходного двоичного кода в виде среднего арифметического значения.

Недостаток этого способа состоит в низкой точности фильтрации и большом запаздывании выходного сигнала по отношению ко входному.

Известен цифровой фильтр [1] , содержащий комбинационное устройство, включающее в себя параллельный сумматор и множительное устройство, осуществляющие, например, формирование выходного цифрового сигнала в виде среднего арифметического значения нескольких измерений входного сигнала.

Недостаток этого фильтра состоит в низкой точности фильтрации и большом запаздывании выходного сигнала по отношению ко входному.

Наиболее близким способом цифровой фильтрации сигналов к предлагаемому является способ [2], включающий преобразование входного сигнала Х в цифровую форму Xi (i= 1, 2, 3...), сравнение преобразованного входного сигнала Xi с выходным цифровым сигналом Xi ф путем определения разностного сигнала ΔXi = Xi-X

Недостаток этого способа фильтрации состоит в сложности его реализации, так как этот способ требует проведения операций умножения и сложения многих переменных, и большом времени переходного процесса.

Наиболее близким техническим решением к предлагаемому цифровому фильтру является устройство [2] , включающее аналого-цифровой преобразователь, генератор, блоки сравнения, умножения и суммирования.

Недостаток этого цифрового фильтра состоит в сложности его реализации и большом времени переходного процесса.

Задача изобретения - упрощение способа фильтрации и цифрового фильтра и снижение времени переходного процесса.

Эта задача достигается тем, что способ цифровой фильтрации сигналов, включающий преобразование входного сигнала Х в цифровую форму Хi, сравнение преобразованного входного сигнала Xi с выходным цифровым сигналом Xi ф путем определения разностного сигнала ΔXi = Xi-X

В цифровой фильтр, содержащий аналого-цифровой преобразователь, вход запуска которого соединен с выходом генератора, дополнительно введены цифровой компаратор, первый и второй реверсивные счетчики, первый, второй, третий и четвертый элементы И, счетчик импульсов, триггер, элемент ИЛИ, второй генератор и элемент НЕ, выход которого соединен со входом параллельной записи РЕ счетчика импульсов, а вход элемента НЕ соединен со входом суммирования второго реверсивного счетчика, выходом готовности аналого-цифрового преобразователя и первым входом четвертого элемента И, выход которого подключен к первым входам первого и второго элементов И, выход первого элемента И соединен с первым входом элемента ИЛИ и входом суммирования первого реверсивного счетчика, выход второго элемента И соединен со вторым входом элемента ИЛИ и входом вычитания первого реверсивного счетчика, выходная шина которого соединена с выходной шиной цифрового фильтра и входной шиной В цифрового компаратора, входная шина А которого подключена к выходной шине аналого-цифрового преобразователя, выход А>В цифрового компаратора соединен со вторым входом первого элемента И, выход А<В цифрового компаратора соединен со вторым входом второго элемента И, при этом выход элемента ИЛИ подключен ко входу суммирования С счетчика импульсов, выход которого соединен с третьим входом элемента ИЛИ и входом вычитания второго реверсивного счетчика, выход которого подключен ко входу S установки в единицу триггера, инверсный выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго генератора, а инверсный выход третьего элемента И соединен со вторым входом четвертого элемента И.

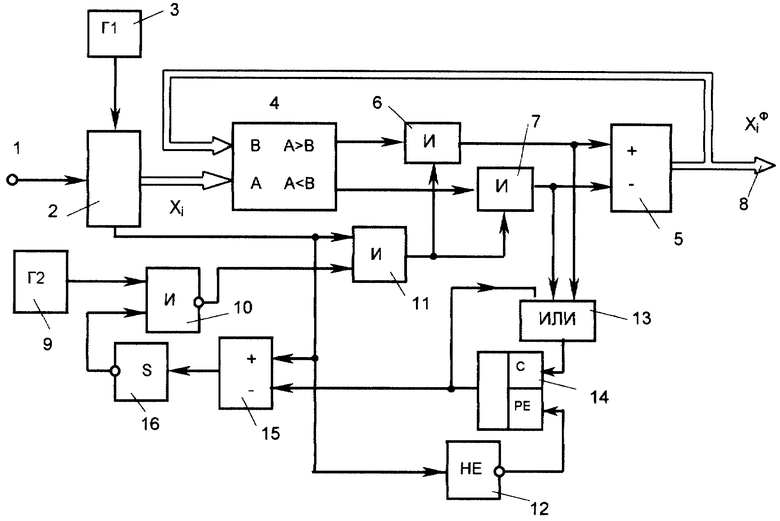

На чертеже представлена блок-схема цифрового фильтра, реализующего предлагаемый способ фильтрации сигналов. На этой схеме

1 - шина входного сигнала X,

2 - аналого-цифровой преобразователь (АЦП),

3, 9 - первый и второй генераторы, соответственно,

4 - цифровой компаратор,

5, 15 - первый и второй реверсивные счетчики, соответственно,

6, 7, 10, 11 - первый, второй, третий и четвертый элементы И, соответственно,

8 - выходная шина цифрового фильтра,

12 - элемент НЕ,

13 - элемент ИЛИ,

14 - счетчик импульсов,

16-триггер.

В цифровом фильтре шина 1 входного сигнала Х соединена со входом аналого-цифрового преобразователя 2, вход запуска которого соединен с выходом первого генератора 3, выходная кодовая шина аналого-цифрового преобразователя 2 подключена к входной шине А цифрового компаратора 4, входная шина В которого соединена с выходной кодовой шиной 8 цифрового фильтра и выходной шиной первого реверсивного счетчика 5. Суммирующий вход первого реверсивного счетчика 5 соединен с выходом первого элемента И 6 и первым входом элемента ИЛИ 13, а вычитающий вход первого реверсивного счетчика 5 соединен со вторым входом элемента ИЛИ 13 и с выходом второго элемента И 7, первый вход которого соединен с выходом четвертого элемента И 11 и первым входом первого элемента И 6, второй вход которого соединен с выходом А>В цифрового компаратора 4, выход А<В которого подключен ко второму входу второго элемента И 7. Выход готовности АЦП 2 соединен с первым входом четвертого элемента И 11, входом суммирования второго реверсивного счетчика 15 и входом элемента НЕ12, выход которого соединен со входом параллельной записи РЕ счетчика импульсов 14, суммирующий вход С которого подключен к выходу элемента ИЛИ 13, а выход соединен с третьим входом элемента ИЛИ 13 и вычитающим входом второго реверсивного счетчика 15, выход которого соединен со входом S установки в единицу триггера 16, инверсный выход которого соединен с первым входом третьего элемента И 10, второй вход которого соединен с выходом второго генератора 9. Инверсный выход третьего элемента И 10 соединен со вторым входом четвертого элемента И 11.

Цифровой фильтр работает следующим образом. Рассмотрим вначале процесс установки начального значения выходного цифрового сигнала Хi ф (0). Пусть первый генератор 3 имеет период Т следования импульсов (Т определяет частоту преобразования входного сигнала Х в цифровой код Xi), а второй генератор 9 имеет период τ следования импульсов, причем отношение T/τ≥m, где m=Xmax/Δ, Хmax - максимально возможное значение входного сигнала Х, Δ- - цена единицы младшего разряда цифрового кода Xi. Предполагаем, что в исходном состоянии первый реверсивный счетчик 5 обнулен, второй, например, q - разрядный реверсивный счетчик 15 имеет состояние, соответствующее заданному числу r, k -разрядный счетчик импульсов 14 состояние, соответствующее заданному числу n, триггер 16 - нулевое состояние. В моменты времени iT (i= 1, 2, 3...) входной сигнал X (шина 1) преобразуется в цифровой код Xi аналого-цифровым преобразователем 2. Пусть ΔX0 - допустимое значение изменения сигнала Xi за время Т. Тогда число n определяется в виде

n=2k-n1, n1 = ΔX0/Δ. (1)

Иначе, число n соответствует такому состоянию счетчика импульсов 14, переполнение которого происходит после поступления на его вход n1, импульсов.

Число r выбирается из условия, что разностный сигнал ΔXi = Xi-X

r=2q-р, р=2. (2)

Иначе, число r соответствует такому состоянию второго реверсивного счетчика 15, переполнение которого произойдет после поступления на его суммирующий вход подряд не менее р (двух) импульсов при отсутствии импульсов на его вычитающем входе.

Пусть на входную шину 1 поступает сигнал Х в виде (3)

X=a+bt, a=0,5, b=0,05 с-1. (3)

Предположим, что период Т первого генератора 3 равен 0, 01 с, период τ второго генератора 9 равен 10-5 с. Пусть АЦП 2 имеет S разрядов (S=10) и его максимальный сигнал (Xi)max (все единицы во всех разрядах, кроме знакового) соответствует максимальному значению Х (например, 1,0). Тогда цена единицы младшего разряда Δ (заданное значение) равна ≅10-3 Δ ≅ 10-3.

Рассмотрим процесс установки начального значения Хi ф (0) в первом реверсивном счетчике 5. Пусть допустимое значение ΔX0 = 8Δ (n1=8), число разрядов счетчика импульсов 14 k=4, число р=2, число разрядов второго реверсивного счетчика 15 q=2. Тогда число n, устанавливаемое в исходном состоянии в счетчик импульсов 14 согласно (1) равно 8, число r, устанавливаемое в исходном состоянии во второй реверсивный счетчик 15 согласно (2) равно 2. При i=1 (t=Т) на выходе АЦП 2 устанавливается код Xi, соответствующий числу 0,5 (см. (4)). Выходной код Xi ф в первом реверсивном счетчике 5 равен нулевому значению. После того как АЦП 2 сформирует сигнал готовности G=1 (высокий уровень) этот сигнал поступает на суммирующий вход второго реверсивного счетчика 15, изменяя его состояние на +1, и дает разрешение на прохождение сигналов с выхода второго генератора 9 через третий элемент И 10, на втором входе которого присутствует сигнал высокого уровня с инверсного выхода триггера 16, который находится в состоянии "0". Импульсы с выхода четвертого элемента И 11 поступают на первые входы первого 6 и второго 7 элементов И. Сигнал Xi на входе А цифрового компаратора 4 превышает сигнал Xi ф на входе В этого компаратора, т.е. на выходе А>В цифрового компаратора 4 формируется сигнал высокого уровня, который разрешает прохождение импульсов с выхода четвертого элемента И 11 через первый элемент И 6 на суммирующий вход первого реверсивного счетчика 5 и через элемент ИЛИ 13 на суммирующий вход С счетчика импульсов 14. Импульсы со второго генератора 9 будут проходить через первый элемент И 6 до тех пор, пока на выходе А>В цифрового компаратора 4 будет присутствовать высокий уровень. Низкий уровень на этом выходе появится тогда, когда Xi=Xi ф (А=В) и счет импульсов прекратится. Таким образом, на выходе первого реверсивного счетчика 5 в течение первого интервала времени Т устанавливается значение Xi ф=Xi=0,5. Так как число импульсов Ii с выхода элемента ИЛИ 13 превышает число n1=8 (Xi-Xi ф=0,5=500Δ), происходит переполнение счетчика импульсов 14 и на его выходе устанавливается высокий уровень, который запрещает прохождение импульсов с выхода элемента ИЛИ 13 (высокий уровень на его третьем входе) и производит вычитание "единицы" из кодового состояния второго реверсивного счетчика 15, который устанавливается в исходное состояние (n=8).

При i= 2 в начальный момент снимается сигнал готовности АЦП 2 (G=0), который с выхода элемента НЕ 12 (высокий уровень) подается на вход параллельной записи РЕ счетчика импульсов 14 и в этом счетчике импульсов по переднему фронту устанавливается исходное состояние (n=8). После формирования сигнала готовности G=1 АЦП 2 процесс повторяется с той лишь разницей, что при i= 2 Xi = Xi-1+Δ, Xi-X

Считаем, что в момент времени t=0 выходной код Xi ф первого реверсивного счетчика 5 соответствует значению Xi ф (0)= Х(0)=0,5 (см. выражение (4)). При i= 1 значение Xi= 0,5, так как значение ΔXi = Xi-Xi-1<Δ. Выходной сигнал цифрового фильтра Xi ф остается неизменным и равен Xi ф (0). При i=2 значение сигнала Xi= 0,501 (0,5+Δ), Xi ф=0,5. В момент формирования аналого-цифровым преобразователем 2 сигнала готовности G=1 на выходе цифрового компаратора 4 формируется сигнал А>В, так как на первой входной шине А сигнал равен Xi= 0,501, а на второй входной шине В сигнал равен Xi ф=0,5. Так как Xi>Xi ф(А>В), то выходной сигнал цифрового компаратора 4 А>В имеет высокий уровень и на выходе первого элемента И 6 появляется также высокий уровень, который поступает на суммирующий вход первого реверсивного счетчика 5, изменяя его код на +1, а его выходной сигнал Xi ф=0,501.

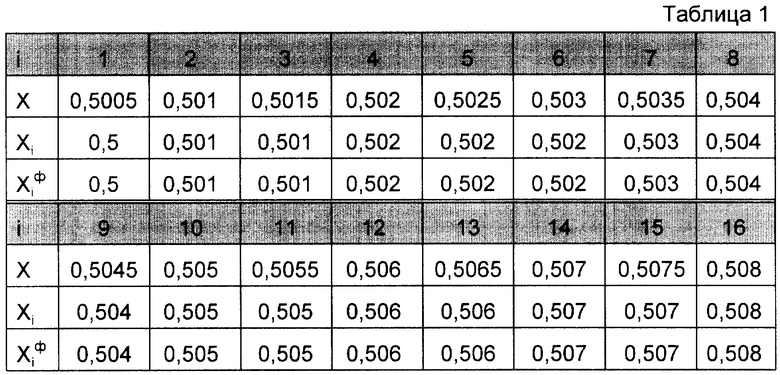

Аналогично работает схема и при других значениях i=3, 4, 5... В случае выполнения условия Xi<Xi ф при некоторых значениях i на выходе цифрового компаратора 4 формируется сигнал А<В высокого уровня и при наличии сигнала готовности G= 1 (высокий уровень) АЦП 2 выходной сигнал второго элемента И 7 также будет высокого уровня. Этот сигнал поступает на вычитающий вход реверсивного счетчика 5 и изменяет его выходной код на минус единицу. Результат цифровой фильтрации приведен в графе Xi ф табл.1. По сравнению со значениями входного сигнала Х выходные значения Xi ф цифрового фильтра отличаются на заданную малую величину Δ. В графах Xi и Xi ф даны значения сигналов в моменты времени iT.

Таким образом, в рассматриваемом цифровом фильтре производится сравнение входного сигнала Xi и сигнала Xi ф путем определения разностного сигнала ΔXi = Xi-X

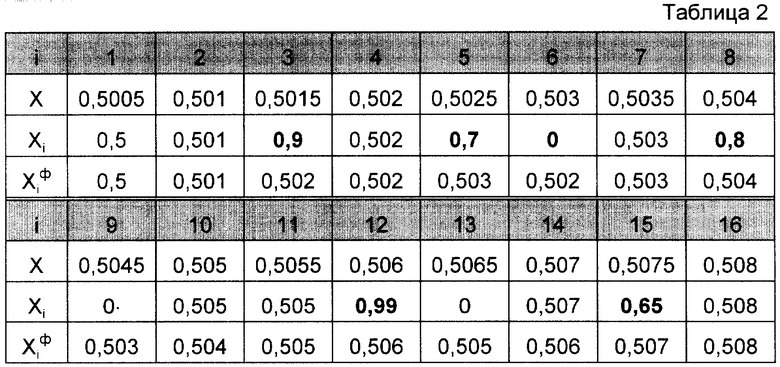

Оценим работоспособность цифрового фильтра в условиях действия помех. Будем считать, что в некоторые моменты времени iT на входе аналого-цифрового преобразователя 2 кроме полезного сигнала Х присутствует сигнал помехи, искажающий цифровой код Xi. Результаты отобразим в табл.2.

Как видно из табл.2 заведомо ложные значения Xi при i=3, 5, 6, 8, 9, 12, 13, 15 не приводят к существенному изменению выходных значений Xi ф (табл.2) по отношению к истинным значениям полезного сигнала Xi (табл.1). Эти изменения не превышают малой заданной величины Δ для любого момента времени iT несмотря на то, что 8 измерений из 16 заведомо ложны, и что свидетельствует о высокой степени фильтрации рассматриваемого цифрового фильтра.

По сравнению с прототипом [2] предлагаемый способ фильтрации и цифровой фильтр, реализующий этот способ, значительно проще известных решений, так как предлагаемый способ не требуют операций многократного умножения и суммирования многих переменных, а цифровой фильтр не требует соответственно блоков умножения и суммирования. Кроме того, предлагаемый цифровой фильтр по сравнению, например, с прототипом [2] имеет значительно меньшее время переходного процесса. Оценку проведем по отношению к схеме [3], являющейся одним из вариантов прототипа [2] и реализующей известный алгоритм фильтрации (4)

Xi ф=(k/k-1)Xi-1 ф+Xi/k (4)

где k - некоторый коэффициент. Например, при k = 10 время переходного процесса ТП, в течение которого Xi-Xi ф≤0,01Xi, составляет примерно 50Т. Например, при n1= 8, р= 2 время переходного процесса не превышает 10 Т, что значительно меньше времени переходного процесса известного устройства.

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации цифрового фильтра можно использовать аналого-цифровой преобразователь типа К1108 ПВ1, цифровой компаратор типа 564 ИП2, реверсивный счетчик, триггер, счетчик импульсов, элементы И и ИЛИ серии 564.

Литература

1. Л. М. Гольденберг, Ю.Т. Бутыльский, М.Н. Поляк. "Цифровые устройства на интегральных схемах в технике связи".- Москва: "Связь", 1979 г., стр. 135, рис.5.10.а.

2. Л. Т. Кузин, "Расчет и проектирование дискретных систем управления", Государственное научно-производственное издательство машиностроительной литературы, Москва, 1962 г. Фиг.70, стр. 115 (прототип).

3. Л. М. Гольденберг, Ю.Т. Бутыльский, М.Н. Поляк. "Цифровые устройства на интегральных схемах в техники связи".- Москва: "Связь", 1979 г., стр. 124, рис.5.3.в.

Изобретение относится к области электронной вычислительной техники, в частности к технике цифровой фильтрации, и может быть использовано при разработке цифровых фильтров высокой точности. Способ цифровой фильтрации позволяет выделить полезный сигнал в условиях действия помех и может быть реализован в цифровом фильтре, содержащем аналого-цифровой преобразователь, первый и второй реверсивные счетчики, цифровой компаратор, триггер, элементы И и ИЛИ. Цифровой фильтр имеет простую структуру и высокую степень фильтрации. Цифровой фильтр может быть реализован на простых стандартных элементах, вследствие чего имеет высокую надежность. Технический эффект, достигаемый при его реализации, состоит в повышении точности фильтрации и сокращении времени запаздывания выходного сигнала по отношению к входному сигналу. 2 с. п. ф-лы, 1 ил., 2 табл.

τ≤T•Xmax/Δ,

где Хmaх - максимально возможное значение входного сигнала X.

| ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2083054C1 |

| US 4340875, 20.07.1982 | |||

| ВСЕСОЮЗНАЯ ^ | 0 |

|

SU372440A1 |

| ПРОБКА ДЛЯ КОНТЕЙНЕРА КОРОБОЧНОГО ТИПА С ДОСТУПОМ ВОЗДУХА | 2015 |

|

RU2710473C1 |

| DE 19712790 А1, 30.10.1997. | |||

Авторы

Даты

2002-08-20—Публикация

2000-06-19—Подача