Изобретение относится к области вычислительной техники и предназначено для выполнения операции приема и преобразования самосинхронизирующегося последовательного двоичного кода, принадлежащего ряду длин, в параллельно-последовательный код с выдачей байтами в сопровождении кода номера байта и сигналов готовности и синхронизации байта, а также формирования сигналов контроля функционирования (информационной ошибки (или сбоя) при четном числе единиц в принятом коде и сбоя битовой синхронизации при отклонении разрядности входного кода от выбранного ряда длин) и готовности результата (окончания операции) с помощью обнаружения паузы с программируемым порогом и может быть использовано при построении устройств для ввода информации типа [1] и контроллеров локальной сети (КЛС), например, КЛС на основе ГОСТ 18977-79 и РТМ 1495-75 по протоколам, которые являются правилами обмена информацией [1, с. 57-64] между станциями локальной сети (СЛС) по мультиплексной и/или раздельным линиям связи сообщениями (последовательными двоичными кодами в ряде длин { 16 бит, 24 бит, 32 бит} младшими разрядами (битами) вперед и старшим разрядом контроля четности количества единиц в младших разрядах), разделенных между собою паузами длительностью (4-40) периодов Т частоты следования импульсов битовой синхронизации передачи сообщения.

В составе современной СЛС можно выделить (см., например, в [2] на с. 221 рис. 5.9) ядро (содержит процессор или однокристальную электронную вычислительную машину (ЭВМ), схему синхронизации и начальной установки и комбинированную память (в общем случае содержит ОЗУ - оперативное запоминающее устройство, ДОЗУ - двухпортовое ОЗУ, ПЗУ2 - постоянное запоминающее устройство и РПЗУ - репрограммируемое ПЗУ)), КЛС (содержит устройство для ввода информации типа [1], устройство для вывода информации и устройство управления обменом (УУО) и синхронизацией (блок связи с подсистемой) для взаимосинхронизации и управления КЛС в целом), функционально ориентированные устройства для ввода-вывода информации в процессе взаимодействия СЛС с внешними объектами (пультом оператора, смежными системами, исполнительными устройствами, датчиками событий в объектах управления и т.п.), блок питания и системную магистраль (Q-BUS или ISA или VME, либо другую) для обмена информацией между составными частями СЛС под управлением ЭВМ.

Для рационального распределения в СЛС функций между аппаратно-программными средствами устройство для ввода информации и устройство для вывода информации (как составные части КЛС, входящего в СЛС) должны с помощью УУО гибко управляться от ЭВМ и быть максимально инвариантными как к типу системной магистрали, так и протоколам локальной сети, т.е. при совершенствовании и специализации КЛС основной варьируемой частью должно быть УУО.

В устройствах для ввода информации типа [1] каждой операции приема и преобразования сообщения должна предшествовать процедура обнаружения паузы для подготовки устройства к выполнению очередной операции, а процесс выполнения каждой операции следует контролировать, например формировать сигналы информационной ошибки (или сбоя) при четном числе единиц в принятом коде и сбоя битовой синхронизации при отклонении разрядности входного кода от выбранного ряда длин.

В этой связи создание простого устройства для ввода информации с широкими функциональными возможностями, обеспечивающими гибкую управляемость от ЭВМ при максимальной независимости от типа системной магистрали и способов обмена информацией между ЭВМ и составными частями КЛС, представляет, на наш взгляд актуальную техническую задачу, решение которой позволит повысить качество разрабатываемых КЛС, в том числе и устройств типа [1], поддерживающих в локальной сети при минимальных аппаратурных затратах высокую достоверность функционирования при обмене самосинхронизирующимися последовательными двоичными кодами в выбранном ряде длин, например, в битовом ряде {8, 16, 24, 32} .

Достоверность функционирования - свойство цифрового устройства, характеризующее способность средств контроля признать выходной результат работы устройства правильным или ошибочным с помощью аппаратно-программных средств контроля [3, с. 6] , обеспечивающих его контролепригодность. Контролепригодность - свойство устройства, обуславливающее приспособленность контроля его технического состояния в процессе изготовления и эксплуатации [3, с. 153]. Именно контролепригодность дает возможность получить на практике необходимую достоверность систем передачи, обработки информации и управления [4, с. 12], которые в современной аппаратуре являются также абонентами (станциями) локальных сетей.

В локальных сетях в качестве самосинхронизирующихся кодов наиболее часто используются манчестерский код и код RZ [5, с. 30-36].

Основным недостатком известных устройств [6-8] для применения их в современном КЛС является узкая специализация или ограниченность их функциональных возможностей.

Так устройство [6], содержащее генератор импульсов, информационный регистр, блок формирования сдвигов и блок выдачи кода, устройство [7], содержащее блоки буферной памяти, счетчик, мультиплексор, дешифратор, регистр сдвига, триггер, генератор импульсов и элементы И, специализированы узко так, что первое из них выполняет функцию преобразования содержимого информационного регистра в последовательный двухразрядный код, соответствующий каждому биту информационного регистра, второе - выполняет функцию последовательного переноса содержимого каждого из блоков буферной памяти в сдвиговый регистр для передачи в ЭВМ, а многоканальное устройство [8] для приема и преобразования самосинхронизирующихся последовательных двоичных кодов при значительной сложности (содержит многоканальный коммутатор-приемник сигналов входных кодов, генератор импульсов, управляемый делитель частоты, три регистра сдвига, пять регистров, декодер, счетчик, триггер и элемент И-НЕ) обладает ограниченными функциональными возможностями, поскольку работает с кодами фиксированной длины без встроенных средств контроля функционирования.

Из известных технических решений наиболее близким к предлагаемому является устройство для ввода информации [1], содержащее приемник-декодер самосинхронизирующегося кода (образован демодулятором и формирователем одиночных импульсов), обнаружитель паузы, выполненный как специализированный счетчик, (n+1)-разрядный регистр сдвига, формирующий сигнал готовности результата операции по окончании каждого n-го сдвигового импульса битовой синхронизации, отсчитываемого после обнаружения паузы (где n=32 - длина принимаемого кода в битах), дешифратор адреса, выходы информационной и выходы управляющей группы, соединенные соответственно с информационной группой выходов регистра сдвига и выходами дешифратора, стробирующий вход которого соединен с выходом младшего (нулевого) разряда регистра сдвига, являющегося выходом готовности результата операции устройства, адресная группа выходов регистра сдвига соединена с информационными входами дешифратора, тактовый вход и входы самосинхронизирующегося последовательного двоичного кода, соединенные с информационными входами приемника-декодера, выход сигнала последовательного двоичного кода которого соединен с информационным входом регистра сдвига, тактовый вход которого соединен с выходом генератора одиночных импульсов, тактовый вход устройства соединен с тактовыми входами генератора одиночных импульсов и обнаружителя паузы, другие входы которых соединены с выходом сдвиговых импульсов битовой синхронизации демодулятора, а первый и второй выходы обнаружителя соединены соответственно с входами установки регистра сдвига в режим преобразования и начальное состояние (старший разряд в "1", а остальные разряды в "0").

Устройство [1] работает следующим образом. По входным сигналам самосинхронизирующегося последовательного двоичного кода RZ приемник-декодер формирует сигнал последовательного двоичного кода и две последовательности импульсов сдвига битовой синхронизации: узкие, привязанные формирователем к тактовым импульсам, по которым регистр сдвига принимает последовательный двоичный код, и широкие, устанавливающие обнаружитель паузы в режим обнаружения.

В каждом четвертом периоде Тn=4Т (где Т - период частоты следования импульсов сдвига битовой синхронизации) паузы обнаружитель вырабатывает с перекрытием во времени широкий импульс установки регистра сдвига в режим преобразования и узкий импульс установки регистра сдвига в начальное состояние "10. . . 0". По окончании этих импульсов регистр сдвига готов к выполнению очередной операции преобразования, которая начинается с поступлением на него сигнала последовательного двоичного кода и последовательности F узких сдвиговых импульсов битовой синхронизации, число которых должно быть всегда равным длине преобразования n=32. При поступлении последовательная информация передается с сдвигом вправо в регистр сдвига по последовательности F узких сдвиговых импульсов битовой синхронизации. После окончания 32-го импульса (n+1)-разрядный сдвиговый регистр заполняется и переходит в режим хранения, что отмечается установкой его младшего разряда, выставляющего сигнал готовности результата, совпадающего началом с паузой, длительность которой Тn= 4Т. По сигналу готовности дешифратор активизирует одну из линий управляющей группы выходов, по сигналу которой абонент (приемник) системы снимает информацию с информационной группы выходов устройства. В четвертом такте паузы обнаружитель паузы формирует импульсы установки режима преобразования и начального состояния, по которым регистр сдвига переходит в начальное состояние режима преобразования и снимает сигнал готовности результата операции, длительность Т1г которого определяется выражением

3Т<Т1г<4Т. (1)

Если в процессе выполнения операции приема и преобразования происходит сбой, например отклонение битовой синхронизации от длины n=32 в сторону уменьшения при F<n или увеличения при F>n, то сигнал готовности результата в первом случае не вырабатывается (регистр сдвига не заполняется), а во втором случае выставляется, и может произойти съем абонентом некорректной информации. Кроме того, при F=n может быть принята информация с ошибкой, которая также снимется абонентом. Таким образом, в двух случаях их трех возможных может произойти ввод ошибочной информации.

Основным недостатком устройства [1] является ограниченность области его применения, что обусловлено как ограниченностью его функциональных возможностей (отсутствует возможность ввода входного кода в ряде длин, например, в битовом ряде { n} ={8, 16, 24, 32} и контроля его функционирования), так и тем, что в современных КЛС функция передачи вводимой информации абоненту принадлежит не устройству ввода, а осуществляется УУО под управлением ЭВМ.

Предлагаемым изобретением решается задача расширения области использования устройства за счет обеспечения возможности приема и преобразования входных кодов в ряде длин с выдачей байтами в параллельно-последовательном коде в сопровождении кода номера байта и сигналов готовности байта и его синхронизации, а также формирования сигналов контроля функционирования устройства (информационной ошибки при четном числе единиц в принятом коде и сбоя битовой синхронизации при отклонении разрядности входного кода от установленного ряда {n} длин принимаемых кодов) и формирования сигнала готовности результата с помощью обнаружения паузы с программируемым порогом.

Для достижения этого технического результата в устройство для ввода информации, содержащее приемник-декодер, регистр сдвига, обнаружитель паузы, выход готовности результата операции, входы самосинхронизирующегося последовательного двоичного кода, являющиеся информационными входами приемника-декодера, выход последовательного двоичного кода которого соединен с информационным входом регистра сдвига, и тактовый вход, соединенный с тактовыми входами приемника-декодера и обнаружителя паузы, введены элемент контроля по модулю два, два триггера, (4+q)-paзpядный суммирующий счетчик, блок управления, вход начального сброса, соединенный с входом установки обнаружителя паузы в состояние паузы и первым входом сброса блока управления.

Вход сброса готовности результата, соединенный с вторым входом сброса блока управления, первый выход которого соединен с счетным входом суммирующего счетчика и тактовым входом регистра сдвига, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя паузы, байтовый выход параллельно-последовательного кода результата операции, соединенный с кодовым выходом регистра сдвига и кодовым входом элемента контроля по модулю два, битовый вход которого соединен с выходом первого триггера, выход синхроимпульсов параллельно-последовательного кода результата операции, соединенный с вторым выходом блока управления и тактовыми входами первого и второго триггеров.

Выход готовности байта результата операции является третьим выходом блока управления, четвертый выход которого является выходом готовности результата операции, выход сигнала сбоя битовой синхронизации, являющийся пятым выходом блока управления, выход сигнала информационной ошибки результата операции, являющийся выходом второго триггера, и q-разрядный выход кода номера байта параллельно-последовательного кода результата операции (где q определяет количество байтов в результате операции, входящее в ряд от одного байта до двух в степени q включительно), являющийся кодовым выходом блока управления, первый импульсный вход которого соединен с выходом импульсов битовой синхронизации приемника-декодера и входом установки обнаружителя паузы в режим обнаружения, выход элемента контроля по модулю два соединен с информационными входами первого и второго триггеров, асинхронные инверсные входы сброса первого триггера и сброса и установки второго триггера соединены с шиной логической 1 устройства, кодовый вход блока управления связан через суммирующий счетчик с входом кода константы устройства, у которого старший и три младших разряда нули, а остальные q разрядов единицы, инверсные асинхронные входы сброса регистра сдвига, установки первого триггера и записи суммирующего счетчика соединены с первым выходом обнаружителя паузы, который содержит входы тактовый, установки в состояние паузы, установки в режим обнаружения, два выхода, первые элементы НЕ и И-НЕ, вычитающий счетчик, первый, второй и третий элементы ИЛИ и кодовый вход, который соединен с информационным входом вычитающего счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, тактовый вход обнаружителя соединен с первым входом первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ и счетным входом вычитающего счетчика, выход младшего разряда которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента И-НЕ и первым выходом обнаружителя, вход установки которого в состояние паузы соединен с входом сброса вычитающего счетчика, инверсный вход записи которого через первый элемент НЕ связан с входом установки обнаружителя в режим обнаружения паузы, выход второго элемента ИЛИ является вторым выходом обнаружителя, который соединен с вторым импульсным входом блока управления, который содержит два входа сброса, два импульсных входа, кодовые (4+q))-разрядный вход и q-разрядный выход, пять выходов, второй и третий элементы НЕ, два элемента ИЛИ-НЕ, с второго по седьмой элементы И-НЕ, четвертый и пятый элементы ИЛИ, элемент И, третий и четвертый триггеры с асинхронными инверсными входами сброса и установки, и регистр, причем входы сброса третьего и четвертого триггеров связаны через первый элемент ИЛИ-НЕ с входами сброса блока управления, первый импульсный вход которого соединен с первыми входами второго, третьего и четвертого элементов И-НЕ, остальные входы второго элемента И-НЕ соединены раздельно с входами второго элемента ИЛИ-НЕ и входами трех младших разрядов кодового входа блока управления, входы (q+1) старших разрядов которого соединены с входами пятого элемента И-НЕ, первый вход шестого элемента И-НЕ соединен с входом самого старшего разряда кодового входа блока управления, входы остальных q-старших разрядов которого связаны через регистр с кодовым выходом блока управления, второй импульсный вход которого соединен с входом установки третьего триггера и первыми входами седьмого элемента И-НЕ и четвертого элемента ИЛИ, выход второго элемента ИЛИ-НЕ соединен с вторыми входами шестого элемента И-НЕ и четвертого элемента ИЛИ, выход второго элемента И-НЕ соединен с тактовыми входами третьего и четвертого триггеров, информационные входы которых соединены с шиной логического 0 блока управления, выход пятого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ и связан через второй элемент НЕ с вторым входом четвертого элемента И-НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, первый выход блока управления соединен с выходом третьего элемента И-НЕ и первым входом пятого элемента ИЛИ, выход которого соединен с вторым входом седьмого элемента И-НЕ, выход которого соединен с вторым выходом блока управления, выход шестого элемента И-НЕ соединен с вторым входом пятого элемента ИЛИ и через третий элемент НЕ связан с третьим выходом блока управления, четвертый выход которого соединен с выходом третьего триггера и асинхронным инверсным входом записи регистра, выход элемента И соединен с входом установки четвертого триггера, выход которого является пятым выходом блока управления.

Авторам неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение элемента контроля по модулю два, двух триггеров, суммирующего счетчика, блока управления, входов начального сброса и сброса готовности результата, программируемого кодового входа порога обнаружения паузы, байтового выхода параллельно-последовательного кода результата операции и q-разрядного выхода кода номера байта результата операции, выходов сигнала информационной ошибки, синхроимпульсов параллельно-последовательного кода и сигнала готовности байта результата операции и выхода сигнала сбоя битовой синхронизации), позволяющие использовать его при построении КЛС, поддерживающих с высокой достоверностью в локальной сети обмен самосинхронизирующимися последовательными двоичными кодами с разными длинами, например, при q=2 принадлежащими ряду (множеству) байтов

М={1,2,3,4}. (2)

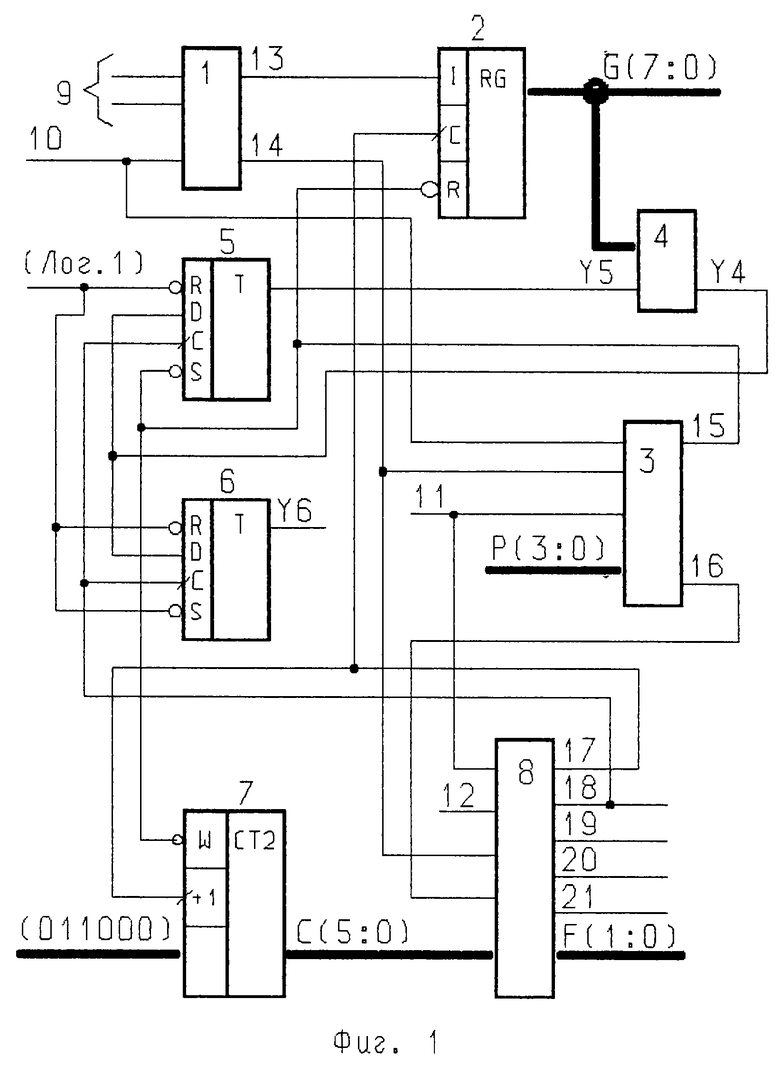

На фиг. 1-3 приведена функциональная схема устройства для ввода информации при реализации его, в частности, с использованием библиотеки элементов интегральных схем (ИС) серий типа 533 и/или 1533 для работы с кодами, длины которых соответствуют ряду (2).

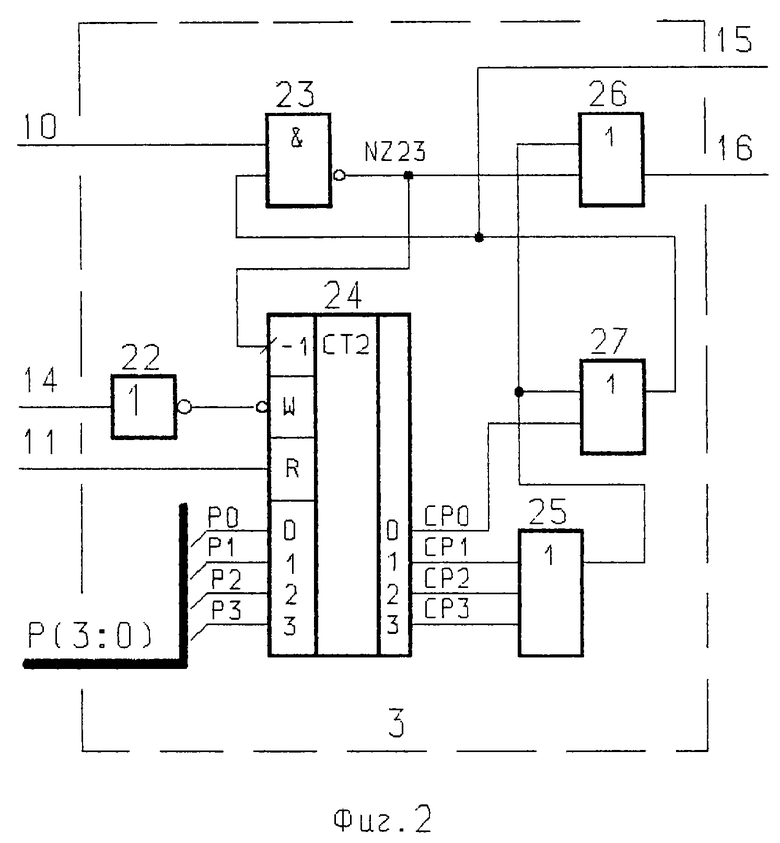

Устройство для ввода информации (фиг.1) содержит приемник-декодер 1, байтовый регистр 2 сдвига, обнаружитель 3 паузы, элемент 4 контроля по модулю два, первый 5 и второй 6 триггеры, (4+q)=6-разрядный суммирующий счетчик 7, блок 8 управления, входы 9 самосинхронизирующегося последовательного двоичного кода, являющиеся и информационными входами приемника-декодера 1, тактовый вход 10, соединенный с тактовыми входами приемника-декодера 1 и обнаружителя 3, вход 11 начального сброса, соединенный с входом установки в состояние паузы обнаружителя 3 и первым входом сброса блока 8, вход 12 сброса готовности результата, соединенный с вторым входом сброса блока в, выход 13 последовательного двоичного кода приемника-декодера 1, соединенный с информационным входом регистра 2, выход 14 импульсов битовой синхронизации приемника-декодера 1, соединенный с входом установки в режим обнаружения обнаружителя 3 и первым импульсным входом блока 6, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя 3, первый 15 и второй 16 выходы обнаружителя 3, байтовый выход параллельно-последовательного кода результата операции, соединенный с кодовым выходом регистра 2 и кодовым входом элемента 4, битовый вход которого соединен с выходом триггера 5, q=2-paзpядный выход номера байта результата операции (где q= 2 определяет количество байт в результате операции, входящее в ряд (2) от одного до четырех байт включительно), являющийся кодовым выходом блока 8, содержащего пять выходов 17-21, первый 17 выход которого соединен с тактовым входом регистра 2 и счетным входом счетчика 7, выход синхроимпульсов параллельно-последовательного кода результата операции, соединенный с тактовыми входами триггеров 5 и 6 и вторым 18 выходом блока 8, выходы готовности байта результата операции и готовности результата операции, являющиеся третьим 19 и четвертым 20 выходами блока 5 соответственно, выход сигнала сбоя битовой синхронизации, соединенный с пятым 21 выходом блока 6 и выход сигнала информационной ошибки результата операции, являющийся выходом триггера 6, асинхронные инверсные входы сброса триггера 5 и сброса и установки триггера 6 соединены с шиной логической 1 устройства, вход кода (011000) константы которого связан через счетчик 7 с кодовым входом блока в, выход элемента 4 соединен с информационными входами триггеров 5 и 6, выход 15 обнаружителя 3 соединен с асинхронными инверсными входами сброса регистра 2, установки триггера 5 и записи счетчика 7, а выход 16 обнаружителя 3 соединен с вторым импульсным входом блока 8.

Обнаружитель 3 паузы (фиг.2) содержит входы 10, 11 и 14 соответственно тактовый, установки в состояние паузы и в режим обнаружения, первый 15 и второй 16 выходы, первые элементы 22 и 23 соответственно НЕ и И-НЕ, вычитающий счетчик 24, первый 25, второй 26 и третий 27 элементы ИЛИ и кодовый вход, который соединен с информационным входом счетчика 24, выходы старших разрядов которого соединены с входами элемента 25, выход которого соединен с первыми входами элементов 26 и 27, вход 10 обнаружителя 3 соединен с первым входом элемента 23, выход которого соединен с вторым входом элемента 26 и счетным входом счетчика 24, выход младшего разряда которого соединен с вторым входом элемента 27, выход которого соединен с вторым входом элемента 23 и выходом 15 обнаружителя 3, вход 11 которого соединен с входом сброса счетчика 24, инверсный вход записи которого через элемент 22 связан с входом 14 обнаружителя 3, выход 16 которого соединен с выходом элемента 26.

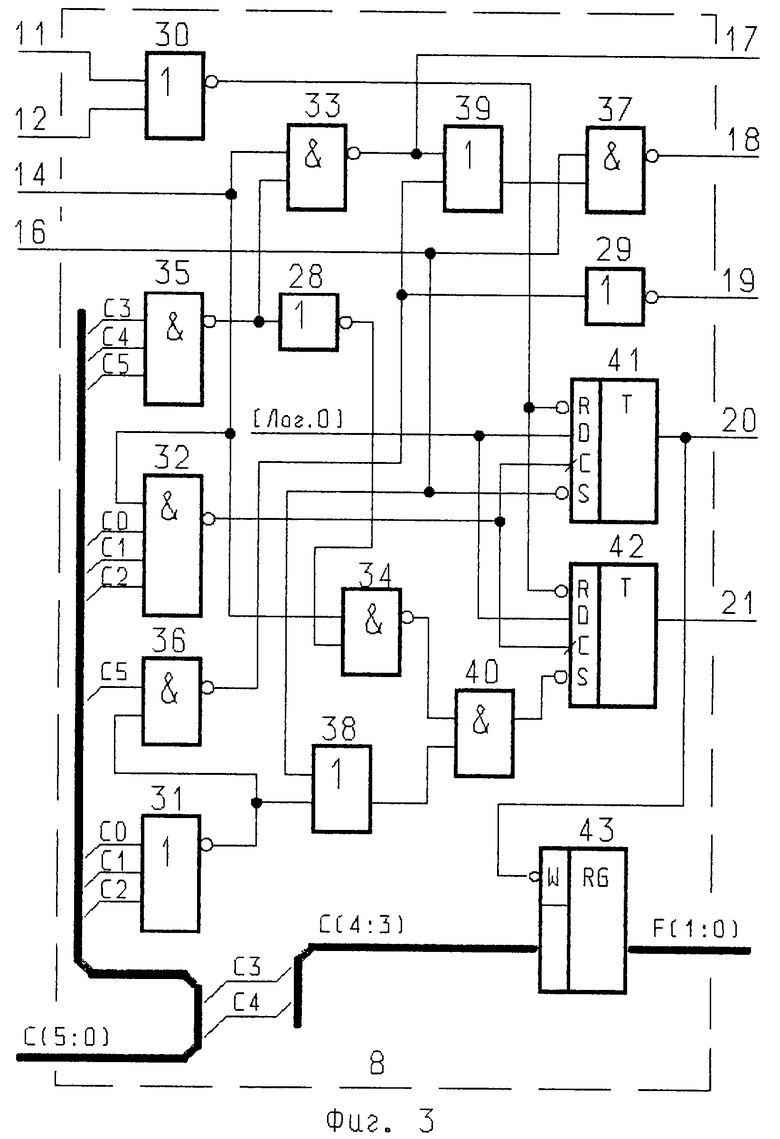

Блок 8 управления (фиг.3) содержит первый 11 и второй 12 входы сброса, первый 14 и второй 16 импульсные входы, кодовые (4+q)=6-разрядный вход и q= 2-paзpядный выход, выходы с первого 17 по пятый 21, второй 28 и третий 29 элементы НЕ, первый 30 и второй 31 элементы ИЛИ-НЕ, элементы И-НЕ с второго 32 по седьмой 37, четвертый 38 и пятый 39 элементы ИЛИ, элемент 40 И, третий 41 и четвертый 42 триггеры с асинхронными инверсными входами сброса и установки, и регистр 43, причем входы сброса триггеров 41 и 42 связаны через элемент 30 с входами 11 и 12 сброса блока 8, импульсный вход 14 которого соединен с первыми входами элементов 32-34, остальные входы элемента 32 соединены раздельно с входами элемента 31 и входами трех младших разрядов кодового входа блока 8, входы (q+l)=3 старших разрядов которого соединены с входами элемента 35, первый вход элемента 36 соединен с входом самого старшего разряда кодового входа блока 8, входы остальных q=2 старших разрядов которого связаны через регистр 43 с кодовым выходом блока 8, импульсный вход 16 которого соединен с входом установки триггера 41 и первыми входами элементов 37 и 38, выход элемента 31 соединен с вторыми входами элементов 36 и 38, выход элемента 35 соединен с вторым входом элемента 33 и связан через элемент 28 с вторым входом элемента 34, выход которого соединен с первым входом элемента 40, второй вход которого соединен с выходом элемента 38, выход элемента 32 соединен с тактовыми входами триггеров 41 и 42, информационные входы которых соединены с шиной логического 0 блока 8, выход 17 которого соединен с выходом элемента 33 и первым входом элемента 39, выход которого соединен с вторым входом элемента 37, выход которого соединен с выходом 18 блока 8, выход элемента 36 соединен с вторым входом элемента 39 и через элемент 29 связан с выходом 19 блока 8, выход 20 которого соединен с выходом триггера 41 и асинхронным инверсным входом записи регистра 43, выход элемента И соединен с входом установки триггера 42, выход которого является выходом 21 блока 8.

Приемник-декодер 1 может быть выполнен для работы с входным самосинхронизирующимся кодом RZ как и в прототипе [1] с использованием в качестве демодулятора микросборки АП.004 Т53.430.006 ТУ, а для работы с манчестерским кодом (МК) приемник можно выполнить, например, на основе аналогового блока приема/передачи МК (см. в [1] на с. 206 рис. 5.1), а декодер МК, например, на основе дешифратора кода Манчестер-11 на микропрограммном автомате (см. в [5] на с. 98 рис. 2.22).

При реализации устройства (фиг 1-3) с использованием библиотеки элементов ИС серии 533 и/или 1533 можно выполнить: регистр 2 - на одной ИС ИР8 (регистре с асинхронным инверсным входом сброса, последовательным информационным входом, соединенным с двумя информационными входами ИС ИР8 функционирующими по И, и тактовым входом ввода последовательной информации по фронтам импульсов битовой синхронизации и параллельным байтовым выходом; счетчик 7 (или счетчик 24) - на двух (или одной) ИС ИЕ7 (ИС ИЕ7 - реверсивный 4-разрядный счетчик с асинхронным входом сброса и асинхронным инверсным входом загрузки кода с параллельных информационных входов, и суммирующим (+1) и вычитающим (-1) счетными входами, обеспечивающими функционирование по фронтам действующих на них счетных импульсов), причем у обеих ИС счетчика 7 входы сброса и вычитающие счетные входы соответственно соединены с шинами логического 0 и 1 устройства, а у ИС счетчика 24 суммирующий счетный вход соединен с шиной логической 1 устройства; в качестве элемента 4 использована ИС ИП5 - девятиразрядная схема контроля четности и нечетности; триггеры 5, 6, 41 и 42 выполнены на двух ИС ТМ2; регистр 43 выполнен на ИС ИЕ7, у которой счетные входы и вход сброса соответственно соединены с шинами логической 1 и логического 0 устройства; остальные составные части устройства выполнены на комбинационных элементах соответствующих ИС.

Описание функционирования устройства осуществляется с помощью системы положений и обозначений, определенных в следующих пунктах:

1. Входные, промежуточные (формируемые внутри составных частей устройства) и результирующие (формируемые на выходах составных частей устройства ) прямые (или инверсные) переменные обозначим соответственно через Xi, Zj (или NZj) и Yk (или NYk), где число из множества {i, j, k} означает или номер входа, или номер элемента, или номер выхода. Например, X10 - тактовые импульсы на входе 10, Y4 - сигнал на выходе элемента 4, NY17 - инверсные синхроимпульсы на выходе 17. NZ23 - инверсные импульсы на выходе элемента 23 и т.п. Кроме того, коды на выходах регистра 2, счетчика 7, блока 8, счетчика 24 и кодовом входе обнаружителя 3 обозначим соответственно через G(7:0)=G7.. .G0, C(5:0)=С5...С0, F(1:0)=F1 F0, СР(3:0)=СР3 СР2 СР1 СР0 и Р(3:0)=Р3 Р2 Р1 Р0, где (G0, С0, F0, СР0 и Р0) младшие, а (G7, С5, Fl, СР3 и Р3) старшие разрядные цифры (т.е. 0 или 1) этих кодов.

2. Используется модифицированный язык описания Булевых (логических) функций ABEL, в котором операторы КОНЪЮНКЦИИ, ДИЗЪЮНКЦИИ, ИНВЕРСИИ и ИСКЛЮЧАЮЩЕЕ ИЛИ имеют обозначения "&", "#", "!" и "$" соответственно. Например, элемент 23 (фиг.2) формирует переменную NZ23=!Z23 (т.е. знак N в левой части эквивалентен знаку ! в правой части) согласно выражению

NZ23=!(Х10 & NY15)=![Х10 & (СРО # СР1 # СР2 # СР3)].

3. Под фронтом или спадом любого сигнала (прямого или инверсного) понимается смена логического значения этого сигнала из "0" в "1" или из "1" в "0".

4. Под установкой (или сбросом), например, триггера 41 блока 8 (фиг.3) понимается переключение этого триггера в "1" (или "0").

5. В процессе функционирования устройства вырабатываются сигнал NY15 паузы и сигнал Y20 готовности результата операции так, что можно выделить следующие четыре режима его работы:

РР0 ожидания (холостого хода) при Y20 NY15 =00, (3)

РР1 преобразования при Y20 NY15 = 01, (4)

РР2 готовности при Y20 NY15=10, (5)

РР3 преобразования и готовности при Y20 NY15=11. (6)

С учетом принятой системы положений и обозначений опишем сначала функционирование устройства в целом как конечного автомата с памятью, а затем работу его составных частей.

Исходным состоянием устройства является режим РР0 (3), в котором инверсным сигналом NY15=0 паузы регистр 2 сброшен, триггер 5 установлен (т.е. Y5= 1), счетчик 7 зафиксирован в состоянии С(5:0)=(011000), сигналом Y20=0 регистр 43 зафиксирован в состоянии F(1:0)=C(4:3)=(11), а триггеры 6 и 42 находятся в состояниях, обусловленных предысторией функционирования устройства. В данный режим устройство переключается при включении аппаратуры по сигналу X11= 1 начального сброса или при переходе из режима РР2 (5) по сигналу X12=1.

Каждая операция приема и преобразования начинается с поступлением на входы 9 сигналов самосинхронизирующегося последовательного двоичного кода, длина которого в битах принадлежит ряду

{n}={8, 16, 24, 32}. (7)

Приемник-декодер 1 по сигналам на входах 9 с помощью тактовых импульсов X10 формирует на выходах 13 и 14 сигналы Y13 и Y14 соответственно последовательного двоичного кода принимаемой информации и последовательности F импульсов битовой синхронизации, причем для корректного выполнения операции число F должно принадлежать ряду (7). Непосредственно по первому импульсу Y14= 1 последовательности F обнаружитель 3 устанавливается в режим обнаружения паузы (по первому, а затем по каждому импульсу NZ22=!Y14 в счетчик 24 загружается код СР(3:0)=Р(3:0) порога обнаружения паузы) и устройство переходит в режим РР1 (4) преобразования, в котором импульсы Y14, при NZ35=!(С3& С4&С5)=1, проходят на выход 17 блока 8 в виде инверсных импульсов NY17=!Y14, по фронту каждого из которых в регистр 2 принимается очередной бит последовательно двоичного кода Y13, а содержимое счетчика 7 увеличивается на "1". Следовательно, при F=n=32 после окончания 8-го, 16-го, 24-го и 32-го импульсов Y14 выставится сигнал Y19=1 готовности байта (0-го, 1-го, 2-го и 3-го) и установятся соответственно следующие состояния:

регистра 2 G(7:0)=D(7:0), D(15:8). D(23:16) и D(32:24), (8)

сигнала Y4= (G7 $ G6 $ G5 $ G4 $ G3 $ G2 $ G1 $ G0) $ Y5, (9)

счетчика 7 С(5:0)=(10000), (101000), (110000) и (111000), (10)

регистра 43 F(1:0)=(00), (01), (10) и (11) (11)

и сформируется синхроимпульс

Y18={Y14 &[!(C3&C4&C5)] & Y19} # Y16 (12)

(по 9-му, 17-му и 25-му импульсу Y14 и инверсному импульсу NY16 обнаружения паузы) параллельно-последовательного кода результата операции, по фронту которого триггер 6 устанавливается в состояние

Y6=Y4 (в момент фронта Y18), (13)

а также может быть снят с устройства соответствующий байт (8) результата операции. Непосредственно по инверсному импульсу NY16 обнаружения паузы устанавливается триггер 41, а по окончании импульса NY16 обнаружитель 3 выставляет сигнал паузы NY15=0 и устройство переходит в режим РР2 (5). Выставлением сигнала Y20=1 готовности результата операции устройство прерывает ЭВМ для сообщения о завершении очередной операции и съема кода F(1:0) и сигналов Y6(13) информационной ошибки результата операции и Y21 сбоя битовой синхронизации. В процессе выполнения прерывающей программы ЭВМ формирует сигнал X12 сброса готовности результата, который через элемент 30 сбрасывает триггеры 41 и 42 и переключает устройство в исходное состояние - режим РР0 (3).

В устройстве сигнал Y21 формируется триггером 42, который устанавливается по инверсному импульсу NZ40, формируемому элементом 40 при числе F, не равном n из ряда (7), согласно формуле

NZ40=!{(Y14 & С3 & С4 & С5) # [Y16 &(С0#С1#С2)]}. (14)

В режиме РР2 или РР3 сигналы Y6 и Y21 вырабатываются так, что при Y6= Y21=0 сбоев не обнаружено; при Y6=1 обнаружена информационная ошибка (четное число единиц) в преобразованном ранее коде Y13 в параллельно-последовательный код (8) согласно принципам контроля по модулю два [10, с.69-73]; при Y21=1 обнаружен сбой битовой синхронизации, т.е. определено, что число F импульсов Y14 битовой синхронизации не принадлежит ряду (7). Кроме того, в режиме РР1 или РР3 по восьмому импульсу Y14 вырабатывается инверсный импульс NZ32= !(Y14 & С0 & С 1 & С2), по фронту которого триггеры 41 и 42 сбрасываются, так как их информационные входы подключены к шине логического 0. Это, даже при отсутствии импульса X12, всегда обеспечивает переход из режима РР3 в режим РР1 и сброс триггера 42 сигнала Y21 сбоя битовой синхронизации перед завершением текущей операции приема и преобразования информации с входов 9.

Таким образом, функционирование устройства как конечного автомата с памятью состоит в чередовании режимов его работы, например, РР0, РР1, РР2, РР3, РР1 и т.п. так, что переход: в РР0 может быть осуществлен из любого режима по сигналу X11 начального сброса, либо из режима РР2 по сигналу X12 сброса готовности результата; в РР1 - из режима РР0 по первому импульсу Y14, или из режима РР3 по сигналу X12, либо по фронту импульса NZ32; в РР2 - только из режима РР1 по импульсу NY16 обнаружения паузы; в РР3 - только из РР2 по первому импульсу Y14.

Функционирование отдельных составных частей устройства заключается в следующем.

Приемник-декодер 1 по сигналам на входах 9 самосинхронизирующегося последовательного двоичного кода (например, типа RZ или Манчестер-11) и тактовым импульсам X10 формирует сигнал Y13 последовательного двоичного кода принимаемой информации и последовательность импульсов Y14 битовой синхронизации, число которых, при корректной работе системы, должно принадлежать ряду (7).

Регистр 2 по сигналу NY15=0 паузы зафиксирован в нулевом состоянии G(7: 0)= (00000000), а при NY15=1 по фронту каждого импульса NY17=!Y14 последовательности F принимает очередной бит последовательного двоичного кода Y13 и, например, при F=32 на кодовом выходе формирует параллельно-последовательный код (8) результата операции приема и преобразования сигналов самосинхронизирующегося последовательного двоичного кода на входах 9.

Обнаружитель 3 (фиг.2) вырабатывает инверсный сигнал NY15 паузы и инверсный импульс обнаружения паузы NY16 согласно выражениям

NY15=СР0 # СР1 # СР2 # СР3, (15)

NY16=[!(Х10 & СР0)] # СР1 # СР2 # СР3, (16)

так, что он находится при NY15=0 в состоянии паузы, а при NY15=1 в режиме обнаружения паузы, который заканчивается по окончании фронта импульса NY16. Из фиг.2 и (16) следует, что импульс NY16 вырабатывается по тактовому импульсу X10 при нахождении счетчика 24 в состоянии СР(3:0)=(0001), а сигнал NY15= 0 паузы выставляется при нахождении счетчика 24 в состоянии СР(3:0)= (0000), в котором счетчик 24 может быть зафиксирован сигналом X11=1 начального сброса. При X11=0 счетчик 24 по коду Р(3:0) и инверсным импульсам NZ22= ! Y14 и NZ23=!(X10 & NY15) функционирует следующим образом. Каждым импульсом NZ22= 0 счетчик 24 фиксируется в состоянии СР(3:0)=Р(3:0), которое определяет порог Р обнаружения как число согласно выражению

Р=Р0+2Р1+4Р2+8Р3. (17)

При наступлении паузы формирование импульсов NZ22=!Y14 прекращается и при NY15=1 элемент 23 формирует ровно Р(17) импульсов NZ23 (отсчитываются от последнего импульса NZ22), по фронту каждого из которых содержимое счетчика 24 уменьшается на "1", а по импульсу Р этой последовательности формируется импульс NY16= !X10 (16) обнаружения паузы, по окончании которого счетчик 24 переходит в состояние СР(3:0)=(0000), обнаружитель 3 выставляет сигнал NY15= 0 паузы и блокирует работу элемента 23 по импульсам Х10. В состоянии паузы обнаружитель 3 остается до поступления на него очередной последовательности F импульсов Y14 битовой синхронизации. В этой связи порог обнаружения Р (17) и частоту f10= kf14 тактовых импульсов X10 (где k - коэффициент пропорциональности, больший "1"; f14 - частота следования импульсов Y14 битовой синхронизации) необходимо выбирать из условия

2/f14>P/f10> l/f14=T (18)

вариацией двух чисел k>1 и Р>2, обеспечивающих длительность То временного порога обнаружения паузы согласно выражению

То=P/f10=P/(kf14)=Т(P/k). (19)

Элемент 4 и триггеры 5 и 6 по коду G(7:0), сигналу NY15 (15) паузы и синхроимпульсам Y18 (12) формируют сигнал Y6 информационной ошибки согласно (13).

Счетчик 7 по сигналу NY15= 0 паузы зафиксирован в состоянии С(5:0)= (011000), а при NY15=1 по фронту каждого импульса NY17 содержимое счетчика 7 увеличивается на "1".

Блок 8 управления (фиг.3) вырабатывает синхроимпульсы Y18 (12) съема по фронтам выходного кода G(7:0) результата с регистра 2, инверсные сдвиговые импульсы

NY17=!{Y14 & [! (С3 & С4 & С5 )]} (20)

битовой синхронизации последовательного кода Y13, сигнал

Y19=[!(С0 # С1 # С2)] & С5 (21)

готовности байта G(7:0) результата операции, сигнал Y20 готовности результата операции (выставляется установкой по импульсу NY16 (16) триггера 41), сигнал Y21 сбоя битовой синхронизации (выставляется установкой по импульсу NZ40 (14) триггера 42) и код F(1:0): F(1:0)=C(4:3) при Y20=0, а при Y20= 1 код F(1: 0) определяет номер последнего байта G(7:0) закончившейся операции, снятого с устройства по фронту импульса Y18=Y16 - cм.(12).

Условие (18) и сброс триггеров 41 и 42 непосредственно по сигналу NZ30=! (Х11 # XI 2) или по фронту импульса

NZ32=!(Y14 & С0 & С1 & С2) (22)

определяют, что при отсутствии NZ30 длительность Т20г сигнала Y20=1 готовности результата операции максимальна и при Тn=4Т оценивается выражением

Т20г=10Т. (23)

Сравнивая (1) и (23) получаем

Т20г/Т1г>2,5, (24)

что длительность времени готовности результата операции предлагаемого устройства в несколько раз выше длительности времени готовности прототипа [1] , емкость регистра сдвига которого в четыре раза больше емкости регистра 2.

Наличие на выходах устройства как синхроимпульсов Y18 так и сигналов Y19 готовности байтов параллельно-последовательного кода G(7:0) (его форму при n= 32 см. в (8)) обеспечивает множество вариантов передачи в ЭВМ через УУО результата операции

{D(J:0), F(1:0), Y6, Y20, Y21}, (25)

где J принадлежит множеству (7).

Опишем два возможных варианта ввода результата (25) в ЭВМ по синхроимпульсам Y18 и/или сигналу готовности Y19 байта.

В первом случае в УУО по фронту каждого импульса Y18 текущий байт G(7:0) загружается в байтовый буферный регистр типа ИР23 и вызывается прерывание ЭВМ первого типа. ЭВМ при выполнении первой прерывающей программы в своей оперативной памяти формирует параллельный код D(J:0). По окончании каждой операции устройство выставляет сигнал Y20=1 и вызывает прерывание ЭВМ второго типа. ЭВМ при выполнении второй прерывающей программы в течение времени Т20г (23) считывает код F(1:0) и битовые сигналы Y6 и Y21, формирует сигнал X11= 1 сброса готовности результата (25), а затем при Y6#Y21=0 пересылает, например, информационную часть кода D(J:0) абоненту (приемнику), а при Y6# Y21= 1 результат игнорируется, поскольку обнаружен сбой (или ошибка) в коде D(J:0) при Y6=1 или сбой битовой синхронизации при Y21=1.

Во втором случае УУО по каждому сигналу Y19 и коду F(1:0) записывает каждый байт G(7:0) кода D(J:0) в оперативную память (ОЗУ, или ДОЗУ, или аппаратный стек ). По окончании каждой операции устройство выставляет сигнал Y20= 1 прерывания ЭВМ, которая в течение времени Т20г (23) выполняет прерывающую программу, аналогичную второй прерывающей программе, описанной для первого случая.

Разнообразие описанных возможных вариантов ввода результата (25) в ЭВМ позволяет оптимизировать построение КЛС с точки зрения аппаратурных затрат, поскольку использование для передачи параллельно-последовательного кода (его называют также последовательно-параллельным кодом) позволяет экономить оборудование [9, с. 66-69].

Таким образом, по сравнению с прототипом [1], предлагаемое устройство, благодаря его существенным признакам, имеет более широкую область использования за счет как обеспечения возможности приема и преобразования входной последовательной информации в ряде длин кодов с обнаружением информационной ошибки и сбоя битовой синхронизации, так и большого разнообразия вариантов ввода в ЭВМ результата (25) при увеличенном времени (23) готовности операции в несколько раз ( см. оценку (24)) при меньшей в несколько раз емкости регистра сдвига. В этой связи данное устройство можно использовать для построения простых КЛС, поддерживающих с высокой достоверностью в локальной сети обмен самосинхронизирующимися последовательными двоичными кодами как с фиксированными, так и различными длинами, принадлежащими, например, ряду типа (7).

Источники информации

1. А.с. СССР 1068927, МКИ G 06 F 3/04. Устройство для ввода информации. Л.П. Горохов, Р.Ю. Хальфан и В.А. Генина. Опубл. 23.01.1984, БИ 3.

2. Организация последовательных мультиплексных каналов систем автоматического управления. С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой. Под общ. ред. С.Т. Хвоща. - М.-Л.: Машиностроение. Ленингр. отд-ние, 1989. - 271 с., ил.

3. Щербаков Н.С. Достоверность работы цифровых устройств. - М.: Машиностроение, 1989. - 224 с.: ил.

4. Контроль функционирования больших систем. Г.П. Шибанов, Е.А. Артеменко, А.А. Матешкин, Н.И. Циклинский. Под ред. засл. изобретателя РСФСР д.т. н. Г.П. Шибанова. - М.: Машиностроение, 1977. - 360 с.

5. Ю.В. Новиков, Д.Г. Карпенко. Аппаратура локальных сетей: функции, выбор, разработка. Под общ. ред. Ю.В. Новикова. - М.: изд-во ЭКОМ, 1998. - 288 с.: ил.

6. А.с. СССР 752317, МКИ 3 G 06 F 3/0. Устройство для ввода информации. Н.Н. Шарпило, Э.В. Щенов и А.М. Гончарова. Опубл. 30.07.1980, БИ 28.

7. А.с. СССР 1081637, МКИ G 06 F 3/00. Устройство для ввода информации. В.М. Задорина и А.В. Кочетков. Опубл. 23.03.84, БИ 11.

8. А.с. СССР 1786491, МКИ G 06 F 13/00. Устройство для ввода информации. Д.Ю. Гусев и Ю.В. Крюков. Опубл. 07.01.1993, БИ 1.

9. Каган Б.М. Электронные вычислительные машины и системы: Учебное пособие для вузов. - 3-е изд., перераб. и доп.-М.: Энергоатомиздат, 1991. - 592 с.: ил.

10. Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2001. - 528 с.: ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

Устройство для ввода информации относится к области вычислительной техники и предназначено для выполнения операции приема и преобразования самосинхронизирующегося последовательного двоичного кода в ряде длин кодов в параллельно-последовательный код с обнаружением информационной ошибки и сбоя битовой синхронизации. Технический результат заключается в расширении области использования устройства за счет обеспечения возможности приема и преобразования входных кодов в ряде длин с выдачей байтами в параллельно-последовательном коде в сопровождении кода номера байта и сигналов готовности байта и его синхронизации, а также в формировании сигналов контроля функционирования устройства (сбоя битовой синхронизации и информационной ошибки результата операции) и в формировании сигнала готовности результата операции с помощью обнаружения паузы с программируемым порогом. Устройство содержит приемник-декодер, регистр сдвига, обнаружитель паузы, элемент контроля по модулю два, два триггера, суммирующий счетчик, блок управления. 3 ил.

Устройство для ввода информации, содержащее приемник-декодер, регистр сдвига, обнаружитель паузы, выход готовности результата операции, входы самосинхронизирующегося последовательного двоичного кода, являющиеся информационными входами приемника-декодера, выход последовательного двоичного кода которого соединен с информационным входом регистра сдвига, и тактовый вход, соединенный с тактовыми входами приемника-декодера и обнаружителя паузы, отличающееся тем, что оно дополнительно содержит элемент контроля по модулю два, два триггера, (4+q)-разрядный суммирующий счетчик, блок управления, вход начального сброса, соединенный с входом установки обнаружителя паузы в состояние паузы и первым входом сброса блока управления, первый выход которого соединен с счетным входом суммирующего счетчика и тактовым входом регистра сдвига, вход сброса готовности результата, соединенный с вторым входом сброса блока управления, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя паузы, байтовый выход параллельно-последовательного кода результата операции, соединенный с кодовым выходом регистра сдвига и кодовым входом элемента контроля по модулю два, битовый вход которого соединен с выходом первого триггера, выход синхроимпульсов параллельно-последовательного кода результата операции, соединенный с вторым выходом блока управления и тактовыми входами первого и второго триггеров, выход готовности байта результата операции, являющийся третьим выходом блока управления, четвертый выход которого соединен с выходом готовности результата операции устройства, выход сигнала сбоя битовой синхронизации, соединенный с пятым выходом блока управления, выход сигнала информационной ошибки результата операции, являющийся выходом второго триггера, и q-разрядный выход кода номера байта результата операции (где q определяет количество байт в результате операции, входящее в ряд от одного байта до два в степени q включительно), являющийся кодовым выходом блока управления, первый импульсный вход которого соединен с выходом импульсов битовой синхронизации приемника-декодера и входом установки обнаружителя паузы в режим обнаружения паузы, выход элемента контроля по модулю два соединен с информационными входами первого и второго триггеров, асинхронный инверсный вход сброса первого триггера и асинхронные инверсные входы сброса и установки второго триггера соединены с шиной логической 1 устройства, кодовый вход блока управления связан через суммирующий счетчик с кодовым входом константы устройства, у которого самый старший и три младших разряда нули, а остальные q разрядов - единицы, инверсные асинхронные входы сброса регистра сдвига, установки первого триггера и записи суммирующего счетчика соединены с первым выходом обнаружителя паузы, который содержит входы тактовый, установки в состояние паузы, установки в режим обнаружения паузы, два выхода, первые элементы НЕ и И-НЕ, вычитающий счетчик, первый, второй и третий элементы ИЛИ и кодовый вход, который соединен с информационными входами вычитающего счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, тактовый вход обнаружителя соединен с первым входом первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ и счетным входом вычитающего счетчика, выход младшего разряда которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента И-НЕ и первым выходом обнаружителя, вход установки которого в состояние паузы соединен с входом сброса вычитающего счетчика, асинхронный инверсный вход записи которого через первый элемент НЕ связан с входом установки обнаружителя в режим обнаружения паузы, выход второго элемента ИЛИ является вторым выходом обнаружителя, который соединен с вторым импульсным входом блока управления, который содержит два входа сброса, два импульсных входа, кодовые (4+q)-разрядный вход и q-разрядный выход, пять выходов, второй и третий элементы НЕ, два элемента ИЛИ-НЕ, с второго по седьмой элементы И-НЕ, четвертый и пятый элементы ИЛИ, элемент И, третий и четвертый триггеры с асинхронными инверсными входами сброса и установки и регистр, причем входы сброса третьего и четвертого триггеров связаны через первый элемент ИЛИ-НЕ с входами сброса блока управления, первый импульсный вход которого соединен с первыми входами второго, третьего и четвертого элементов И-НЕ, остальные входы второго элемента И-НЕ соединены раздельно с входами второго элемента ИЛИ-НЕ и входами трех младших разрядов кодового входа блока управления, входы (q+1) старших разрядов которого соединены с входами пятого элемента И-НЕ, первый вход шестого элемента И-НЕ соединен с входом самого старшего разряда кодового входа блока управления, входы остальных q старших разрядов которого связаны через регистр с кодовым выходом блока управления, второй импульсный вход которого соединен с входом установки третьего триггера и первыми входами седьмого элемента И-НЕ и четвертого элемента ИЛИ, выход второго элемента ИЛИ-НЕ соединен с вторыми входами шестого элемента И-НЕ и четвертого элемента ИЛИ, выход второго элемента И-НЕ соединен с тактовыми входами третьего и четвертого триггеров, информационные входы которых соединены с шиной логического 0 блока управления, выход пятого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ и связан через второй элемент НЕ с вторым входом четвертого элемента И-НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, первый выход блока управления соединен с выходом третьего элемента И-НЕ и первым входом пятого элемента ИЛИ, выход которого соединен с вторым входом седьмого элемента И-НЕ, выход которого соединен с вторым выходом блока управления, выход шестого элемента И-НЕ соединен с вторым входом пятого элемента ИЛИ и через третий элемент НЕ связан с третьим выходом блока управления, четвертый выход которого соединен с выходом третьего триггера и асинхронным инверсным входом записи регистра, выход элемента И соединен с входом установки четвертого триггера, выход которого является пятым выходом блока управления.

| SU 253633 А1, 23.08.1982 | |||

| Устройство для ввода информации | 1982 |

|

SU1068927A1 |

| Устройство для ввода информации | 1976 |

|

SU638948A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2000 |

|

RU2166790C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| US 6232960 А, 15.05.2001 | |||

| US 6211702 А, 03.04.2001. | |||

Авторы

Даты

2003-04-10—Публикация

2001-05-22—Подача