Изобретение относится к электронно-вычислительной технике, предназначено для синтеза сигналов с V-образной частотной модуляцией и может быть использовано для измерения частоты Доплера в радиолокации, системах навигации и системах зондирования различных сред.

Известны цифровые синтезаторы частот, содержащие генератор тактовых импульсов, блок задержки, два блока постоянного запоминания, счетчик с предварительной установкой, два регистра памяти, два цифровых накопителя, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот и формирователь импульсов [1].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор частот, содержащий последовательно соединенные генератор тактовых импульсов и блок задержки, последовательно соединенные первый блок постоянного запоминания и счетчик с предварительной установкой, последовательно соединенные второй блок постоянного запоминания, второй регистр памяти, второй цифровой накопитель, первый регистр памяти, первый цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, выход которого является выходом цифрового синтезатора частот, а входами являются адресные входы первого и второго блоков постоянного запоминания [2].

Однако в известных синтезаторах частот нет возможности синтезировать сигнал с V-образной частотной модуляцией, который используется в радиолокаторах для измерения частоты Доплера.

Изобретение позволяет расширить функциональные возможности цифрового синтезатора и обеспечивает требуемый закон частотной модуляции синтезируемого сигнала.

Положительный эффект - обеспечение возможности синтеза сигнала с V-образной частотной модуляцией достигается за счет того, что в цифровом синтезаторе частотно-модулированных сигналов в качестве счетчика частоты вместо цифрового накопителя использован реверсивный счетчик с предварительной установкой и введена обратная связь через схему сравнения для изменения направления счета реверсивного счетчика.

При этом в цифровой синтезатор частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок задержки; блок постоянного запоминания, регистр памяти, делитель с переменным коэффициентом деления, последовательно соединенные цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом синтезатора, а входами цифрового синтезатора частотно-модулированных сигналов являются адресные входы блока постоянного запоминания, выход старшего разряда суммы цифрового накопителя подключен к входу управления инверсией преобразователя кодов, причем новым является то, что в цифровой синтезатор частотно-модулированных сигналов введены ждущий мультивибратор, реверсивный счетчик с предварительной установкой, схема сравнения, при этом вход ждущего мультивибратора является входом запуска цифрового синтезатора частотно-модулированных сигналов, а его выход подключен к входам установки делителя с переменным коэффициентом деления, реверсивного счетчика и цифрового накопителя; выход блока постоянного запоминания подключен к входу реверсивного счетчика и первому входу схемы сравнения, а выход реверсивного счетчика подключен к входу цифрового накопителя и второму входу схемы сравнения, выход которой подсоединен к входу управления направлением счета реверсивного счетчика; тактовые входы регистра памяти, делителя с переменным коэффициентом деления, цифрового накопителя и цифроаналогового преобразователя подключены к соответствующим выходам блока задержки; входами цифрового синтезатора частотно-модулированных сигналов также являются информационные входы регистра памяти, выход которого подключен к информационному входу делителя с переменным коэффициентом деления, выход последнего подсоединен к тактовому входу реверсивного счетчика.

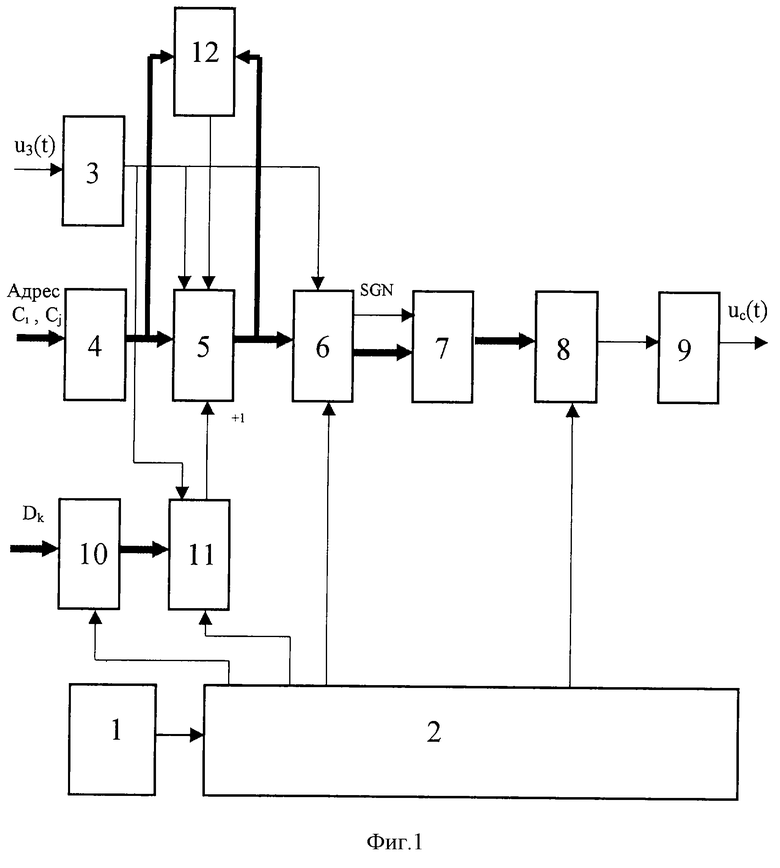

На фиг. 1 приведена структурная схема цифрового синтезатора частотно-модулированных сигналов, на фиг.2 - диаграммы работы устройства, на фиг.3 - график изменения частоты выходного сигнала синтезатора.

Цифровой синтезатор частотно-модулированных сигналов (фиг.1) содержит эталонный (опорный) генератор 1, блок задержки 2, ждущий мультивибратор 3, блок постоянного запоминания 4, реверсивный счетчик с предварительной установкой 5, цифровой накопитель 6, преобразователь кодов 7, цифроаналоговый преобразователь 8, фильтр нижних частот 9, первый регистр памяти 10, делитель с переменным коэффициентом деления 11, схему сравнения 12.

Цифровой синтезатор частотно-модулированных сигналов (фиг.1) содержит последовательно соединенные эталонный генератор 1 и блок задержки 2, последовательно соединенные блок постоянного запоминания 4, реверсивный счетчик с предварительной установкой 5 (счетчик частоты), цифровой накопитель 6 (вычислитель фазы), преобразователь кодов 7, цифроаналоговый преобразователь 8, фильтр нижних частот 9, выход которого является аналоговым выходом синтезатора, а выход старшего разряда суммы цифрового накопителя 6 подключен к входу управления инверсией преобразователя кодов 7, ждущий мультивибратор 3, выходы которого подключены к входам установки реверсивного счетчика 5, цифрового накопителя 6, делителя с переменным коэффициентом деления 11; регистра памяти 10, выходы которого подсоединены к информационным входам делителя с переменным коэффициентом деления 11, выход последнего подключен к тактовому входу реверсивного счетчика 5; схему сравнения 12, первые входы которой подключены к выходам блока постоянного запоминания 4, вторые входы - к выходам реверсивного счетчика 5, а выход подключен к входу управления направления счета реверсивного счетчика 5, выходы блока задержки 2 подключены к тактовым входам регистра памяти 10, делителя с переменным коэффициентом деления 11, цифрового накопителя 6, цифроаналогового преобразователя 8, при этом цифровыми входами синтезатора являются информационные входы регистра памяти 10, адресные входы блока постоянного запоминания 4 и вход запуска ждущего мультивибратора 3.

Цифровой синтезатор частотно-модулированных сигналов работает следующим образом.

Эталонный генератор 1 выдает сигнал опорной частоты синусоидальной формы, который поступает на вход блока задержки 2, формирующий разнесенные во времени последовательности прямоугольных импульсов формы "меандр" (фиг. 2а), поступающие на тактовые входы регистра памяти 10, делителя с переменным коэффициентом деления 11, цифрового накопителя 6, цифроаналогового преобразователя 8 и служащие для синхронизации работы синтезатора.

Пусть в момент t1 (фиг.2б) приходит импульс запуска u3(t) на вход ждущего мультивибратора 3, формирующий импульс установки uу(t) отрицательной полярности (фиг.2в), по которому сначала в схему сравнения 12 происходит запись кода конечной частоты Cj, а код коэффициента деления Dk записывается в регистр памяти 10, затем в момент t2 код начальной частоты Ci записывается в реверсивный счетчик с предварительной установкой 5, а код Dk из регистра памяти 10 - в делитель с переменным коэффициентом деления 11.

В момент t3 по окончании импульса установки (фиг.2в) происходит запись кода Ci из реверсивного счетчика 5 в первый цифровой накопитель 6.

Далее, с каждым следующим тактовым импульсом код на выходах реверсивного счетчика 5 будет изменяться по формуле

A = Ci + T/Dk, (1a)

где Т=0,1,2,3,4,... - номер тактового импульса.

Как только А достигнет значения Сj, схема сравнения переключит направление счета реверсивного счетчика 5, следовательно, код частоты сигнала будет описываться формулой

A = Cj - T/Dk (1б)

Тогда частота сигнала будет изменяться согласно графику, представленному на фиг.3.

На выходах цифрового накопителя 6 код суммы будет изменяться следующим образом:

S = CiT + T2/Dk при Ci<A<Cj (2a)

S = CjT - T2/Dk как только A = Cj (2б)

Если принять, что f0 = Ci/2π - начальная частота, 0,5f' = 1/Dk - скорость изменения частоты, Δt = Т, то фаза сигнала будет изменяться по формуле:

ϕ = f0t + 0,5f't2 при Ci<A<Cj (3а)

ϕ = f0t - 0,5f't2 при А = Cj и далее (3б)

Старший разряд SGN кода суммы S поступает на вход управления инверсией преобразователя кодов 7, а остальные N старших разрядов кода суммы через преобразователь кодов 7 подключены к соответствующим информационным входам цифроаналогового преобразователя 8 (где N - число разрядов ЦАП). Если SGN=0, то на цифроаналоговый преобразователь 8 поступает прямой двоичный код суммы, а если SGN=1, то - обратный код суммы.

На выходе цифроаналогового преобразователя формируется аналоговый сигнал "пилообразной формы", если отключен знаковый разряд SGN, и сигнал "треугольной" формы, если подключен знаковый разряд SGN.

С выхода цифроаналогового преобразователя 8 аналоговый сигнал поступает на фильтр нижних частот 9, который пропускает на выход синтезатора только первую гармонику синтезированного сигнала, амплитуда которого будет изменяться по формуле: ,

,

где Um - амплитуда сигнала.

Как только на вход ждущего мультивибратора 3 поступит следующий импульс запуска tз2 (фиг.3), произойдет установка кода начальной частоты Ci и направление счета снова станет положительным.

Таким образом, в синтезаторе формируется сигнал с V-образной частотной модуляцией, который используется в радиолокации для измерения частоты Доплера.

Литература

1. Патент 2149503 Российской Федерации МКИ Н 03 В 19/00, Цифровой синтезатор частот. /Рябов И. В. , Рябов В. И. - Заявл. 13.04.1999. Опубл. 20.05.2000. Бюл. 14.

2. Патент 2058659 Российской Федерации МКИ Н 03 В 19/00, Цифровой синтезатор частот. /Рябов И. В. , Фищенко П.А. - Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. 11 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИГНАЛОВ | 2004 |

|

RU2257669C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ С РАСШИРЕННЫМ ЧАСТОТНЫМ ДИАПАЗОНОМ | 2002 |

|

RU2227366C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2000 |

|

RU2166833C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| СИНТЕЗАТОР С V-ОБРАЗНЫМ ЗАКОНОМ МОДУЛЯЦИИ ЧАСТОТЫ | 2009 |

|

RU2407144C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2143173C1 |

Изобретение относится к электронно-вычислительной технике и может использоваться для измерения частоты Доплера в радиолокации. Цифровой синтезатор частотно-модулированных сигналов содержит эталонный генератор, блок задержки, блок постоянного запоминания, регистр памяти, делитель с переменным коэффициентом деления, цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, ждущий мультивибратор, реверсивный счетчик с предварительной установкой и схему сравнения. Достигаемый технический результат - обеспечение возможности синтеза сигнала с V-образной частотной модуляцией. 3 ил.

Цифровой синтезатор частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок задержки; блок постоянного запоминания, регистр памяти, делитель с переменным коэффициентом деления, последовательно соединенные цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом синтезатора, а входами цифрового синтезатора частотно-модулированных сигналов являются адресные входы блока постоянного запоминания, выход старшего разряда суммы цифрового накопителя подключен к входу управления инверсией преобразователя кодов, отличающийся тем, что в цифровой синтезатор частотно-модулированных сигналов введены ждущий мультивибратор, реверсивный счетчик с предварительной установкой, схема сравнения, при этом вход ждущего мультивибратора является входом запуска цифрового синтезатора частотно-модулированных сигналов, а его выход подключен к входам установки делителя с переменным коэффициентом деления, реверсивного счетчика и цифрового накопителя; выход блока постоянного запоминания подключен к входу реверсивного счетчика и первому входу схемы сравнения, а выход реверсивного счетчика - к входу цифрового накопителя и второму входу схемы сравнения, выход которой подсоединен к входу управления направлением счета реверсивного счетчика; тактовые входы регистра памяти, делителя с переменным коэффициентом деления, цифрового накопителя и цифроаналогового преобразователя подключены к соответствующим выходам блока задержки; входами цифрового синтезатора частотно-модулированных сигналов также являются информационные входы регистра памяти, выход которого подключен к информационному входу делителя с переменным коэффициентом деления, выход последнего подсоединен к тактовому входу реверсивного счетчика.

| RU 2058659 C1, 20.04.1996 | |||

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| Синтезатор частот | 1989 |

|

SU1654969A1 |

| US 4862109 A, 29.08.1989 | |||

| US 5235531 A, 10.08.1993. | |||

Авторы

Даты

2003-05-10—Публикация

2001-04-06—Подача