Изобретение относится к электронно-вычислительной технике, предназначено для синтеза сигналов с частотной модуляцией (ЧМ) и может быть использовано в радиолокации, адаптивных широкополосных системах связи.

Известны цифровые синтезаторы частот, содержащие два блока постоянного запоминания, накопитель, умножитель кодов, счетчик с предварительной установкой, преобразователь кодов, регистр памяти, цифроаналоговый преобразователь, фильтр нижних частот, генератор тактовых импульсов и блок задержки [1] .

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор частот, содержащий два блока постоянного запоминания, два накопителя, два регистра памяти, счетчик с предварительной установкой, цифроаналоговый преобразователь, фильтр нижних частот, генератор тактовых импульсов, блок задержки, преобразователь кодов [2].

Однако известные синтезаторы частот, основанные на нерекурсивных принципах, для получения высокой линейности изменения частоты требуют высокой разрядности фазового вычислителя, что приводит к снижению быстродействия.

Изобретение позволяет обеспечить достижение высокой линейности изменения частоты и повышение быстродействия.

Это достигается за счет использования импульсов переполнения фазового вычислителя, введения формирователя импульсов и обратной связи с первым накопителем.

Цифровой синтезатор частот, содержащий последовательно соединенные генератор тактовых импульсов и блок задержки, последовательно соединенные первый блок постоянного запоминания и счетчик с предварительной установкой, выход которого подключен ко входу последовательного переноса второго накопителя, последовательно соединенные второй блок постоянного запоминания, второй регистр памяти, второй накопитель, первый регистр памяти, первый накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, первый выход блока задержки подсоединен к тактовому входу счетчика с предварительной установкой, адресные входы первого и второго блоков постоянного запоминания являются входами, а выход фильтра нижних частот - выходом цифрового синтезатора частот, причем новым является то, что введен формирователь импульсов, вход которого подсоединен к выходу самого старшего разряда первого накопителя, а выход формирователя импульсов подключен ко входу последовательного переноса первого накопителя, предпоследний старший разряд которого подключен ко входу управления инверсией преобразователя кодов, второй и третий выходы блока задержки подключены к тактовым входам первого и второго накопителей соответственно.

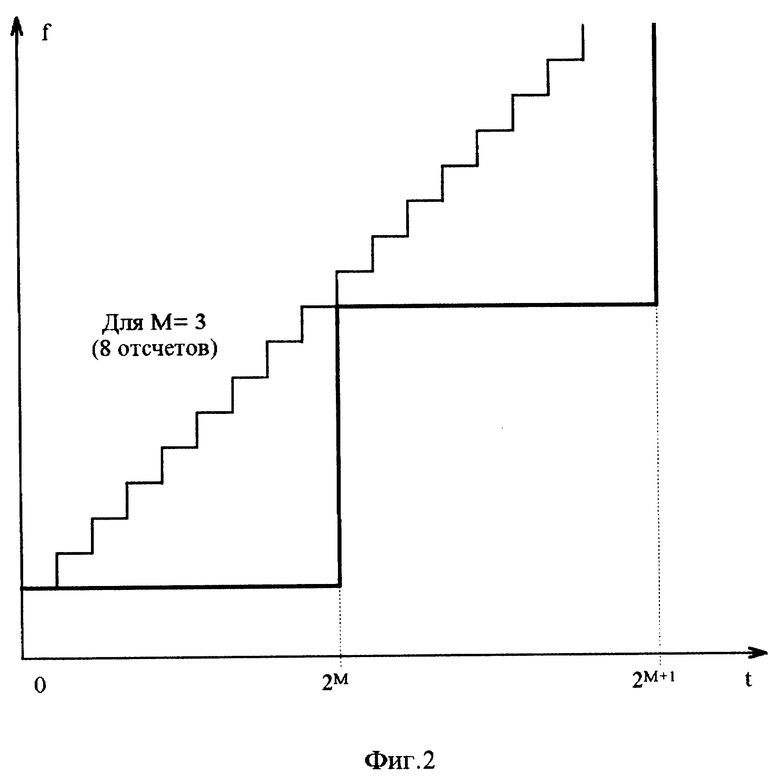

На фиг. 1 представлена структурная схема цифрового синтезатора частот; на фиг. 2 приведены графики изменения частоты цифровых синтезаторов частот (жирная линия - для прототипа, тонкая линия - для предлагаемого синтезатора частот).

Цифровой синтезатор частот содержит последовательно соединенные генератор тактовых импульсов 1 и блок задержки 2, последовательно соединенные первый блок постоянного запоминания 3, счетчик с предварительной установкой 4, выход которого подключен к входу последовательного переноса второго накопителя 7, последовательно соединенные второй блок постоянного запоминания 5, второй регистр памяти 6, второй накопитель 7, первый регистр памяти 8, первый накопитель 9, преобразователь кодов 10, цифроаналоговый преобразователь 11, фильтр нижних частот 12, первый выход блока задержки 2 подключен к тактовому входу счетчика с предварительной установкой 4; адресные входы первого и второго блоков постоянного запоминания 3, 5 являются входами, а выход фильтра нижних частот - выходом цифрового синтезатора частот, причем новым является то, что введен формирователь импульсов 13, вход которого подсоединен к выходу самого старшего разряда первого накопителя 9, а выход формирователя импульсов 13 подключен ко входу последовательного переноса первого накопителя 9, предпоследний старший разряд SGN 2 подключен ко входу управления инверсией преобразователя кодов 10, второй и третий выходы блока задержки 2 подключены к тактовым входам первого и второго накопителей 9, 7 соответственно.

Цифровой синтезатор частот работает следующим образом.

На адресные входы первого блока постоянного запоминания 3 поступает адрес выборки Dk, определяющий скорость изменения частоты синтезируемого частотно-модулированного сигнала, одновременно на адресные входы второго блока постоянного запоминания 5 поступает адрес выборки Ci, определяющий частоту синтезируемого сигнала.

Генератор тактовых импульсов 1 формирует синусоидальный сигнал опорной частоты fт, а блок задержки 2 осуществляет преобразование сигнала в тактовые импульсы формы "меандр" и разнесение по времени последовательности тактовых импульсов на 1. ..3 выходах, при этом обеспечивается снижение шумов переключения счетчика 4, первого и второго накопителей 7, 9 при неопределенных состояниях на их выходах. Счетчик с предварительной установкой 4 используется в качестве делителя с переменным коэффициентом деления, который зависит от значения Dk. Частота сигнала f на выходе счетчика 4 равна fт/Dk.

На выходе первого накопителя 7 код числа A обновляется в соответствии с тактовой частотой fт:

A = Ci + T/Dk,

где Ci - константа, записанная во втором блоке постоянного запоминания 5;

Dk - константа, записанная в первом блоке постоянного запоминания 3;

T - номер тактового импульса (T = 0, 1, 2, 3 ...).

Тогда на выходах второго накопителя 9 с каждым последующим тактовым импульсом код B изменяется следующим образом:

B = A • T = (Ci + T/Dk) • T = Ci • T + T2/Dk

Последний старший разряд SGN 1 результата суммирования с первого накопителя 9 поступает на вход формирователя импульсов 13, где формирует импульс добавления единицы (+1) к результату суммирования первого накопителя 9. Предпоследний старший разряд SGN 2 результата суммирования с первого накопителя 9 поступает на вход управления инверсией преобразователя кодов 10. Остальные N старших разрядов (N - число разрядов ЦАП) через преобразователь кодов 10 поступают на соответствующие входы цифроаналогового преобразователя 11, который формирует аналоговый ступенчатый сигнал "треугольной" формы.

Фаза синтезируемого сигнала будет изменяться по закону:

ϕ = [Ci×T+T2/Dk](1+1/2M).

Необходимо отметить, что результат суммирования изменяется в интервале B = 0 ... 2N, что соответствует изменению фазы в интервале ϕ = 0...2π..

Аналоговый сигнал проходит ФНЧ 9, который пропускает на выход синтезатора частот только первую гармонику сформированного сигнала. В результате разработанное устройство синтезирует сигнал, амплитуда которого изменяется по формуле:

u(t) = Umsin[(ω0t+0.5ω′2t)(1+2M)],

где Um - максимальная амплитуда синтезируемого сигнала.

По сравнению с прототипом у заявленного синтезатора частот линейность скорости изменения частоты значительно выше. Как можно видеть из фиг. 2, "дискрет" изменения частоты у данного синтезатора частот в 2M раза меньше, чем у прототипа, где M - число разрядов первого накопителя, который является фазовым вычислителем.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204197C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2143173C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИГНАЛОВ | 2004 |

|

RU2257669C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ С РАСШИРЕННЫМ ЧАСТОТНЫМ ДИАПАЗОНОМ | 2002 |

|

RU2227366C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2000 |

|

RU2166833C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР МНОГОФАЗНЫХ СИГНАЛОВ | 2010 |

|

RU2423782C1 |

Изобретение относится к электронно-вычислительной технике и может быть использовано для синтеза сигналов с частотной модуляцией в радиолокации, адаптивных системах связи. Достигаемый технический результат - увеличение линейности изменения частоты и повышение быстродействия. Цифровой синтезатор частот содержит генератор тактовых импульсов, блок задержки, два блока постоянного запоминания, счетчик с предварительной установкой, два регистра памяти, два накопителя, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот и формирователь импульсов. 2 ил.

Цифровой синтезатор частот, содержащий последовательно соединенные генератор тактовых импульсов и блок задержки, последовательно соединенные первый блок постоянного запоминания и счетчик с предварительной установкой, выход которого подключен ко входу последовательного переноса второго накопителя, последовательно соединенные второй блок постоянного запоминания, второй регистр памяти, второй накопитель, первый регистр памяти, первый накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, первый выход блока задержки подсоединен к тактовому входу счетчика с предварительной установкой, адресные входы первого и второго блоков постоянного запоминания являются входами, а выход фильтра нижних частот - выходом цифрового синтезатора частот, отличающийся тем, что введен формирователь импульсов, вход которого подсоединен к выходу самого старшего разряда первого накопителя, а выход формирователя импульсов подключен ко входу последовательного переноса первого накопителя, предпоследний старший разряд которого подключен ко входу управления инверсий преобразователя кодов, второй и третий выходы блока задержки подключены к тактовым входам первого и второго накопителей соответственно.

| RU 2058659 C1, 20.04.1996 | |||

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Синтезатор частот | 1989 |

|

SU1654969A1 |

| US 5070310 A, 03.12.1991. | |||

Авторы

Даты

2000-05-20—Публикация

1999-04-13—Подача