Изобретение относится к электронно-вычислительной технике, предназначено для синтеза сигналов с частотной модуляцией (ЧМ) и может быть использовано в радиолокации, адаптивных широкополосных системах связи.

Известны цифровые синтезаторы частот, содержащие два блока постоянного запоминания, два накопителя, два регистра памяти, счетчик с нижних частот, генератор тактовых импульсов, блок задержки, преобразователь кодов /1/.

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор частот, содержащий два блока постоянного запоминания, накопитель, умножитель кодов, счетчик с предварительной установкой, преобразователь кодов, регистр памяти, цифроаналоговый преобразователь, фильтр нижних частот, генератор тактовых импульсов и блок задержки /2/.

Однако известные синтезаторы частот не обеспечивают возможности быстрого управления частотой и скоростью изменения частоты.

Изобретение позволяет расширить функциональные возможности синтезатора частот и повысить его быстродействие.

Положительный эффект - увеличение скорости изменения частоты по сравнению с существующими синтезаторами частот - достигается за счет введения дополнительной операции суммирования при вычислении фазы сигнала и исключения двух операций суммирования перед перемножением входных кодов. Для этого последовательно соединенные генератор тактовых импульсов и блок задержки, последовательно соединенные блок постоянного запоминания, счетчик с предварительной установкой и умножитель кодов, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, регистр памяти, накопитель, преобразователь кодов, при этом счетный вход счетчика с предварительной установкой соединен с первым выходом блока задержки, третий, четвертый и пятый выходы которого подсоединены к тактовым входам записи множимого, множителя и произведения умножителя кодов соответственно, входы блока постоянного запоминания и выход фильтра нижних частот являются соответственно входом и выходом синтезатора частот, причем выходы счетчика с предварительной установкой подключены к входам множимого умножителя кодов, выходы произведения которого соединены с информационными входами накопителя, выходы которого подключены к информационным входам преобразователя кодов, выходы которого соединены с соответствующими входами цифроаналогового преобразователя, тактовый вход накопителя подключен к шестому выходу блока задержки, а выход сигнала старшего знакового разряда накопителя соединен с входом управления инверсией преобразователя кодов, входы регистра памяти является входом цифрового синтезатора частот, а второй выход блока задержки соединен с тактовым выходом регистра памяти.

Подобного технического решения ни в научно-технической, ни в патентной литературе выявлено не было.

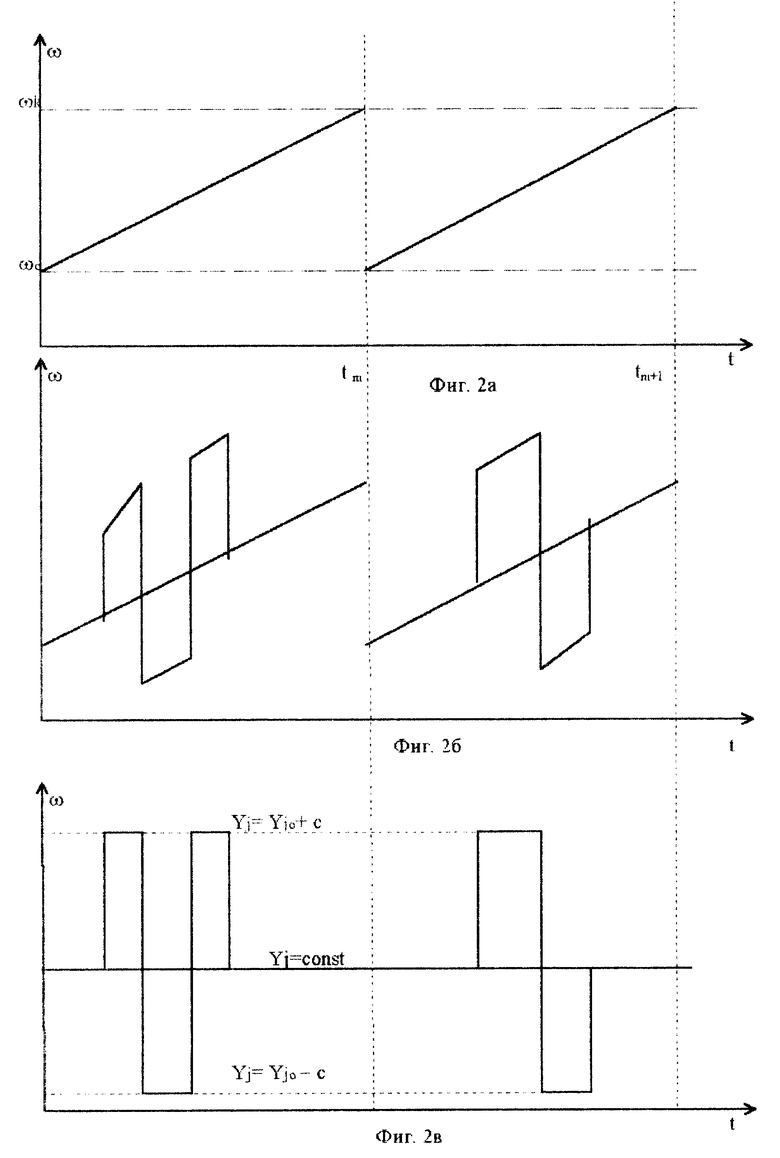

На фиг. 1 приведена структурная схема цифрового синтезатора частот. На фиг. 2 - графики и изменения циклической частоты во времени. Фиг. 2а - в гетеродине приемника, фиг. 2б - в модуле передатчика, фиг. 2в - на выходе приемника.

Цифровой синтезатор частот содержит:

1. Генератор тактовых импульсов

2. Блок задержки

3. Блок постоянного запоминания

4. Счетчик с предварительной установкой

5. Умножитель кодов

6. Накопитель

7. Преобразователь кодов

8. Цифроаналоговый преобразователь

9. Фильтр нижних частот

10. Регистр памяти

Цифровой синтезатор частот содержит последовательно соединенные генератор тактовых импульсов 1 и блок задержки 2, последовательно соединенные блок постоянного запоминания 3, счетчик с предварительной установкой 4, входы множимого умножителя кодов 5, выходы произведения умножителя кодов 5 и входы накопителя 6, преобразователь кодов 7, цифроаналоговый преобразователь 8, фильтр нижних частот 9, причем старший разряд накопителя 6 подключен ко входу управления инверсий преобразования кодов 7. Выходы регистра памяти 10 подключены ко входам множителя умножителя кодов, а первый выход блока задержки 2 подключен к тактовому входу счетчика 4, второй - к тактовому входу регистра памяти 10, третий, четвертый и пятый - к тактовым входам множимого, множителя и произведения умножителя кодов 5 соответственно, шестой выход блока задержки 3 подключен к тактовому входу накопителя 6. Входами цифрового синтезатора частот являются адресные входы блока постоянного запоминания 3 и входы регистра памяти 10, а выход фильтра нижних частот 9 является выходом устройства.

Цифровой синтезатор частот работает следующим образом.

На адресные входы блока постоянного запоминания 3 поступает адрес выборки Xi, определяющий синтезируемого частотно-модулированного сигнала, одновременно код Yi из управляющей ЭВМ записывается в регистр памяти 10. Генератор тактовых импульсов 1 формирует синусоидальный сигнал опорной частоты fт, а блок задержки 2 осуществляет преобразование сигнала в тактовые импульсы формы "меандр" и разнесение по времени последовательности тактовых импульсов на 1. ..6 выходах, при этом обеспечивается снижение шумов переключения счетчика 4, умножителя кодов 5 и накопителя при неопределенных состояниях на их выходах.

На выходе счетчика с предварительной установкой 4 код числа X обновляется в соответствии с тактовой частотой fт

X = Xi + T,

где Xi - константа, записанная в блоке постоянного запоминания 3;

T - номер тактового импульса (T = 0, 1, 2, 3...).

Тогда на выходах произведения умножителя кодов 5 код произведения с каждым последующим тактовым импульсом изменяется следующим образом:

П = X* Y = (Xi + T)* Yj.

С выхода умножителя кодов 5 код произведения поступает на входы накопителя 6, который в данном синтезаторе частот является фазовым вычислителем. На выходах накопителя 6 код суммирования изменяется следующим образом:

S = П* T = (Xi + T)* Yj * T = Xi * Yj * T + Yj * T2.

Старший разряд результата суммирования с накопителя 6 поступает на вход управления инверсией преобразователя кодов 7. Остальные N старших разрядов (N - число разрядов ЦАП) через преобразователь кодов 7 поступает на соответствующие входы цифроаналогового преобразователя 8, который формирует аналоговый ступенчатый сигнал "пилообразной" формы, если отключен знаковый разряд Ssgn и сигнал "треугольной" формы, если подключен знаковый разряд Ssgn.

Фаза синтезируемого сигнала изменяется по закону

ϕ = S = X

Необходимо отметить, что результат суммирования изменяется в интервале

S = 0...2N, что соответствует изменению фазы ϕ = 0...2.

Если принять ω0= X

0.5ω′ = Yi - скорость изменения циклической частоты,

Δt = T, то тогда фаза будет изменяться по формуле

ϕ = ω0t+0,5ω′t2.

Аналоговый сигнал проходит ФНЧ 9, который пропускает на выход синтезатора частот только первую гармонику сформированного сигнала. В результате разработанное устройство синтезирует сигнал, амплитуда которого изменяется по формуле

u(t) = Umsin(ω0t+0,5ω′t2),

где Um - максимальная амплитуда синтезируемого сигнала.

Особенностью заявленного синтезатора частот является то, что его можно использовать для передачи информации. Необходимо два таких синтезатора частот, один из которых используется в качестве модулятора передатчика, а другой - в качестве гетеродина приемника.

Изменение частоты в приемнике происходит по формуле

ω0(t) = Xi0Yi0+Yi0t.

Изменение частоты в передатчике происходит по формуле

ω1(t) = xi0Yi1+Yi1t.

где Yj1 = Yi0 + c;

Yi1 - код частоты информационного сигнала;

c - код информационного символа.

Следовательно, в приемнике можно выделить разностный сигнал .

.

Таким образом, изменяя код множителя Yi в синтезаторе передатчика, можно передавать информационное сообщение синтезированным ЧМ-сигналом (фиг. 2а, 2б, 2в).

Литература

1. Патент РФ 2058659, кл. H 03 B 19/00, 1996.

2. Авторское свидетельство СССР 1774464, кл. H 03 B 19/00, 1992.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С БЫСТРОЙ ПЕРЕСТРОЙКОЙ ЧАСТОТЫ | 2012 |

|

RU2491710C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204197C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2000 |

|

RU2166833C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ С РАСШИРЕННЫМ ЧАСТОТНЫМ ДИАПАЗОНОМ | 2002 |

|

RU2227366C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИГНАЛОВ | 2004 |

|

RU2257669C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

Цифровой синтезатор частот относится к электронно-вычислительной технике, предназначен для синтеза сигналов с частотной модуляцией и может использоваться в радиолокации, адаптивных широкополосных системах связи. Цифровой синтезатор частот содержит генератор тактовых импульсов, блок задержки, блок постоянного запоминания, счетчик с предварительной установкой, умножитель кодов, накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот и регистр памяти. Достигаемый технический результат - расширение функциональных возможностей и повышение быстродействия. 4 ил.

Цифровой синтезатор частот, содержащий последовательно соединенные генератор тактовых импульсов и блок задержки, последовательно соединенные блок постоянного запоминания, счетчик с предварительной установкой и умножитель кодов, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, регистр памяти, накопитель, преобразователь кодов, при этом счетный вход счетчика с предварительной установкой соединен с первым выходом блока задержки, третий, четвертый и пятый выходы которого подсоединены к тактовым входам записи множимого, множителя и произведения умножителя кодов соответственно, входы блока постоянного запоминания и выход фильтра нижних частот являются соответственно входом и выходом синтезатора частот, отличающийся тем, что выходы счетчика с предварительной установкой подключены к входам множимого умножителя кодов, выходы произведения которого соединены с информационными входами накопителя, выходы которого подключены к информационным входам преобразователя кодов, выходы которого соединены с соответствующими входами цифроаналогового преобразователя, тактовый вход накопителя подключен к шестому выходу блока задержки, а выход сигнала старшего знакового разряда накопителя соединен с входом управления инверсией преобразователя кодов, входы регистра памяти являются входом цифрового синтезатора частот, а второй выход блока задержки соединен с тактовым входом регистра памяти, выходы которого подключены к входам множителя умножителя кодов.

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

| RU 2058659 C1, 20.04.96 | |||

| Синтезатор частот | 1989 |

|

SU1654969A1 |

| US 4862109 A, 29.08.89 | |||

| US 5235531 A, 10.08.93 | |||

| СПОСОБ ПОЛУЧЕНИЯ ГРАНУЛ ИЗ РАСПЛАВА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2229332C2 |

Авторы

Даты

1999-12-20—Публикация

1999-02-04—Подача