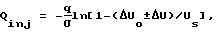

FIELD: semiconductor engineering; manufacture of metal-insulator- semiconductor transistors and integrated circuits. SUBSTANCE: method includes formation of source and drain regions, and sub-gate insulator on silicon wafer, formation of metal interconnections, estimation of adjustment of threshold voltage ΔUo and next adjustment of threshold voltage by external action on value of ΔUo±ΔU followed by thermal annealing, where signs "+" and "-" for n- and p-channel MIS transistors; ΔU is change in threshold voltage value during thermal annealing. External action is applied by heavy field-effect tunnel injection of electron charge into sub-gate insulator, electron-charge density being  where q is electron charge, C; σ is electron trap capture section in sub-gate insulator, sq. cm; Us is saturation voltage of MIS transistor threshold voltage varying in the course of injection. EFFECT: facilitated procedure; enhanced precision of threshold voltage adjustment. 2 cl, 2 dwg

where q is electron charge, C; σ is electron trap capture section in sub-gate insulator, sq. cm; Us is saturation voltage of MIS transistor threshold voltage varying in the course of injection. EFFECT: facilitated procedure; enhanced precision of threshold voltage adjustment. 2 cl, 2 dwg

| Title | Year | Author | Number |

|---|---|---|---|

| METHOD FOR MANUFACTURING MIS TRANSISTORS | 2002 |

|

RU2206142C1 |

| METHOD FOR GENERATION OF METAL-DIELECTRIC- SEMICONDUCTOR TRANSISTORS | 1986 |

|

SU1452398A1 |

| PROCESS OF MANUFACTURE OF MIS LSI CIRCUITS | 1991 |

|

RU2017265C1 |

| PROCESS OF MANUFACTURE OF MIS LARGE-SCALE INTEGRATED CIRCUITS | 1987 |

|

RU1519452C |

| PROCESS OF MANUFACTURE OF MIS LARGE-SCALE INTEGRATED CIRCUITS | 1990 |

|

SU1762688A1 |

| METHOD OF MANIPULATING INSULATED-GATE FIELD-EFFECT TRANSISTORS | 1984 |

|

SU1176777A1 |

| METHOD TO RESTORE THRESHOLD VOLTAGE OF MIS TRANSISTOR STRUCTURES AFTER EXPOSURE TO PLASMA TREATMENTS | 2010 |

|

RU2426192C1 |

| MANUFACTURING PROCESS FOR MIS LARGE-SCALE INTEGRATED CIRCUITS | 1985 |

|

SU1384106A2 |

| METHOD FOR MANUFACTURING FIELD-EFFECT TRANSISTORS | 1986 |

|

RU1499614C |

| METHOD FOR MANUFACTURING OF FIELD-EFFECT TRANSISTOR | 1987 |

|

SU1419418A1 |

Authors

Dates

2003-06-10—Published

2002-03-25—Filed