Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известна энергонезависимая ячейка памяти (см. а.с. СССР №1811353 от 02.04.90, МКИ Н 03 К 3/286. Энергонезависимая ячейка памяти. Г.И. Шишкин, опубл. 20.07.95, бюл. №20), содержащая сердечник с прямоугольной петлей гистерезиса и двумя обмотками, RS-триггер, три логических элемента, резистор выходную шину и шины опроса, разрешения и установки в ноль и единицу. Конец первой обмотки сердечника подключен к выходу первого логического элемента, один вход которого подключен к выходной шине и прямому выходу RS-триггера. Выход второго логического элемента соединен с одним из входов третьего логического элемента. Другой вход первого логического элемента подключен к шине установки в единицу. Начало первой обмотки сердечника через резистор соединено с выходом третьего логического элемента, другой вход которого подключен к шине установки в ноль. Один из входов второго логического элемента соединен с прямым выходом RS-триггера, другой вход - с шиной опроса. Шина разрешения соединена с R-входом RS-триггера, S-вход которого подключен к началу второй обмотки сердечника, конец которой соединен с общей шиной. Первый и третий логические элементы выполнены в виде элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй логический элемент - в виде элемента ИЛИ-НЕ.

Недостатком известной энергонезависимой ячейки памяти являются ограниченные функциональные возможности, связанные с отсутствием возможности постоянного съема информации.

Известна энергонезависимая ячейка памяти (см. патент РФ №2036547 от 04.04.91, МКИ Н 03 К 3/286, 3/037. Энергонезависимая ячейка памяти. Г.И. Шишкин, опубл. 27.05.95, бюл. №15), содержащая RS-триггер, прямой выход которого соединен с выходной шиной, три логических элемента, первые входы первого и третьего из которых подключены к шинам установки в единицу и в ноль, соответственно сердечник с прямоугольной петлей гистерезиса и первой и второй обмотками, концы которых подключены к выходу первого логического элемента и общей шине соответственно, первый резистор и шину питания, второй сердечник с прямоугольной петлей гистерезиса и двумя обмотками, второй - четвертый резисторы. Второй логический элемент снабжен третьим входом, вторым и третьими выходами и выполнен в виде четырехканального коммутатора, а первый и третий логические элементы - в виде соответственно первого и второго двунаправленных ключей, управляющие входы которых являются первыми входами этих логических элементов. Первый и второй адресные входы четырехканального коммутатора соединены с шинами установки в единицу и в ноль соответственно, а информационный вход - с информационными входами двунаправленных ключей и шиной питания, первый выход - с началами первых обмоток сердечников, второй вход - с S-входом RS-триггера и через первый резистор с началом второй обмотки первого сердечника, третий выход - с R-входом RS-триггера и через второй резистор с началом второй обмотки второго сердечника, конец которой соединен с общей шиной. Прямой и инверсный выходы RS-триггера через третий и четвертый резисторы соответственно соединены с концами первых обмоток соответственно первого и второго сердечников, а выход второго двунаправленного ключа соединен с концом первой обмотки второго сердечника.

Энергонезависимая ячейка памяти является наиболее близкой по технической сущности к заявленному устройству и взята в качестве прототипа.

Недостатками прототипа являются низкая помехоустойчивость по входам и повышенное потребление в режиме хранения информации.

Задачей, решаемой предлагаемым изобретением, является создание энергонезависимой ячейки памяти, обладающей повышенной помехоустойчивостью по входам и пониженным энергопотреблением в режиме хранения информации.

Технический результат достигается тем, что в энергонезависимую ячейку памяти, содержащую три логических элемента, шины установки в единицу и в ноль, общую шину, два сердечника с прямоугольной петлей гистерезиса и двумя обмотками каждый, первые обмотки которых соединены между собой и два резистора, первый вывод первого резистора соединен с началом первой обмотки второго сердечника с прямоугольной петлей гистерезиса, а конец первой обмотки первого сердечника с прямоугольной петлей гистерезиса соединен с выходом третьего логического элемента, выход второго логического элемента соединен с первым выводом второго резистора. Новым является то, что первый логический элемент выполнен в виде триггера Шмитта, второй логический элемент выполнен в виде мажоритарного элемента, а третий логический элемент выполнен в виде инвертора, дополнительно введены два диода и конденсатор, первый вывод которого соединен с общей шиной, а второй вывод конденсатора соединен со вторым выводом второго резистора и входом триггера Шмитта, инверсный выход которого подключен ко второму выводу первого резистора и к входу инвертора, выход которого соединен с первым входом мажоритарного элемента и анодом первого диода, катод которого соединен с началом первой обмотки первого сердечника с прямоугольной петлей гистерезиса и с катодом второго диода, анод которого соединен с первым выводом первого резистора, второй вход мажоритарного элемента соединен с началом второй обмотки первого сердечника с прямоугольной петлей гистерезиса, конец которой соединен с шиной установки в единицу, а шина установки в ноль соединена с концом второй обмотки второго сердечника с прямоугольной петлей гистерезиса, начало которой соединено с третьим входом мажоритарного элемента.

Указанная совокупность признаков позволяет повысить помехоустойчивость по входам и снизить энергопотребление в режиме хранения информации.

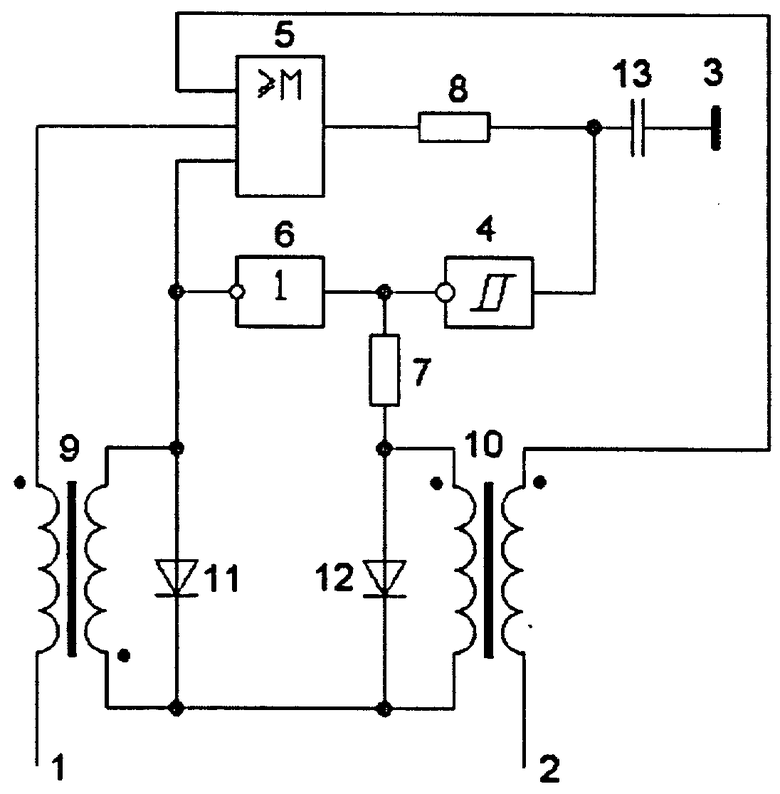

На чертеже приведена принципиальная схема энергонезависимой ячейки памяти.

Энергонезависимая ячейка памяти содержит шину установки в единицу 1, шину установки в ноль 2, общую шину 3, триггер Шмитта 4, мажоритарный элемент 5, инвертор 6, первый и второй резисторы 7 и 8 соответственно, первый и второй сердечники с прямоугольной петлей гистерезиса и двумя обмотками 9 и 10 соответственно, первый и второй диоды 11 и 12 соответственно и конденсатор 13.

Шина установки в единицу 1 соединена с концом второй обмотки сердечника с прямоугольной петлей гистерезиса 9, начало которой подключено ко второму входу мажоритарного элемента 5, первый вход которого соединен с концом первой обмотки сердечника с прямоугольной петлей гистерезиса 9 и анодом диода 11, катод которого соединен с началом первой обмотки сердечника с прямоугольной петлей гистерезиса 9, с катодом диода 12 и концом первой обмотки сердечника с прямоугольной петлей гистерезиса 10, начало которой подключено к аноду диода 12 и первому выводу резистора 7. Начало второй обмотки сердечника с прямоугольной петлей гистерезиса 10 соединено с шиной установки в ноль 2, а ее конец - с третьим входом мажоритарного элемента 5, выход которого подключен к первому выводу резистора 8, второй вывод которого соединен с входом триггера Шмитта, инверсный выход которого соединен со вторым выводом резистора 7 и с входом инвертора 6, выход которого подключен к аноду диода 11. Первый вывод конденсатора 13 соединен с общей шиной 3, а второй его вывод - со вторым выводом резистора 8.

Энергонезависимая ячейка памяти работает следующим образом.

В исходном состоянии на шину установки в единицу 1 устройства подается сигнал с уровнем логического “0”, а на шину установки в ноль 2 - сигнал с уровнем логической “1”: Устройство находится в режиме хранения информации.

Допустим, что выход мажоритарного элемента 5 и сердечники с прямоугольной петлей гистерезиса 9, 10 находятся в состоянии логического “0”. За состояние логического “0” сердечников с прямоугольной петлей гистерезиса 9, 10 принимается состояние, в которое они перемагничивается током, втекающим в начало их первой обмотки. На выходе триггера Шмитта 4 присутствует уровень логической “1”, а на выходе инвертора 6, являющегося прямым выходом устройства, - уровень логического “0”, поэтому через первые обмотки сердечников с прямоугольной петлей гистерезиса 9, 10 протекает ток, ограничиваемый резистором 7. При этом напряжение на первой обмотке сердечника с прямоугольной петлей гистерезиса 10 ограничено прямым напряжением диода 12. На первом и втором входах мажоритарного элемента 5 присутствует уровень логического “0”, а третьем его входе - уровень логической “1”.

При поступлении импульса положительной полярности на шину установки в единицу 1 на втором входе мажоритарного элемента 5 появляется уровень логической “1”, что приводит к появлению уровня логической “1” на его выходе. Это приводит к появлению сигнала логического “0” на выходе триггера Шмитта 4 и сигнала логической “1” на выходе инвертора 6. Поэтому через первые обмотки сердечников с прямоугольной петлей гистерезиса 9, 10 начинает протекать ток, ограничиваемый резистором 7, и перемагничивающий сердечники с прямоугольной петлей гистерезиса 9, 10 в состояние логической “1”. При этом напряжение на первой обмотке сердечника с прямоугольной петлей гистерезиса 9 ограничивается прямым напряжением диода 11 и время его перемагничивания больше времени перемагничивания сердечника с прямоугольной петлей гистерезиса 10, у которого в этот момент диод 12 включен в обратном направлении, а на второй его обмотке формируется импульс, приводящий к появлению импульса с уровнем логического “0” на третьем входе мажоритарного элемента, формируется импульс, длительность которого равна времени перемагничивания сердечника. Но так как на первых двух входах мажоритарного элемента 5 находится уровень логической “1”, то состояние его выхода не изменяется. На второй обмотке сердечника с прямоугольной петлей гистерезиса 9 формируется импульс, связанный с процессом его перемагничивания, но он не приводит к появлению сигнала с уровнем логического “0” на втором входе мажоритарного элемента 5, так как напряжение на первой обмотке ограничено прямым напряжением диода 11. Значение сопротивления резисторов 13 и 14 в прототипе больше значения сопротивления резистора 7 предлагаемого устройства, так как в прототипе каждый из них обеспечивает ток перемагничивания обоих сердечников с одинаковой скоростью. Поэтому в режиме хранения информации предлагаемое устройство потребляет ток меньше, чем прототип в аналогичном режиме.

После перемагничивания сердечников в состояние логической “1” импульсы на вторых обмотках сердечников с прямоугольной петлей гистерезиса 9, 10 заканчиваются. Импульс положительной полярности на шине установки в единицу 1 заканчивается. На первом и третьем входах мажоритарного элемента 5 и его выходе присутствует уровень логической “1”.

Аналогичным образом происходит переключение энергонезависимой ячейки памяти в состояние логического “0” при подаче импульса с уровнем логического “0” на шину установки в ноль 2.

При поступлении на шину установки в единицу 1 помехи, длительность которой не превышает времени перемагничивания сердечника с прямоугольной петлей гистерезиса 10, напряжение на первой обмотке которого не ограничено прямым напряжением диода 12, процессы в устройстве во время ее действия аналогичны описанным выше. После окончания помехи на втором и третьем входах мажоритарного элемента 5 и его выходе устанавливаются сигналы с уровнем логического “0”, что приводит к появлению уровня логической “1” на выходе триггера Шмитта 4 и уровня логического “0” на выходе инвертора 6. Поэтому через первые обмотки сердечников с прямоугольной петлей гистерезиса 9, 10 начинает протекать ток, ограничиваемый резистором 7 и перемагничивающий сердечники с прямоугольной петлей гистерезиса 9, 10 в состояние логической “1”, при этом напряжение на первой обмотке сердечника с прямоугольной петлей гистерезиса 10 ограничивается прямым напряжением диода 12, после чего на третьем входе мажоритарного элемента 5 появляется уровень логической “1”, а на первом и втором его входах - уровень логического “0”. На второй обмотке сердечника с прямоугольной петлей гистерезиса 9, у которого в этот момент диод 11 включен в обратном направлении, формируется импульс помехи, вызванный неидеальностью петли гистерезиса сердечника и частичным его перемагничиванием во время действия помехи. Это приводит к появлению уровня логической “1” на втором входе мажоритарного элемента 5, на выходе которого формируется импульс помехи с уровнем логической “1”, поглощаемый интегрирующей RC-цепью, состоящей из резистора 8 и конденсатора 13. Сердечники перемагничиваются в исходное состояние логического “0”.

Необходимо отметить, что рассмотренный импульс помехи может поступать несколько раз между импульсами установки в единицу и в ноль, и каждый раз сердечники восстанавливают свое состояние.

Аналогичным образом протекают процессы при поступлении помехи с уровнем логического “0” на шину установки в ноль 2 и при действии помех по питанию.

Триггер Шмитта 4, мажоритарный элемент 5 и инвертор 6 могут быть выполнены на микросхемах 564ТЛ1, 564ЛП13 и 564ЛН2 соответственно. В качестве резисторов 7, 8 могут быть использованы резисторы типа С2-33, в качестве сердечников 9, 10 - сердечники зМч-3/2,5-60 де4.804.005ТУ. В качестве диодов 11, 12 могут быть использованы диоды типа 2Д522, а в качестве конденсатора 9 - конденсатора типа К10-17с.

Изготовлен лабораторный макет энергонезависимой ячейки памяти, выполненный по схеме чертежа, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2034397C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1811353A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1999 |

|

RU2180985C2 |

| ТРОИЧНЫЙ ТРИГГЕР | 1990 |

|

SU1804270A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2234801C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и системах управления. Его использование позволяет получить технический результат в виде повышения помехоустойчивости по выходам и понижения энергопотребления в режиме хранения информации. Технический результат достигается за счет использования в энергонезависимой ячейке памяти триггера Шмитта мажоритарного элемента и инвертора и дополнительного введения двух диодов и конденсатора. 1 ил.

Энергонезависимая ячейка памяти, содержащая три логических элемента, шины установки в “1” и в “0”, общую шину, два сердечника с прямоугольной петлей гистерезиса и двумя обмотками каждый, первые обмотки которых соединены между собой, и два резистора, первый вывод первого резистора соединен с началом первой обмотки второго сердечника с прямоугольной петлей гистерезиса, а конец первой обмотки первого сердечника с прямоугольной петлей гистерезиса соединен с выходом третьего логического элемента, выход второго логического элемента соединен с первым выводом второго резистора, отличающаяся тем, что первый логический элемент выполнен в виде триггера Шмитта, второй логический элемент выполнен в виде мажоритарного элемента, а третий логический элемент выполнен в виде инвертора, дополнительно введены два диода и конденсатор, первый вывод которого соединен с общей шиной, а второй вывод конденсатора соединен со вторым выводом второго резистора и входом триггера Шмитта, инверсный выход которого подключен ко второму выводу первого резистора и ко входу инвертора, выход которого соединен с первым входом мажоритарного элемента и анодом первого диода, катод которого соединен с началом первой обмотки первого сердечника с прямоугольной петлей гистерезиса и с катодом второго диода, анод которого соединен с первым выводом первого резистора, второй вход мажоритарного элемента соединен с началом второй обмотки первого сердечника с прямоугольной петлей гистерезиса, конец которой соединен с шиной установки в “1”, а шина установки в “0” соединена с концом второй обмотки второго сердечника с прямоугольной петлей гистерезиса, начало которой соединено с третьим входом мажоритарного элемента.

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2034397C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1811353A1 |

| US 5995412 A, 30.11.1999. | |||

Авторы

Даты

2004-06-10—Публикация

2002-06-21—Подача