Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах вычислительной техники и систем управления, работающих в условиях воздействия интенсивных электромагнитных помех, разрядов статического электричества и импульсного ионизирующего излучения.

Известно помехоустойчивое устройство для счета импульсов [1] содержащее трансформаторы на магнитных сердечниках с прямоугольной петлей гистерезиса, с обмотками начальной установки, записи и считывания, блок управления, ключи записи и считывания. На два двоичных разряда счетчика используется четыре основных и шесть вспомогательных сердечников.

Недостатком такого устройства является сложность схемы, заключающаяся в большом числе моточных изделий (трансформаторов).

Наиболее близким к изобретению является помехоустойчивый счетчик импульсов [2] содержащий инвертор, элемент задержки и последовательно соединенные счетные ячейки, каждая из которых содержит ферритовый с прямоугольной петлей гистерезиса сердечник с тремя рабочими обмотками выходной, записи и считывания, последовательно соединенные первый резистор и конденсатор, а также три элемента И-НЕ, элемент НЕ, диод, второй, третий и четвертый резисторы. Вход элемента задержки подключен к входу устройства, а выход к третьим входам всех счетных ячеек. В каждой счетной ячейке анод диода соединен с началом выходной обмотки и вторым выходом этой счетной ячейки. Катод диода через последовательно установленные первый резистор и конденсатор соединен с концом выходной обмотки, соединенным также с общей шиной питания. Второй резистор подключен параллельно конденсатору. Общая точка соединения первого и второго резисторов и конденсатора подключена к второму входу первого элемента И-НЕ, его выход, являясь одновременно и первым выходом счетной ячейки, подключен к первому входу второго элемента И-НЕ. Первый вход первого элемента И-НЕ соединен с третьим входом счетной ячейки. Выход второго элемента И-НЕ через третий резистор подключен к началу обмотки записи. Конец обмотки записи объединен с началом обмотки считывания и одновременно с общей шиной питания положительного потенциала. Второй вход второго элемента И-НЕ соединен с выходом элемента НЕ. Вход элемента НЕ соединен с первым входом счетной ячейки. Второй вход счетной ячейки соединен с первым входом третьего элемента И-НЕ, выход которого через четвертый резистор подключен к концу обмотки считывания. Второй вход третьего элемента И-НЕ соединен с четвертым входом счетной ячейки. У первой счетной ячейки четвертый вход объединен с вторым входом и подсоединен к входу устройства, а ее первый вход соединен с выходом инвертора. У каждой i-й счетной ячейки, где i 2,3,n, первый вход соединен с первым выходом (i-1)-й ячейки, второй вход соединен с вторым выходом предыдущей ячейки. Третьи входы всех счетных ячеек подключены к входу инвертора. Четвертые входы всех счетных ячеек объединены и подключены к входу устройства. Первый выход n-ой счетной ячейки подключен к основному выходу устройства, а второй выход этой ячейки является его дополнительным выходом.

Недостатком данного счетчика является низкая помехоустойчивость по счетному входу из-за высокого быстродействия микросхем и малого времени перемагничивания сердечников элементов памяти в разрядах счетчика.

Цель изобретения повышение помехоустойчивости.

Для этого в помехоустойчивый счетчик импульсов, содержащий шину счетных импульсов, шину питания и в каждом разряде инвертор, два резистора, элемент памяти на магнитном сердечнике с прямоугольной петлей гистерезиса, имеющий обмотку считывания и обмотку записи, начало которой подключено к первому выводу первого резистора, введена шина установки исходного состояния, в каждый разряд асинхронный RS-триггер, полусумматор и повторитель, а в каждый разряд, кроме последнего, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем в каждом разряде R-вход асинхронного RS-триггера подключен к шине установки исходного состояния, S-вход через второй резистор к началу обмотки считывания элемента памяти, конец которой соединен с общей шиной, выходы инвертора и повторителя соединены с вторым выводом первого резистора и концом обмотки записи элемента памяти соответственно, а выводы питания с шиной питания, в каждом разряде, кроме последнего, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом триггера, выход с первым входом полусумматора, выход суммы которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входам инвертора и повторителя, второй вход полусумматора каждого разряда, начиная с второго, соединен с выходом переноса полусумматора предыдущего разряда, второй вход полусумматора первого разряда соединен с шиной счетных импульсов, в каждом разряде, кроме двух последних, вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом и первым входом соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ предпоследнего разряда соединен с прямым выходом асинхронного RS-триггера последнего разряда и с первым входом полусумматора последнего разряда, выход которого соединен с входами инвертора и повторителя последнего разряда и с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ предпоследнего разряда.

Указанная совокупность признаков позволяет повысить помехоустойчивость за счет того, что в паузе между счетными импульсами триггеры в разрядах принудительно удерживаются в нуле, а информация о состоянии счетчика хранится в элементах памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, обмотки которых в паузе между счетными импульсами обесточены. Поэтому помеха любой длительности и формы по счетному входу в паузе между счетными импульсами не приведет к изменению состояния счетчика.

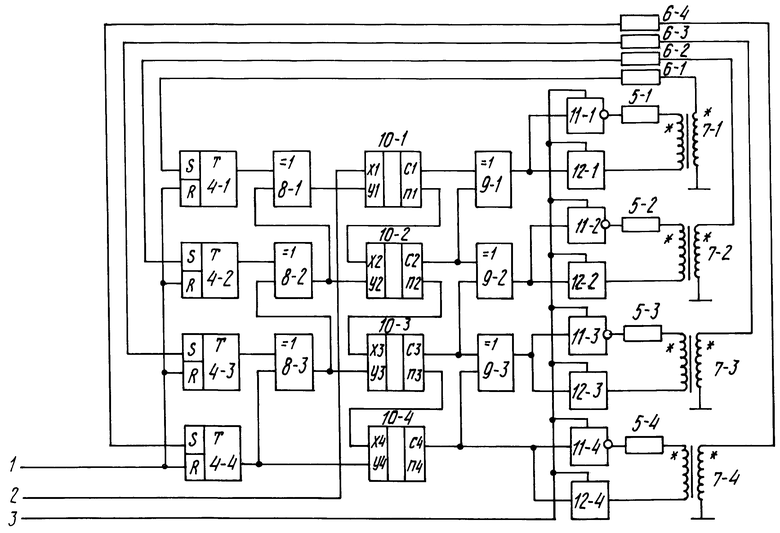

На чертеже приведена схема помехоустойчивого счетчика импульсов (четырехразрядного).

Помехоустойчивый счетчик импульсов содержит шину 1 установки исходного состояния, шину 2 счетных импульсов, шину 3 питания инверторов и повторителей и в каждом разряде триггер 4 (4-1, 4-2, 4-3, 4-4), первый 5 (5-1, 5-2, 5-3, 5-4) и второй 6 (6-1, 6-2, 6-3, 6-4) резисторы, элемент 7 (7-1, 7-2, 7-3, 7-4) памяти на сердечнике с прямоугольной петлей гистерезиса и обмотками считывания и записи, в каждом разряде, кроме последнего, первый 8 (8-1, 8-2, 8-3) и второй 9 (9-1, 9-2, 9-3) элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, в каждом разряде полусумматор 10 (10-1, 10-2, 10-3, 10-4), инвертор 11 (11-1, 11-2, 11-3, 11-4) и повторитель 12 (12-1, 12-2, 12-3, 12-4). Триггер 4 (4-1, 4-2, 4-3, 4-4) выполнен в виде асинхронного RS-триггера. Все логические элементы, кроме инверторов и повторителей, запитываются постоянно по отдельной шине, которая на чертеже не показана.

В каждом разряде начало обмотки записи элемента 7 (7-1, 7-2, 7-3, 7-4) памяти подключено к первому выводу резистора 5 (5-1, 5-2, 5-3, 5-4). Первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, 8-2, 8-3 соединены соответственно с прямыми выходами триггеров 4-1, 4-2, 4-3. Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, 8-2 соединены соответственно с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-2, 8-3.

Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8-3 соединен с прямым выходом триггера 4-4. В каждом разряде R-вход триггера 4 (4-1, 4-2, 4-3, 4-4) подключен к шине 1 установки исходного состояния, а S-вход триггера 4 (4-1, 4-2, 4-3, 4-4) через резистор 6 (6-1, 6-2, 6-3, 6-4) соединен с началом обмотки считывания элемента 7 (7-1, 7-2, 7-3, 7-4), конец которой подключен к общей шине.

В каждом разряде выходы инвертора 11 (11-1, 11-2, 11-3, 11-4) и повторителя 12 (12-1, 12-2, 12-3, 12-4) соединены с вторым выводом резистора 5 (5-1, 5-2, 5-3, 5-4) и концом обмотки записи элемента 7 (7-1, 7-2, 7-3, 7-4) памяти соответственно, а выводы питания инвертора 11 (11-1, 11-2, 11-3, 11-4) и повторителя 12 (12-1, 12-2, 12-3, 12-4) с шиной 3 питания.

Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, 8-2, 8-3 соединены соответственно с первыми входами полусумматоров 10-1, 10-2, 10-3, выходы суммы которых соединены соответственно с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1, 9-2, 9-3, выходы которых подключены к входам инверторов 11-1, 11-2, 11-3 и повторителей 12-1, 12-2, 12-3 соответственно. Вторые входы полусумматоров 10-2, 10-3, 10-4 соединены с выходами переноса соответственно полусумматоров 10-1, 10-2, 10-3.

Второй вход полусумматора 10-1 соединен с шиной 2 счетных импульсов. Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1, 9-2 подключены к первым входам соответственно элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9-2, 9-3. Прямой выход триггера 4-4 соединен с первым входом полусумматора 10-4, выход которого соединен с входами инвертора 11-4 и повторителя 12-4 и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9-3.

Счетчик выполнен на микросхемах серии 564.

Помехоустойчивый счетчик импульсов работает следующим образом.

Для установки счетчика в исходное (нулевое) состояние на шину 3 подается напряжение питания, при этом на шине 1 установки исходного состояния присутствует уровень логической "1", а на шине 2 счетных импульсов уровень логического "0". Триггеры 4-1, 4-2, 4-3, 4-4 принудительно удерживаются в нулевом состоянии. На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, 8-2, 8-3, на выходах суммы и переноса полусумматоров 10-1, 10-2, 10-3, 10-4 и на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1, 9-2, 9-3 присутствует уровень логического "0". На выходах инверторов 11-1, 11-2, 11-3, 11-4 уровень логической "1", а на выходах повторителей 12-1, 12-2, 12-3, 12-4 уровень логического "0". Через обмотки записи элементов 7-1, 7-2, 7-3, 7-4 памяти и резисторы 5-1, 5-2, 5-3, 5-4 протекает ток и сердечники элементов памяти принимают нулевое состояние. За состояние логического "0" принято состояние, в которое он намагничивается током, втекающим к обмотку записи со стороны начала. После установки счетчика в исходное состояние с шины 3 снимается питание, а на шинах 1 и 2 сохраняются соответственно уровни логической "1" и "0".

Цикл переключения счетчика в следующее состояние начинается с поступления питания на шину 3. При этом на началах обмоток считывания элементов 7-1, 7-2, 7-3, 7-4 памяти формируются импульсы помехи положительной полярности, обусловленные непрямоугольностью петли гистерезиса сердечников. Эти импульсы передаются через резисторы 6-1, 6-2, 6-3, 6-4 на S-входы триггеров 4-1, 4-2, 4-3, 4-4, которые удерживаются в нулевом состоянии по R-входам. С задержкой, превышающей максимальную длительность импульса помехи, на шине 1 установки исходного состояния появляется уровень логического "0". При этом триггеры 4-1, 4-2, 4-3, 4-4 сохраняют свое состояние. Затем на шину 2 счетных импульсов поступает счетный импульс положительной полярности (относительно общей шины). На выходе суммы полусумматора 10-1 и на выходах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1 и повторителя 12-1 появляется уровень логической "1", а на выходе инвертора 11-1 уровень логического "0". По обмотке записи элемента 7-1 памяти через ограничительный резистор 5-1 протекает ток, перемагничивающий сердечник элемента 7-1 памяти в единичное состояние. При этом на начале обмотки считывания формируется импульс отрицательной полярности, не влияющий на состояние триггера 4-1. Длительность счетного импульса должна быть достаточной для перемагничивания сердечника. После окончания счетного импульса на шине 2 на шине 1 установки исходного состояния появляется уровень логической "1", а с шины 3 снимается питание.

На выходах триггеров и полусумматоров всех разрядов при этом будет уровень логического "0", а в сердечнике элемента 7-1 памяти хранится "1".

В следующем цикле при запитке инверторов и повторителей по шине 3 питания сердечник элемента 7-1 памяти начнет перемагничиваться в нулевое состояние, при этом на начале его обмотки считывания сформируется импульс положительной полярности.

Сердечники элементов 7-2, 7-3, 7-4 памяти находятся в нулевом состоянии, поэтому на началах их обмоток считывания формируются короткие импульсы помехи. К моменту снятия уровня логической "1" с шины 1 установки исходного состояния на S-входе триггера 4-1 будет присутствовать уровень "1", а на S-входах триггеров остальных разрядов уровни "0". Триггер 4-1 по S-входу устанавливается в единичное состояние и уровень "1" с его прямого выхода проходит через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, полусумматор 10-1 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1 на входы инвертора 11-1 и повторителя 12-1. Направление тока в обмотке записи элемента 7-1 памяти изменяется на противоположное и происходит восстановление единичного состояния сердечника этого элемента памяти. После окончания этих процессов на шину 2 поступает второй счетный импульс. При этом на выходе суммы полусумматора 10-1 появляется уровень "0", а на выходе переноса суммы этого полусумматора уровень "1", который проходит через полусумматор 10-2 на его выход суммы и соответственно на второй вход элемента 9-1 ИСКЛЮЧАЮЩЕЕ ИЛИ и на первый вход элемента 9-2 ИСКЛЮЧАЮЩЕЕ ИЛИ.

На выходе элемента 9-1 ИСКЛЮЧАЮЩЕЕ ИЛИ сохраняется, а на выходе элемента 9-2 ИСКЛЮЧАЮЩЕЕ ИЛИ появляется уровень "1". Таким образом, полярность сигналов на обмотках записи элементов 7-1, 7-3, 7-4 памяти не изменится, а на обмотке записи элемента 7-2 памяти изменится на противоположную. Сердечник элемента 7-2 памяти перемагничивается в единичное состояние, при этом на начале обмотки считывания этого элемента памяти формируется импульс отрицательной полярности, который не приводит к изменению состояния триггера 4-2. По окончании процесса перемагничивания второй цикл заканчивается. На шине 1 появляется уровень "1", а на шинах 2 и 3 уровень "0".

Очередной цикл начинается, как и предыдущие, с подачи питания на шину 3. В сердечниках элементов 7-1 и 7-2 памяти хранится "1", а в сердечниках элементов 7-3 и 7-4 памяти "0". Поэтому сердечники элементов 7-1 и 7-2 памяти начинают перемагничиваться и к моменту снятия уровня "1" с шины 1 установки исходного состояния на S-входах триггеров 4-1 и 4-2 присутствует уровень "1", а на S-входах триггеров 4-3 и 4-4 уровень "0". Триггеры 4-1 и 4-2 устанавливаются в единичное состояние, и происходит регенерация информации, хранившейся в сердечниках элементов 7-1 и 7-2 памяти. Третий счетный импульс на шине 2 проходит на выход суммы полусумматора 10-1 и на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1, на втором входе которого сохраняется уровень "1". Это приводит к появлению уровня "0" на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9-1 и изменению полярности сигналов на обмотке записи элемента 7-1 памяти, сердечник которого начинает перемагничиваться в нулевое состояние. При этом на начале обмотки считывания элемента 7-1 памяти формируется импульс положительной полярности, подтверждающий по S-входу единичное состояние триггера 4-1.

Аналогичным образом происходит переключение и в следующих циклах работы счетчика. При этом информация в сердечниках элементов 7-1, 7-2, 7-3, 7-4 памяти записывается в однопеременном коде Грея, который перед очередным счетным импульсом по шине 2 считывается из сердечников в соответствующие триггеры. При (n+1)-ом счетном импульсе меняется информация, снимаемая с выходов полусумматоров 10-1, 10-2, 10-3, 10-4 и записываемая в сердечники элементов 7-1, 7-2, 7-3, 7-4 памяти, в RS-триггерах 4-1, 4-2, 4-3, 4-4 в это время сохраняется информация предыдущего n-го такта.

Помехоустойчивость счетчика импульсов в условиях воздействия мощных помех и провалов по цепи питания обеспечивается за счет сохранения информации о состоянии счетчика в энергонезависимых элементах 7-1, 7-2, 7-3, 7-4 памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, обмотки записи которых запитываются только при переключении счетчика в следующее состояние, а также за счет принудительного удержания триггеров в разрядах счетчика в нулевом состоянии между тактами работы счетчика.

Таким образом, описание работы помехоустойчивого счетчика импульсов подтверждает его работоспособность. Работоспособность лабораторного образца предлагаемого счетчика подтверждена в диапазоне температуры окружающей среды от минус 50 до плюс 60оС. Проведенные испытания показали осуществимость предлагаемого счетчика и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1992 |

|

RU2022463C1 |

| ТРОИЧНЫЙ ТРИГГЕР | 1991 |

|

RU2038693C1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1990 |

|

RU2036556C1 |

Использование: в импульсной технике. Цель: повышение помехоустойчивости. Сущность изобретения: помехоустойчивый счетчик импульсов содержит шину 1 установки исходного состояния, шину 2 счетных импульсов, шину 3 питания инверторов и повторителей и в каждом разряде триггер 4(4 - 1, 4 - 3, 4 - 4), первый 5(5 - 1, 5 - 2, 5 - 3, 5 - 4) и второй 6(6 - 1, 6 - 2, 6 - 3, 6 - 4) резисторы, элемент 7(7 - 1, 7 - 2,7 - 3, 7 - 4) памяти на сердечнике с прямоугольной петлей гистерезиса и обмотками считывания и записи, в каждом разряде, кроме последнего, первый 8(8 - 1, 8 - 2, 8 - 3) и второй 9(9 - 1, 9 - 2, 9 - 3) элементы исключающее ИЛИ, в каждом разряде полусумматор 10(10 - 1, 10 - 2, 10 - 3, 10 - 4), инвертор 11(11 - 1, 11 - 2, 11 - 3, 11 - 4) и повторитель 12(12 - 1, 12 - 2, 12 - 3, 12 - 4). Триггер 4(4 - 1, 4 - 2, 4 - 3, 4 - 4) выполнен в виде асинхронного RS-триггера. 1 ил.

ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ, содержащий шину счетных импульсов, шину питания и в каждом разряде инвертор, два резистора, элемент памяти на магнитном сердечнике с прямоугольной петлей гистерезиса, имеющий обмотку считывания и обмотку записи, начало которой подключено к первому выводу первого резистора, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены шина установки исходного состояния, в каждый разряд асинхронный RS-триггер, полусумматор и повторитель, а в каждый разряд, кроме последнего, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем в каждом разряде R-вход асинхронного RS-триггера подключен к шине установки исходного состояния, S-вход через второй резистор к началу обмотки считывания элемента памяти, конец которой соединен с общей шиной, выходы инвертора и повторителя соединены с вторым выводом первого резистора и концом обмотки записи элемента памяти соответственно, а выводы питания с шиной питания, в каждом разряде, кроме последнего, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом триггера, выход с первым входом полусумматора, выход суммы которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входам инвертора и повторителя, второй вход полусумматора каждого разряда, начиная с второго, соединен с выходом переноса полусумматора предыдущего разряда, второй вход полуссуматора первого разряда соединен с шиной счетных импульсов, в каждом разряде, кроме двух последних, вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом и первым входом соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ предпоследнего разряда соединен с прямым выходом асинхронного RS-триггера последнего разряда, выход которого соединен с входами инвертора и повторителя последнего разряда и вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ предпоследнего разряда.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Счетчик импульсов, сохраняющий информацию при перерывах питания | 1985 |

|

SU1633490A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-06-27—Публикация

1991-06-28—Подача