Изобретение относится к технике радиосвязи и может быть использовано в многоканальных (многонаправленных) системах радиосвязи с разнесенным приемом.

Заявленное техническое решение расширяет арсенал средств данного назначения.

Известно устройство для разнесенного приема телеграфных сигналов (см. А. с. 1292195, Н 04 В 7/02, бюл. 7 от 07.02.87), содержащее каналы разнесения, сумматор, блок обратной связи, блок прерывания программы, мультиплексор ввода, вычислительный блок и демультиплексор вывода. При этом каждый канал разнесения содержит основной приемный блок, блок фазирования, регистр, дополнительный приемный блок, фазовращатель, блок определения разности сигналов, блок демодуляции и измеритель временных искажений. Некоторое повышение помехоустойчивости достигается за счет когерентного сложения сигналов с далеко разнесенных адаптивных двухантенных модулей - ослабителей сосредоточенных помех.

Недостатком аналога является низкая эффективность использования канального и аппаратурного ресурсов. Это обусловлено тем, что в направление связи заранее выделяется определенное количество каналов разнесения (двухантенных модулей), а при изменении условий ведения связи в нескольких направлениях нет возможности перераспределять антенные модули между ними для обеспечения связи с требуемым качеством.

Известно также устройство выбора каналов для разнесенного приема (см. А. с. 1525925, Н 04 В 7/08, бюл. 44 от 30.11.89), содержащее блок сложения, демодулятор, регенератор и N трактов разнесения, каждый из которых включает радиоприемник, первый и второй коммутаторы, блок анализа частот и измеритель искажений. Оно обеспечивает некоторое повышение помехоустойчивости за счет сочетания оптимального частотно-разнесенного приема сигналов с выбором для сложения каналов с минимальным уровнем помех в каждом тракте разнесения. Кроме того, в каждом тракте осуществляется смена рабочих частот при воздействии помех и ухудшении условий распространения радиоволн.

Недостатком аналога является низкая эффективность использования канального и частотного ресурсов. Это обусловлено тем, что в направление связи заранее выделяется определенное количество каналов (ветвей) разнесения и частот, а при изменении условий ведения связи в нескольких направлениях нет возможности перераспределять каналы и частоты между ними для обеспечения связи с требуемым качеством.

Наиболее близким как по количеству сходных признаков, так и по достигаемому техническому результату к заявленному устройству является устройство дискретно-весового сложения разнесенных сигналов (см. А.с. 1660184, Н 04 В 7/02, бюл. 24 от 30.06.91).

Оно содержит блок сумматоров, тактовый блок и N каналов, где N≥2. При этом блок сумматоров включает первый и второй сумматоры, а также решающий элемент. Первый и второй входы решающего элемента соединены соответственно с выходами первого и второго сумматоров, а выход решающего элемента является выходом блока сумматоров, i-й вход первого сумматора и i-й вход второго сумматора, где i = 1, 2,...N, являются соответственно (2i-1)-м и (2i)-м входами блока сумматоров. Тактовый вход решающего элемента является тактовым входом блока сумматоров.

Тактовый блок включает дешифратор, счетчик, элемент задержки, элемент выделения первого отклика и элемент выделения тактовой последовательности. Выход элемента выделения тактовой последовательности подключен к входу счетчика и является первым и четвертым выходами тактового блока. Четвертый выход тактового блока подключен к тактовому входу блока сумматоров. Выходы счетчика подключены к соответствующим входам дешифратора, выход которого является третьим выходом тактового блока. Выход элемента выделения первого отклика подключен к входу элемента задержки. Выход элемента задержки подключен к входу сброса счетчика и является вторым выходом тактового блока. Каждый вход сигнала тактовой частоты элемента выделения тактовой последовательности является соответствующим тактовым входом тактового блока, а каждый вход элемента выделения тактовой последовательности и элемента выделения первого отклика является соответствующим задающим входом тактового блока.

Каждый канал включает дискретный согласованный фильтр, управляемый запоминающий элемент, фазируемый регенератор откликов, формирователь весовых коэффициентов, первый и второй элементы задержки, инвертор, первый и второй перемножители, арифметический делитель, первый, второй и третий ключи, первый и второй регистры, первый и второй счетчики, обнаружитель ошибок, обнаружитель сосредоточенной помехи, переключатель. Выход переключателя соединен с входом второго элемента задержки, выход которого соединен с входом первого ключа. Выход первого ключа соединен с входом первого регистра, выход которого соединен с входом первого счетчика. Выходы первого счетчика соединены с входами делимого арифметического делителя. Выходы второго счетчика соединены с входами делителя арифметического делителя, выход которого соединен с входом третьего ключа. Выход третьего ключа соединен с вторыми входами первого и второго перемножителей, а управляющий вход третьего ключа соединен с последовательным выходом второго регистра.

Выход обнаружителя ошибок соединен с инверсным входом переключателя и с входом обнаружителя сосредоточенной помехи. Выход обнаружителя сосредоточенной помехи соединен с входом второго ключа, выход которого соединен с управляющим входом первого ключа и с входом второго регистра. Выход второго регистра соединен с входом второго счетчика. Информационный вход дискретного согласованного фильтра является информационным входом канала, а тактовый вход дискретного согласованного фильтра является тактовым входом канала. Первый выход дискретного согласованного фильтра подключен к входу фазируемого регенератора откликов и входу формирователя весовых коэффициентов и является синхронизирующим выходом канала. Второй выход дискретного согласованного фильтра подключен к информационному входу управляемого запоминающего элемента, вход записи которого соединен с выходом фазируемого регенератора откликов. Тактовый вход управляемого запоминающего устройства соединен с тактовым входом формирователя весовых коэффициентов и является первым синхронизирующим входом канала, а вход считывания управляемого запоминающего элемента является вторым синхронизирующим входом канала. Выход управляемого запоминающего элемента соединен с входом обнаружителя ошибок и входом первого элемента задержки.

Выход первого элемента задержки соединен с первым входом второго перемножителя и с входом инвертора. Выход инвертора соединен с первым входом первого перемножителя. Выход формирователя весовых коэффициентов соединен с входом переключателя, управляющий вход которого соединен с управляющим входом второго ключа и является третьим синхронизирующим входом канала. Первый и второй выходы i-го канала подключены соответственно к первому и второму входу i-ой группы входов блока сумматоров. Тактовый вход каждого канала подключен к соответствующему тактовому входу тактового блока. Синхронизирующий выход каждого канала подключен к соответствующему задающему входу тактового блока. Первый, второй и третий синхронизирующие входы каждого канала подключены соответственно к первому, второму и третьему выходам тактового блока.

Данное устройство в сравнении с аналогами обеспечивает некоторое повышение помехоустойчивости за счет отключения канала, пораженного сосредоточенной помехой, от блока сумматоров. Это устройство и примем в качестве прототипа.

Недостатком прототипа является низкая эффективность использования канального и аппаратурного ресурсов (ветвей разнесения). Это обусловлено тем, что в направление связи заранее выделяется определенное количество каналов (ветвей) разнесения, а при изменении условий ведения связи в нескольких направлениях нет возможности перераспределять каналы между ними для обеспечения связи с требуемым качеством.

Целью изобретения является разработка устройства сложения разнесенных сигналов для многонаправленной радиосвязи, обеспечивающего более высокую эффективность использования канального и аппаратурного ресурсов за счет перераспределения свободных каналов приема, а также каналов, пораженных сосредоточенной помехой в одном из направлений связи, между другими направлениями связи.

Поставленная цель достигается тем, что в известное устройство, содержащее первый блок сумматоров, включающий первый и второй сумматоры, решающий элемент, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров, выход и тактовый вход решающего элемента являются соответственно выходом и тактовым входом блока сумматоров, i-й вход первого сумматора и i-ый вход второго сумматора, где i=1, 2,...N, a N ≥2, являются соответственно (2i-1)-м и (2i)-м входом блока сумматоров, первый тактовый блок, включающий дешифратор, счетчик, элемент задержки, элемент выделения первого отклика, элемент выделения тактовой последовательности, выход которого подключен к входу счетчика и является первым и четвертым выходами тактового блока, выходы счетчика подключены к соответствующим входам дешифратора, выход элемента выделения первого отклика подключен к входу элемента задержки, выход которого подключен к входу сброса счетчика, каждый вход сигнала тактовой частоты элемента выделения тактовой последовательности является соответствующим тактовым входом тактового блока, а каждый вход элемента выделения тактовой последовательности и элемента выделения первого отклика является соответствующим задающим входом тактового блока, четвертый выход тактового блока соединен с тактовым входом первого блока сумматоров.

Выход элемента задержки является вторым выходом тактового блока, выход дешифратора является третьим выходом тактового блока, N каналов, где N≥2, каждый из которых включает дискретный согласованный фильтр, управляемый запоминающий элемент, фазируемый регенератор откликов, формирователь весовых коэффициентов, первый и второй элементы задержки, инвертор, первый и второй перемножители, арифметический делитель, первый, второй и третий ключи, первый и второй регистры, первый и второй счетчики, обнаружитель ошибок, обнаружитель сосредоточенной помехи, переключатель, выход которого соединен с входом второго элемента задержки, выход которого соединен с входом первого ключа, выход которого соединен с входом первого регистра, выход которого соединен с входом первого счетчика, выходы которого соединены с входами делимого арифметического делителя, выходы второго счетчика соединены с входами делителя арифметического делителя, выход которого соединен с входом третьего ключа, выход которого соединен с вторыми входами первого и второго перемножителей.

Управляющий вход третьего ключа соединен с последовательным выходом второго регистра, информационный вход дискретного согласованного фильтра является информационным входом канала, а тактовый вход дискретного согласованного фильтра является тактовым входом канала, первый выход дискретного согласованного фильтра подключен к входу фазируемого регенератора откликов и входу формирователя весовых коэффициентов и является синхронизирующим выходом канала, а второй выход дискретного согласованного фильтра подключен к информационному входу управляемого запоминающего элемента, вход записи которого соединен с выходом фазируемого регенератора откликов, тактовый вход управляемого запоминающего устройства соединен с тактовым входом формирователя весовых коэффициентов и является первым синхронизирующим входом канала, а вход считывания управляемого запоминающего элемента является вторым синхронизирующим входом канала, выход управляемого запоминающего элемента соединен с входом обнаружителя ошибок и входом первого элемента задержки, выход которого соединен с первым входом второго перемножителя и с входом инвертора, выход которого соединен с первым входом первого перемножителя, выход формирователя весовых коэффициентов соединен с входом переключателя, управляющий вход которого соединен с управляющим входом второго ключа и является третьим синхронизирующим входом канала.

Выходы первого и второго перемножителей являются соответственно первым и вторым выходами канала, выход обнаружителя ошибок соединен с инверсным входом переключателя и с входом обнаружителя сосредоточенной помехи, выход которого соединен с входом второго ключа, выход которого соединен с управляющим входом первого ключа и с входом второго регистра, выход которого соединен с входом второго счетчика, дополнительно введены L-1 блоков сумматоров, где N≥L≥2, L-1 тактовых блоков, коммутатор информационных сигналов, блок управления и коммутатор тактовых импульсов.

В каждом канале последовательный выход второго регистра является сигнальным выходом канала и подключен к соответствующему входу блока управления. Тактовый вход каждого канала подключен к соответствующему тактовому входу коммутатора тактовых импульсов, а синхронизирующий выход каждого канала подключен к соответствующему канальному входу коммутатора тактовых импульсов. Первый, второй и третий синхронизирующие входы i-го канала, где i=1, 2,...N, подключены соответственно к первому, второму и третьему выходам i-й группы канальных выходов коммутатора тактовых импульсов. Первый и второй выходы i-го канала, где i=1, 2,...N, подключены соответственно к первому и второму входам соответствующей i-ой группы информационных входов коммутатора информационных сигналов, i-я группа выходов блока управления подключена к соответствующей i-й группе управляющих входов коммутатора тактовых импульсов и коммутатора информационных сигналов. N выходов j-й группы тактовых выходов коммутатора тактовых импульсов, где j=1, 2,...L, подключены соответственно к N тактовым входам j-го тактового блока, а N выходов j-ой группы задающих выходов коммутатора тактовых импульсов подключены соответственно к N задающим входам соответствующего j-го тактового блока. Первый, второй и третий выходы j-го тактового блока подключены соответственно к первому, второму и третьему входам j-й группы задающих входов коммутатора тактовых импульсов. Четвертый выход каждого тактового блока подключен к тактовому входу соответствующего блока сумматоров. 2N выходов j-й группы выходов коммутатора информационных сигналов подключены к соответствующим 2N входам j-го блока сумматоров.

Благодаря новой совокупности существенных признаков за счет введения дополнительных блоков обеспечивается возможность перераспределения свободных каналов приема, а также каналов, пораженных сосредоточенной помехой в одном из направлений связи, между другими направлениями связи.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявляемое устройство поясняется чертежами, на которых:

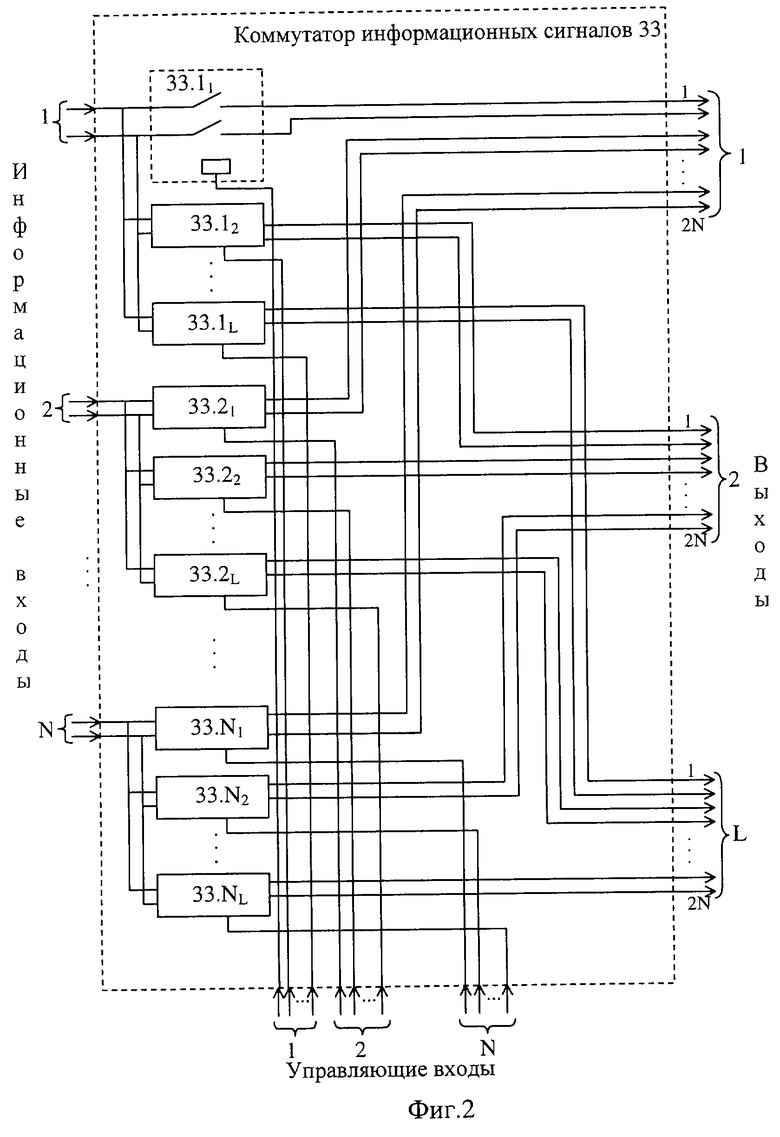

на фиг. 1 показана функциональная схема устройства дискретно-весового сложения разнесенных сигналов;

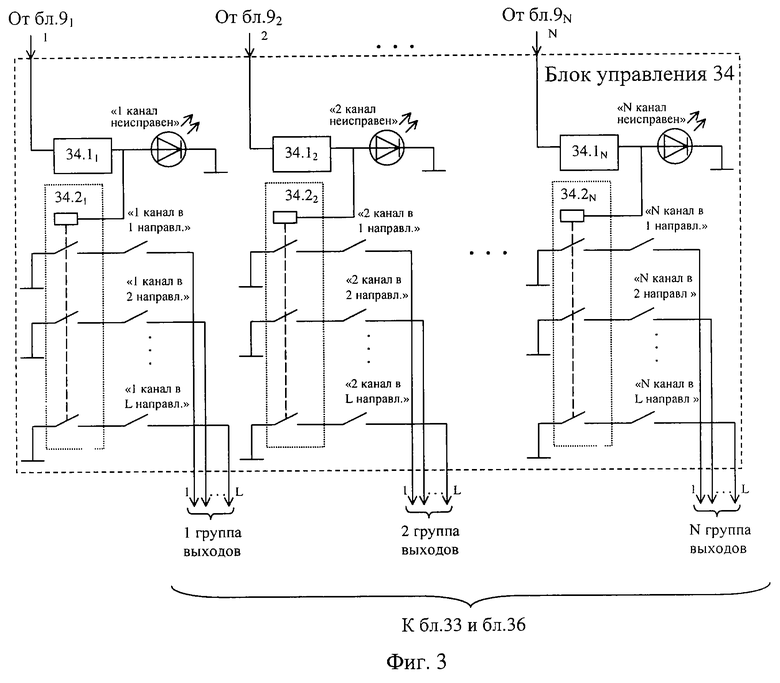

на фиг.2 - схема коммутатора информационных сигналов 33;

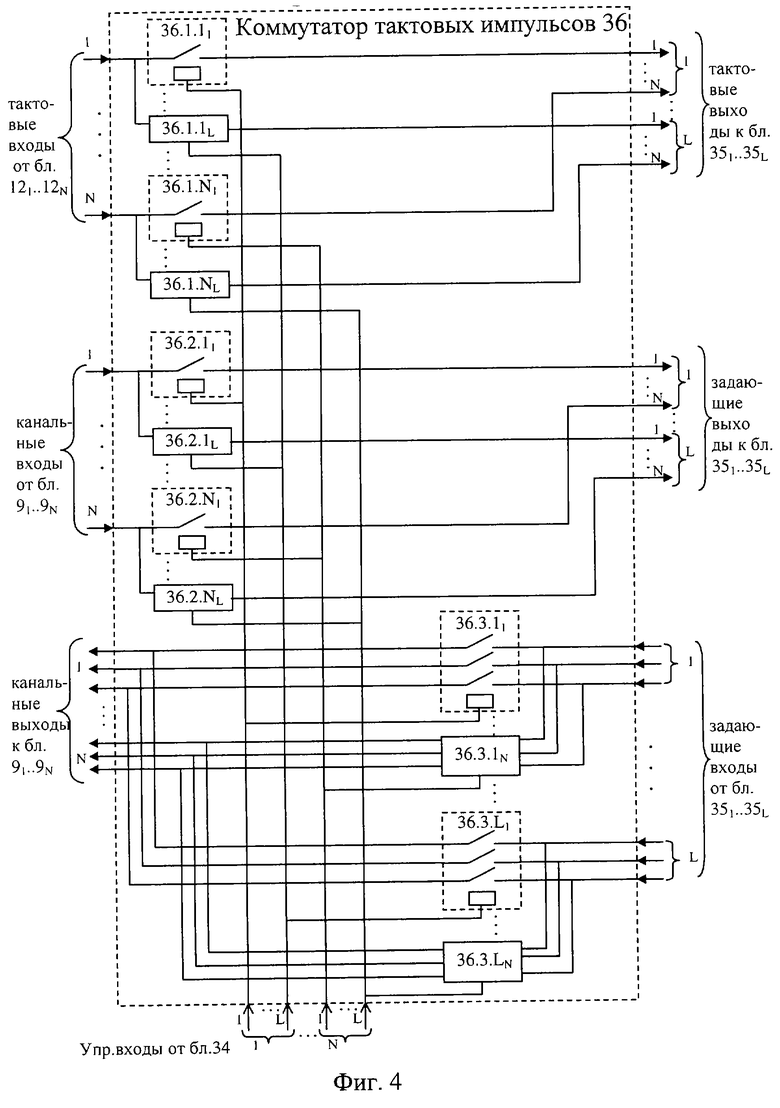

на фиг.3 - схема блока управления 34;

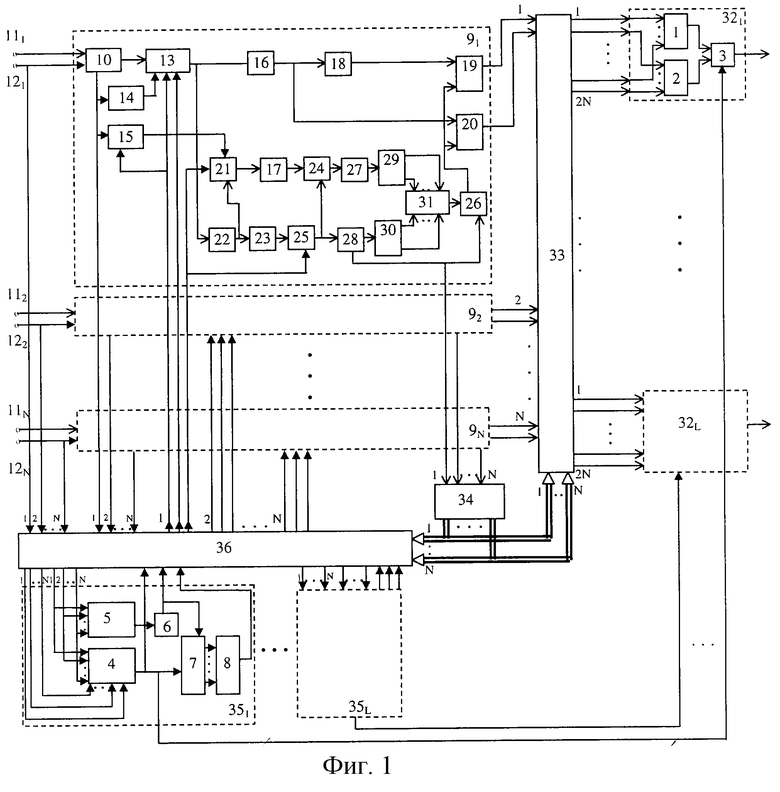

на фиг.4 - схема коммутатора тактовых импульсов 36.

Заявляемое устройство, показанное на фиг.1, состоит из N каналов 91... 9N, L блоков сумматоров 321...32L,L тактовых блоков 351...35L коммутатора информационных сигналов 33, блока управления 34, коммутатора тактовых импульсов 36. Причем каждый канал 9 содержит дискретный согласованный фильтр 10, управляемый запоминающий элемент 13, фазируемый регенератор откликов 14, формирователь весовых коэффициентов 15, первый элемент задержки 16, инвертор 18, первый 19 и второй 20 перемножители, арифметический делитель 31, третий ключ 26, последовательно соединенные переключатель 21, второй элемент задержки 17, первый ключ 24, первый регистр 27 и первый счетчик 29, последовательно соединенные обнаружитель ошибок 22, обнаружитель сосредоточенной помехи 23, второй ключ 25, второй регистр 28 и второй счетчик 30. Выходы второго счетчика 30 соединены с входами делителя арифметического делителя 31, выход которого соединен с входом третьего ключа 26. Выход третьего ключа 26 соединен с вторыми входами первого 19 и второго перемножителей 20. Управляющий вход третьего ключа 26 соединен с последовательным выходом второго регистра 28 и является сигнальным выходом канала 9.

Выход обнаружителя ошибок 22 соединен с инверсным входом переключателя 21 и с входом обнаружителя сосредоточенной помехи 23. Выход обнаружителя сосредоточенной помехи 23 соединен с входом второго ключа 25, выход которого соединен с управляющим входом первого ключа 24 и с входом второго регистра 28. Выход второго регистра 28 соединен с входом второго счетчика 30. Выход переключателя 21 соединен с входом второго элемента задержки 17, выход которого соединен с входом первого ключа 24. Выход первого ключа 24 соединен с входом первого регистра 27, выход которого соединен с входом первого счетчика 29. Выходы первого счетчика 29 соединены с входами делимого арифметического делителя 31. Информационный вход дискретного согласованного фильтра 10 является информационным входом канала 11, а тактовый вход дискретного согласованного фильтра 10 является тактовым входом канала 12. Первый выход дискретного согласованного фильтра 10 подключен к входу фазируемого регенератора откликов 14 и входу формирователя весовых коэффициентов 15 и является синхронизирующим выходом канала 9. Второй выход дискретного согласованного фильтра 10 подключен к информационному входу управляемого запоминающего элемента 13, вход записи которого соединен с выходом фазируемого регенератора откликов 14.

Тактовый вход управляемого запоминающего устройства 13 соединен с тактовым входом формирователя весовых коэффициентов 15 и является первым синхронизирующим входом канала 9. Вход считывания управляемого запоминающего элемента 13 является вторым синхронизирующим входом канала 9. Выход управляемого запоминающего элемента 13 соединен с входом обнаружителя ошибок 22 и входом первого элемента задержки 16. Выход первого элемента задержки 16 соединен с первым входом второго перемножителя 20 и с входом инвертора 18. Выход инвертора 18 соединен с первым входом первого перемножителя 19. Выход формирователя весовых коэффициентов 15 соединен с входом переключателя 21, управляющий вход которого соединен с управляющим входом второго ключа 25 и является третьим синхронизирующим входом канала 9. Выходы первого 19 и второго 20 перемножителей являются соответственно первым и вторым выходами канала 9.

Каждый блок сумматоров 32 содержит первый 1 и второй 2 сумматоры, решающий элемент 3. Первый и второй входы решающего элемента 3 соединены соответственно с выходами первого 1 и второго 2 сумматоров, а его выход является выходом блока сумматоров 32. i-й вход первого сумматора 1 и i-й вход второго сумматора 2, где i=1, 2,...N, a N≥2 являются соответственно (2i-1)-м и 2i-м входом блока сумматоров 32. Тактовый вход решающего элемента 3 является тактовым входом блока сумматоров 32.

Каждый тактовый блок 35 включает дешифратор 8, счетчик 7, элемент задержки 6, элемент выделения первого отклика 5 и элемент выделения тактовой последовательности 4. Выход элемента выделения тактовой последовательности 4 подключен к входу счетчика 7 и является первым и четвертым выходами тактового блока 35. Выходы счетчика 7 подключены к соответствующим входам дешифратора 8, выход которого является третьим выходом тактового блока 35. Выход элемента выделения первого отклика 5 подключен к входу элемента задержки 6. Выход элемента задержки 6 подключен к входу сброса счетчика 7 и является вторым выходом тактового блока 35. Каждый вход сигнала тактовой частоты элемента выделения тактовой последовательности 4 является соответствующим тактовым входом тактового блока 35, а каждый вход элемента выделения тактовой последовательности 4 и элемента выделения первого отклика 5 является соответствующим задающим входом тактового блока 35. Четвертый выход каждого тактового блока 35 подключен к тактовому входу соответствующего блока сумматоров 32.

Сигнальный выход каждого канала 9 подключен к соответствующему входу блока управления 34. Тактовый вход каждого канала 9 подключен к соответствующему тактовому входу коммутатора тактовых импульсов 36, а синхронизирующий выход каждого канала 9 подключен к соответствующему канальному входу коммутатора тактовых импульсов 36. Первый, второй и третий синхронизирующие входы i-го канала 9, где i=1, 2,...N, подключены соответственно к первому, второму и третьему выходам i-й группы канальных выходов коммутатора тактовых импульсов 36. Первый и второй выходы i-го канала 9 подключены соответственно к первому и второму входам соответствующей i-ой группы информационных входов коммутатора информационных сигналов 33. i-я группа выходов блока управления 34 подключена к соответствующей i-й группе управляющих входов коммутатора тактовых импульсов 36 и коммутатора информационных сигналов 33. N тактовых выходов j-ой группы тактовых выходов коммутатора тактовых импульсов 36, где j=1, 2,...L, подключены к соответствующим N тактовым входам соответствующего j-го тактового блока 35j, a N задающих выходов j-й группы задающих выходов коммутатора тактовых импульсов 36 подключены к N задающим входам соответствующего j-го тактового блока 35j. Первый, второй и третий выходы j-го тактового блока 35j подключены соответственно к первому, второму и третьему входам j-ой группы задающих входов коммутатора тактовых импульсов 36. 2N выходов j-й группы выходов коммутатора информационных сигналов 33 подключены к соответствующим 2N входам j-го блока сумматоров 32j.

Коммутатор информационных сигналов 33 предназначен для подключения его первого и второго входов i-й группы информационных входов к определяемым в соответствии с управляющими командами (2i-1)-му и 2i-му выходам j-й группы выходов. Коммутатор информационных сигналов 33 показан на фиг.2 и состоит из N групп управляемых ключей по L в каждой группе 33.11..L...33.N1..L. Он имеет N парных информационных входов, N групп управляющих входов по L входов в каждой группе и L групп выходов по 2N выходов в каждой группе. При этом первый и второй входы i-ой группы информационных входов коммутатора информационных сигналов 33 являются соответственно первым и вторым входами всех L ключей i-ой группы управляемых ключей 33.i1...33.iL, где i=1, 2,...N, j=1, 2,.. . L. Управляющий вход j-го ключа i-й группы управляемых ключей 33.i1...33.iL является j-м управляющим входом i-й группы управляющих входов коммутатора информационных сигналов 33. Парный выход j-го ключа i-й группы управляемых ключей 33. i1...33.iL является i-м парным выходом j-й группы выходов коммутатора информационных сигналов 33.

Управляемые ключи 33.11..L...33.N1..L предназначены для подключения первого и второго своих входов (пары входов) к первому и второму выходам (паре выходов) соответственно при подаче управляющего напряжения на управляющий вход. Схемы построения управляемых ключей 33.11..L..., 33.N1..L известны и описаны, они могут быть построены на микросхемах КР143КТ1 (см. Вениаминов В. Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 66-69).

Блок управления 34 предназначен для подачи управляющих напряжений на коммутаторы информационных сигналов 33 и тактовых импульсов 36 с целью подключения свободных и не пораженных сосредоточеными помехами каналов в требуемые направления связи, т.е. к необходимым блокам сумматоров (i-го канала 9i к j-му блоку сумматоров 32j). Управление коммутаторами может осуществляться как автоматически с использованием микропроцессора, так и с помощью оператора. В случае управления коммутаторами с помощью оператора блок управления 34 может быть реализован, например, как показано на фиг.3. При этом он состоит из N инверторов 34.11...34.1n, N управляемых ключей 34.21...34.2N, N светодиодов "i-й канал неисправен" и N групп выключателей "i-й канал в j-e направление" по L в каждой группе.

Причем i-й вход блока управления 34 является входом i-го инвертора 34.1i, выход которого подключен к соответствующему i-му светодиоду и является управляющим входом i-го управляемого ключа 34.2i. К j-му входу i-го управляемого ключа 34.2i может быть подключен, например, "корпус". Через соответствующий выключатель "i-й канал в j-e направление" j-й выход i-го управляемого ключа 34.2i подключен к j-му выходу i-й группы выходов блока управления 34.

Инверторы 34.11..N предназначены для преобразования поступающего на их вход напряжения низкого уровня (сигнала "0" из блоков 91..N) при поражении сосредоточенной помехой одного из каналов в напряжение высокого уровня на выходе (>1 В). Инверторы 34.11..N известны и описаны. Они могут быть реализованы, например, на микросхеме К555ЛА13, описанной - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, c.196-197.

Управляемые ключи 34.21..N предназначены для отключения своих L входов от соответствующих L выходов при подаче управляющего напряжения на управляющий вход. Схемы построения управляемых ключей 34.21..N известны и описаны, они могут быть реализованы на микросхемах 435КН1 (см. Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с.66-69).

Выключатели "i-й канал в j-e направление" представляют собой кнопки со световой индикацией при их нажатии и могут быть объединены в единое световое табло.

Коммутатор тактовых импульсов 36 предназначен для подключения i-гo входа группы тактовых входов к i-му выходу j-й группы тактовых выходов (одной из L), i-гo входа группы канальных входов - к i-му выходу j-й группы задающих выходов и j-й группы задающих входов - к i-й группе канальных выходов (одной или нескольким из N). Коммутатор тактовых импульсов 36 показан на фиг.4 и состоит из N групп управляемых ключей по L в каждой группе 36.1.11..L... 36.1. N1..L, N групп управляемых ключей по L в каждой группе 36.2.11..L... 36.2. N1..L и L групп управляемых ключей по N в каждой группе 36.3.11..N... 36.3.L1..N. При этом i-й вход группы тактовых входов подключен к входам всех L управляемых ключей i-й группы управляемых ключей 36.1.i1...36.1.iL, выход j-го управляемого ключа i-й группы управляемых ключей 36.1.ij, является i-м выходом j-й группы тактовых выходов коммутатора тактовых импульсов 36. i-й вход группы канальных входов коммутатора тактовых импульсов 36 подключен к входам всех L управляемых ключей i-й группы управляемых ключей 36.2.i1... 36.2.iL, а выход j-го управляемого ключа i-й группы управляемых ключей 36.2. ij является i-м выходом j-й группы задающих выходов коммутатора тактовых импульсов 36.

Первый, второй и третий входы j-й группы задающих входов коммутатора тактовых импульсов 36 подключены соответственно к первому, второму и третьему входам всех N управляемых ключей j-й группы управляемых ключей 36.3.j1. . . 36.3. jN, а первый, второй и третий выходы i-го управляемого ключа j-й группы управляемых ключей 36.3.ji является соответственно первым, вторым и третьим выходами i-й группы канальных выходов коммутатора тактовых импульсов 36. j-й управляющий вход i-ой группы управляющих входов коммутатора тактовых импульсов 36 подключен к управляющему входу j-го управляемого ключа i-й группы управляемых ключей 36.1. ij и 36.2.ij а также к управляющему входу i-го ключа j-й группы управляемых ключей 36.3.ji.

Управляемые ключи 36.1.11..L. . . 36.1.N1..L и 36.2.11..L...36.2.N1..L предназначены для подключения своего входа к выходу при подаче управляющего напряжения на управляющий вход. Схемы построения управляемых ключей 36.1.11..L. . . 36.1.N1..L и 36.2.11..L...36.2.N1..L известны и описаны. Они могут быть реализованы, например, на микросхемах К265КН1 (см. Вениаминов В. Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с.66-69).

Управляемые ключи 36.3.11..N...36.3.L1..N предназначены для подключения своих первого, второго и третьего входов к первому, второму и третьему выходам соответственно при подаче управляющего напряжения на управляющий вход. Схемы построения управляемых ключей 36.3.11..N. . .36.3.L1..N известны и описаны. Они могут быть реализованы, например, на микросхемах К168КТ2 (см. Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с.66-69).

Заявляемое устройство работает следующим образом. Перед началом работы оператор или микропроцессор (МП) выбирает определенное количество каналов (ветвей разнесения) nj из N с целью обеспечения требуемого качества приема сообщений для каждого j-го направления связи из L направлений. По командам оператора (с помощью выключателей) или МП блок управления 34 подает управляющие напряжения на соответствующие управляемые ключи коммутатора информационных сигналов 33 и коммутатора тактовых импульсов 36. С помощью коммутатора информационных сигналов 33 пара канальных выходов каждого канала 9 из числа nj выбранных для j-го направления связи каналов подключается к соответствующему блоку сумматоров 32j. Для обеспечения тактовой синхронизации выбранных каналов по ведущему каналу они с помощью коммутатора тактовых импульсов 36 подключаются также к соответствующему тактовому блоку 35j. При этом тактовые входы всех nj выбранных каналов 9 подключаются к соответствующим тактовым входам тактового блока 35j, а синхронизирующие выходы всех nj выбранных каналов 9 - к задающим входам тактового блока 35j.

В свою очередь, первый, второй и третий задающие выходы блока 35j подключаются соответственно к первому, второму и третьему синхронизирующим входам всех nj, выбранных каналов 9. Возможна ситуация, когда в j-м направлении связи не обеспечивается требуемое качество приема сообщений и при этом имеются свободные каналы 9. В этом случае для обеспечения требуемого качества приема в это направление также с помощью блока управления 34, коммутатора информационных сигналов 33 и коммутатора тактовых импульсов 36 можно подключить дополнительные каналы 9 из числа свободных.

При поражении сосредоточенной помехой одного из nj каналов 9 этот канал не участвует в сложении в j-м блоке сумматоров 32j и через сигнальный выход в блок управления 34 поступает соответствующий сигнал (низкого уровня) о том, что канал неисправен. С помощью блока управления 34 этот канал отключается от j-го блока сумматоров 32j. Если это, например, радиоканал, то его могут перестроить на другую частоту с целью избежать воздействия сосредоточенной помехи и использовать в дальнейшем как свободный.

Для того, чтобы обеспечить требуемое качество связи в j-м направлении при отключении одного из каналов (ветвей разнесения), оператор или МП может подключить один или несколько каналов, из числа свободных на данный момент, для чего оператор выбирает канал и с помощью выключателей "i-й канал в j-e направление" подает управляющее напряжение на j-й выход соответствующей i-й группы выходов блока управления 34. Далее это напряжение поступает на соответствующие управляемые ключи в коммутатор информационных сигналов 33 и коммутатор тактовых импульсов 36. С их помощью подключаются необходимые входы и выходы выбранного канала 9 к блоку сумматоров 32j и тактовому блоку 35j j-го направления связи.

Блок управления 34 работает следующим образом. В исходном положении (при отсутствии сосредоточенных помех) при наличии напряжения высокого уровня от i-го канала 9i все L контакты соответствующего i-го ключа 34.2i замкнуты. Если оператор с помощью выключателя "i-й канал в j-e направление" подключает i-й канал в j-e направление связи, то управляющее напряжение ("корпус") через замкнутые контакты соответствующего ключа 34.2i и соответствующего выключателя "i-й канал в j-e направление" поступает на j-й выход i-й группы выходов и далее на управляющие входы в коммутатор информационных сигналов 33 и коммутатор тактовых импульсов 36. При поражении сосредоточенной помехой i-го канала 9i с его сигнального выхода сигнал низкого уровня поступает на соответствующий i-й вход блока управления 34. С помощью инвертора это напряжение преобразуется в напряжение высокого уровня, включается светодиод "i-й канал неисправен" и размыкаются контакты i-го ключа 34.2i Управляющее напряжение на выходах i-й группы выходов блока управления 34 отсутствует, подсветка соответствующего выключателя "i-ый канал в j-e направление" гаснет и данный канал отключается oт j-гo блока сумматоров 32j.

Таким образом, предложенное устройство повышает эффективность использования канального и аппаратурного ресурсов, так как в нем имеется возможность перераспределять свободные каналы (ветви разнесения) между направлениями связи, качество связи в которых не обеспечивается выделенными в них каналами. При этом пораженные сосредоточенными помехами каналы можно отключать, а если это, например, радиоканалы, то перестраивать их на другие частоты и в дальнейшем использовать как свободные.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ КОММУТАЦИИ КАНАЛОВ СВЯЗИ | 1998 |

|

RU2143788C1 |

| Устройство для мажоритарного декодирования двоичных кодов | 1982 |

|

SU1077050A1 |

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Система контроля каналов связи многопрограммного проводного вещания | 1983 |

|

SU1145481A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| СПОСОБ ОБРАБОТКИ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ СО СЛОЖНЫМ ЗАКОНОМ МОДУЛЯЦИИ | 2001 |

|

RU2293356C2 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

Изобретение относится к технике радиосвязи. Сущность изобретения: разработка устройства сложения разнесенных сигналов, обеспечивающего более высокую эффективность использования канального и аппаратурного ресурсов за счет перераспределения свободных каналов приема. Технический результат достигается благодаря введению дополнительных L-1 тактовых блоков, L-1 блоков сумматоров, коммутатора информационных сигналов, коммутатора тактовых импульсов и блока управления. Информационные выходы одного или нескольких свободных каналов по команде блока управления с помощью коммутатора информационных сигналов могут подключаться к блоку сумматоров того направления связи, в котором не обеспечивается заданное качество приема сообщений. 4 ил.

Устройство дискретно-весового сложения разнесенных сигналов, содержащее первый блок сумматоров, включающий первый и второй сумматоры, решающий элемент, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров, выход и тактовый вход решающего элемента являются соответственно выходом и тактовым входом блока сумматоров, i-й вход первого сумматора и i-й вход второго сумматора, где i=l,2,...N, a N≥2, являются соответственно (2i-1)-ым и (2i)-ым входами блока сумматоров, первый тактовый блок, включающий дешифратор, счетчик, элемент задержки, элемент выделения первого отклика, элемент выделения тактовой последовательности, выход которого подключен к входу счетчика и является первым и четвертым выходами тактового блока, выходы счетчика подключены к соответствующим входам дешифратора, выход элемента выделения первого отклика подключен к входу элемента задержки, выход которого подключен к входу сброса счетчика, каждый вход сигнала тактовой частоты элемента выделения тактовой последовательности является соответствующим тактовым входом тактового блока, а каждый вход элемента выделения тактовой последовательности и элемента выделения первого отклика является соответствующим задающим входом тактового блока, четвертый выход тактового блока соединен с тактовым входом первого блока сумматоров, выход элемента задержки является вторым выходом тактового блока, выход дешифратора является третьим выходом тактового блока, N каналов, каждый из которых включает дискретный согласованный фильтр, управляемый запоминающий элемент, фазируемый регенератор откликов, формирователь весовых коэффициентов, первый и второй элементы задержки, инвертор, первый и второй перемножители, арифметический делитель, первый, второй и третий ключи, первый и второй регистры, первый и второй счетчики, обнаружитель ошибок, обнаружитель сосредоточенной помехи, переключатель, выход которого соединен с входом второго элемента задержки, выход которого соединен с входом первого ключа, выход которого соединен с входом первого регистра, выход которого соединен с входом первого счетчика, выходы которого соединены с входами делимого арифметического делителя, выходы второго счетчика соединены с входами делителя арифметического делителя, выход которого соединен с входом третьего ключа, выход которого соединен с вторыми входами первого и второго перемножителей, управляющий вход третьего ключа соединен с последовательным выходом второго регистра, информационный вход дискретного согласованного фильтра является информационным входом канала, а тактовый вход дискретного согласованного фильтра является тактовым входом канала, первый выход дискретного согласованного фильтра подключен к входу фазируемого регенератора откликов и входу формирователя весовых коэффициентов и является синхронизирующим выходом канала, а второй выход дискретного согласованного фильтра подключен к информационному входу управляемого запоминающего элемента, вход записи которого соединен с выходом фазируемого регенератора откликов, тактовый вход управляемого запоминающего элемента соединен с тактовым входом формирователя весовых коэффициентов и является первым синхронизирующим входом канала, а вход считывания управляемого запоминающего элемента является вторым синхронизирующим входом канала, выход управляемого запоминающего элемента соединен с входом обнаружителя ошибок и входом первого элемента задержки, выход которого соединен с первым входом второго перемножителя и с входом инвертора, выход которого соединен с первым входом первого перемножителя, выход формирователя весовых коэффициентов соединен с входом переключателя, управляющий вход которого соединен с управляющим входом второго ключа и является третьим синхронизирующим входом канала, выходы первого и второго перемножителей являются соответственно первым и вторым выходами канала, выход обнаружителя ошибок соединен с инверсным входом переключателя и с входом обнаружителя сосредоточенной помехи, выход которого соединен с входом второго ключа, выход которого соединен с управляющим входом первого ключа и с входом второго регистра, выход которого соединен с входом второго счетчика, отличающееся тем, что дополнительно введены L-1 блоков сумматоров, где N≥L≥2, L-1 тактовых блоков, коммутатор информационных сигналов, блок управления, коммутатор тактовых импульсов, в каждом канале последовательный выход второго регистра является сигнальным выходом канала и подключен к соответствующему входу блока управления, тактовый вход каждого канала подключен к соответствующему тактовому входу коммутатора тактовых импульсов, синхронизирующий выход каждого канала подключен к соответствующему канальному входу коммутатора тактовых импульсов, первый, второй и третий синхронизирующие входы i-го канала подключены соответственно к первому, второму и третьему выходам i-й группы канальных выходов коммутатора тактовых импульсов, первый и второй выходы i-го канала подключены соответственно к первому и второму входам соответствующей i-й группы информационных входов коммутатора информационных сигналов, i-я группа выходов блока управления подключена к соответствующей i-й группе управляющих входов коммутатора тактовых импульсов и коммутатора информационных сигналов, N выходов j-й группы тактовых выходов, где j=l,2,...L, коммутатора тактовых импульсов подключены соответственно к N тактовым входам j-го тактового блока, N выходов j-й группы задающих выходов коммутатора тактовых импульсов подключены соответственно к N задающим входам j-го тактового блока, первый, второй и третий выходы j-го тактового блока подключены соответственно к первому, второму и третьему входам j-й группы задающих входов коммутатора тактовых импульсов, четвертый выход каждого тактового блока подключен к тактовому входу соответствующего блока сумматоров, 2N выходов j-й группы выходов коммутатора информационных сигналов подключены к соответствующим 2N входам j-го блока сумматоров.

| Устройство дискретно-весового сложения разнесенных сигналов | 1988 |

|

SU1660184A1 |

| Устройство для разнесенного приема телеграфных сигналов | 1985 |

|

SU1292195A1 |

| Устройство выбора каналов для разнесенного приема | 1988 |

|

SU1525925A1 |

| US 5444745 А, 22.08.1995 | |||

| US 5787131 А, 28.07.1998 | |||

| ВЕНИАМИНОВ В.Н | |||

| и др | |||

| Микросхемы и их применение (Справочное пособие) | |||

| - М.: Радио и связь, 1983, с.66-69, 196 и 197. | |||

Авторы

Даты

2003-12-27—Публикация

2002-04-29—Подача