Изобретение относится к вычислительной технике и может быть использовано для подключения периферийных устройств с шиной типа И41 к электронным цифровым машинам (например, персональной ЭВМ ЕС1840), имеющим выходной интерфейс стык С2 (Р-232), причем оба устройства, периферийное устройство и ЭВМ, могут быть расположены на больших расстояниях друг от друга.

Известно устройство сопряжения [1], содержащее ЭВМ, устройство управления, терминальные устройства, причем устройство управления содержит регистр команд, блок управления с использованием команд записи после считывания, блок записи, блок считывания, регистр адресации памяти, счетчик байтов.

Недостатками данного устройства являются большая сложность, для реализации его работы необходима ЭВМ, недостаточное быстродействие, отсутствие автоматизации процесса передачи информации.

Наиболее близким к данному является устройство сопряжения интерфейсов [2] , содержащее узел начального сброса, две схемы укорочения длительности импульсов, два делителя числа импульсов, тактовый генератор, пять элементов И-НЕ, пять триггеров, шесть регистров, элементы приема и передачи информации, элементы И, ИЛИ-НЕ.

Недостаток этого устройства - большие аппаратурные затраты.

Целью изобретения является сокращение аппаратурных затрат устройства.

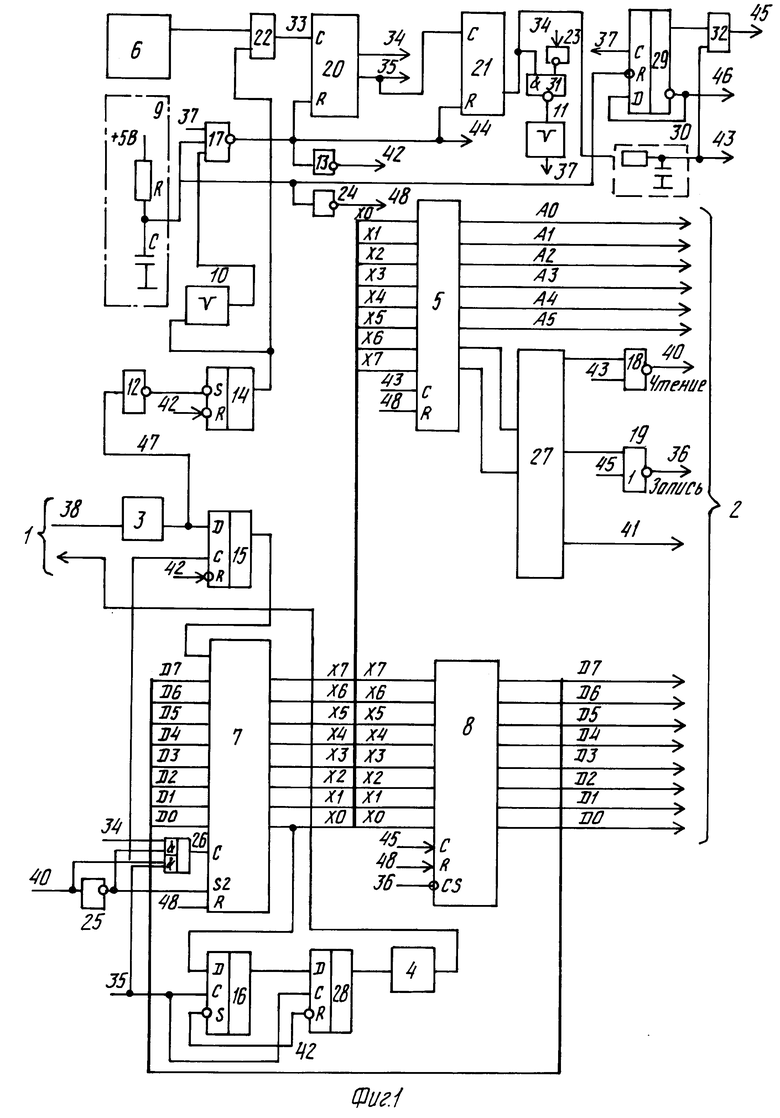

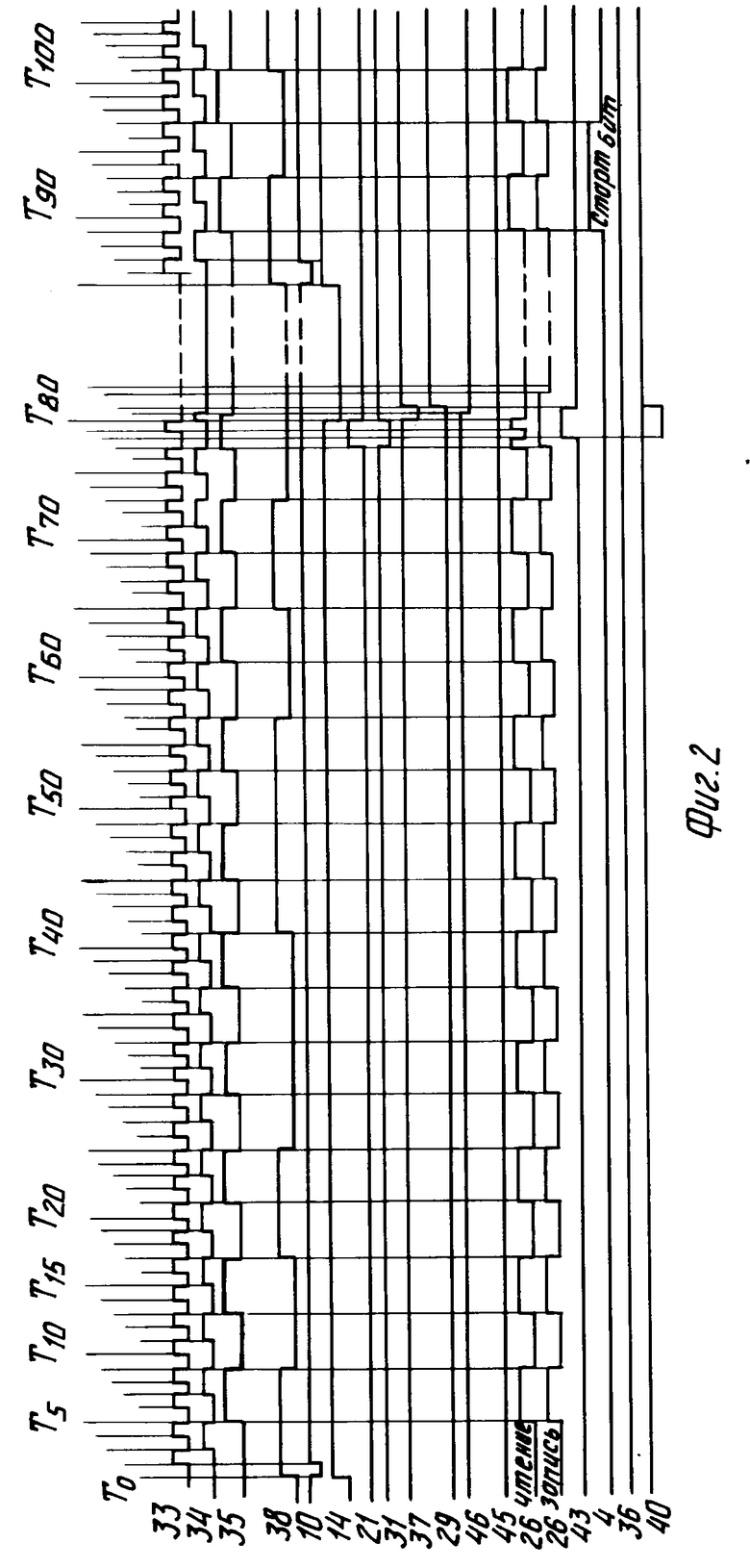

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временная диаграмма его работы.

Устройство содержит (фиг. 1) шины 1 и 2 первого и второго интерфейсов, элементы 3 и 4 приема и передачи информации, регистр 5 адреса, тактовый генератор 6, регистры 7 и 8 приема и передачи данных, узел 9 начального сброса, узлы (схемы) 10 и 11 укорочения длительности импульса, элементы НЕ 12 и 13, триггеры 14, 15 и 16, элементы И-НЕ 17, 18 и 19, делители 20 и 21 числа импульсов, элемент И 22, третий элемент НЕ 23, пятый и четвертый элементы НЕ 24 и 25, элемент И-ИЛИ 26, дешифратор 27, триггеры 28 и 29, элемент 30 задержки, четвертый элемент И-НЕ 31, второй элемент И 32, линии 33-48 входов и выходов элементов устройства.

Устройство работает следующим образом.

Предположим в момент ТO устройство находится в исходном состоянии (фиг. 2), т.е. после включения питания узел 9 начальной установки устанавливает в исходное состояние все триггеры и регистры устройства. В момент Т1 на вход 38 приходит первый байт информации, начинающийся положительным стартовым импульсом, который, пройдя через элемент 3 приема и элемент НЕ 12, устанавливает триггер 14 в единичное состояние. Высокий потенциал с выхода триггера 14 разрешает прохождение импульсов с генератора 6 через элемент И 22 и вызывает на выходе схемы 10 узкий отрицательный импульс, который формирует на выходе элемента И-НЕ 17 узкий положительный импульс. Этот импульс поступает на входы делителей 20 и 21 и устанавливает их в нулевое состояние, а пройдя через элемент НЕ 13, обнуляет триггеры 14, 15, 16 и 28. В момент Т2 на вход элемента И 22 приходит положительный импульс с генератора 6 и на выходе элемента И 22 появляется положительный импульс, по заднему фронту которого на выходе 34 первого разряда делителя 20 появляется положительный импульс. По заднему фронту этого импульса устанавливается в "1" второй разряд первого делителя. По переднему фронту положительного импульса на выходе 35 делителя 20, а затем и девяти следующих за ним импульсов информации (сначала первый стартовый, а затем информационные и стоповый биты) запоминаются в триггере 15, регистре 7 и триггере 16, причем в момент Т77 в триггере 16 находится "1", а в регистре 7 - код, причем в разрядах, расположенных на фиг. 1 ниже, младшие разряды принимаемого кода (в нашем случае на фиг. 2 код 11110010). Кроме того, импульс с выхода 35 делителя 20 поступает на вход делителя 21 и по переднему фронту десятого импульса на выходе делителя 21 появляется положительный импульс в момент Т77, который устанавливает триггер 29 в "1", а также поступает на вход элемента 30 задержки.

Сигналы с выхода элемента 30 задержки и единичного выхода триггера 29 поступают на вход элемента И 32, на выходе которого с момента Т78 по момент Т83 будет высокий потенциал. Этот потенциал поступает на вход элемента И-НЕ 19, а также на вход С регистра 5 и переписывает код с регистра 7 в регистр 5. Если в двух старших разрядах принимаемого кода код 01, т.е. в управляющих разрядах код чтения информации (01 - чтение, 10 - запись, 11 - начальная установка), то срабатывает первый выход дешифратора и на выходе 40 элемента И-НЕ 18 появляется отрицательный импульс, являющийся сигналом чтения для второго интерфейса. Этот отрицательный импульс, кроме того, поступает на вход элемента И-ИЛИ 26, запрещая прохождение через него положительного импульса с шины 35. Кроме того, этот импульс проходит через элемент НЕ 25 и разрешает прохождение стробирующего импульса с выхода элемента И-ИЛИ 26 на вход регистра 7.

На выходе элемента И-НЕ 31 в момент Т80 появляется положительный потенциал, который поступает на вход схемы 11. Сформированный схемой 11 узкий отрицательный импульс поступает на вход элемента И-НЕ 17, сигналы с выхода которого и элемента НЕ 13 устанавливают делители 20, 21 и триггеры 14,15, 28 в нулевое состояние, а триггер 16 в единичное, и считанная информация с второго интерфейса запоминается в регистре 7.

Затем с момента Т89 по момент Т101 с триггеров 15, 16, 28 и регистра 7 поступают десять положительных импульсов на выход 39 элемента 4 передачи, формируя принятый последовательный код, причем вначале идет стартовый бит, а затем информационные, начиная с младшего, а в конце идет стоповый бит.

Если в управляющем слове, т.е. в первом байте, получаемом по интерфейсу 1, в старших разрядах код 10 (остальные разряды кода адреса), то это для интерфейса 2 характерен режим записи. В момент Т102 на выходе 45 элемента И 32 появляется положительный импульс, который стробирует прием информации в регистр 8. На выходе 36 элемента И-НЕ 19 появляется отрицательный импульс, который переводит выходы регистра 8 в активное состояние, и информация с шин данных интерфейса 2 записывается по адресу, выставленному на шинах адреса этого интерфейса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения интерфейсов | 1989 |

|

SU1817097A1 |

| Устройство для сопряжения интерфейсов | 1991 |

|

SU1798791A1 |

| Устройство для передачи информации | 1989 |

|

SU1762307A1 |

| Устройство для передачи дискретной информации | 1991 |

|

SU1783533A1 |

| Сдвиговый регистр | 1973 |

|

SU643974A1 |

| Устройство для сопряжения ЭВМ с печатающим устройством и абонентами | 1989 |

|

SU1705831A1 |

| Счетчик на кольцевом регистре | 1978 |

|

SU733111A1 |

| Устройство для возведения в степень | 1982 |

|

SU1084787A1 |

| Устройство сопряжения интерфейсов разной разрядности | 1989 |

|

SU1689962A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

Изобретение относится к вычислительной технике и может быть использовано для подключения периферийных устройств с шиной типа И41 к электронным цифровым машинам (например, персональным ЭВМ ЕС1840, имеющим выходной интерфейс стык С2), причем оба устройства, периферийное устройство и ЭВМ, могут быть расположены на больших расстояниях друг от друга. Цель изобретения - сокращение аппаратурных затрат устройства. Устройство содержит элементы приема и передачи информации, регистр адреса, тактовый генератор, регистр приема данных, регистр передачи данных, узел начального сброса, два узла укорочения длительности импульса, пять элементов НЕ, пять триггеров, четыре элемента И - НЕ, два делителя числа импульсов, два элемента И, элемент 2И - ИЛИ, дешифратор и элемент задержки. 2 ил. ил.

УСТРОЙСТВО СОПРЯЖЕНИЯ ИНТЕРФЕЙСОВ, содержащее тактовый генератор, соединенный выходом с первым входом первого элемента И, два делителя числа импульсов, четыре элемента И - НЕ, регистр приема данных, регистр передачи данных, регистр адреса, элемент приема информации, вход которого является входом устройства для подключения и выходной информационной линии первого интерфейса, элемент передачи информации, выход которого является выходом устройства для подключения к входной информационной линии второго интерфейса, пять триггеров, два узла укорочения длительности импульса и узел начального сброса, выход которого соединен с первым входом первого элемента И - НЕ, вторым входом подключенного к выходу первого узла укорочения длительности импульса, причем выход первого элемента И соединен с тактовым входом первого делителя числа импульсов, а второй вход - с выходом первого триггера, выход триггера соединен с информационным входом регистра приема данных, группа выходов которого подключена к группам информационных входов регистра адреса и регистра передачи данных, группы выходов которых и выходы второго и третьего элементов И - НЕ являются соответствующими группами выходов устройства для подключения к адресным, информационным и управляющим шинам второго интерфейса, первый выход первого делителя числа импульсов соединен с тактовым входом второго делителя числа импульсов и синхровходами второго, третьего и четвертого триггеров, информационные входы второго и четвертого триггеров соединены соответственно с выходами элемента приема информации и третьего триггера, выход четвертого триггера - с входом элемента передачи информации, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены дешифратор, пять элементов НЕ, элемент И - ИЛИ, второй элемент И и элемент задержки, причем выход элемента приема информации через первый элемент НЕ соединен с установочным входом первого триггера, выходом подключенного к входу первого узла укорочения длительности импульса, а входом сброса - к выходу второго элемента НЕ и входами сброса второго, третьего и четвертого триггеров, информационный вход четвертого триггера соединен с выходом соответствующего разряда регистра приема данных, группа информационных входов которого подключена к группе выходов регистра передачи данных, первый и второй входы четвертого элемента И - НЕ соединены соответственно с выходами второго делителя числа импульсов и третьего элемента НЕ, а выход через второй узел укорочения длительности импульса - к синхровходу пятого триггера и третьему входу первого элемента И - НЕ, выход которого подключен к входу второго элемента НЕ и входам сброса второго и первого делителей числа импульсов, выходы соответствующих разрядов регистра адреса соединены с первым и вторым входами дешифратора, первый и второй выходы которого подключены соответственно к первым входам второго и третьего элементов И - НЕ, вторые входы которых соединены соответственно с выходами элемента задержки и второго элемента И, первым и вторым входами подключенного соответственно к прямому выходу пятого триггера и выходу элемента задержки, вход которого соединен с выходом второго делителя числа импульсов, информационный выход пятого триггера соединен со своим инверсным выходом, первый - четвертый входы элемента И - ИЛИ соединены соответственно с первым и вторым выходами первого делителя числа импульсов, выходами второго элемента И - НЕ и четвертого элемента НЕ, выход узла начального сброса соединен через пятый элемент НЕ с входами сброса регистров приема и передачи данных и регистра адреса, тактовые входы регистра адреса и регистра передачи данных подключены к выходу второго элемента И, третий выход дешифратора является выходом устройства для подключения к управляющей шине второго интерфейса, выход третьего элемента И - НЕ соединен с входом выборки регистра передачи данных, управляющий и тактовый входы регистра приема данных подключены соответственно к выходам четвертого элемента НЕ и элемента И - ИЛИ, входы четвертого и третьего элементов НЕ соединены соответственно с выходом второго элемента И-НЕ и вторым выходом первого делителя числа импульсов, выход первого триггера соединен с входом первого узла укорочения длительности импульса.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство сопряжения интерфейсов | 1989 |

|

SU1817097A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1990-01-09—Подача