нальных возможностей устройства за счет организации приоритетного обращения одной из ЦВМ к общей памяти. Устройство содержит регистры 1-10, элемент П задержки, блоки 12,13 регистров, пятый элемент И 14, триг геры 15,16,17, формирователи 18,19, 20 импульсов, блок 21 коммутации, с

Изобретение относится к вычислительной технике, в частности к устройствам сопряжения с памятью, и может быть использовано при разработке мультипроцессорных вычислительных комплексов.

Цель изобретения - расширение функциональных возможностей устройства за счет организации приоритетного обращения одной из ЦВМ к общей памяти.

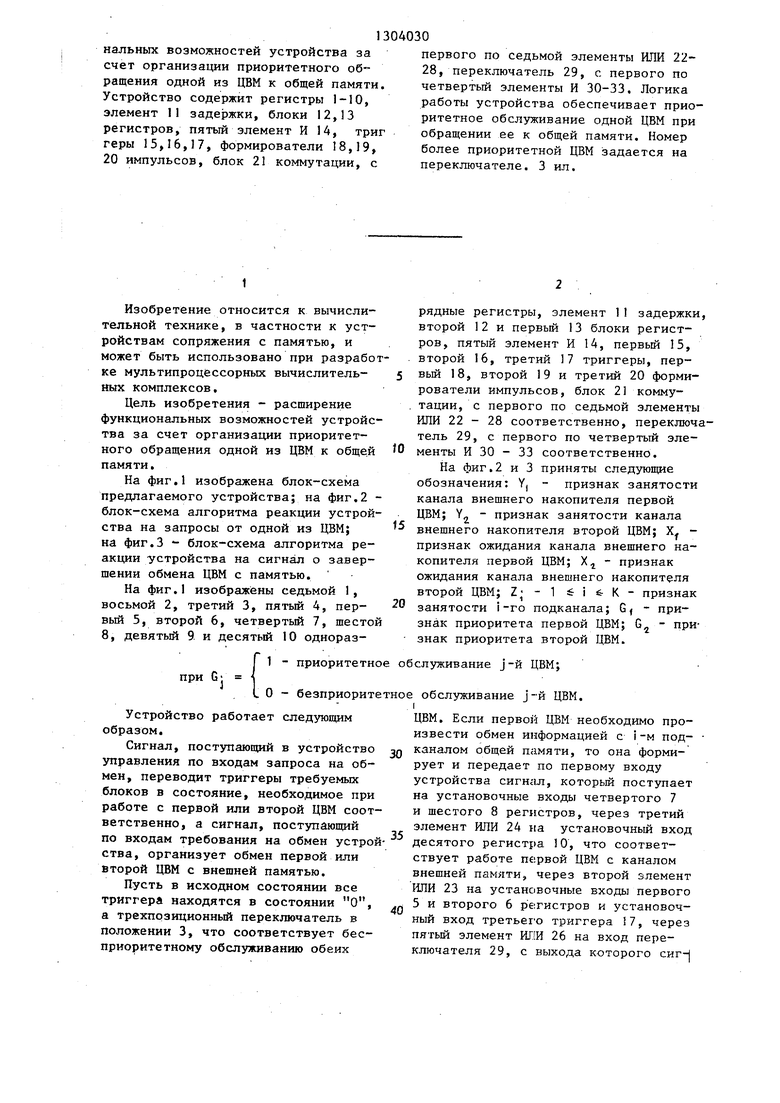

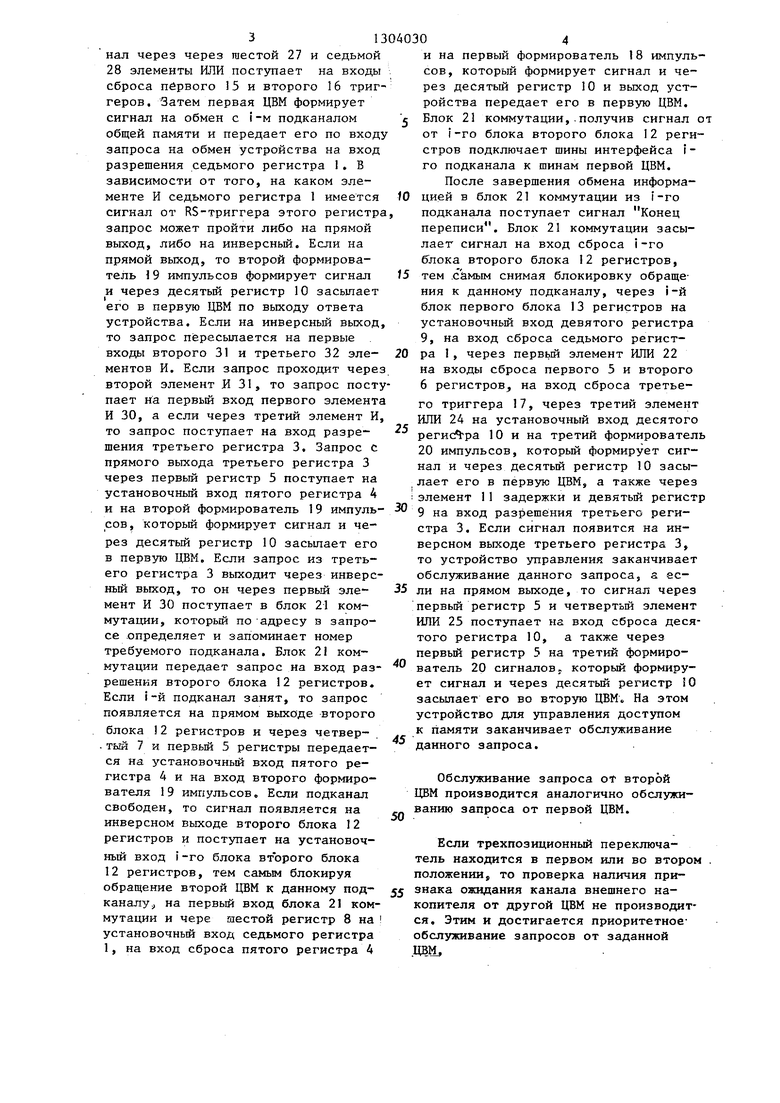

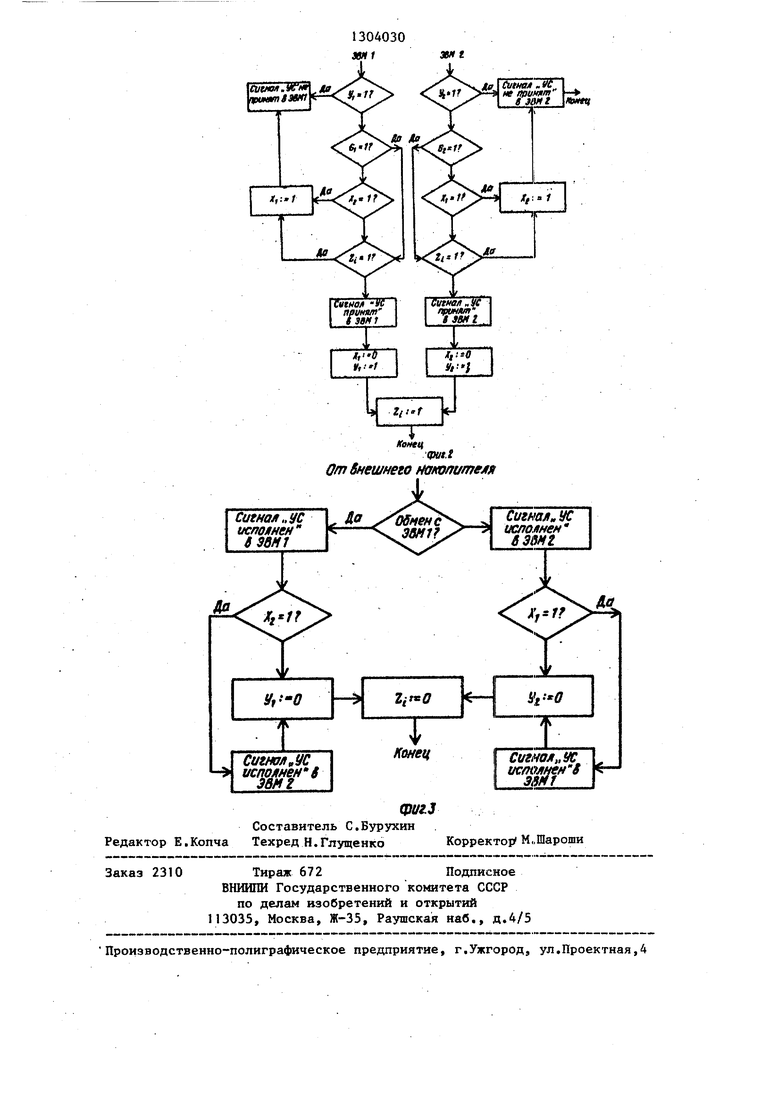

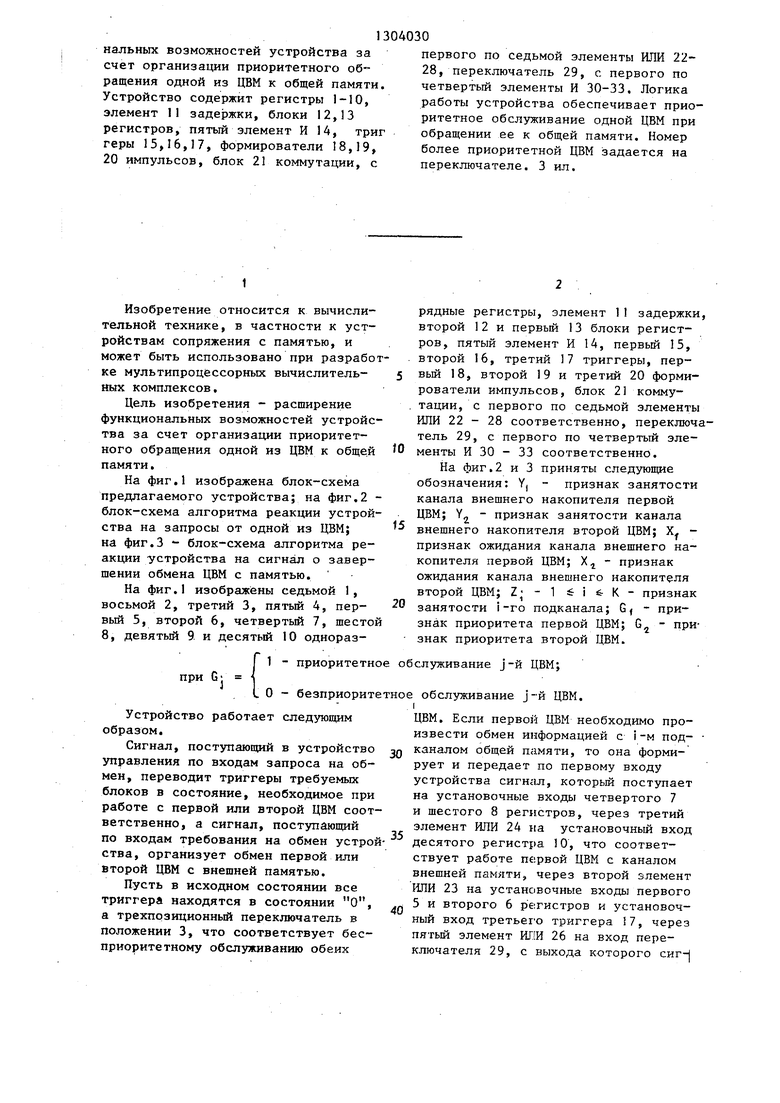

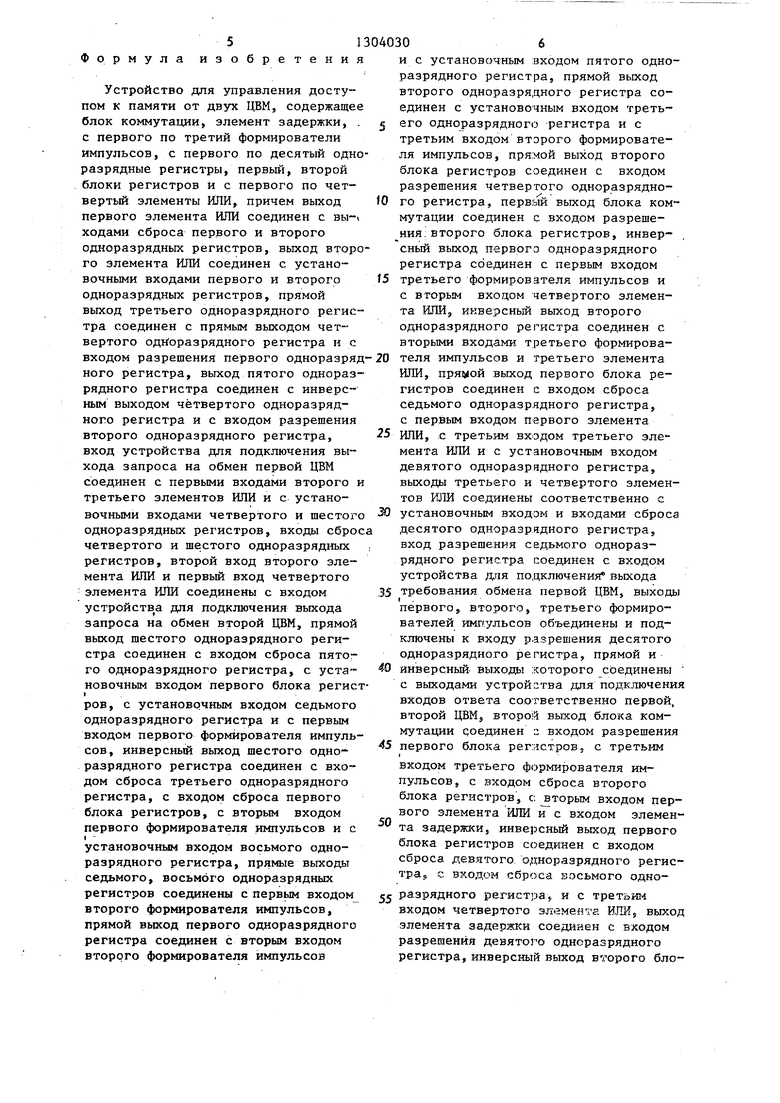

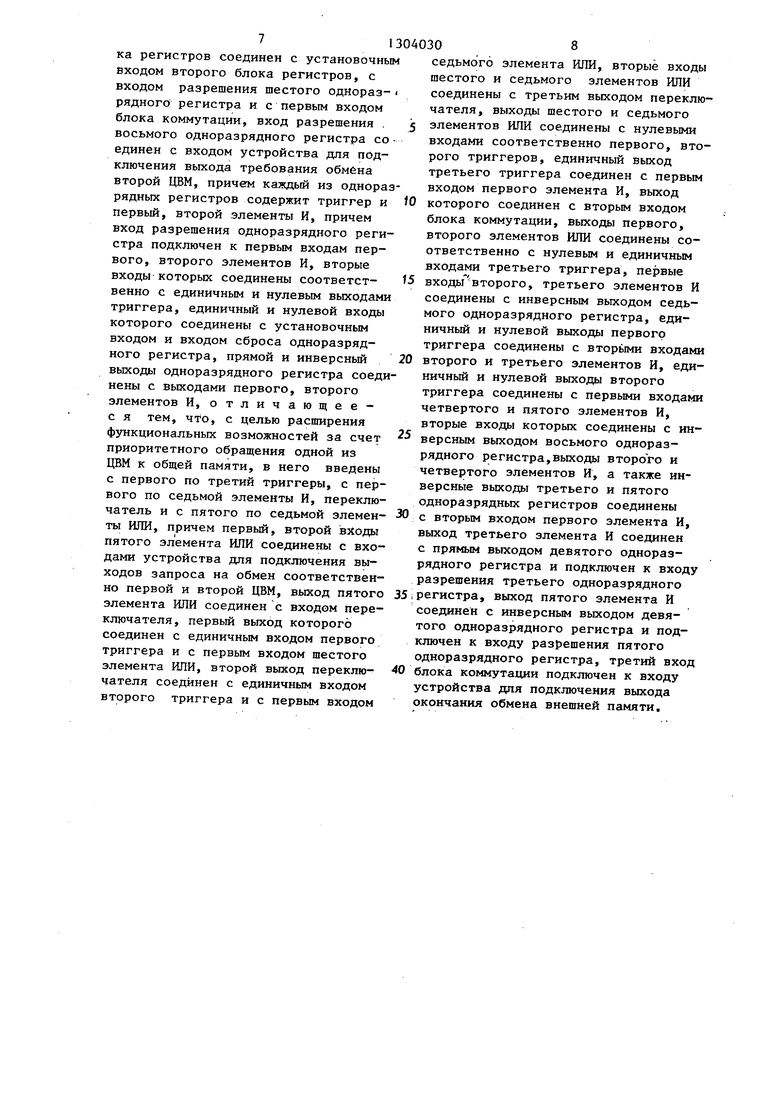

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 - блок-схема алгоритма реакции устройства на запросы от одной из ЦВМ; на фиг.З - блок-схема алгоритма реакции устройства на сигнал о завершении обмена ЦВМ с памятью.

На фиг.1 изображены седьмой 1, восьмой 2, третий 3, пятый 4, первый 5, второй 6, четвертый 7, шестой 8, девятый 9 и десятый 10 одноразпри G

1 - приоритетное обслуживание j-й ЦВМ; . О - безприоритетное обслуживание j-й ЦВМ.

Устройство работает следующим образом.

Сигнал, поступающий в устройство управления по входам запроса на обмен, переводит триггеры требуемых блоков в состояние, необходимое при работе с первой или второй ЦВМ соответственно, а сигнал, поступающий по входам требования на обмен устроства, организует обмен первой или второй ЦВМ с внешней памятью.

Пусть в исходном состоянии все триггера находятся в состоянии О, а трехпозиционный переключатель в положении 3, что соответствует бесприоритетному обслуживанию обеих

первого по седьмой элементы ИЛИ 22- 28, переключатель 29, с первого по четвертый элементы И 30-33. Логика работы устройства обеспечивает приоритетное обслуживание одной ЦВМ при обращении ее к общей памяти. Номер более приоритетной ЦВМ задается на переключателе. 3 ил.

рядные регистры, элемент 11 задержки, второй 12 и первый 13 блоки регистров, пятый элемент И 14, первый 15, второй 16, третий 17 триггеры, первый 18, второй 19 и третий 20 формирователи импульсов, блок 21 комму- тации, с первого по седьмой элементы ИЛИ 22 - 28 соответственно, переключатель 29, с первого по четвертый элементы И 30 - 33 соответственно.

На фкг.2 и 3 приняты следзтощие обозначения: Y, признак занятости канала внешнего накопителя первой ЦВМ; YJ - признак занятости канала внешнего накопителя второй ЦВМ; Х - признак ожидания канала внешнего накопителя первой ЦВМ; Х признак ожидания канала внешнего накопителя второй ЦВМ; Z; - 1 i i fr К - признак

занятости i-го подканала; Gf - признак приоритета первой ЦВМ; G при- знак приоритета второй ЦВМ.

ЦВМ. Если первой ЦВМ необходимо произвести обмен информацией с i-м подканалом общей памяти, то она формирует и передает по первому входу устройства сигнгш, который поступает на установочные входы четвертого 7 и шестого 8 регистров, через третий элемент ИЛИ 24 на установочный вход десятого регистра 10, что соответствует работе первой ЦВМ с каналом внешней памяти, через второй элемент ИЛИ 23 на установочные входы первого 5 и второго 6 ре;гистров и установочный вход третьего триггера 7, через пятый элемент ИЛИ 26 на вход переключателя 29, с выхода которого сиг

нал через через шестой 27 и седьмой 28 элементы ИЛИ поступает на входы сброса первого 15 и второго 16 триггеров. Затем первая ЦВМ формирует сигнал на обмен с i-м подканалом общей памяти и передает его по входу запроса на обмен устройства на вход разрешения седьмого регистра 1. В зависимости от того, на каком зле- менте И седьмого регистра 1 имеется сигнал от RS-триггера этого регистра запрос может пройти либо на прямой выход, либо на инверсньш. Если на прямой выход, то второй формирователь 19 импульсов формирует сигнал и через десятый регистр 10 засьшает его в первую ЦВМ по выходу ответа устройства. Если на инверсньш выход, то запрос пересылается на первые входы второго 31 и третьего 32 элементов И. Если запрос проходит через второй элемент И 31, то запрос поступает на первый вход первого элемента И 30, а если через третий элемент И, то запрос поступает на вход разрешения третьего регистра 3, Запрос с прямого выхода третьего регистра 3 через первый регистр 5 поступает на установочный вход пятого регистра А и на второй формирователь 19 импуль-

сов, который формирует сигнал и через десятый регистр 10 засылает его в первую ЦВМ. Если запрос из третьего регистра 3 выходит через инверсный выход, то он через первый элемент И 30 поступает в блок 21 коммутации, который по адресу в запро се .определяет и запоминает номер требуемого подканала. Блок 21 коммутации передает запрос на вход разрешения второго блока 12 регистров. Если i-и подканал занят, то запрос появляется на прямом выходе второго блока 2 регистров и через четвер- - тый 7 и первый 5 регистры передается на установочный вход пятого регистра 4 и на вход второго формирователя 19 импульсов. Если подканал свободен, то сигнал появляется на инверсном выходе второго блока I2 регистров и поступает на установочный вход i-го блока второго блока 12 регистров, тем самым блокируя обращение второй ЦВМ к данному подканалу, на первый вход блока 21 коммутации и чере шестой регистр В на установочный вход седьмого регистра 1, на вход сброса пятого регистра 4

и на первый формирователь 18 импульсов, который формирует сигнал и чеO

0

рез десятый регистр 10 и выход устройства передает его в первую ЦВМ. Блок 21 коммутации,.получив сигнал от от i-ro блока второго блока 12 регистров подключает шины интерфейса i- го подканала к шинам первой ЦВМ.

После завершения обмена информацией в блок 21 коммутации из i-ro подканала поступает сигнал Конец переписи. Блок 21 коммутации засылает сигнал на вход сброса i-го блока второго блока 12 регистров, 5 тем .самым снимая блокировку обращения к данному подканалу, через i-й блок первого блока 13 регистров на установочный вход девятого регистра 9, на вход сброса седьмого регистра 1 , через первьш элемент ИЛИ 22 на входы сброса первого 5 и второго 6 регистров, на вход сброса третьего триггера 17, через третий элемент ИЛИ 24 на установочный вход десятого peгиc pa 10 и на третий формирователь 20 импульсов, который формирует сигнал и через десятый регистр 10 засылает его в первую ЦВМ, а также через элемент 11 задержки и девятый регистр 9 на вход разрешения третьего регистра 3. Если сигнал появится на инверсном выходе третьего регистра 3, то устройство управления заканчивает обслуживание данного запроса, а если на прямом выходе, то сигнал через первьй регистр 5 и четвертый элемент ИЛИ 25 поступает на вход сброса десятого регистра 10, а также через первьй регистр 5 на третий формирователь 20 сигналов, который формирует сигнал и через десятый регистр 0 засылает его во вторую ЦВМ« На этом устройство для управления доступом к памяти заканчивает обслуживание данного запроса.

0

5

5

0

5

Обслуживание запроса от второй ЦВМ производится аналогично обслуживанию запроса от первой ЦВМ.

Если трехпозиционный переключатель находится в первом или во втором положении, то проверка наличия признака ожидания канала внешнего накопителя от другой ЦВМ не производится. Этим и достигается приоритетное- обслуживание запросов от заданной ЦВМ,

ормула

и

5 зоб

13

р е т е н и я

Устройство для управления доступом к памяти от двух ЦВМ, содержащее блок коммутации, элемент задержки, . с первого по третий формирователи импульсов, с первого по десятый одноразрядные регистры, первый, второй блоки регистров и с первого по четвертый элементы ИЛИ, причем выход первого элемента ИЛИ соединен с вы-i ходами сброса первого и второго одноразрядных регистров, выход второго элемента ИЛИ соединен с установочными входами первого и второго одноразрядных регистров, прямой выход третьего одноразрядного регистра соединен с прямым выходом четвертого одн оразрядного регистра и с

входом разрешения первого одноразряд-20 теля импульсов и третьего элемента

ного регистра, выход пятого одноразрядного регистра соединен с инверсным выходом четвертого одноразрядного регистра и с входом разрешения второго одноразрядного регистра, вход устройства для подключения выхода запроса на обмен первой ЦВМ соединен с первыми входами второго третьего элементов ИЛИ и с установочными входами четвертого и шестог одноразрядных регистров, входы сбро четвертого и шестого одноразрядных регистров, второй вход второго элемента ИЛИ и первый вход четвертого элемента ИЛИ соединены с входом устройств а для подключения выхода запроса на обмен второй ЦВМ, прямой выход шестого одноразрядного регистра соединен с входом сброса пятого одноразрядного регистра, с уста

новочным входом первого блока регис I

ров, с установочным входом седьмого одноразрядного регистра и с первым входом первого формирователя импульсов, инверсный выход шестого одно- разрядного регистра соединен с входом сброса третьего одноразрядного регистра, с входом сброса первого блока регистров, с вторым входом

первого формирователя импульсов и с I установочным входом восьмого одноразрядного регистра, прямые выходы седьмого, восьмого одноразрядных регистров соединены с первым входом второго формирователя импульсов, прямой выход первого одноразрядного регистра соединен с вторым входом второго формирователя импульсов

1304030

и с установочным входом пятого одноразрядного регистра, прямой выход второго одноразрядного регистра соединен с установочным входом третьего одноразрядного регистра и с третьим входом второго формирователя импульсов, прямой выход второго блока регистров соединен с входом разрешения четвертого одноразрядного регистра, первый выход блока коммутации соединен с входом разрешения; второго блока регистров, инверсный вькод первого одноразрядного регистра соединен с первым входом

третьего формирователя импульсов и с вторым вкоцом четвертого элемента ИЛИ, инверсный выход второго одноразрядного регистра соединен с вторыми входами третьего формирова

ИЛИ, выход первого блока регистров соединен с входом сброса седьмого одноразрядного регистра, с первым входом первого элемента ИЛИ, с третьим входом третьего элемента ИЛИ и с установочным входом девятого одноразрядного регистра, выходы третьего и четвертого элементов ИЛИ соединены соответственно с

установочным входом и входами сброса десятого одноразрядного регистра, вход разрешения седьмого одноразрядного регистра соединен с входом устройства для подключения выхода

требования обмена первой ЦВМ, выходы первого, второго, третьего формирователей имгг/льсов объединены и подключены к входу разрешения десятого одноразрядного регистра, прямой и

инверсный- выходы :которого соединены с выходами устройства для подключения входов ответа соответственно первой, второй ЦВМ, второй выход блока коммутации соединен :; входом разрешения

первого блока регистров, с третьим

входом третьего формирователя импульсов, с входом сброса второго блока регистров, с: торым входом первого элемента ИЛИ и с входом элемента задержки, инверсный выход первого блока регистров соединен с входом сброса девятого одноразрядного регистра р с входом сброса зосьмого одноразрядного perHCTjjaf и с третьим

входом четвертого элемента НШ, выход элемента задержки соединен с входом разрешения девятог о одноразрядного регистра, инверсный выход второго бло

ка регистров соединен с установочны входом второго блока регистров, с входом разрешения шестого одноразрядного регистра и с первым входом блока коммутации, вход разрешения . восьмого одноразрядного регистра со единен с входом устройства для подключения выхода требования обмина второй ЦВМ, причем каждый из однорарядных регистров содержит триггер и первый, второй элементы И, причем вход разрешения одноразрядного регистра подключен к первым входам первого, второго элементов И, вторые входы которых соединены соответст- венно с единичным и нулевым выходами триггера, единичный и нулевой входы которого соединены с установочным входом и входом сброса одноразрядного регистра, прямой и инверсный выходы одноразрядного регистра соединены с выходами первого, второго элементов И, отличающее- с я тем, что, с целью расширения функциональных возможностей за счет приоритетного обращения одной из ЦВМ к общей памяти, в него введены с первого по третий триггеры, с первого по седьмой элементы И, переключатель и с пятого по седьмой элемен- ты ИЛИ, причем первый, второй входы пятого элемента ИЛИ соединены с входами устройства для подключения выходов запроса на обмен соответствен

но первой и второй ЦВМ, выход пятого 35iрегистра, выход пятого элемента И

элемента ИЛИ соединен с входом переключателя, первый выход которого соединен с единичным входом первого триггера и с первым входом шестого элемента ИЛИ, второй выход переключателя соединен с единичным входом второго триггера и с первым входом

O 5

0

5

седьмого элемента ИЛИ, вторые входы шестого и седьмого элементов ИЛИ соединены с третьим выходом переключателя, выходы шестого и седьмого элементов ИЛИ соединены с нулевыми входами соответственно первого, второго триггеров, единичный выход третьего триггера соединен с первым входом первого элемента И, выход которого соединен с вторым входом блока коммутации, выходы первого, второго элементов ИЛИ соединены соответственно с нулевым и единичным входами третьего триггера, первые входы второго, третьего элементов И соединены с инверсным выходом седьмого одноразрядного регистра, единичный и нулевой выходы первого триггера соединены с вторьми входами второго и третьего элементов И, единичный и нулевой выходы второго триггера соединены с первыми входами четвертого и пятого элементов И, вторые входы которых соединены с инверсным выходом восьмого одноразрядного регистра,выходы второго и четвертого элементов И, а также инверсные выходы третьего и пятого одноразрядных регистров соединены с вторым входом первого элемента И, выход третьего элемента И соединен с прямым выходом девятого одноразрядного регистра и подключен к входу разрешения третьего одноразрядного

соединен с инверсным выходом девятого одноразрядного регистра и подключен к входу разрешения пятого одноразрядного регистра, третий вход блока коммутации подключен к входу устройства для подключения выхода окончания обмена внешней памяти.

Конец

фаг.

От Внешнею накопителя

коми

Cut нал „НС

(хполнен

{9вМ1

Сигнал, УС исполнен 6Э8Мг

Да

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1986 |

|

SU1312590A1 |

| Устройство для обмена данными в вычислительной системе | 1984 |

|

SU1251090A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1989 |

|

SU1689961A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обращения двух процессоров к общему блоку памяти | 1990 |

|

SU1784986A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам для сопряжения с памятью, и может быть использовано при проектировании многопроцессорных систем с общей памятью. Целью изобретения является расширение функцио 9eff2t :«9 э « D

Фии

Составитель С.Бурухин Редактор Е.Копча Техред Н.Глущенко Корректор М„Шароши

Заказ 2310 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство управления доступом к общей памяти | 1977 |

|

SU750490A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления доступом к памяти | 1983 |

|

SU1161946A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ф | |||

Авторы

Даты

1987-04-15—Публикация

1985-06-19—Подача