Изобретение относится к вычислительной технике и может быть использовано в электрически перепрограммируемом постоянном запоминающем устройстве, сохраняющем информацию при отключении источника питания.

Целью изобретения является повышение надежности матричного накопителя.

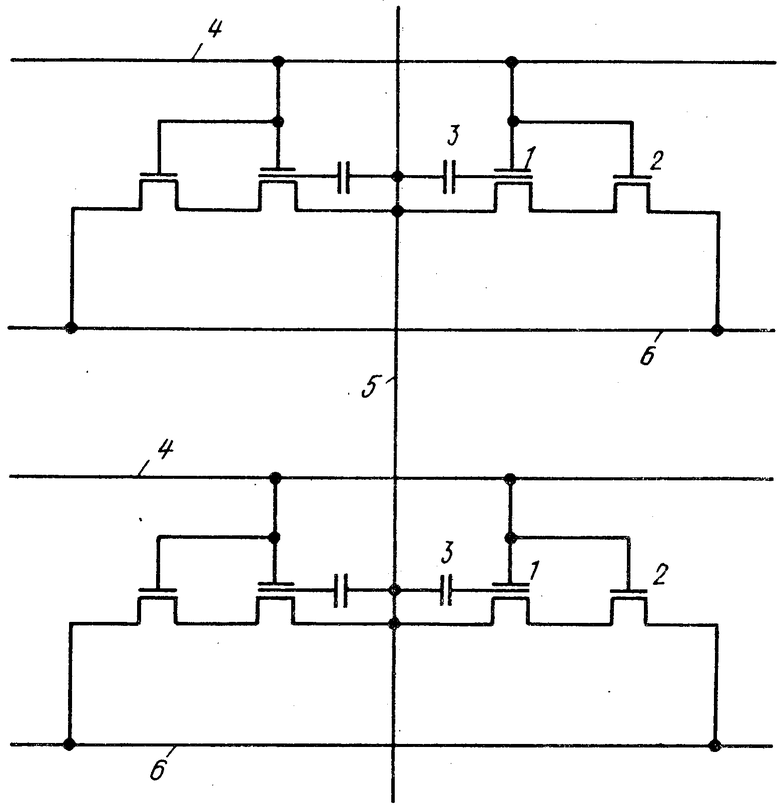

На чертеже приведена электрическая схема матричного накопителя для электрически перепрограммируемого постоянного запоминающего устройства, сохраняющего информацию при отключении источника питания.

Накопитель содержит запоминающие транзисторы 1 с плавающими и управляющими затворами, адресные транзисторы 2, конденсаторы 3 ячеек памяти, адресные шины 4, разрядные шины 5, шину 6 нулевого потенциала.

Матричный накопитель работает следующим образом. В режиме считывания информации на выбранную адресную шину 4 и разрядные шины 5 подают низкое положительное импульсное напряжение (+5 В и 1-2 В, 200 нс), на остальные адресные шины 4, разрядные шины 5 - нулевое напряжение.

Под действием этих напряжений выбранные МДП-транзисторы 2 находятся в открытом состоянии, невыбранные транзисторы 2 - в закрытом состоянии. Если пороговое напряжение выбранного транзистора 1 превышает (не превышает) напряжение на адресной шине 4, то через него выбранные транзистор 2, разрядные шины 5, шину 6 не протекает (протекает) ток, что эквивалентно нулевому (единичному) состоянию выбранного транзистора 1.

Через остальные транзисторы 1 и разрядные шины 5 ток не протекает, так как или закрыты транзисторы 2, или разность напряжений между разрядными шинами 5 и шиной 6 равна нулю.

В режиме общего стирания информации на все разрядные шины 5 подают высокое положительное импульсное напряжение (+18 В, 1 мс), на все адресные шины 4 - нулевое напряжение.

Под действием этих напряжений происходит перезарядка всех конденcаторов 3, в результате чего пороговые напряжения всех запоминающих транзисторов 1 становятся отрицательными (-6-8 В), что эквивалентно единичному состоянию в режиме считывания информации.

В режиме разрядного стирания на выбранные разрядные шины 5 подают высокое положительное импульсное напряжение (+18 В, 1 мс), на остальные разрядные шины 5, адресные шины 4 - нулевое напряжение.

Под действием этих напряжений происходит перезарядка конденсаторов 3 выбранных разрядов, у остальных конденсаторов 3 потенциал сохраняется неизменным из-за нулевых напряжений на разрядных шинах 5, адресных шинах 4, шине 6.

В режиме программирования информации на выбранную адресную шину 4 подают высокое положительное импульсное напряжение (12 В, 1-10 мс), на выбранные разрядные шины 5 - низкое положительное импульсное напряжение (+5 В, 1-10 мс), на остальные адресные шины 4, разрядные шины 5 - нулевое напряжение.

Под действием этих напряжений адресные МДП-транзисторы 2 выбранной строки находятся в открытом состоянии, остальные - в закрытом состоянии. На плавающие затворы выбранных запоминающих транзисторов 1 передаются положительные напряжения с адресной шины 4 через емкость, управляющий затвор-плавающий затвор и с разрядных шин 5 через конденсаторы 3. Горячие электроны инжектируются из каналов выбранных запоминающих лавинно-инжекционных транзисторов 1, захватываются их плавающими затворами, заряжая конденсаторы 3. В результате пороговые напряжения выбранных запоминающих транзисторов 1 увеличиваются (+6-8 В), что эквивалентно нулевому состоянию в режиме считывания информации.

Состояния остальных невыбранных запоминающих транзисторов 1 сохраняются неизменными из-за нулевого напряжения на адресных шинах 4 или разрядных шинах 5.

Таким образом, за счет подключения выводов конденсаторов между разрядными шинами и плавающими затворами запоминающих лавинно-инжекционных транзисторов обеспечивается повышение надежности работы матричного накопителя, возможность разрядного стирания информации и использования емкостных умножителей напряжения в этом режиме.

Изобретение относится к вычислительной технике и может быть использовано в электрически перепрограммируемом постоянном запоминающем устройстве. Целью изобретения является повышение надежности матричного накопителя. Для этого между разрядной шиной накопителя и плавающим затвором запоминающего транзистора подсоединен конденсатор. 1 ил.

МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий адресные и разрядные шины, в перекрестиях которых включены ячейки памяти, причем каждая ячейка состоит из запоминающего и адресного транзисторов и конденсатора, первый вывод которого соединен с плавающим затвором запоминающего транзистора, управляющий затвор запоминающего транзистора каждой ячейки памяти соединен с затвором адресного транзистора и подключен к соответствующей адресной шине, исток адресного транзистора каждой ячейки памяти подключен к шине нулевого потенциала накопителя, а сток соединен с истоком запоминающего транзистора, сток запоминающего транзистора каждой ячейки памяти смежных столбцов подключен к разрядной шине, отличающийся тем, что, с целью повышения надежности накопителя, второй вывод конденсатора каждой ячейки памяти смежных столбцов подключен к разрядной шине.

| Electronics | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1994-12-30—Публикация

1986-06-04—Подача