(Г.

с

1 .

Изобретение относится к области вычислительной техники и может быть использовано при построении интегральных полупроводниковых запоминающих устройств.

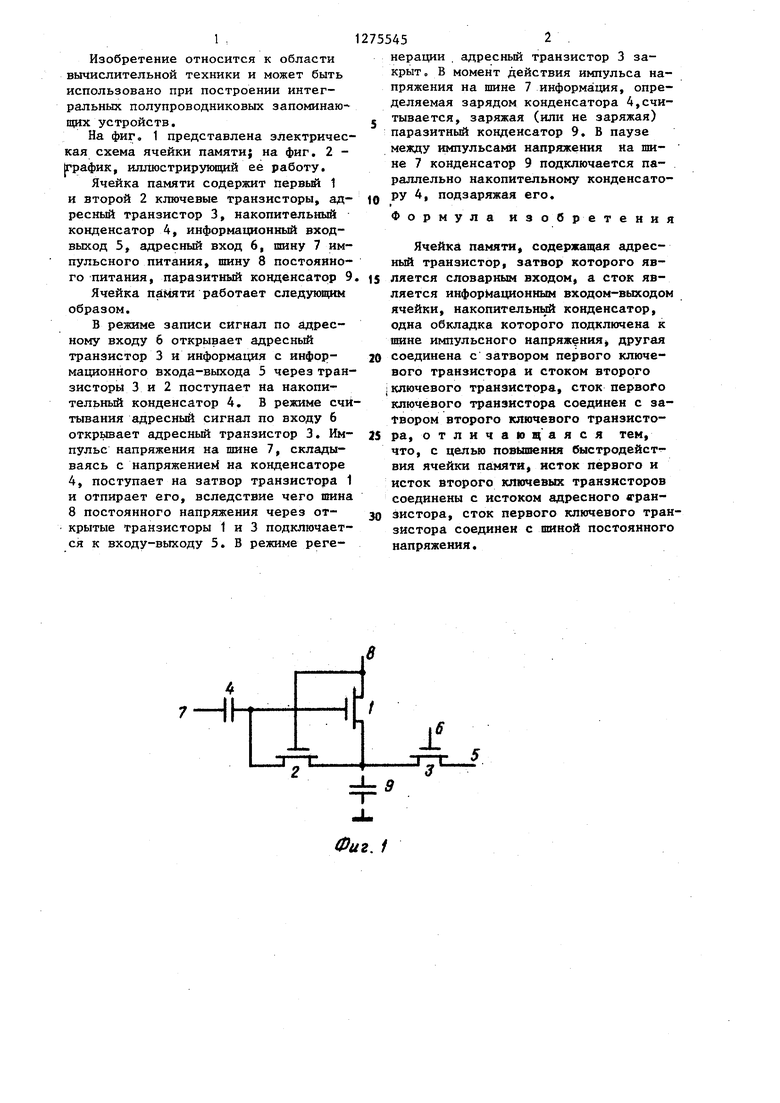

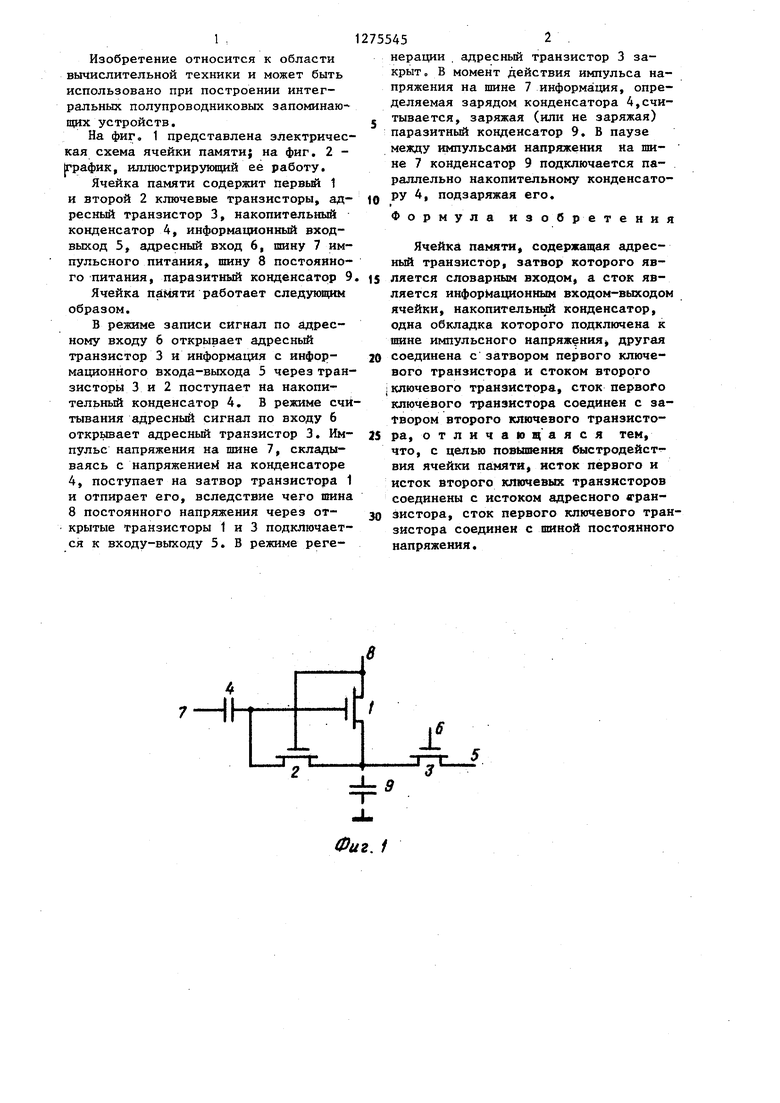

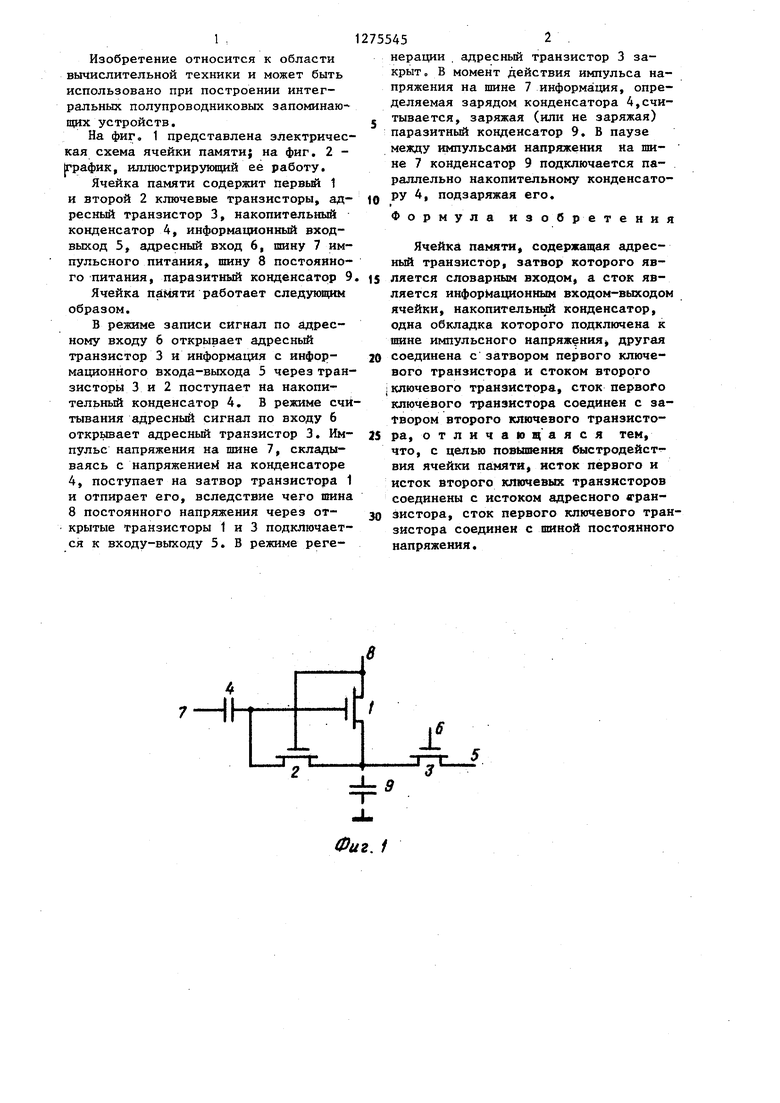

На фиг, 1 представлена электрическая схема ячейки памяти; на фиг. 2 рафик, иллюстрирующий ее работу.

Ячейка памяти содержит первый 1 и второй 2 ключевые транзисторы, адресный транзистор 3, накопительный конденсатор 4, информационный входвыход 5, адресный вход 6, шину 7 импульсного питания, шину 8 постоянного питания, паразитный конденсатор 9

Ячейка памяти работает следующим образом,

В режиме записи сигнал по адресному входу 6 открывает адресньй транзистор 3 и информация с информационного входа-выхода 5 через транзисторы 3 и 2 поступает на накопительный конденсатор 4. В режиме счй тывания адресный сигнал по входу 6 открывает адресный транзистор 3, Импульс напряжения на шине 7, складываясь с напряжение на конденсаторе 4, поступает на затвор транзистора 1 и отпирает его, вследствие чего шина 8 постоянного напряжения через открытые транзисторы 1 и 3 подключается к входу-выходу 5, В реясиме реге12755452 .

нерации . адресный транзистор 3 закрыт, В момент действия импульса напряжения на шине 7 информация, определяемая зарядом конденсатора 4,счи- тывается, заряжая (или не заряжая) паразитный конденсатор 9, В паузе между импульсами напряжения на шине 7 конденсатор 9 подключается параллельно накопительному конденсатору 4, подзаряжая его.

Формула изобретения

Ячейка памяти, содержащая адресный транзистор, затвор которого является словарным входом, а сток является информационным входом-выходом ячейки, накопительный конденсатор, одна обкладка которого подключена к шне импульсного напряжения другая

соединена с затвором первого ключевого транзистора и стоком второго ключевого транзистора, сток первого ключевого транзистора соединен с заtBopoM второго ключевого транзистора, отличающаяся тем, что, с целью повышения быстродейст ВИЯ ячейки , исток первого и исток второго ключевых транзисторов соединены с истоком адресного в-ранзистора, сток первого ключевого транзистора соединен с шиной постоянного напряжения,

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Ячейка памяти с внутренней регенерацией | 1984 |

|

SU1274001A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Элемент памяти | 1985 |

|

SU1287232A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении интегральных полупроводниковых запоминающих устройств. Ячейка памяти содержит два ключевых транзистора, адресный транзистор, накопительный конденсатор, адресные и информационные входы, a также шины постоянного и импульсного питания и позволяет с более высоким быстродействием записывать и считывать информацию за счет того, что истоки первого и второго ключевых транзисторов соединены с истоком адресного транзистора,сток первого ключевого транзистора соединен с шиной постоянного.напряжения. 2 ил.

Фиг. 1

f/l

Фиг. 2

Авторы

Даты

1986-12-07—Публикация

1981-10-19—Подача