Изобретение относится к вычислительной технике и может быть использовано в устройствах сбора и обработки быстроменяющихся данных с множества каналов.

Известны устройства для сбора, обработки и передачи информации, например устройство сбора, преобразования и передачи результатов измерения параметров физической среды [1] , содержащее n аналоговых измерительных датчиков, управляющую электронную вычислительную машину с адресно-информационной и командной магистралью, аналого-цифровой преобразователь, коммутатор, блок управления коммутатором, буферное запоминающее устройство, регистр уровня запуска, цифроаналоговый преобразователь, блок дешифрации и компаратор, вход опорного сигнала которого связан с выходом цифроаналогового преобразователя, выход i-гo аналогового измерительного датчика (i=1,..., n) подключен к i-му входу коммутатора, управляющий вход которого соединен с выходом блока управления коммутатором, а выход - со входом аналого-цифрового преобразователя, подсоединенного своим выходом к информационному входу буферного запоминающего устройства, вход управления записью регистра уровня запуска, подключенного своим информационным входом к адресно-информационной и командной магистрали управляющей электронной вычислительной машины, связан с первым выходом блока дешифрации, соединенного своими входами с адресно-информационной и командной магистралью управляющей электронной вычислительной машины, подключенной к каналу ввода-вывода и к входу-выходу канала управления опросом датчиков, управляющий вход которого связан с вторым входом блока дешифрации, а выход - со входом блока управления коммутатором, выход буферного запоминающего устройства подключен к входу блока регистров результата, информационный и управляющий входы которого соединены с информационным и, соответственно, управляющим входами формирователя передаваемой информации, подсоединенного своим выходом к входу узла передачи данных, выход которого является выходом устройства и связан также с информационным периферийным входом канала ввода-вывода, управляющий периферийный вход которого подключен к управляющему выходу блока регистров результата, вход i-гo масштабирующего усилителя соединен с выходом i-гo аналогового измерительного датчика, а выход - с одним из входов узла выделения экстремума, выход которого подсоединен к информационному входу компаратора, связанного своим выходом с входом прерывания управляющей электронной вычислительной машины, вход регистра уровня запуска подключен к входу цифроаналогового преобразователя, а управляющий вход аналого-цифрового преобразователя, адресно-управляющий вход буферного запоминающего устройства и информационно-управляющие входы блока регистров результата, формирователя передаваемой информации и узла передачи данных соединены соответственно с первым, вторым, третьим, четвертым и пятым периферийными выходами канала ввода-вывода.

Недостатком описанного устройства является его сложность. Кроме того, оно контролирует только один параметр, например порог превышения одной величины над заданным ее значением.

Наиболее близким по технической сущности к предлагаемому является устройство для сбора, обработки и пакетной передачи результатов измерения параметров [2], содержащее управляющий вычислительный комплекс с адресно-информационной и командной магистралью, группу из n аналоговых измерительных датчиков, аналого-цифровой преобразователь, блок обработки данных, оперативное запоминающее устройство, буферное запоминающее устройство, коммутатор и блок управления коммутатором, выход которого подключен к управляющему входу коммутатора, а выход аналого-цифрового преобразователя связан с входом блока обработки данных, вторую группу из n аналоговых измерительных датчиков, n1 аналого-цифровых преобразователей первой группы и n аналого-цифровых преобразователей второй группы, n1 блоков обработки данных первой группы и n блоков обработки данных второй группы, второй коммутатор, второй блок управления коммутатором, k1 оперативное запоминающее устройство, второе буферное запоминающее устройство, два формирователя передаваемой информации, два узла передачи данных и канал ввода-вывода, при этом коммутаторы выполнены в виде соединителей nхk, а выход второго блока управления коммутатором соединен с управляющим входом второго коммутатора, а выход второго блока управления коммутатором соединен с управляющим входом второго коммутатора, выход каждого из n1 аналого-цифрового преобразователя первой группы связан с информационным входом соответствующего блока обработки данных первой группы, а выход каждого из n аналого-цифровых преобразователей второй группы - с информационным входом соответствующего блока обработки данных второй группы, выход i-го аналогового измерительного датчика (i=1,..., n) первой и второй группы подсоединен ко входу i-го аналого-цифрового преобразователя соответствующей группы, выход i-го блока обработки данных первой и второй группы связан с i-ым входом первого и второго коммутатора, j-й выход (j=1,..., k) первого и второго коммутаторов подключен к информационному входу j-гo оперативного запоминающего устройства, первый выход каждого из которых соединен с информационным входом первого буферного запоминающего устройства, а второй выход - с информационным входом второго буферного запоминающего устройства, первые выходы первого и второго буферных запоминающих устройств подсоединены к информационному входу первого формирователя передаваемой информации, а вторые их выходы - к информационному входу второго формирователя передаваемой информации, выход которого связан с вторыми входами первого и второго узлов передачи данных, первые входы которых подключены к выходу первого формирователя передаваемой информации, периферийный вход-выход канала ввода-вывода, соединенного с адресно-информационной и командной магистралью управляющего вычислительного комплекса, связан с информационно-управляющими входами-выходами блоков обработки данных первой и второй группы, управляющие входы аналогово-цифровых преобразователей первой и второй группы, управляющие входы первого и второго блоков управления коммутатором, адресно-управляющие входы оперативных запоминающих устройств и буферных запоминающих устройств, информационно-управляющие входы формирователей передаваемой информации и управляющие входы узлов передачи данных подключены соответственно к первому, второму, третьему, четвертому, пятому, шестому, седьмому и восьмому периферийным выходам канала ввода-вывода.

Данное устройство, как и ранее описанный аналог, является достаточно сложным. Для его реализации требуется гальваническая развязка для большого числа линий. Кроме того, необходимость обработки информации с большого числа датчиков требует наличия достаточно большого числа процессоров. При изменении алгоритмов обработки информации от датчиков, например при изменении пороговых значений, требуется перезагрузка программного обеспечения в блоки обработки данных, то есть отсутствует оперативное управление процессом работы.

Кроме этого, накапливаемые данные никуда не передаются, пока не заполнится БЗУ, то есть в случае кратковременного критического события информация о нем сохраняется и передается значительно позднее времени свершения события. Таким образом, отсутствует возможность оперативно реагировать на произошедшие события.

Данное изобретение направлено на решение задачи создания многоканального устройства для регистрации быстроменяющихся сигналов о состоянии контролируемых объектов, поступающих от измерительных датчиков телесигнализации (ТС), с запоминанием времени произошедших событий по каждому каналу для последующей передачи этих данных центральному процессору по параллельной шине при обеспечении гальванической развязки данного устройства и центрального процессора.

Описанная задача решается за счет того, что в устройство для сбора и обработки данных, содержащее управляющий вычислительный комплекс, n входных цепей, m мультиплексоров, блок предварительной обработки данных, выходная шина которого подключена к управляющим шинам мультиплексоров, оперативное запоминающее устройство, блок запроса и обработки данных, блок ввода-вывода данных, через внешнюю шину данных и через внешнюю шину адреса связанный с управляющим вычислительным комплексом, а через соответствующие входные шины подключенный к шине адреса/данных оперативного запоминающего устройства, выходная шина адреса и выходы чтения и записи блока запроса и обработки данных соединены соответственно с входной шиной адреса и с входами чтения и записи блока ввода-вывода данных, введены блок гальванической развязки, включенный между шинами ввода-вывода блока предварительной обработки данных и блока запроса и обработки данных, и регистр адреса, входная шина которого соединена с шиной адреса/данных блока запроса и обработки данных, а выходная шина регистра адреса подключена к первой входной шине адреса оперативного запоминающего устройства, вторая входная шина адреса и входы чтения и записи которого подключены соответственно к выходной шине адреса и к выходам чтения и записи блока запроса и обработки данных, вход каждой из n входных цепей подключен к соответствующему датчику телесигнализации, а выходы каждых k входных цепей объединены и подключены к входной шине соответствующего мультиплексора, выход каждого из которых соединен с соответствующим входом блока предварительной обработки данных; при этом блок предварительной обработки данных содержит аналого-цифровой преобразователь, m триггеров Шмитта, регистр управления, блок обработки и управления, последовательный интерфейс, причем входы аналого-цифрового преобразователя и триггеров Шмитта соединены с выходами мультиплексоров, выходная шина регистра управления подключена к шинам управления мультиплексоров, выходная шина аналого-цифрового преобразователя, выходы триггеров Шмитта и входная шина регистра управления соединены соответственно с входной шиной, с соответствующими входами и с выходной шиной блока обработки и управления, шина ввода-вывода которого через последовательный интерфейс подключена к блоку гальванической развязки, а блок ввода-вывода данных содержит входной накопительный буфер, выходной накопительный буфер, регистр состояния и дешифратор адреса, причем входы дешифратора адреса через внешние шины адреса соединены с управляющим вычислительным комплексом, шины управления входного накопительного буфера, выходного накопительного буфера и регистра состояния соединены с выходной шиной управления дешифратора адреса, шины данных регистра состояния, входного накопительного буфера и выходного накопительного буфера соединены с шиной адреса/данных блока запроса и обработки данных, выход "БУФЕР ПУСТ" выходного накопительного буфера соединен с входом регистра состояния, выход "БУФЕР ПУСТ" входного накопительного буфера соединен с входом прерывания блока запроса и обработки данных, входная шина адреса и входы чтения и записи дешифратора адреса подключены соответственно к выходной шине адреса и к выходам чтения и записи блока запроса и обработки данных.

Предлагаемое техническое решение позволяет осуществлять сбор и обработку быстроменяющейся информации о состоянии контролируемых объектов с множества каналов более простыми средствами, чем с помощью известных аналогов. Кроме того, оно позволяет осуществлять контроль целостности линий, идущих от датчиков ТС. В процессе информационного поиска технических решений, идентичных заявляемому, не обнаружено.

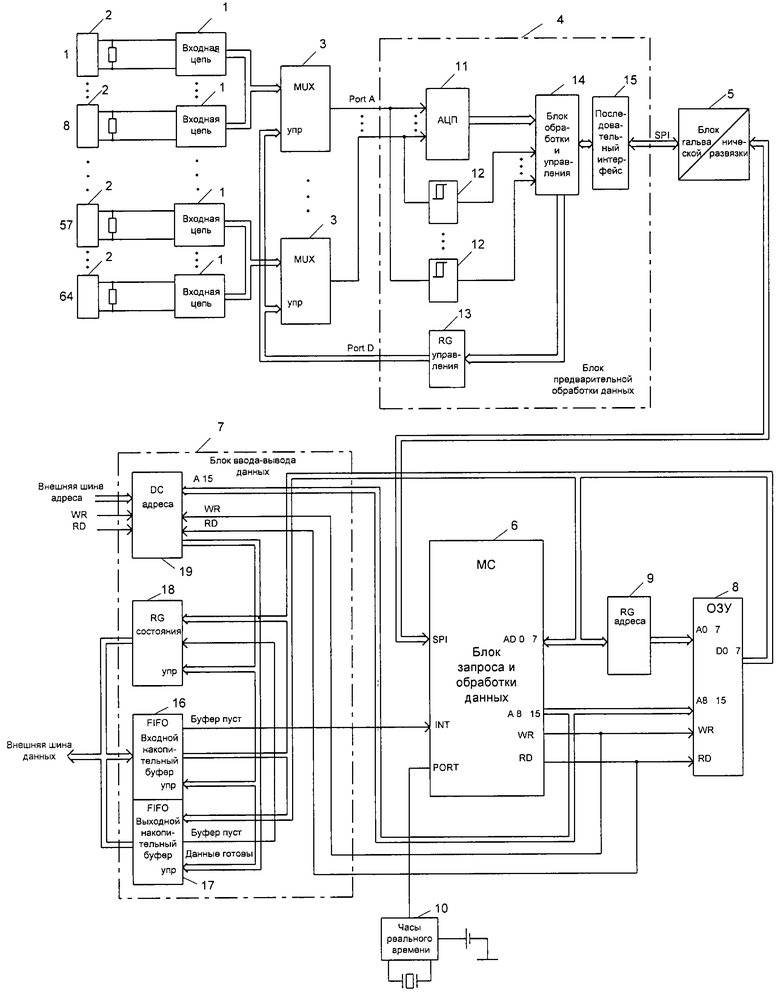

Изобретение иллюстрируется чертежом, на котором представлена функциональная схема заявляемого устройства, пример конкретного исполнения блока сбора и предварительной обработки данных и пример конкретного исполнения блока ввода-вывода данных.

Предлагаемое устройство для сбора и обработки данных содержит n входных цепей 1, входами подключенных к соответствующим выходам датчиков 2 телесигнализации (ТС), которые в состав предлагаемого устройства не входят, а являются по отношению к нему внешними устройствами. Выходы каждых k из n входных цепей 1 объединены и соединены с входными шинами соответствующих мультиплексоров 3, блок 4 сбора и предварительной обработки данных, входы которого соединены с выходами соответствующих мультиплексоров 3, шины управления которых подключены к шине управления блока 4 сбора и предварительной обработки данных, последовательный интерфейс блока 4 сбора и предварительной обработки данных через блок 5 гальванической развязки соединен с последовательным интерфейсом блока 6 запроса и обработки данных, двунаправленная шина адреса/данных которого соединена с входной шиной блока 7 ввода-вывода данных, внешняя шина адреса, внешняя шина данных, вход записи и вход чтения которого связаны с управляющим вычислительным комплексом (на чертеже не показан), а выход подключен к входу прерывания блока 6 запроса и обработки данных, выходы чтения и записи которого соединены соответственно с входами чтения и записи блока 7 ввода-вывода данных и оперативного запоминающего устройства (ОЗУ) 8, шина адреса которого соединена с выходной шиной адреса блока 6 запроса и обработки данных, шина данных соединена с двунаправленной шиной адреса/данных блока 6 запроса и обработки данных и с входной шиной регистра 9 адреса, выходная шина адреса которого соединена с второй шиной адреса ОЗУ 8, часы 10 реального времени, подключенные к блоку 6 запроса и обработки данных. При этом входная цепь 1 может быть выполнена, например, на диодах и токоограничивающих резисторах, блок 5 гальванической развязки может быть выполнен, например, на транзисторных оптопарах, а блок 6 запроса и обработки данных может быть выполнен, например, на микроконтроллере Atmega103 фирмы Atmel. В приведенном конкретном примере реализации предлагаемого устройства количество измерительных датчиков 2 телесигнализации и входных цепей 1 равно 64 (n=64), а количество мультиплексоров 3 равно 8 (m=8).

Блок 4 предварительной обработки данных содержит аналого-цифровой преобразователь (АЦП) 11, m триггеров Шмитта 12, регистр 13 управления, блок 14 обработки и управления, последовательный интерфейс 15, входы АЦП 11 и входы триггеров Шмитта 12 соединены с выходами мультиплексоров 3, выходная шина регистра 13 управления подключена к шинам управления мультиплексоров 3, выходная шина АЦП 11, выходы триггеров Шмитта 12 и входная шина регистра 13 управления соединены соответственно с входной шиной, с соответствующими входами и с выходной шиной блока 14 обработки и управления, который через последовательный интерфейс 15 подключен к блоку гальванической развязки 5. Блок предварительной обработки данных 4 может быть выполнен, например, на микроконтроллере AT90S8535 фирмы Atmel. Блок 4 предварительной обработки данных может работает с цифровыми сигналами, поступающими от цифровых датчиков ТС, например, от замыкающегося-размыкающегося контакта, показывающего включение или выключение какого-либо устройства или срабатывание предохранителя.

Блок 7 ввода-вывода данных содержит входной накопительный буфер 16, выходной накопительный буфер 17, регистр состояния 18 и дешифратор адреса 19, через внешнюю шину адреса и входы записи и чтения соединенный с управляющим вычислительным комплексом (на чертеже не показан), шины управления входного накопительного буфера 16, выходного накопительного буфера 17 и регистра 18 состояния соединены с выходной шиной управления дешифратора адреса 19, выходы регистра 18 состояния, входы входного 16 накопительного буфера и выходы выходного 17 накопительного буфера соединены с внешней шиной данных, выход "БУФЕР ПУСТ" выходного 17 накопительного буфера соединен с входом регистра 18 состояния, выход "БУФЕР ПУСТ" входного накопительного буфера 16 соединен с входом прерывания блока 6 запроса и обработки данных, шины адреса и входы чтения и записи дешифратора адреса 19 подключены соответственно к шине адреса и к выходам чтения и записи блока 6 запроса и обработки данных, шина адреса/данных которого соединена с шинами данных входного 16 накопительного буфера, выходного 17 накопительного буфера и регистра 18 состояния.

Предлагаемое устройство, представленное на чертеже, работает следующим образом.

Сигналы с n измерительных датчиков 2 телесигнализации поступают на соответствующие входные цепи 1, обеспечивающие защиту от перенапряжения на входах остальных элементов устройства. Выходные сигналы входных цепей 1 подаются на входы мультиплексоров 3, выполненных, например, на микросхемах DG408 фирмы VISHAY, которые выбирают один из восьми входных каналов. Сигналы с мультиплексоров 3 подаются на входы блока 4 предварительной обработки данных, который считывает их как цифровые сигналы.

При работе устройства с датчиками ТС сигналы с выходов мультиплексоров 3 поступают на входы соответствующих триггеров Шмитта 12 блока 4 предварительной обработки данных и с выходов триггеров Шмитта 12 - на входы блока 14 обработки и управления, который осуществляет сканирование каналов, выбирая по одному каналу от каждого мультиплексора 3 и считывая данные сразу со всех мультиплексоров 3 этого канала. Для считывания данных со всех каналов (в данном случае 64) осуществляется восемь циклов чтения, при этом каждый раз выбирается новый канал. Выбор каналов мультиплексоров 3 осуществляется по сигналу управления, представляющему собой двоичный код, соответствующий выбранному каналу, выдаваемый блоком 14 обработки и управления на входы управления всех мультиплексоров 3 одновременно. Каждый канал опрашивается блоком 14 обработки и управления три раза, после чего осуществляется выборка "два из трех" и разбор данных по каналам. Сигнал минимальной длительности, который гарантированно зафиксирует блок 14 обработки и управления, соответствует времени измерения tmin, в течение которого осуществляется выборка трех сигналов. Подготовленные блоком 14 обработки и управления данные о состоянии каналов через последовательный интерфейс 15 и блок 5 гальванической развязки, выполненный на транзисторных оптопарах, пересылаются в блок 6 запроса и обработки данных, представляющий собой микроконтроллер Atrnega 103 фирмы Atmel, по его запросу через каждые tmin. Блок 6 запроса и обработки данных осуществляет сравнение каждого вновь поступившего блока данных с предыдущим и определяет, были ли какие-либо изменения входных данных. Если при сравнении поступающих данных о состоянии каналов блоком 6 запроса и обработки данных были выявлены изменения, он фиксирует это изменение и записывает полученные данные в ОЗУ 8 вместе с временем свершения события.

В случае, если необходимо осуществлять контроль состояния линии до датчиков ТС, параллельно датчику и в непосредственной близости к нему устанавливается резистор. При этом по измерительной цепи протекает небольшой ток. Этот сигнал через соответствующую входную цепь 1 подается на вход АЦП 11. Наличие этого сигнала на входе блока 14 обработки и управления указывает на то, что линия до датчиков 2 не имеет повреждений. В случае повреждения линии, например обрыва, ток в линии отсутствует, что и фиксирует блок 14 обработки и управления, который через последовательный интерфейс 15 и блок гальванической развязки 5 посылает информацию в блок 6 запроса и обработки данных. Анализ состояния линии осуществляется по всем каналам ТС. Полученные данные передаются в блок 6 запроса и обработки данных, в котором хранится информация о том, в каких каналах ТС установлены резисторы и в каких каналах необходимо контролировать исправность линии до датчиков ТС. В случае обрыва блок 6 запроса и обработки данных фиксирует это событие и записывает полученные данные в ОЗУ 8 вместе с временем свершения события. Информация о режимах работы каналов (наличие резисторов, необходимость контроля исправности линии) записывается в блок 6 по команде, поступающей от управляющего вычислительного комплекса.

Для хранения текущего времени предназначены часы реального времени 10. Для продолжения работы часов 10 при выключенном блоке используется аккумуляторная батарея. При включении питания текущее время считывается с часов 10 и фиксируется в блоке 6 запроса и обработки данных. В дальнейшем текущее время отслеживается блоком 6.

Обмен данными между устройством сбора и обработки информации и управляющим вычислительным комплексом осуществляется через блок 7 ввода-вывода данных. При запросе данных управляющий вычислительный комплекс (на чертеже не показан) выставляет на шину блока 7 ввода-вывода адрес и данные и выдает команду записи (WR). Дешифратор 19 адреса блока 7 определяет принадлежность обращения именно к данному устройству, и данные переписываются во входной 16 накопительный буфер блока 7 ввода-вывода данных. Входной 16 накопительный буфер и выходной 17 накопительный буфер представляют собой элементы FIFO (например, IDT7205 фирмы IDT). Данные записываются во входной накопительный буфер 16, одновременно с его выхода снимается сигнал "БУФЕР ПУСТ", который поступает на вход прерывания блока 6 запроса и обработки данных, показывая, что поступили данные от управляющего вычислительного комплекса. Блок 6 считывает данные из входного накопительного буфера 16 и дешифрует принятые данные. Если поступила команда на запрос данных о произошедших событиях, блок 6 запроса и обработки данных считывает данные из ОЗУ 8 и переписывает их в выходной накопительный буфер 17. После того как все данные переписаны в выходной накопительный буфер 17, на вход регистра 18 состояния подается сигнал готовности данных от блока 6 запроса и обработки данных. Управляющий вычислительный комплекс читает содержимое регистра 18 состояния и, если на выходе последнего присутствует признак готовности данных, считывает данные из выходного накопительного буфера 17. Данные считываются до тех пор, пока выходной накопительный буфер 17 не выдаст на вход регистра 18 состояния сигнал о том, что буфер 12 пуст. При чтении управляющий вычислительный комплекс после считывания каждого байта данных читает регистр 18 состояния и проверяет, установлен ли сигнал "БУФЕР ПУСТ" на выходе выходного 17 накопительного буфера. Это означает, что все данные из буфера 17 считаны.

В случае, когда необходимо подключить или отключить датчики или включить (отключить) контроль состояния линии, управляющий вычислительный комплекс посылает соответствующую команду на отключение (подключение) датчиков 2 телесигнализации или включение (отключение) контроля состояния линии. Обмен данными осуществляется аналогично тому, как это происходит при запросе данных.

Предлагаемое техническое решение за счет введения блока предварительной обработки данных, блока гальванической развязки, последовательного интерфейса и новых связей между узлами устройства позволило создать более простое и надежное устройство, чем известные аналоги.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Патент РФ 2079882, МПК G 06 F 17/40, опубл. 20.05.97.

2. Патент РФ 2079881, МПК G 06 F 17/40, опубл. 20.07.96 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах сбора и обработки быстроменяющихся данных с множества каналов. Технический результат заключается в создании многоканального устройства регистрации быстроменяющихся сигналов о состоянии контролируемых объектов. Устройство содержит управляющий вычислительный комплекс, n входных цепей, m мультиплексоров, блок предварительной обработки данных, оперативное запоминающее устройство, блок запроса и обработки данных, блок ввода-вывода данных, блок гальванической развязки, регистр адреса, датчики телесигнализации. 2 з.п.ф-лы, 1 ил.

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079881C1 |

| RU 2066473 C1, 10.09.1996 | |||

| Устройство для уплотнения баласта железнодорожного пути | 1933 |

|

SU45308A1 |

| Диодный функциональный преобразователь | 1960 |

|

SU131514A1 |

Авторы

Даты

2003-12-10—Публикация

2002-02-20—Подача