Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении высокопроизводительных матричных, конвейерных, систолических, векторных и других процессоров, в которых в процессе обработки происходит движение данных в вычислительной среде, а также при построении коммутационных средств управляющих и информационно-измерительных систем.

Известен модуль матричного коммутатора, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый и второй дешифраторы, элемент И (а.с. 1575167 СССР G 06 F 7/00, 15/16; опубл. 30.06.90; БИ N 24).

Недостатками известного модуля являются ограниченные коммутационные возможности, обусловленные наличием выходных связей только с двумя соседними модулями в матричном коммутаторе, а также существенная зависимость сложности блока анализа очереди сообщений от количества входных связей модуля с соседними модулями.

Наиболее близким к предлагаемому устройству по технической сущности является устройство для формирования маршрута сообщения в однородной вычислительной системе, содержащее девять буферных запоминающих блоков, блок памяти констант, блок считывания информации, регистр, демультиплексор, первый блок сравнения, второй блок сравнения, блок элементов И, блок элементов ИЛИ, элемент ИЛИ, блок синхронизации, элемент И (а.с. 1462344 СССР G 06 F 15/16; опубл. 28.02.89, БИ N 8).

Недостатком указанного устройства является узкая область применения, что связано с отсутствием средств выбора опрашиваемого буферного запоминающего блока в зависимости от текущей длины очереди сообщений. Отсутствие подобных средств может вызвать быстрое переполнение буферных запоминающих блоков и, следовательно, возникновение некорректных режимов функционирования.

Технической задачей, на решение которой направлено заявляемое изобретение, является расширение области применения устройства путем включения в него средств, обеспечивающих выбор опрашиваемого буферного запоминающего блока в зависимости от длины очереди сообщений.

Техническая задача решается тем, что в устройство для формирования маршрута сообщения, содержащее с первого по девятый буферные запоминающие блоки, блок памяти констант, регистр, демультиплексор, первый и второй блоки сравнения, блок элементов И, блок элементов ИЛИ, элемент ИЛИ, элемент И и блок синхронизации, причем информационные входы буферных запоминающих блоков с первого по девятый подключены к информационным входам устройства с первого по девятый соответственно, первые управляющие входы буферных запоминающих блоков с первого по девятый соединены с информационными входами устройства с первого по девятый соответственно, информационные выходы буферных запоминающих блоков с первого по девятый соединены со входами блока элементов ИЛИ с первого по девятый соответственно, первые управляющие выходы буферных запоминающих блоков с первого по девятый соединены со входами элемента ИЛИ с первого по девятый соответственно, выход блока элементов ИЛИ подключен к информационному входу регистра, вход синхронизации которого соединен со вторым выходом блока синхронизации, вход запуска которого подключен к выходу элемента ИЛИ, третий выход блока синхронизации соединен со входом синхронизации блока памяти констант, первый и второй выходы которого подключены к первым входам первого и второго блоков сравнения соответственно, выходы первой и второй группы регистра соединены с вторыми входами первого и второго блоков сравнения соответственно, выходы третьей группы регистра и четвертый выход блока синхронизации подключены к первому входу блока элементов И, выходы первой, второй и третьей групп регистра и четвертый выход блока синхронизации соединены с информационным входом демультиплексора, выходы "Больше", "Меньше" и "Равно" первого и второго блоков сравнения соединены с управляющими входами демультиплексора с первого по шестой соответственно, выходы "Равно" первого и второго блоков сравнения соединены с первым и вторым входами элемента И соответственно, выход элемента И подключен ко второму входу блока элементов И, выход которого является первым выходом устройства, выходы демультиплексора с первого по восьмой являются выходами устройства со второго по девятый соответственно, дополнительно введен блок анализа очередей сообщений, включающий блоки элементов ИЛИ с первого по восьмой, блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ с первого по восьмой, первую группу элементов И, вторую группу элементов И, причем первый, третий, пятый и седьмой информационные входы блока анализа очередей сообщений соединены с первыми входами блоков элементов ИЛИ с первого по четвертый соответственно и первыми входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ с первого по четвертый соответственно, второй, четвертый, шестой и восьмой информационные входы блока анализа очередей сообщений соединены со вторыми входами блоков элементов ИЛИ с первого по четвертый соответственно, выходы которых соединены со вторыми входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ с первого по четвертый соответственно, выход первого блока элементов ИЛИ соединен с первым входом пятого блока элементов ИЛИ и первым входом пятого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выход второго блока элементов ИЛИ соединен со вторым входом пятого блока элементов ИЛИ, выход которого соединен со вторым входом пятого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выход третьего блока элементов ИЛИ соединен с первым входом шестого блока элементов ИЛИ и первым входом шестого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выход четвертого блока элементов ИЛИ соединен со вторым входом шестого блока элементов ИЛИ, выход которого соединен со вторым входом шестого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выход пятого блока элементов ИЛИ соединен с первым входом седьмого блока элементов ИЛИ и первым входом седьмого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выход шестого блока элементов ИЛИ соединен со вторым входом седьмого блока элементов ИЛИ, выход которого соединен со вторым входом седьмого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выход седьмого блока элементов ИЛИ соединен с первым входом восьмого блока элементов ИЛИ и первым входом восьмого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, девятый информационный вход блока анализа очередей сообщений соединен со вторым входом восьмого блока элементов ИЛИ, выход которого соединен со вторым входом восьмого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ, выходы блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - НЕ с первого по восьмой соединены с входами элементов И первой группы с первого по восьмой соответственно, синхронизирующий вход блока анализа очередей сообщений соединен с первыми входами элементов И второй группы с первого по девятый, выход первого элемента И первой группы соединен со вторым входом первого элемента И второй группы и со вторым входом второго элемента И второй группы, выход второго элемента И первой группы соединен со вторым входом третьего элемента И второй группы и со вторым входом четвертого элемента И второй группы, выход третьего элемента И первой группы соединен со вторым входом пятого элемента И второй группы и со вторым входом шестого элемента И второй группы, выход четвертого элемента И первой группы соединен со вторым входом седьмого элемента И второй группы и со вторым входом восьмого элемента И второй группы, выход пятого элемента И первой группы соединен с третьим входом первого элемента И второй группы, с третьим входом второго элемента И второй группы, с третьим входом третьего элемента И второй группы и с третьим входом четвертого элемента И второй группы, выход шестого элемента И первой группы соединен с третьим входом пятого элемента И второй группы, с третьим входом шестого элемента И второй группы, с третьим входом седьмого элемента И второй группы и с третьим входом восьмого элемента И второй группы, выход седьмого элемента И первой группы соединен с четвертым входом первого элемента И второй группы, с четвертым входом второго элемента И второй группы, с четвертым входом третьего элемента И второй группы, с четвертым входом четвертого элемента И второй группы, с четвертым входом пятого элемента И второй группы, с четвертым входом шестого элемента И второй группы, с четвертым входом седьмого элемента И второй группы и с четвертым входом восьмого элемента И второй группы, выход восьмого элемента И первой группы соединен с пятым входом первого элемента И второй группы, с пятым входом второго элемента И второй группы, с пятым входом третьего элемента И второй группы, с пятым входом четвертого элемента И второй группы, с пятым входом пятого элемента И второй группы, с пятым входом шестого элемента И второй группы, с пятым входом седьмого элемента И второй группы, с пятым входом восьмого элемента И второй группы, со вторым входом девятого элемента И второй группы, выходы элементов И второй группы с первого по девятый являются информационными выходами блока анализа очередей сообщений с первого по девятый соответственно, информационные выходы блока анализа очередей сообщений с первого по девятый соединены со вторыми управляющими входами буферных запоминающих блоков с первого по девятый соответственно, информационные входы блока анализа очередей сообщений с первого по девятый соединены со вторыми управляющими выходами буферных запоминающих блоков с первого по девятый соответственно, синхронизирующий вход блока анализа очередей сообщений соединен с первым выходом блока синхронизации.

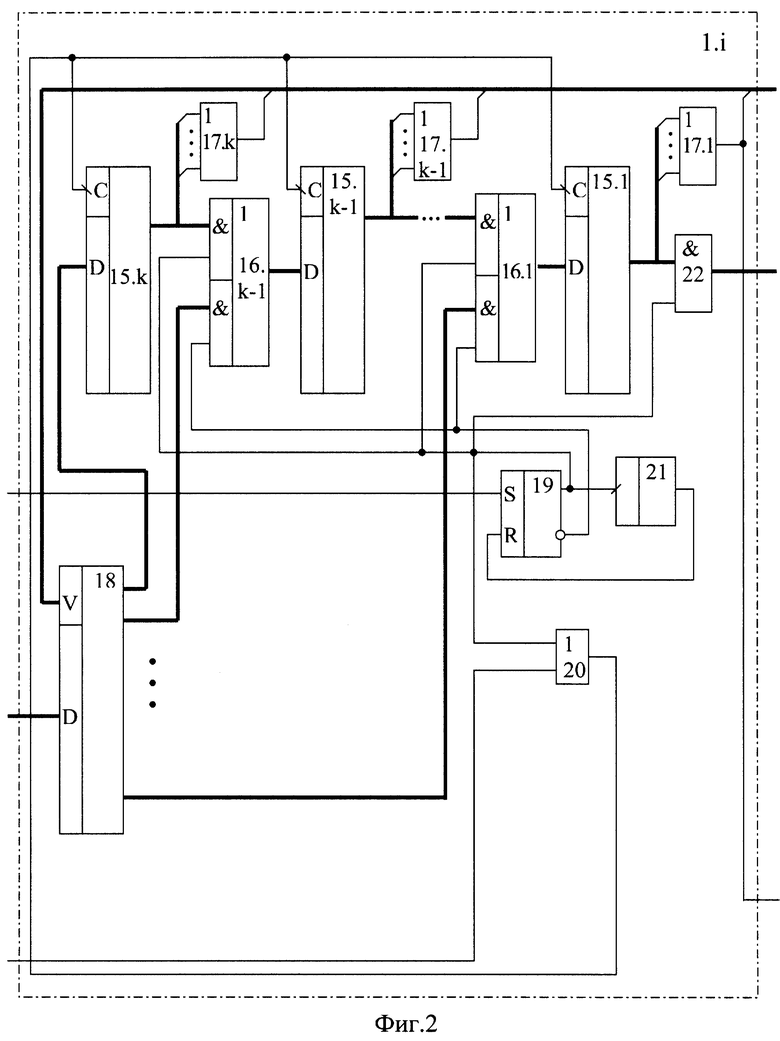

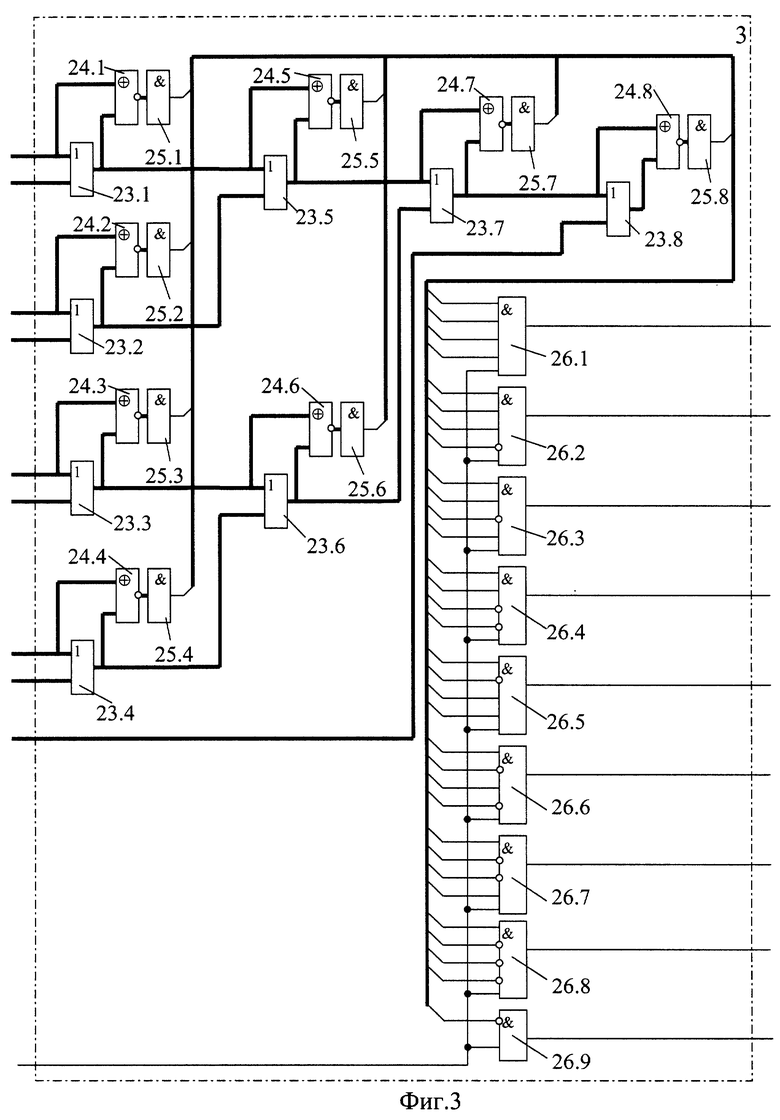

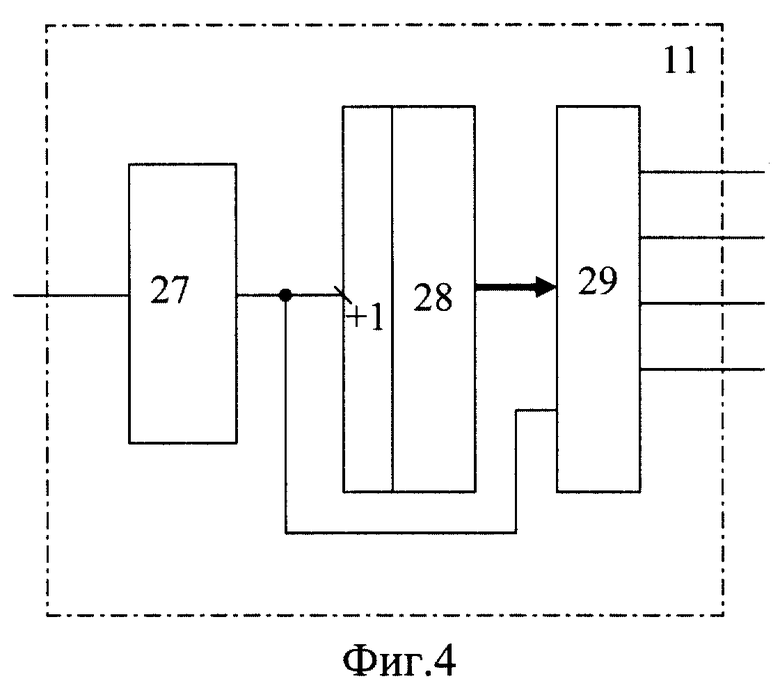

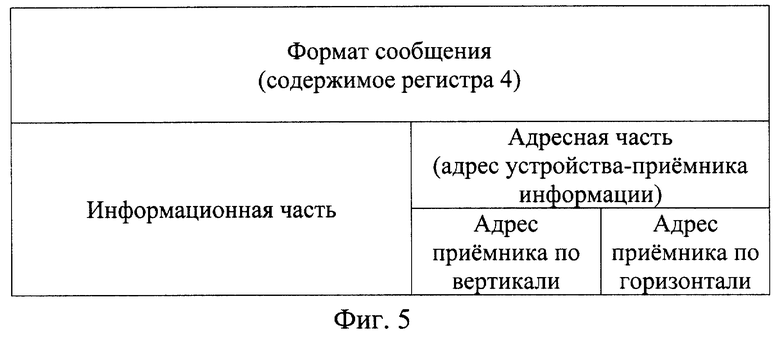

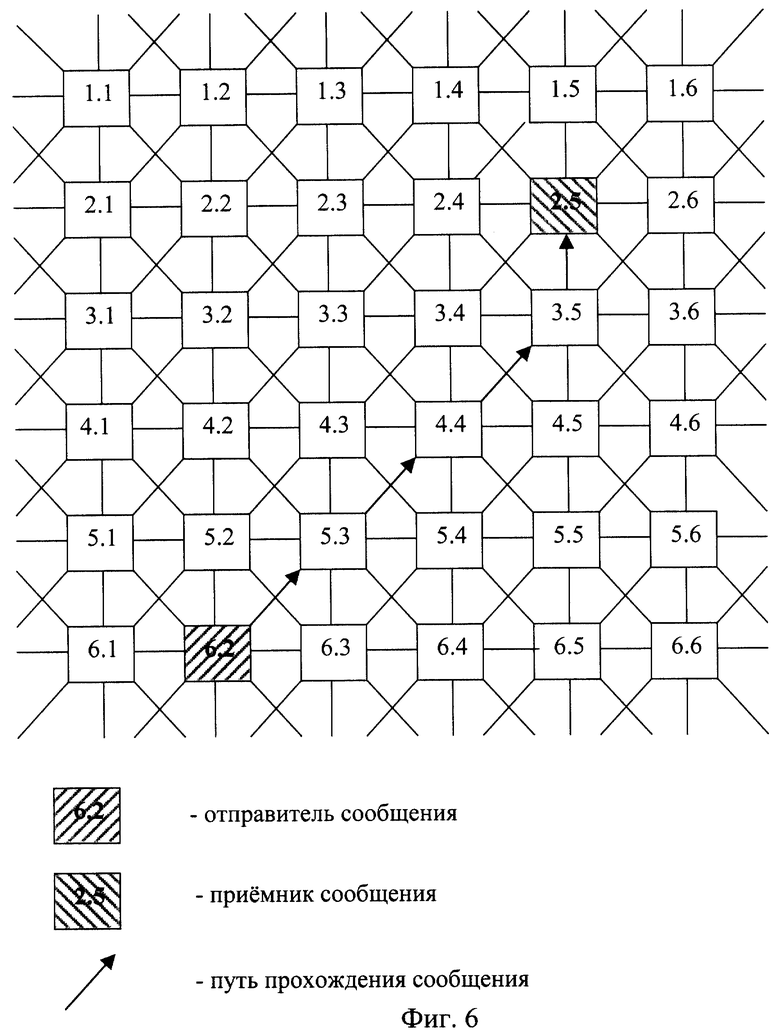

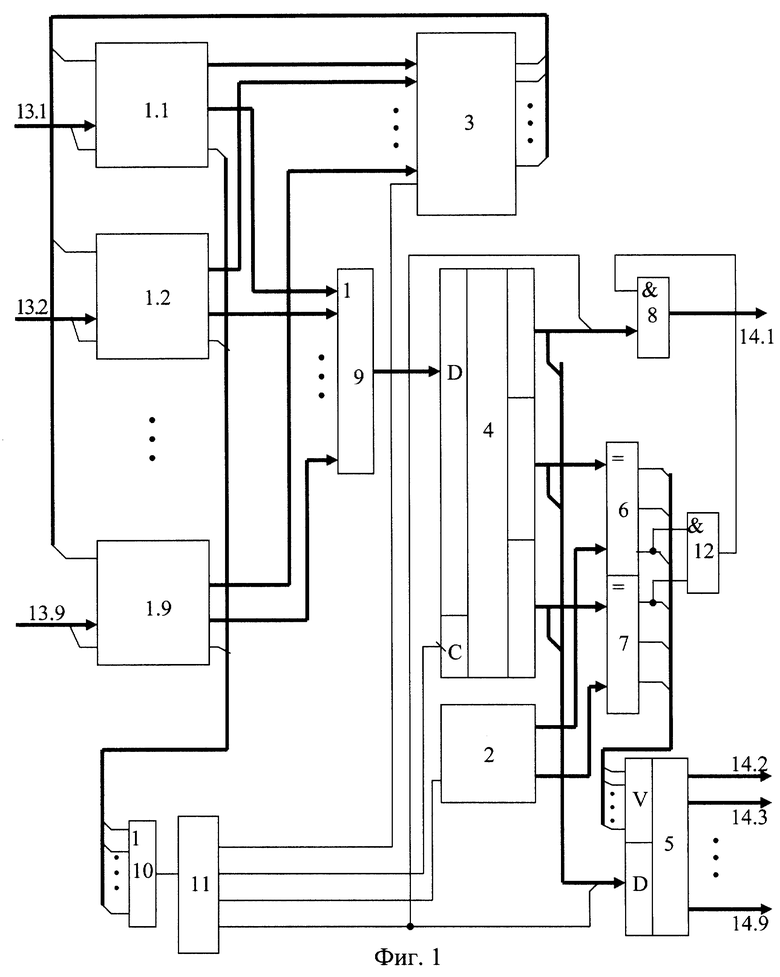

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема устройства для формирования маршрута сообщения; на фиг. 2 представлена функциональная схема буферного запоминающего блока; на фиг. 3 дана функциональная схема блока анализа очередей сообщений; на фиг. 4 изображена функциональная схема блока синхронизации; на фиг. 3 показан формат сообщений (содержимое регистра 4); на фиг. 6 показана схема передачи сообщения между устройствами в системе обмена сообщениями.

Общие особенности функционирования устройства.

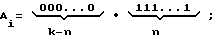

Предлагаемое устройство совместно с другими аналогичными устройствами образует систему обмена сообщениями. Система представляет собой однородную матричную структуру, каждый модуль (устройство) которой соединен по восьми направлениям с соседними модулями (устройствами). Каждому модулю (устройству) системы присваивается адрес (идентификатор), состоящий из двух кодов, определяющих местоположение модуля в матрице. Первый код соответствует номеру строки, второй номеру столбца (фиг. 6). Аналогичные коды включаются в адресную часть сообщения для идентификации их приемников (фиг. 3). Передача информации между любыми модулями системы осуществляется по минимальному физическому пути через другие модули (транзитным способом). Поступающие в модуль сообщения заносятся в буферные запоминающие блоки 1.i (i = 1,9) (фиг. 1) и затем считываются в порядке поступления для выдачи очередному модулю. Выбор сообщения для обработки (выбор буферного запоминающего блока) осуществляется на основе анализа соотношения длин очередей сообщений в буферных запоминающих блоках. Длины очередей сообщений отображаются соответствующими кодами. Код длины очереди сообщений буферного запоминающего блока 1.i представлен в виде:

где n - текущая длина очереди сообщений в блоке 1.i;

k - максимальная длина очереди в буферных запоминающих блоках;

"." - символ операции конкатенации (сцепления).

Например, если длина очереди равна 3, то Аi = 00... 000111.

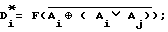

При таком представлении максимальный из двух кодов длин очередей Ai и Aj определяется как:

Признак выбора максимального кода длины очереди из кодов Аi и Aj определяется как:

где ⊕ - символ операции ИСКЛЮЧАЮЩЕЕ ИЛИ,

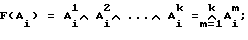

F - функция поразрядного логического умножения:

где m - номер разряда.

Если Ai ≥ Aj (то есть длина очереди сообщений в блоке 1.i больше, чем в блоке 1.j), то D

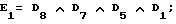

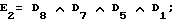

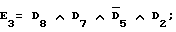

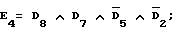

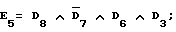

С учетом сказанного признаки выбора буферных запоминающих блоков 1.1-1.9 определяются следующим образом:

Если E1= 1, то буферный запоминающий блок 1.1 содержит максимальное количество сообщений и сообщение считывается из буферного запоминающего блока 1.1. Если E2=1, то буферный запоминающий блок 1.2 содержит максимальное количество сообщений и сообщение считывается из буферного запоминающего блока 1.2 и т.д.

После считывания сообщения оно выдается очередному модулю.

Выбор направления выдачи сообщения осуществляется по следующему правилу: если C>А - вверх; если C<А - вниз; если C=А - стоп; если D>B - влево; если D<B - вправо; если D=B - стоп; где А.В - адрес модуля-приемника сообщения; C. D - адрес текущего модуля. Если C=А и D=B, то сообщение доставлено модулю-приемнику.

Устройство для формирования маршрута сообщения (фиг. 1) содержит буферные запоминающие блоки 1.1 - 1.9, блок 2 памяти констант, регистр 4, демультиплексор 5, первый 6 и второй 7 блоки сравнения, блок элементов И 8, блок элементов ИЛИ 9, элемент ИЛИ 10, блок 11 синхронизации и элемент И 12, причем информационные входы буферных запоминающих блоков 1.1 - 1.9 соединены с информационными входами 13.1-13.9 устройства соответственно, первые управляющие входы буферных запоминающих блоков 1.1 - 1.9 соединены с информационными входами 13.1 - 13.9 устройства соответственно, информационные выходы буферных запоминающих блоков 1.1 - 1.9 соединены с входами блока элементов ИЛИ 9 с первого по девятый соответственно, первые управляющие выходы буферных запоминающих блоков 1.1 - 1.9 соединены с входами элемента ИЛИ 10 с первого по девятый соответственно, выход блока элементов ИЛИ 9 подключен к информационному входу регистра 4, вход синхронизации которого соединен со вторым выходом блока 11 синхронизации, вход запуска которого подключен к выходу элемента ИЛИ 10, третий выход блока 11 синхронизации соединен с входом синхронизации блока 2 памяти констант, первый и второй выходы которого подключены к первым входам блоков 6 и 7 сравнения соответственно, выходы первой и второй группы регистра 4 соединены с вторыми входами блоков 6 и 7 сравнения соответственно, выходы третьей группы регистра 4 и четвертый выход блока 11 синхронизации подключены к первому входу блока элементов И 8, выходы первой, второй и третьей групп регистра 4 и четвертый выход блока 11 синхронизации соединены с информационным входом демультиплексора 5, выходы "Больше", "Меньше" и "Равно" блоков 6 и 7 сравнения соединены с управляющими входами демультиплексора 5 с первого по шестой соответственно, выходы "Равно" блоков 6 и 7 сравнения соединены с первым и вторым входами элемента И 12 соответственно, выход элемента И 12 подключен ко второму входу блока элементов И 8, выход которого является выходом 14.1 устройства, выходы демультиплексора 5 с первого по восьмой являются выходами 14.2 - 14.9 устройства соответственно, а также дополнительно введенный блок 3 анализа очередей сообщений, информационные выходы которого с первого по девятый соединены со вторыми управляющими входами буферных запоминающих блоков 1.1 - 1.9 соответственно, информационные входы блока 3 анализа очередей сообщений с первого по девятый соединены со вторыми управляющими выходами буферных запоминающих блоков 1.1 - 1.9 соответственно, синхронизирующий вход блока 3 анализа очередей сообщений соединен с первым выходом блока 11 синхронизации.

Буферный запоминающий блок 1.i (i=1,9) (фиг. 2) содержит регистры 15.1 - 15.k, блоки элементов И-ИЛИ 16.1 - 16.(k-1), демультиплексор 18, триггер 19, элемент ИЛИ 20, одновибратор 21, блок элементов И 22, причем информационный вход буферного запоминающего блока соединен с информационным входом демультиплексора 18, выходы которого с первого по (k-1)-й соединены с третьими входами блоков элементов И-ИЛИ 16.1-16.(k-1) соответственно, k-й выход демультиплексора 18 соединен с информационным входом регистра 15.k, первый управляющий вход буферного запоминающего блока соединен с первым входом элемента ИЛИ 20, второй управляющий вход буферного запоминающего блока соединен с S-входом триггера 19, прямой выход триггера 19 соединен с запускающим входом одновибратора 21, вторыми входами блоков элементов И-ИЛИ 16.1 - 16.(k-1), со вторым входом блока элементов И 22 и вторым входом элемента ИЛИ 20, инверсный выход триггера 19 соединен с четвертыми входами блоков элементов И-ИЛИ 16.1-16.(k-1), выход одновибратора 21 соединен с R-входом триггера 19, выход элемента ИЛИ 20 соединен с синхронизирующими входами регистров 15.1-15. k, выходы регистров 15.2-15.k соединены с первыми входами блоков элементов И-ИЛИ 16.1-16.(k-1) соответственно, выходы которых подключены к информационным входам регистров 15.1- 15.(k-1) соответственно, выход регистра 15.1 соединен с первым входом блока элементов И 22, выход которого является информационным выходом буферного запоминающего блока, а также дополнительно введенную группу элементов ИЛИ 17.1-17.k, входы которых соединены с выходами регистров 15.1-15.k соответственно, выход элемента ИЛИ 17.1 соединен с первым управляющим выходом буферного запоминающего блока, выходы элементов ИЛИ 17.1-17. k соединены с управляющими входами демультиплексора 18 и с вторым управляющим выходом буферного запоминающего блока.

Блок 3 анализа очередей сообщений (фиг. 3) содержит блоки элементов ИЛИ 23.1-23.8, блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.1-24.8, первую группу элементов И 25.1-25.8, вторую группу элементов И 26.1-26.9, причем первый, третий, пятый и седьмой информационные входы блока анализа очередей сообщений соединены с первыми входами блоков элементов ИЛИ 23.1-23.4 соответственно и первыми входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.1-24.4 соответственно, второй, четвертый, шестой и восьмой информационные входы блока анализа очередей сообщений соединены со вторыми входами блоков элементов ИЛИ 23.1-23.4 соответственно, выходы которых соединены со вторыми входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.1-24.4 соответственно, выход блока элементов ИЛИ 23.1 соединен с первым входом блока элементов ИЛИ 23.5 и первым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.5, выход блока элементов ИЛИ 23.2 соединен со вторым входом блока элементов ИЛИ 23.5, выход которого соединен со вторым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ -НЕ 24.5, выход блока элементов ИЛИ 23.3 соединен с первым входом блока элементов ИЛИ 23.6 и первым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.6, выход блока элементов ИЛИ 23.4 соединен со вторым входом блока элементов ИЛИ 23.6, выход которого соединен со вторым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.6, выход блока элементов ИЛИ 23.5 соединен с первым входом блока элементов ИЛИ 23.7 и первым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.7, выход блока элементов ИЛИ 23.6 соединен со вторым входом блока элементов ИЛИ 23.7, выход которого соединен со вторым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.7, выход блока элементов ИЛИ 23.7 соединен с первым входом блока элементов ИЛИ 23.8 и первым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.8, девятый информационный вход блока анализа очередей сообщений соединен со вторым входом блока элементов ИЛИ 23.8, выход которого соединен со вторым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.8, выходы блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.1-24.8 соединены с входами элементов И 25.1-25.8 соответственно, синхронизирующий вход блока анализа очередей сообщений соединен с первыми входами элементов И 26.1-26.9, выход элемента И 25.1 соединен со вторым входом элемента И 26.1 и со вторым входом элемента И 26.2, выход элемента И 25.2 соединен со вторым входом элемента И 26.3 и со вторым входом элемента И 26.4, выход элемента И 25.3 соединен со вторым входом элемента И 26.5 и с вторым входом элемента И 26.6, выход элемента И 25.4 соединен со вторым входом элемента И 26.7 и со вторым входом элемента И 26.8, выход элемента И 25.5 соединен с третьим входом элемента И 26.1, с третьим входом элемента И 26.2, с третьим входом элемента И 26.3 и с третьим входом элемента И 26.4, выход элемента И 25.6 соединен с третьим входом элемента И 26.5, с третьим входом элемента И 26.6, с третьим входом элемента И 26.7 и с третьим входом элемента И 26.8, выход элемента И 25.7 соединен с четвертым входом элемента И 26.1, с четвертым входом элемента И 26.2, с четвертым входом элемента И 26.3, с четвертым входом элемента И 26.4, с четвертым входом элемента И 26.5, с четвертым входом элемента И 26.6, с четвертым входом элемента И 26.7 и с четвертым входом элемента И 26.8, выход элемента И 25.8 соединен с пятым входом элемента И 26.1, с пятым входом элемента И 26.2, с пятым входом элемента И 26.3, с пятым входом элемента И 26.4, с пятым входом элемента И 26.5, с пятым входом элемента И 26.6, с пятым входом элемента И 26.7, с пятым входом элемента И 26.8, со вторым входом элемента И 26.9, выходы элементов И 26.1-26.9 являются информационными выходами блока анализа очередей сообщений с первого по девятый соответственно.

Блок 11 синхронизации (фиг. 4) содержит генератор 27 тактовых импульсов, счетчик 28 и дешифратор 29, причем разрешающий вход генератора 27 тактовых импульсов соединен с входом запуска блока синхронизации, выход генератора 27 тактовых импульсов соединен с управляющим входом дешифратора 29 и со счетным входом счетчика 28, выход которого соединен с информационным входом дешифратора 29, выходы которого с первого по четвертый являются выходами блока синхронизации с первого по четвертый соответственно.

Назначение элементов устройства для формирования маршрута сообщения (фиг. 1) состоит в следующем.

Буферные запоминающие блоки 1.1-1.9 предназначены для организации очередей сообщений, поступающих от восьми соседних модулей (устройств) и собственного операционного устройства для передачи информации соседним устройствам.

Блок 2 памяти констант предназначен для хранения кода (идентификатора), определяющего местонахождение модуля (устройства) в матрице системы обмена сообщениями.

Блок 3 анализа очередей сообщений предназначен для анализа соотношения длин очередей сообщений в буферных запоминающих блоках 1.1-1.9 и организации их опроса в зависимости от длины очереди поступивших сообщений.

Регистр 4 предназначен для хранения адресной и информационной части сообщения во время анализа и выбора направления передачи сообщения.

Демультиплексор 5 предназначен для коммутации сообщения в одном из восьми направлений к соседним устройствам.

Первый 6 и второй 7 блоки сравнения предназначены для сравнения адресной части поступившего на обслуживание сообщения с адресом данного устройства.

Блок элементов И 8 предназначен для разрешения записи (передачи) информационной части сообщения собственному операционному устройству при совпадении адресной части поступившего сообщения и адреса устройства.

Блок элементов ИЛИ 9 предназначен для объединения кодов, поступающих с информационных выходов буферных запоминающих блоков 1.1-1.9 и передачи их на информационный вход регистра 4.

Элемент ИЛИ 10 служит для формирования сигнала запуска блока 11 синхронизации при наличии хотя бы одного сообщения в буферных запоминающих блоках 1.1-1.9.

Блок 11 синхронизации предназначен для формирования четырех сдвинутых друг относительно друга последовательностей импульсов t1, t2, t3, t4 для синхронизации работы устройства.

Элемент И 12 предназначен для формирования сигнала разрешения для блока элементов И 8.

Группа информационных входов 13.1 -13.9 устройства предназначена для приема информации от восьми соседних аналогичных устройств и собственного операционного устройства.

Группа выходов 14.1-14.9 предназначена для передачи информации собственному операционному устройству и соседним аналогичным устройствам.

Назначение элементов буферного запоминающего блока (фиг. 2) состоит в следующем:

Регистры 15.1-15. k предназначены для хранения очереди поступающих на обслуживание сообщений.

Блоки элементов И-ИЛИ 16.1- 16.(k-1) предназначены для подключения информационных входов регистров 15.1-15.(k-1) либо к соответствующим выходам демультиплексора 18, либо к выходам регистров 15.2-15.k соответственно при приеме сообщения или сдвиге очереди сообщений.

Группа элементов ИЛИ 17.1-17.k предназначена для формирования кода текущей длины очереди сообщений буферного запоминающего блока. Кроме того, элемент 17.1 служит для формирования сигнала о наличии сообщения в буферном запоминающем блоке.

Демультиплексор 18 предназначен для коммутации (распределения) поступающих на обслуживание сообщений в порядке их поступления в регистры 15.1-15.k.

Триггер 19 предназначен для управления процессом записи и сдвига информации в регистрах 15.1-15.k.

Элемент ИЛИ 20 предназначен для формирования сигнала записи сообщений в регистры 15.1-15.k.

Одновибратор 21 предназначен для формирования импульса обнуления триггера 19 после сдвига очереди сообщений в регистрах 15.1-15.k.

Блок элементов И 22 предназначен для разрешения передачи сообщения из регистра 15.1 на информационный выход буферного запоминающего блока.

Назначение элементов блока 3 анализа очередей сообщений (фиг. 3) состоит в следующем.

Блоки элементов ИЛИ 23.1-23.8 и блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.1-24.8 предназначены для определения максимального значения кода длины очереди

Первая группа элементов И 25.1-25.8 предназначена для формирования сигналов Di.

Вторая группа элементов И 26.1-26.9 предназначена для формирования сигналов-признаков выбора буферных запоминающих блоков E1-E9.

Рассмотрим работу предлагаемого устройства. Учитывая, что устройство предназначено для работы в составе однородной системы обмена сообщениями, его функционирование будем рассматривать во взаимосвязи с другими аналогичными устройствами. (Структура системы на базе предлагаемого устройства, содержащей тридцать шесть идентичных устройств, представлена на фиг. 6).

В начальный момент времени (после включения питания) в буферных запоминающих блоках 1. i сообщения отсутствуют, содержимое регистров 15.1-15.k (фиг. 2) равно нулю, на прямых выходах триггеров 19 находится уровень логического нуля, на выходах элементов ИЛИ 17.1 также находится уровень логического нуля, поэтому на выходе элемента ИЛИ 10 (фиг. 1) присутствует сигнал логического нуля, блокирующий формирование импульсов блоком 11 синхронизации. В регистре 4 сообщение отсутствует. В блоке 2 памяти констант хранится адрес устройства. Цепи начальной установки на фиг. 1-4 не показаны с целью упрощения.

Работа устройства начинается в момент поступления первого сообщения (формат сообщения изображен на фиг. 5). Данное сообщение поступает на один из входов 13.1-13.9 устройства (например, 13.i), через информационный вход заносится в соответствующий буферный запоминающий блок и передается на информационный вход демультиплексора 18 (фиг. 1, 2). Кроме сообщения на вход 13. i устройства одновременно подается импульс. Так как триггер 19 находится в нулевом состоянии, то сигнал логической единицы с его инверсного выхода поступает на четвертые входы блоков элементов И-ИЛИ 16.1-16.(k-l) и разрешает тем самым прохождение информации с выходов демультиплексора 18 на информационные входы регистров 15.1-15.k. При поступлении первого сообщения регистры 15.1-15.k находятся в нулевом состоянии, и на выходах элементов ИЛИ 17.1-17. k находятся сигналы логического нуля. Эти сигналы (код длины очереди) поступают на управляющие входы демультиплексора 18 и разрешают запись поступившего сообщения в регистр 15.1. После записи сообщения в регистр 15.1 состояние этого регистра становится отлично от нулевого, что изменяет код длины очереди. Указанный код подается на управляющие входы демультиплексора 18 и обеспечивает его настройку для передачи следующего сообщения в регистр 15.2.

После занесения сообщения в буферный запоминающий блок 1.i (фиг. 2) сигнал логической единицы с выхода элемента 17.1 через первый управляющий выход буферного запоминающего блока 1. i передается на элемент ИЛИ 10 (фиг. 1), через который проходит на вход запуска блока 11 синхронизации. Сигнал логической единицы на входе запуска блока 11 синхронизации разрешает формирование импульсов синхронизации на его выходах. Одновременно код длины очереди со второго управляющего выхода буферного запоминающего блока 1.i поступает на соответствующий информационный вход блока 3 анализа очередей сообщений. Таким образом, запуск устройства завершается. Далее на входы 13.1-13.9 устройства начинают последовательно поступать следующие сообщения, что приводит к возникновению их очередей в буферных запоминающих блоках. Коды длин указанных очередей формируются на вторых управляющих выходах блоков 1.1-1.9 и поступают на информационные входы блока 3 анализа очередей сообщений. Блок 3 анализа очередей сообщений анализирует соотношение кодов длин очередей сообщений и формирует признаки выбора буферных запоминающих блоков E1-E9.

Предположим, что во всех буферных запоминающих блоках 1.1-1.9 находятся сообщения и код длины очереди сообщений, поступающий от буферного запоминающего блока 1.1, равен А1= <<0. . . 0001111>>, от блока 1.2-А2=<<0... 0000111>>, от 1.3-А3=<<0...0000011>>, от 1.4-A4=<<0...0011111>>, от 1.5-A5= <<0. . . 0111111>>, от 1.6-A6=<<0...0011111>>, от 1.7-A7=<<0...0011111>>, от 1.8-A8= <<0. . . 0000011>>, от 1.9-A9=<<0...0000111>>. Тогда на входы блока элементов ИЛИ 23.1 (фиг. 3) подаются коды А1=<<0... 0001111>> и A2=<<0... 0000111>>, в результате чего на выходе блока 23.1 образуется код max{A1,A2}= A1= <<0. ..0001111>>. Этот код совместно с кодом A1=<<0...0001111>> подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.1. В результате на выходе блока 24.1 образуется код <<1.1111111>>. Данный код подается на входы элемента И 25.1 ив результате на выходе элемента И 25.1 образуется сигнал логической единицы(D1=1).

На входы блока элементов ИЛИ 23.2 подаются коды А3=<<0...0000011>> и А4= <<0. ..0011111>>, в результате чего на выходе блока 23.2 образуется код max{ A3, A4}=A4=<<0...0011111>>. Этот код совместно с кодом А3=<<0...0000011> подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.2. В результате на выходе блока 24.2 образуется код <<1...1100011>>. Данный код подается на входы элемента И 25.2. В результате на выходе элемента И 25.2 образуется сигнал логического нуля (D2=0).

На входы блока элементов ИЛИ 23.3 подаются коды A5=<<0...0111111>> и A6= <<0. ..0011111>>, в результате чего на выходе блока 23.3 образуется код max{ A5, A6} = A5= <<0...0111111>>. Этот код совместно с кодом A5=<<0...0111111>> подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.3. В результате на выходе блока 24.3 образуется код <<111...11111>>. Данный код подается на входы элемента И 25.3. В результате на выходе элемента И 25.3 образуется сигнал логической единицы (D3=1).

На входы блока элементов ИЛИ 23.4 подаются коды А7=<<0...0011111>> и A8= <<0. ..0000011>>, в результате чего на выходе блока 23.4 образуется код max{ A7, A8} = A7= <<0...0011111>>. Этот код совместно с кодом A7=<<0...0011111>> подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.4. В результате этого на выходе блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.4 образуется код <<111. ..11111>>. Данный код подается на входы элемента И 25.4. В результате на выходе элемента И 25.4 образуется сигнал логической единицы (D4=1).

Затем на входы блока элементов ИЛИ 23.5 подаются коды A1=<<0...0001111>> и А4= <<0. . . 0011111>> с выходов блоков 23.1 и 23.2 соответственно, в результате чего на выходе блока 23.5 образуется код max{A1,A4}=A4=<<0... 0011111>>. Этот код совместно с кодом А1=<<0...0001111>> с выхода блока 23.1 подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.5. В результате на выходе блока 24.5 образуется код <<1...1101111>>. Данный код подается на входы элемента И 25.5 и формирует на выходе элемента И 25.5 сигнал логического нуля (D5=0).

Одновременно на входы блока элементов ИЛИ 23.6 подаются коды А5=<<0... 0111111>> и A7=<<0...0011111>> с выходов блоков 23.3 и 23.4 соответственно, в результате чего на выходе блока 23.6 образуется код max{A5,A7}=A5= <<0.0111111>>. Этот код совместно с кодом А5=<<0.0111111>> с выхода блока 23.3 подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.6. В результате на выходе блока 24.6 образуется код <<1.1111111>>. Данный код подается на входы элемента И 25.6 и формирует на выходе элемента И 25.6 сигнал логической единицы(D6=1).

Далее на входы блока элементов ИЛИ 23.7 подаются коды А4=<<0...0011111>> и A5= <<0. . . 0111111>> с выходов блоков 23.5 и 23.6 соответственно, в результате чего на выходе блока 23.7 образуется код max{A4,A5}=A5=<<0... 0111111>>. Этот код совместно с кодом A4=<<0...0011111>> с выхода блока 23.5 подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.7. В результате на выходе блока 24.7 образуется код <<1...1011111>>. Данный код подается на входы элемента И 25.7 и формирует на выходе элемента И 25.7 сигнал логического нуля(D7=0).

И наконец на входы блока элементов ИЛИ 23.8 подаются коды A5=<<0... 0111111>> и А9= <<0...0000011>>, с выхода блока 23.7 и девятого информационного входа блока анализа очередей сообщений соответственно, в результате чего на выходе блока 23.8 образуется код max{A5,A9}=A5=<<0...0111111>>. Этот код совместно с кодом A5=<<0...0111111>> с выхода блока 23.7 подается на входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 24.8. В результате на выходе блока 24.8 образуется код <<111...11111>>. Данный код подается на входы элемента И 25.8 и формирует на выходе элемента И 25.8 сигнал логической единицы(D8=1).

Далее сигналы с выходов элементов И 25.1-25.8 подаются на входы элементов И 26.1 - 26.9 и обеспечивают открывание элемента 26.5, блокируя при этом элементы 26.1-26.4, 26.6-26.9. Очередной импульс t1 от блока 11 синхронизации поступает на синхронизирующий вход блока 3 анализа очередей сообщений и, проходя через открытый элемент 26.5, появляется на пятом информационном выходе блока 3. Появление указанного импульса означает E5=1 (осуществляется опрос буферного запоминающего блока 1.5).

Импульс с пятого информационного выхода блока 3 поступает на второй управляющий вход буферного запоминающего блока 1.5 (фиг. 2), устанавливает триггер 19 в единичное состояние и разрешает выдачу сообщения через блок элементов И 22 с выхода регистра 15.1. Кроме того, единичный сигнал с прямого выхода триггера 19 формирует единичный уровень сигнала на выходе элемента 20, подключает информационные входы регистров 15.1-15.(k-l) к выходам регистров 15.2-15.k соответственно и возбуждает одновибратор 21.

Сообщение с выхода регистра 15.1 блока 1.5 через блок элементов И 22, а затем - через блок элементов ИЛИ 9 (фиг. 1) поступает на информационный вход регистра 4. По импульсу t2 с блока 11 синхронизации поступившее сообщение заносится в регистр 4. Одновременно в блоке 1.5 происходит сдвиг очереди сообщений. Импульс, возникающий на выходе одновибратора 21, восстанавливает нулевое состояние триггера 19. В результате на прямом выходе этого триггера формируется переход уровня сигнала из единицы в нуль (срез сигнала). Этот переход через элемент ИЛИ 20 воздействует на синхронизирующие входы регистров 15.1-15. k и обеспечивает сдвиг очереди сообщений. На выходе регистра 15.1 появляется информация, ранее размещавшаяся в регистре 15.2.

Далее осуществляется выбор направления выдачи сообщения из регистра 4. Адресная часть сообщения поступает на вторые входы блоков 6 и 7 сравнения. В то же время по импульсу t3 на первые входы блоков 6 и 7 сравнения с выходов блока 2 памяти констант поступает адрес (идентификатор), определяющий местоположение данного устройства в матрице устройств. В зависимости от соотношения этих двух адресов (кодов) определяется направление дальнейшей передачи сообщения (см. выше). При совпадении кодов как по вертикали, так и по горизонтали на выходах "равно" блоков 6 и 7 сравнения формируются единичные сигналы. Эти сигналы образуют единичный сигнал на выходе элемента И 12. Указанный сигнал, поступая на второй вход блока элементов И 8, разрешает прохождение информационной части сообщения на выход 14.1 устройства для последующей обработки сообщения операционным устройством. В случае другой комбинации сигналов на выходах блоков 6 и 7 сравнения правило выбора направления дальнейшей передачи сообщения реализуется демультиплексором 5. Информационный вход демультиплексора 5 подключается к выходу 14.j (J=2,9) устройства и сообщение из регистра 4 через выход 14.j устройства поступает к одному из соседних аналогичных устройств системы. Прием сообщения соседним устройством или операционным устройством обеспечивает импульс t4 с четвертого выхода блока 11 синхронизации.

Сообщение, переданное на выход 14.j, аналогичным образом обрабатывается соседним устройством и перемещается далее до тех пор, пока не будет достигнут модуль - приемник. При этом траектория (маршрут) перемещения сообщения может быть подобна выделенной на фиг. 6.

Работа устройства завершается тогда, когда регистры 15.1- 15.k буферных запоминающих блоков 1.1-1.9 переходят в нулевое состояние. В этом случае на выходах элементов ИЛИ 17.1 блоков 1.1 - 1.9 присутствует уровень логического нуля, индицирующий отсутствие сообщений в соответствующем буферном запоминающем блоке. Сигналы логического нуля с выходов элементов 17.1 через первые управляющие выходы соответствующих буферных запоминающих блоков поступают на входы элемента ИЛИ 10 и формируют на его выходе нулевой уровень сигнала. Уровень логического нуля с выхода элемента ИЛИ 10 поступает на вход запуска блока 11 синхронизации и запрещает формирование импульсов на выходах блока 11 синхронизации; устройство переходит в состояние ожидания.

Таким образом, как следует из описания, введение в устройство дополнительных элементов и обусловленных ими связей позволяет организовать выбор опрашиваемого буферного запоминающего блока в зависимости от длины очереди сообщений. Тем самым уменьшается вероятность потери сообщений вследствие переполнения буферных запоминающих блоков, обеспечивается возможность увеличения интенсивности потоков входящих сообщений устройства без увеличения максимальной длины очередей k, и, следовательно, имеет место расширение области применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении высокопроизводительных матричных, конвейерных, систолических, векторных и других процессоров, в которых в процессе обработки происходит движение данных в вычислительной среде, а также при построении коммутационных средств управляющих и информационно-измерительных систем. Техническим результатом является расширение области применения устройства путем включения в него средств, обеспечивающих выбор буферного запоминающего блока с наибольшим числом сообщений. Устройство содержит девять буферных запоминающих блоков, блок памяти констант, регистр, демультиплексор, два блока сравнения, блок элементов И, блок элементов ИЛИ, элемент ИЛИ, элемент И, блок синхронизации и блок анализа очередей сообщений. 2 з.п. ф-лы, 6 ил.

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Модуль матричного коммутатора | 1988 |

|

SU1575167A1 |

| US 5151996 A, 29.09.1992 | |||

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

Авторы

Даты

2001-10-20—Публикация

2000-02-08—Подача