(54) СЕЛЕКТОРНЫЙ КАПАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1973 |

|

SU517019A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Селекторный канал | 1973 |

|

SU519703A1 |

| Устройство для ввода и вывода информации | 1980 |

|

SU905811A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

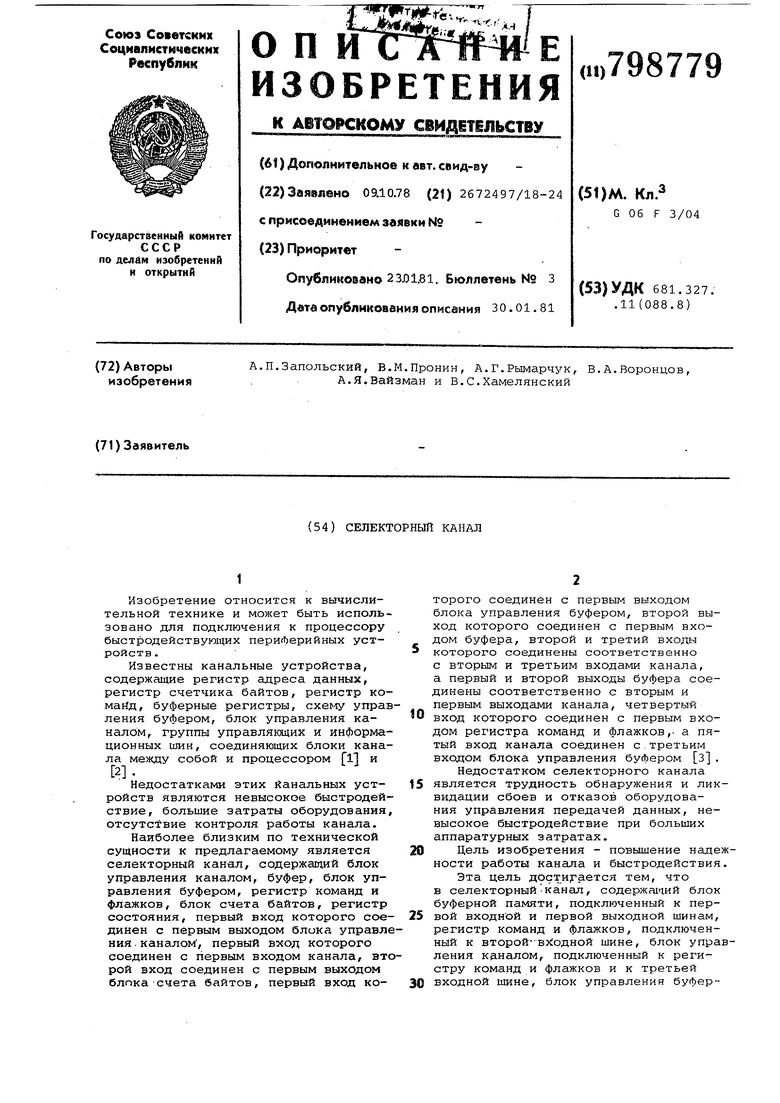

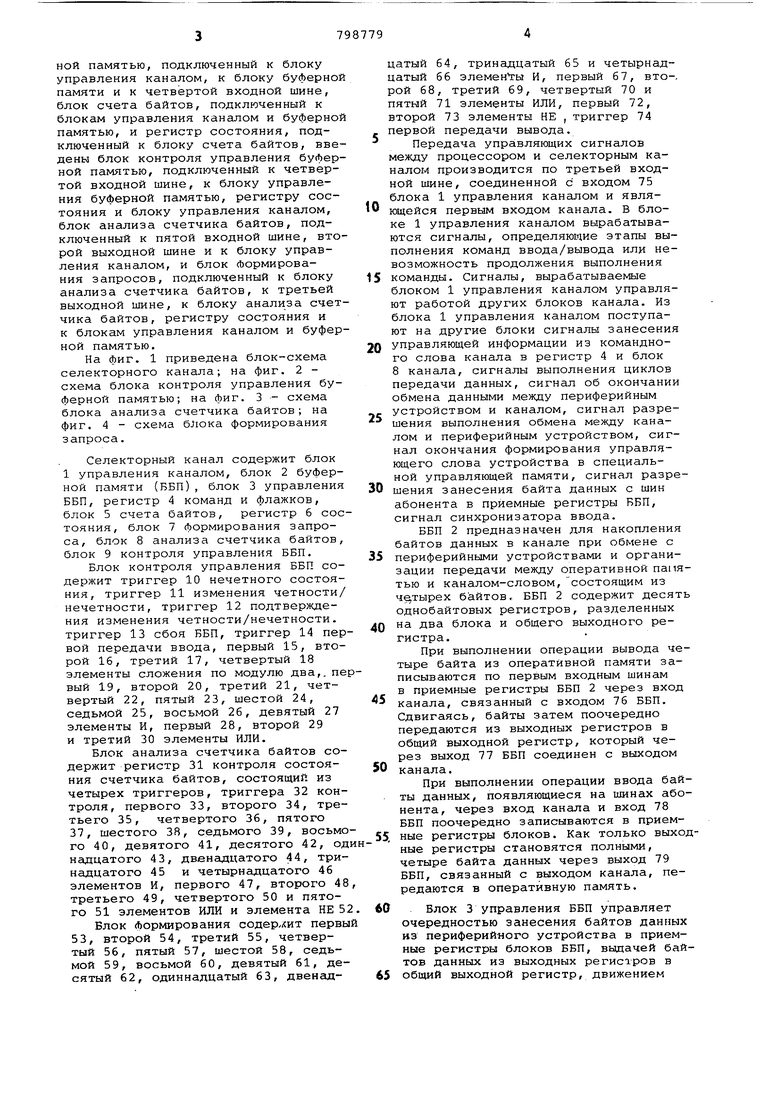

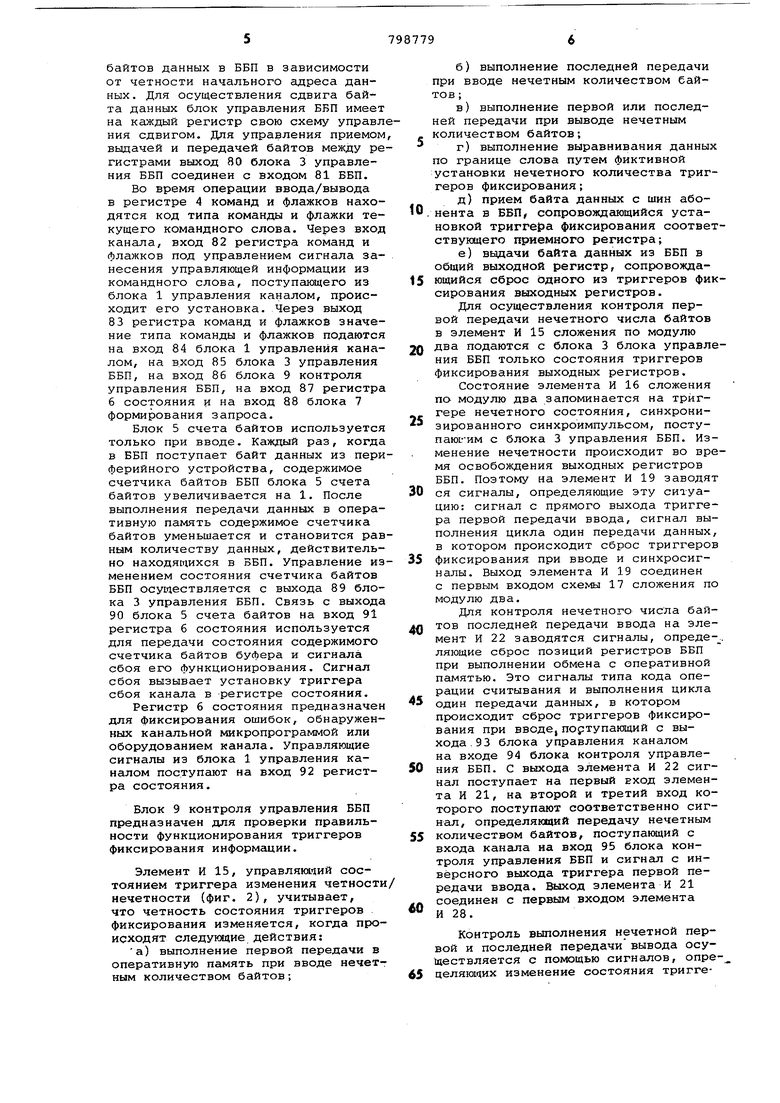

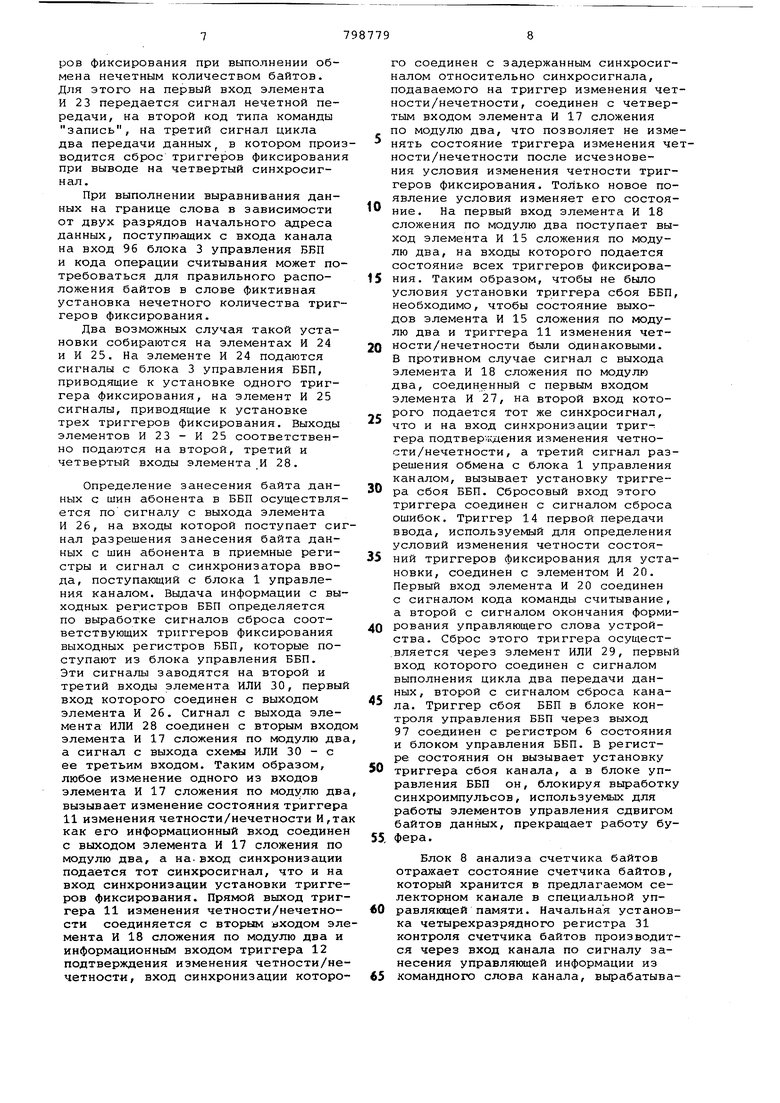

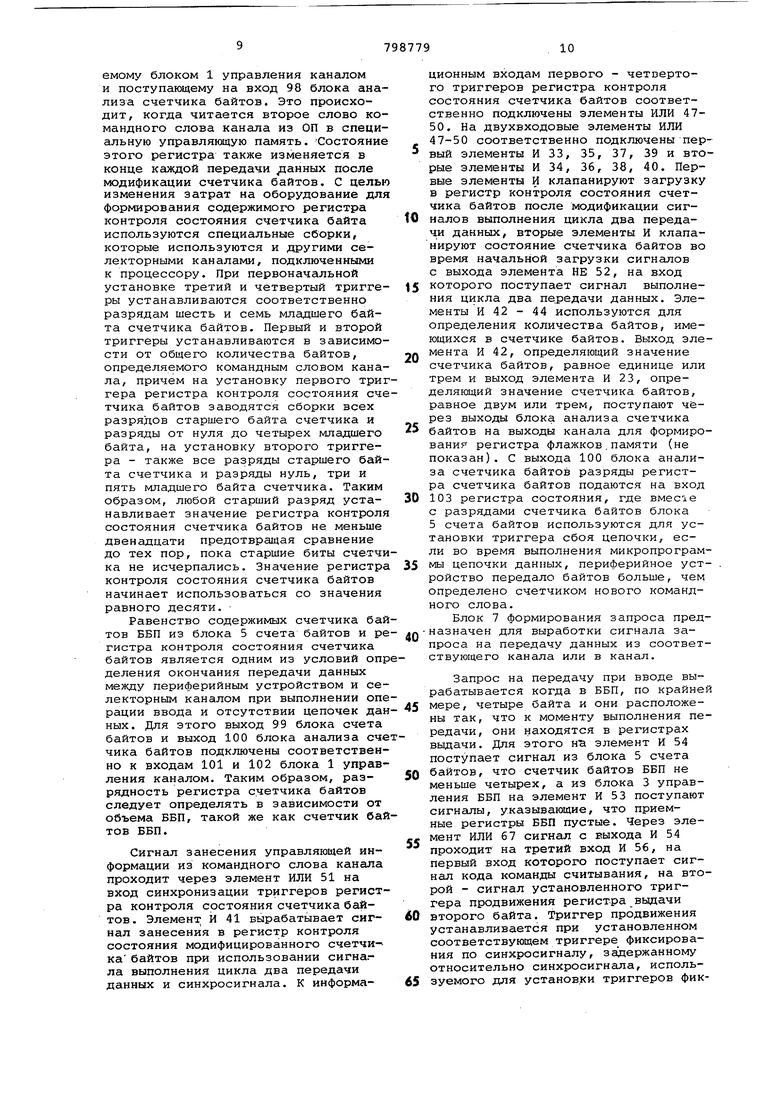

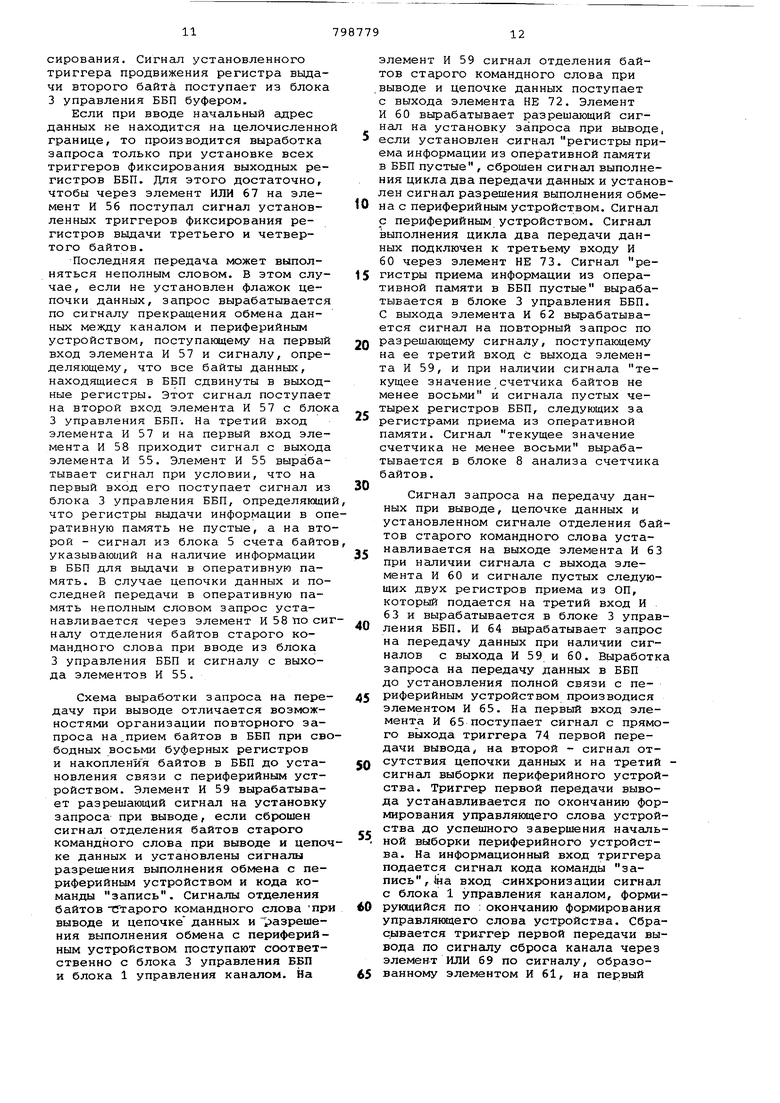

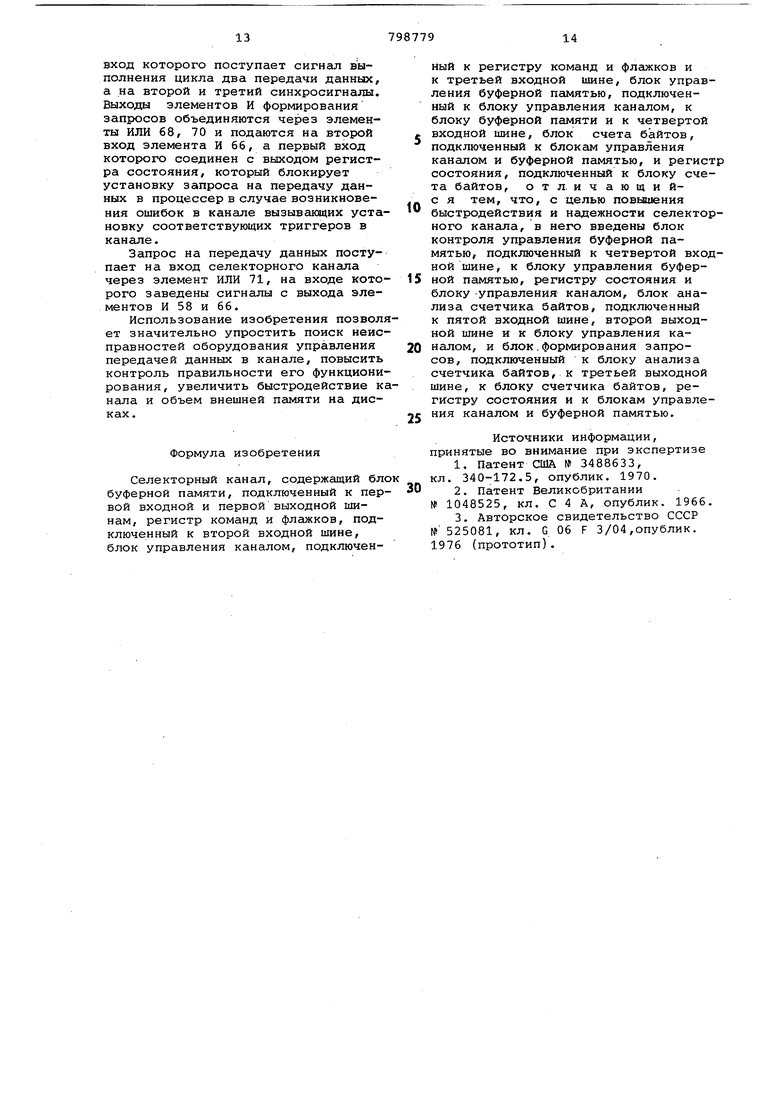

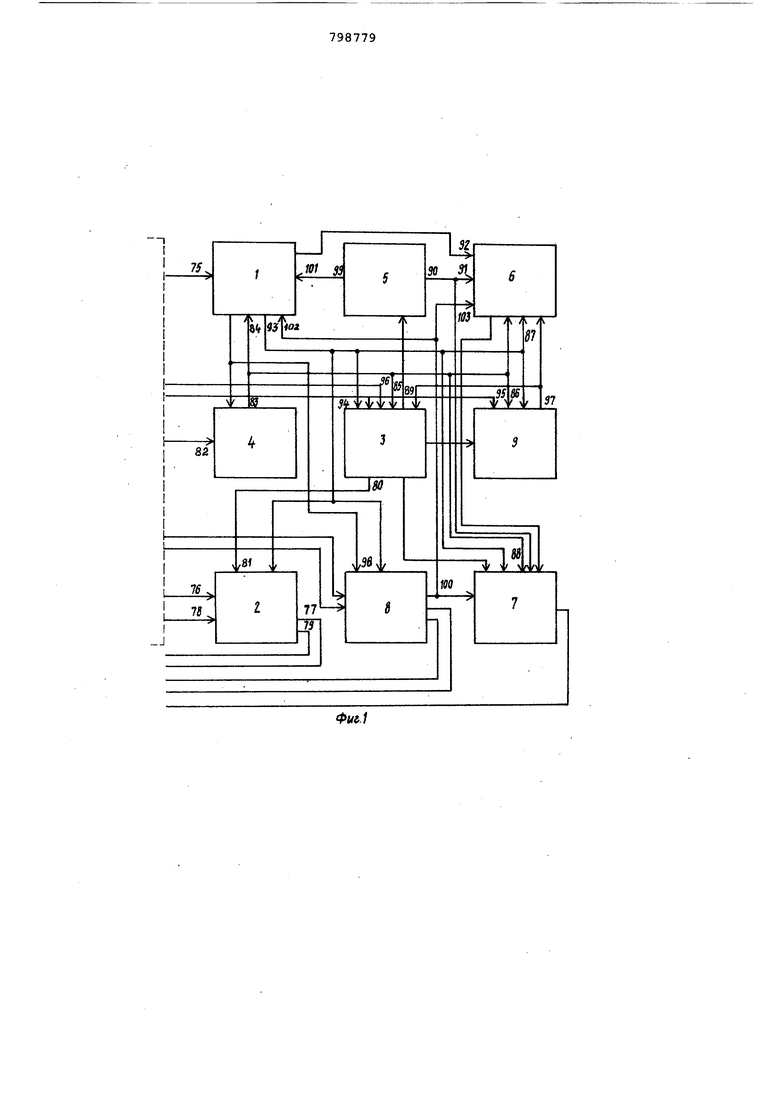

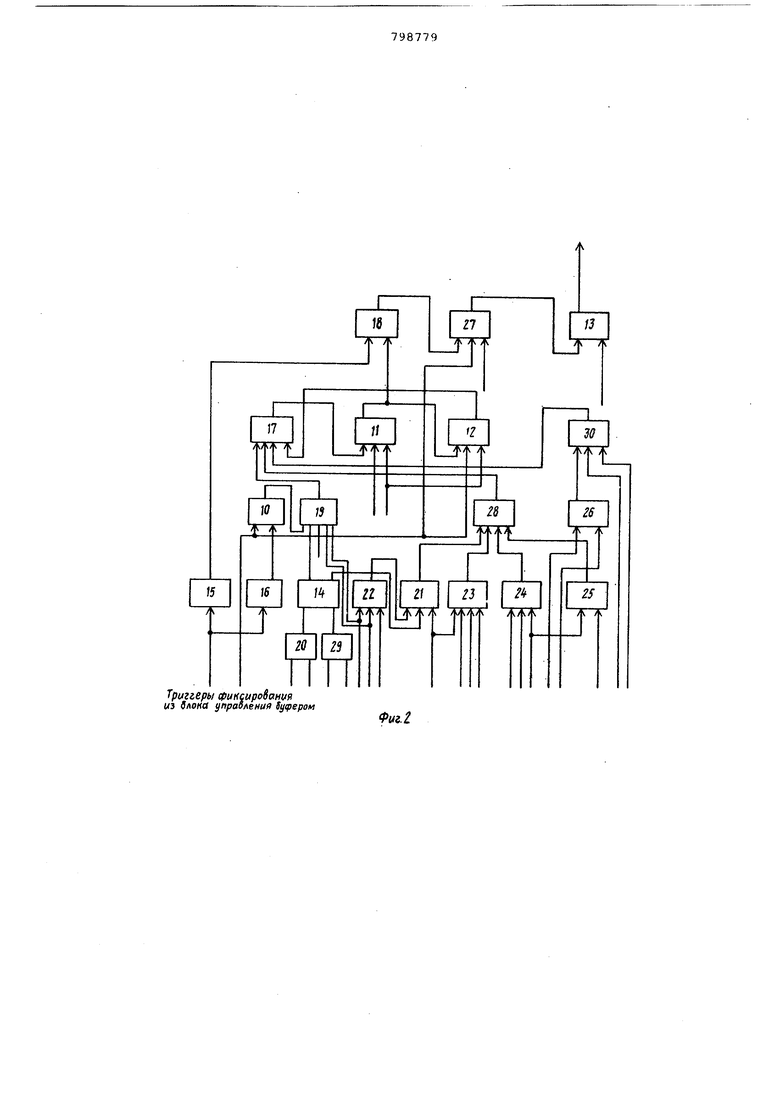

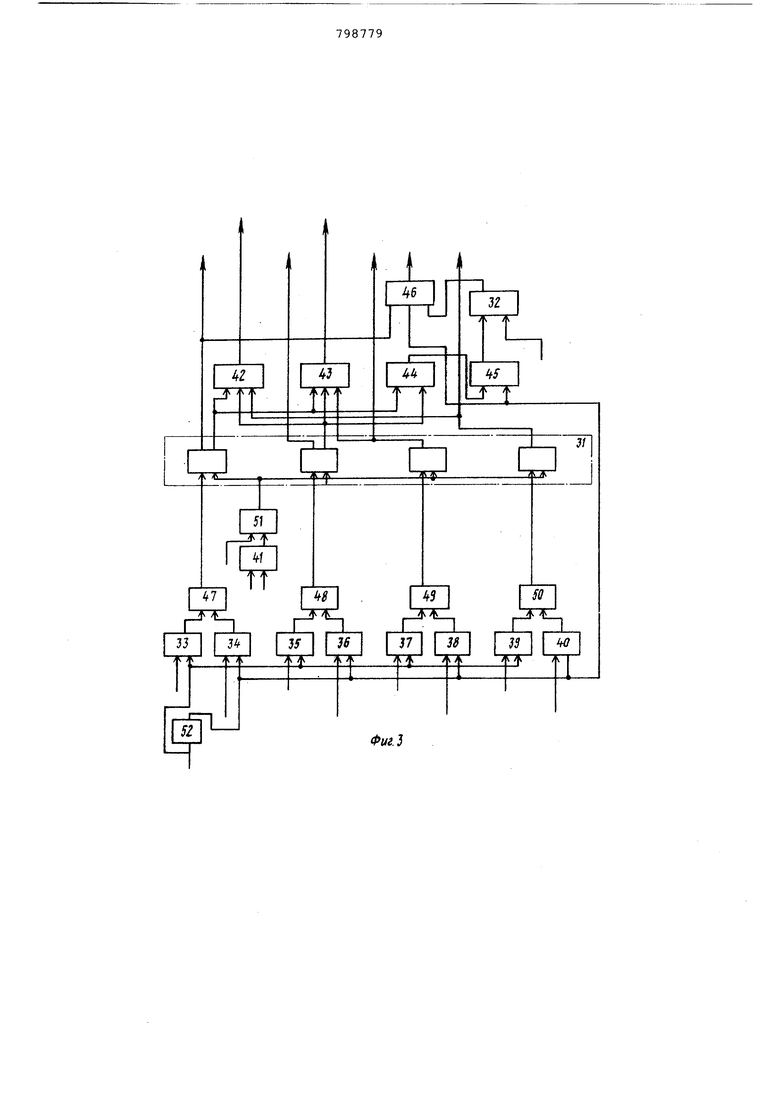

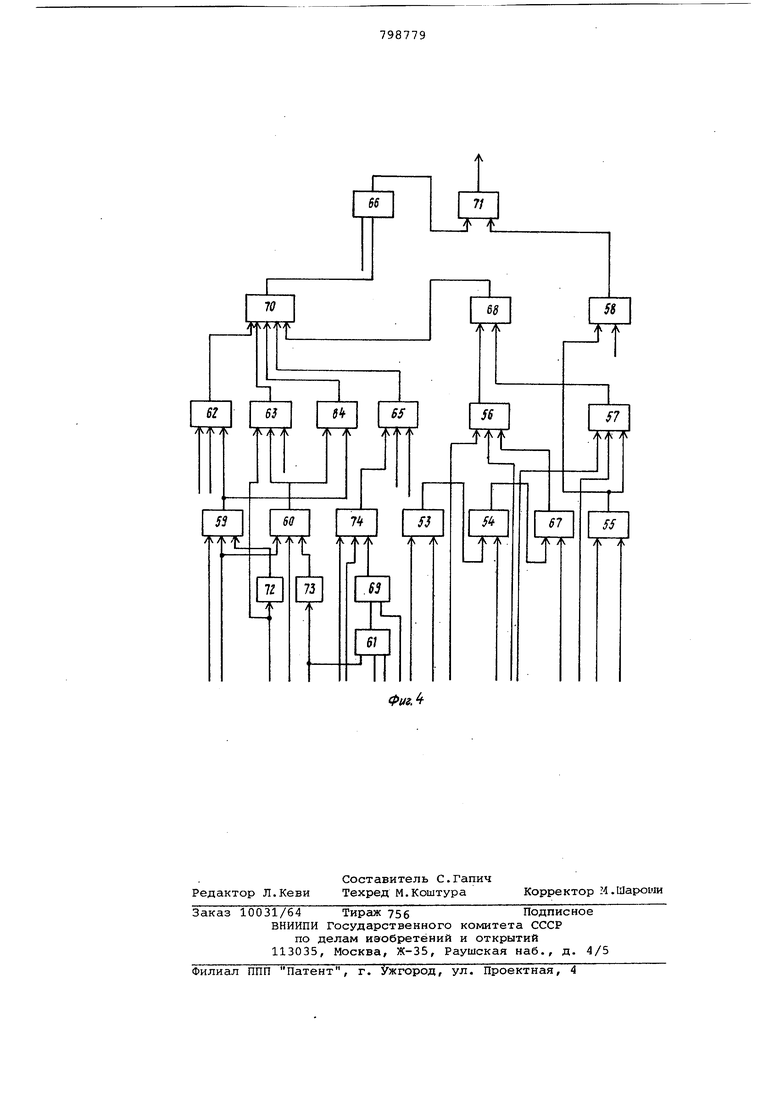

Изобретение относится к вычислительной технике и может быть использовано для подключения к процессору быстродействующих периферийных устройств . Известны канальные устройства, содержащие регистр адреса данных, регистр счетчика байтов, регистр комайд, буферные регистры, управ ления буфером, блок управления каналом, группы управляквдих и информационных шин, соединяющих блоки канала между собой и процессором 11 и 2. Недостатками этих Канальных устройств являются невысокое быстродей ствие, большие затраты оборудования отсутствие контроля работы канала. Наиболее близким по технической сущности к предлагаемому является селекторный канал, содержащий блок управления каналом, буфер, блок управления буфером, регистр команд и флажков, блок счета байтов, регистр состояния, первый вход которого сое динен с первым выходом блока управл ния . каналом , первый вход которого соединен с первым входом канала, вт рой вход соединен с первым выходом блпка счета байтов, первый вход которого соединен с первым выходом блока управления буфером, второй выход которого соединен с первым входом буфера, второй и третий входы которого соединены соответственно с вторым и третьим входами канала, а первый и второй выходы буфера соединены соответственно с вторым и первым выходами канала, четвертый вход которого соединен с первым входом регистра команд и флажков, а пятый вход канала соединен с.третьим входом блока управления буфером З. Недостатком селекторного канала является трудность обнаружения и ликвидации сбоев и отказов оборудования управления передачей данных, невысокое быстродействие при больших аппаратурных затратах. Цель изобретения - повышение надежности работы канала и быстродействия. Эта цель достигается тем, что в селекторныйканал, содержащий блок буферной памяти, подключенный к первой входной и первой выходной шинам, регистр команд и флажков, подключенный к второй входной шине, блок управления каналом, подключенный к регистру команд и флажков и к третьей входной шине, блок управления буферной памятью, подключенный к блоку управления каналом, к блоку буферно памяти и к четвертой входной шине, блок счета байтов, подключенный к блокам управления каналом и буферно памятью, и регистр состояния, подключенный к блоку счета байтов, вве дены блок контроля управления буфер ной памятью, подключенный к четвертой входной шине, к блоку управления буферной памятью, регистру состояния и блоку управления каналом, блок анализа счетчика байтов, подключенный к пятой входной шине, вто рой выходной шине и к блоку управления каналом, и блок Нормирования запросов, подключенный к блоку анализа счетчика байтов, к третьей выходной шине, к блоку анализа счет чика байтов, регистру состояния и к блокам управления каналом и буфер ной памятью. На фиг. 1 приведена блок-схема селекторного канала; на фиг. 2 схема блока контроля управления буферной памятью; на фиг. 3 - схема блока анализа счетчика байтов; на фиг. 4 - схема 6JioKa формирования запроса. Селекторный канал содержит блок 1 управления каналом, блок 2 буферной памяти (ББП), блок 3 управления ББП, регистр 4 команд и флажков, блок 5 счета байтов, регистр 6 сос тояния, блок 7 формирования запроса, блок 8 анализа счетчика байтов блок 9 контроля управления ББП. Блок контроля управления ББП содержит триггер 10 нечетного состояния, триггер 11 изменения четности нечетности, триггер 12 подтверждения изменения четности/нечетности, триггер 13 сбоя ББП, триггер 14 пер вой передачи ввода, первый 15, второй 16, третий 17, четвертый 18 элементы сложения по модулю два,.пе вый 19, второй 20, третий 21, четвертый 22, пятый 23, шестой 24, седьмой 25, восьмой 26, девятый 27 элементы И, первый 28, второй 29 и третий 30 элементы ИЛИ. Блок анализа счетчика байтов содержит регистр 31 контроля состояния счетчика байтов, состоящий из четырех триггеров, триггера 32 кон троля, первого 33, второго 34, тре тьего 35, четвертого 36, пятого 37, шестого 38, седьмого 39, восьмо го 40, девятого 41, десятого 42, од надцатого 43, двенадцатого 44, тринадцатого 45 и четырнадцатого 46 элементов И, первого 47, второго 4 третьего 49, четвертого 50 и пятого 51 элементов ИЛИ и элемента НЕ 5 Блок формирования содер/хит первы 53, второй 54, третий 55, четвертый 56, пятый 57, шестой 58, седьмой 59, восьмой 60, девятый 61, де сятый 62, одиннадцатый 63, двенадцатый 64, тринадцатый 65 и четырнадцатый 66 элементы И, первый 67, вто-, рой 68, третий 69, четвертый 70 и пятый 71 элементы ИЛИ, первый 72, второй 73 элементы НЕ , триггер 74 первой передачи вывода. Передача управляющих сигналов между процессором и селекторным каналом производится по третьей входной шине, соединенной с входом 75 блока 1 управления каналом и являгацейся первым входом канала. В блоке 1 управления каналом вырабатываются сигналы, определяющие этапы выполнения команд ввода/вывода или невозможность продолжения выполнения команды. Сигналы, вырабатываемые блоком 1 управления каналом управляют работой других блоков канала. Из блока 1 управления каналом поступают на другие блоки сигналы занесения управляющей информации из командного слова канала в регистр 4 и блок 8 канала, сигналы выполнения циклов передачи данных, сигнал об окончании обмена данными между периферийным устройством и каналом, сигнал разрешения выполнения обмена между каналом и периферийным устройством, сигнал окончания формирования управляющего слова устройства в специальной управляющей памяти, сигнал разрешения занесения байта данных с шин абонента в приемные регистры ББП, сигнал синхронизатора ввода. ББП 2 предназначен для накопления байтов данных в канале при обмене с периферийными устройствами и организации передачи между оперативной памятью и каналом-словом, состоящим из четырех байтов, ББП 2 содержит десять однобайтовых регистров, разделенных на два блока и общего выходного регистра. При выполнении операции вывода четыре байта из оперативной памяти записываются по первым входным шинам в приемные регистры ББП 2 через вход канала, связанный с входом 76 ББП. Сдвигаясь, байты затем поочередно передаются из выходных регистров в общий выходной регистр, который через выход 77 ББП соединен с выходом канала. При выполнении операции ввода байты данных, появляющиеся на шинах абонента, через вход канала и вход 78 ВБП поочерёдно записываются в приемные регистры блоков. Как только выходные регистры становятся полными, четыре байта данных через выход 79 БВП, связанный с выходом канала, передаются в оперативную память. Блок 3 управления БВП управляет очередностью занесения байтов данных из периферийного устройства в приемные регистры блоков ВБП, выдачей байтов данных из выходных регистров в общий выходной регистр, движением

байтов данных в ББП в зависимости от четности начального адреса данных. Для осуществления сдвига байта данных блок управления ББП имеет на каждый регистр свою схему управлния сдвигом. Для управления приемом выдачей и передачей байтов между регистрами выход 80 блока 3 управления ББП соединен с входом 81 ББП.

Во время операции ввода/вывода в регистре 4 команд и флажков находятся код типа команды и флажки текущего командного слова. Через вход канала, вход 82 регистра команд и флажков под управлением сигнала занесения управляющей информации из командного слова, поступаквдего из блока 1 управления каналом, происходит его установка. Через выход 83 регистра команд и флажков значение типа команды и флажков подаются на вход 84 блока 1 управления каналом, на вход 85 блока 3 управления ББП, на вход 86 блока 9 контроля управления ББП, на вход 87 регистра 6 состояния и на вход 88 блока 7 формирования запроса.

Блок 5 счета байтов используется только при вводе. Каждый раз, когда в ББП поступает байт данных из периферийного устройства, содержимое счетчика байтов ББП блока 5 счета байтов увеличивается на 1. После выполнения передачи данных в оперативную память содержимое счетчика байтов уменьшается и становится равным количеству данных, действительно находяЕчихся в ББП. Управление изменением состояния счетчика байтов ББП осуществляется с выхода 89 блока 3 управления ББП. Связь с выхода 90 блока 5 счета байтов на вход 91 регистра 6 состояния используется для передачи состояния содержимого счетчика байтов буфера и сигнала сбоя его функционирования. Сигнал сбоя вызывает установку триггера сбоя канала в регистре состояния.

Регистр 6 состояния предназначен для фиксирования ошибок, обнаруженных канальной микропрограммой или оборудованием канала. Управляющие сигналы из блока 1 управления каналом поступают на вход 92 регистра состояния.

Блок 9 контроля управления ББП предназначен для проверки правильности функционирования триггеров фиксирования информации.

Элемент И 15, управлякадий состоянием триггера изменения четности нечетности (фиг. 2), учитывает, что четность состояния триггеров фиксирования изменяется, когда происходят следунядие действия:

а) выполнение первой передачи в оперативную память при вводе нечетным количеством байтов;

б)выполнение последней передачи при вводе нечетным количеством байтов ;

в)выполнение первой или последней передачи при выводе нечетным количеством байтов;

г)выполнение выравнивания данных по границе слова путем фиктивной установки нечетного количества триггеров фиксирования;

д)прием байта данных с шин або0 . нента в ББП сопровождающийся установкой тригге1 а фиксирования соответствующего приемного регистра;

е)выдачи байта данных из ББП в общий выходной регистр, сопровожда5ющийся сброс одного из триггеров фиксирования выходных регистров.

Для осуществления контроля первой передачи нечетного числа байтов в элемент И 15 сложения по модулю два подаются с блока 3 блока управле0ния ББП только состояния триггеров фиксирования выходных регистров.

Состояние элемента И 16 сложения по модулю два запоминается на триггере нечетного состояния, синхрони5зированного синхроимпульсом, поступаюгим с блока 3 управления ББП. Изменение нечетности происходит во время освобождения выходных регистров ББП. Поэтому на элемент И 19 заводят

0 ся сигналы, определяющие эту ситуацию: сигнал с прямого выхода триггера первой передачи ввода, сигнал выполнения цикла один передачи данных, в котором происходит сброс триггеров

5 фиксирования при вводе и синхросигналы. Быход элемента И 19 соединен с первым входом схемы 17 сложения по модулю два.

Для контроля нечетного числа байтов последней передачи ввода на эле0мент И 22 заводятся сигналы, опреде-.. ляющие сброс позиций регистров БВП при выполнении обмена с оперативной памятью. Это сигналы типа кода операции считывания и выполнения цикла

5 один передачи данных, в котором происходит сброс триггеров фиксирования при вводе,поступающий с выхода. 93 блока управления каналом на входе 94 блока контроля управле0ния ББП. С выхода элемента И 22 сигнал поступает на первый вход элемента И 21, на второй и третий вход которого поступают соответственно сигнал, определяющий передачу нечетным количеством байтов, поступающий с

5 входа канала на вход 95 блока контроля управления ББП и сигнал с инверсного выхода триггера первой передачи ввода. Выход элемента И 21 соединен с первым входом элемента

О И 28.

Контроль выполнения нечетной первой и последней передачи вывода осуществляется с помощью сигналов, опре65 целяющих изменение состояния триггеров фиксирования при выполнении обмена нечетным количеством байтов. Для этого на первый вход элемента И 23 передается сигнал нечетной передачи, на второй код типа команды запись, на третий сигнал цикла два передачи данных в котором прои водится сброс триггеров фиксировани при выводе на четвертый синхросигнал. При выполнении выравнивания данных на границе слова в зависимости от двух разрядов начального адреса данных, поступюащих с входа канала на вход 96 блока 3 управления ББП и кода операции считывания может по требоваться для правильного расположения байтов в слове фиктивная установка нечетного количества триг геров фиксирования. Два возможных случая такой установки собираются на элементах И 24 и И 25. На элементе И 24 подаются сигналы с блока 3 управления ББП, приводящие к установке одного триггера фиксирования, на элемент И 25 сигналы, приводящие к установке трех триггеров фиксирования. Выходы элементов И 23 - И 25 соответственно подаются на второй, третий и четвертый входы элемента И 28. Определение занесения байта данных с шин абонента в ББП осуществля ется по сигналу с выхода элемента И 26, на входы которой поступает си нал разрешения занесения байта данных с шин абонента в приемные регистры и сигнал с синхронизатора ввода, поступающий с блока 1 управления каналом. Выдача информации с вы ходных регистров ББП определяется по выработке сигналов сброса соответствующих триггеров фиксирования выходных регистров ББП, которые поступают из блока управления ББП. Эти сигналы заводятся на второй и третий входы элемента ИЛИ 30, первы вход которого соединен с выходом элемента И 26. Сигнал с выхода элемента ИЛИ 28 соединен с вторым вход элемента И 17 сложения по модулю дв а сигнал с выхода схемы ИЛИ 30 - с ее третьим входом. Таким образом, любое изменение одного из входов элемента И 17 сложения по модулю дв вызывает изменение состояния триггер 11 изменения четности/нечетности И,т как его информационный вход соедине с выходом элемента И 17 сложения по модулю два, а на.вход синхронизации подается тот синхросигнал, что и на вход синхронизации установки тригге ров фиксирования. Прямой выход триг гера 11 изменения четности/нечетности соединяется с вторым входом эл мента И 18 сложения по модулю два и информационным входом триггера 12 подтверждения изменения четности/не четности, вход синхронизации которо го соединен с задержанным синхросигналом относительно синхросигнала, подаваемого на триггер изменения четности/нечетности, соединен с четвертым входом элемента И 17 сложения по модулю два, что позволяет не изменять состояние триггера изменения четности/нечетности после исчезновения условия изменения четности триггеров фиксирования. Только новое появление условия изменяет его состояние. На первый вход элемента И 18 сложения по модулю два поступает выход элемента И 15 сложения по модулю два, на входы которого подается состояния всех триггеров фиксирования. Таким образом, чтобы не было условия установки триггера сбоя ББП, необходимо, чтобы состояние выходов элемента И 15 сложения по модулю два и триггера 11 изменения четности/нечетности были одинаковыми. В противном случае сигнал с выхода элемента И 18 сложения по модулю два, соединенный с первым входом элемента И 27, на второй вход которого подается тот же синхросигнал, что и на вход синхронизации триггера подтвер.кдения изменения четности/нечетности, а третий сигнал разрешения обмена с блока 1 управления каналом, вызывает установку триггера сбоя ББП. Сбросовый вход этого триггера соединен с сигналом сброса ошибок. Триггер 14 первой передачи ввода, используемый для определения условий изменения четности состояний триггеров фиксирования для установки, соединен с элементом И 20. Первый вход элемента И 20 соединен с сигналом кода команды считывание, а второй с сигналом окончания формирования управляющего слова устройства. Сброс этого триггера осуществляется через элемент ИЛИ 29, первый вход которого соединен с сигналом выполнения цикла два передачи данных, второй с сигналом сброса канала. Триггер сбоя ББП в блоке контроля управления ББП через выход 97 соединен с регистром 6 состояния и блоком управления ББП. В регистре состояния он вызывает установку триггера сбоя канала, а в блоке управления ББП он, блокируя выработку синхроимпульсов, используемых для работы элементов управления сдвигом байтов данных, прекращает работу буфера. Блок 8 анализа счетчика байтов отражает состояние счетчика байтов, который хранится в предлагаемом селекторном канале в специальной управляющей памяти. Начальная установка четырехразрядного регистра 31 контроля счетчика байтов производится через вход канала по сигналу занесения управляющей информации из командного слова канала, вырабатываемому блоком 1 управления каналом и поступающему на вход 98 блока анализа счетчика байтов. Это происходит, когда читается второе слово ко мандного слова канала из ОП в специальную управлякщую память. -Состояние этого регистра также изменяется в конце каждой передачи /1анных после модификации счетчика байтов. С целью изменения затрат на оборудование дл формирования содержимого регистра контроля состояния счетчика байта используются специальные сборки, которые используются и другими селекторными каналами, подключенными к процессору. При первоначальной установке третий и четвертый тригге ры устанавливаются соответственно разрядам шесть и семь младшего байта счетчика байтов. Первый и второй триггеры устанавливаются в зависимо сти от общего количества байтов, определяемого командным словом канала, причем на установку первого три гера регистра контроля состояния сче тчика байтов заводятся сборки всех разрядов старшего байта счетчика и разряды от нуля до четырех младшего байта, на установку второго триггера - также все разряды старшего байта счетчика и разряды нуль, три и пять младшего байта счетчика. Таким образом, любой старший разряд устанавливает значение регистра контроля состояния счетчика байтов не меньше двенадцати предотвращая сравнение до тех пор, пока старшие биты счетчи ка не исчерпались. Значение регистра контроля состояния счетчика байтов начинает использоваться со значения равного десяти. Равенство содержимых счетчика бай тов ББП из блока 5 счета байтов и ре гистра контроля состояния счетчика байтов является одним из условий опр деления окончания передачи данных между периферийным устройством и селекторным каналом при выполнении опе рации ввода и отсутствии цепочек дан ных. Для этого выход 99 блока счета байтов и выход 100 блока анализа сче чика байтов подключены соответственно к входам 101 и 102 блока 1 управления каналом. Таким образом, разрядность регистра счетчика байтов следует определять в зависимости от объема ББП, такой же как счетчик бай тов ББП. Сигнал занесения управляющей информации из командного слова канала проходит через элемент ИЛИ 51 на вход синхронизации триггеров регистра контроля состояния счетчика байтов. Элемент И 41 вырабатывает сигнал занесения в регистр контроля состояния модифицированного счетчи- ка байтов при использовании сигна.ла выполнения цикла два передачи данных и синхросигнала. К информационным входам первого - четвертого триггеров регистра контроля состояния счетчика байтов соответственно подключены элементы ИЛИ 4750. На двухвходовые элементы ИЛИ 47-50 соответственно подключены первый элементы И 33, 35, 37, 39 и вторые элементы И 34, 36, 38, 40. Первые элементы И клапанируют загрузку в регистр контроля состояния счетчика байтов после модификации сигналов выполнения цикла два передачи данных, вторые элементы И клапанируют состояние счетчика байтов во время начальной загрузки сигналов с выхода элемента НЕ 52, на вход которого поступает сигнал выполнения цикла два передачи данных. Элементы И 42 - 44 используются для определения количества байтов, имеющихся в счетчике байтов. Выход элемента И 42, определяющий значение счетчика байтов, равное единице или трем и выход элемента И 23, определяющий значение счетчика байтов, равное двум или трем, поступают через выходы блока анализа счетчика байтов на выходы канала для формирования регистра флажков.памяти (не показан). С выхода 100 блока анализа счетчика байтов разряды регистра счетчика байтов подаются на вход 103 регистра состояния, где вмесге с разрядами счетчика байтов блока 5 счета байтов используются для установки триггера сбоя цепочки, если во время выполнения микропрограммы цепочки данных, периферийное устройство передало байтов больше, чем определено счетчиком нового командного слова. Блок 7 формирования запроса предназначен для выработки сигнала запроса на передачу данных из соответствующего канала или в канал. Запрос на передачу при вводе вырабатывается когда в ББП, по крайней мере, четыре байта и они расположены так, что к моменту выполнения передачи, они находятся в регистрах выдачи. Для этого HS элемент И 54 поступает сигнал из блока 5 счета байтов, что счетчик байтов ББП не меньше четырех, а из бло-ка 3 управления ББП на элемент И 53 поступают сигнсшы, указывающие, что приемные регистры ББП пустые. Через элемент ИЛИ 67 сигнал с выхода И 54 проходит на третий вход И 56, на первый вход которого поступает сигнал кода команды считывания, на второй - сигнал установленного триггера продвижения регистра выдачи второго байта. Триггер продвижения устанавливается при установленном соответствующем триггере фиксирования по синхросигналу, задержанному относительно синхросигнала, используемого для установки триггеров фиксирования. Сигнал установленного триггера продвижения регистра выдачи второго байта поступает из блока 3 управления ББП буфером.

Если при вводе начальный адрес данных не находится на целочисленно границе, то производится выработка запроса только при установке всех триггеров фиксирования выходных регистров ББП. Для этого достаточно, чтобы через элемент ИЛИ 67 на элемент И 56 поступал сигнал установленных триггеров фиксирювания регистров выдачи третьего и четвертого байтов.

Последняя передача может выполняться неполным словом. В этом случае, если не установлен флажок цепочки данных, запрос вырабатывается по сигналу прекращения обмена данных между каналом и периферийным устройством, поступающему на первый вход элемента И 57 и сигналу, определяющему, что все байты данных, находящиеся в ББП сдвинуты в выходные регистры. Этот сигнал поступает на второй вход элемента И 57 с блок 3 управления ББП-. На третий вход элемента И 57 и на первый вход элемента И 58 приходит сигнал с выхода элемента И 55. Элемент И 55 вырабатывает сигнал при условии, что на первый вход его поступает сигнал из блока 3 управления ББП, определяющи что регистры выдачи информации в опративную память не пустые, а на второй - сигнал из блока 5 счета байто указывающий на наличие информации в ББП для выдачи в оперативную память. В случае цепочки данных и последней передачи в оперативную память неполным словом запрос устанавливается через элемент И 58 tio синалу отделения байтов старого командного слова при вводе из блока 3 управления ББП и сигналу с выхода элементов И 55.

Схема выработки запроса на передачу при выводе отличается воз1«южностями организации повторного запроса на.прием байтов в ББП при свободных восьми буферных регистров и накопленная байтов в ББП до установления связи с периферийным устройством. Элемент И 59 вырабатывает разрешающий сигнал на установку запроса при выводе, если сброшен сигнал отделения байтов старого командйого слова при выводе и цепочке данных и установлены сигналы разрешения выполнения обмена с периферийным устройством и кода команды запись. Сигналы отделения байтов Старого командного слова пр выводе и цепочке данных и разрешения выполнения обмена с периферийным устройством поступают соответственно с блока 3 управления ББП и блока 1 управления кангшом. На

элемент И 59 сигнал отделения байтов старого командного слова при .выводе и цепочке данных поступает с выхода элемента НЕ 72. Элемент И 60 вырабатывает разрешающий сигнал на установку запроса при выводе, если установлен сигнал регистры приема информации из оперативной памяти в ББП пустые , сброшен сигнал выполнения цикла два передачи данных и установлен сигнал разрешения выполнения обмена с периферийным устройством. Сигнал с периферийным устройством. Сигнал выполнения цикла два передачи данных подключен к третьему входу И 60 через элемент НЕ 73. Сигнал регистры приема информации из оперативной памяти в ББП пустые вырабатывается в блоке 3 управления ББП. С выхода элемента И 62 вырабатывается сигнал на повторный запрос по разрешающему сигналу, поступающему на ее третий вход с выхода элемента И 59, и при наличии сигнала текущее значение счетчика байтов не менее восьми и сигнала пустых четырех регистров ББП, следующих за регистрами приема из оперативной памяти. Сигнал текущее значение счетчика не менее восьми вырабатывается в блоке 8 анализа счетчика байтов.

Сигнал запроса на передачу данных при выводе, цепочке данных и установленном сигнале отделения байтов старого командного слова устанавливается на выходе элемента И 63 при наличии сигнала с выхода элемента И 60 и сигнале пустых следующих двух регистров приема из ОП, который подается на третий вход И 63 и вырабатывается в блоке 3 управления ББП. И 64 вырабатывает запрос на передачу данных при наличии сигналов с выхода И 59 и 60. Выработка запроса на передачу данных в ББП до установления полной связи с периферийным устройством производися элементом И 65. На первый вход элемента И 65 поступает сигнал с прямого выхода триггера 74 первой передачи вывода, на второй - сигнал отсутствия цепочки данных и на третий сигнал выборки периферийного устройства. Триггер первой передачи вывода устанавливается по окончанию формирования управляющего слова устройства до успешного завершения начальной выборки периферийного устройства. На информационный вход триггера подается сигнал кода команды запись, taa вход синхронизации сигнал с блока 1 управления каналом, формирующийся по : окончанию формирования управляющего слова устройства. Сбрасывается триггер первой передачи вывода по сигналу сброса канала через элемент ИЛИ 69 по сигналу, образованному элег ентом И 61, на первый вход которого поступает сигнал выполнения цикла два передачи данных, а на второй и третий синхросигналы. Выходы элементов И формирования запросов объединяются через элементы ИЛИ 68, 70 и подаются на второй вход элемента И 66, а первый вход которого соединен с выходом регистра состояния, который блокирует установку запроса на передачу данных в процессер в случае возникновения ошибок в канале вызывакадих уста новку соответствующих триггеров в канале. Запрос на передачу данных поступает на вход селекторного канаша через элемент ИЛИ 71, на входе кото рого заведены сигналы с выхода элементов И 58 и 66. Использование изобретения позвол ет значительно упростить поиск неис правностей оборудования управления передачей данных в канале, повысить контроль правильности его функциони рования , увеличить быстродействие к нала и объем внешней памяти на дисках. Формула изобретения Селекторный канал, содержащий бл буферной памяти, подключенный к пер вой входной и первой выходной шинам, регистр команд и флажков, подключенный к второй входной шине, блок управления каналом, подключенный к регистру команд и флажков и к третьей входной шине, блок управления буферной памятью, подключенный к блоку управления каналом, к блоку буферной памяти и к четвертой входной шине, блок счета байтов, подключенный к блокам управления каналом и буферной памятью, и регистр состояния, подключенный к блоку счета байтов, отл. ичающийс я тем, что, с целью повышения быстродействия и надежности селекторного канала, в него введены блок контроля управления буферной памятью, подключенный к четвертой входной шине, к блоку управления буферной памятью, регистру состояния и блоку -управления каналом, блок анализа счетчика байтов, подключенный к пятой входной шине, второй выходной шине и к блоку управления каналом, и блок,формирования запросов, подключенный к блоку анализа счетчика байтов, к третьей выходной шине, к блоку счетчика байтов, регистру состояния и к блокам управления каналом и буферной памятью. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3488633, кл. 340-172.5, опублик. 1970. 2.Патент Великобритании № 1048525, кл. С 4 А, опублик. 1966. 3.Авторское свидетельство СССР № 525081, кл. G 06 F 3/04,опублик. 1976 (прототип).

Триггеры фиксирования из SAOHO упраоления Syipepoin

Фиг. 2

A /k

у V k У / k

T:

1

j.

Авторы

Даты

1981-01-23—Публикация

1978-10-09—Подача