Изобретение относится к области вычислительной техники и может найти применение при построении коммутационных средств мультипроцессорных вычислительных и управляющих систем, абонентских систем связи с децентрализованным управлением и информационно-измерительных систем.

Известен модуль матричного коммутатора, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, два элемента сравнения, два дешифратора и элемент И (авт.св. СССР N 1575167, G 06 F 7/00, 15/16; опубл. 30.06.90, БИ N 24).

Недостатком данного модуля являются ограниченные коммутационные возможности, что обусловлено наличием только двух входных и двух выходных каналов для подключения к соседним модулям в составе коммутатора.

Наиболее близким к предлагаемому модулю по технической сущности является устройство для формирования маршрута сообщения в однородной вычислительной системе, содержащее девять буферных запоминающих блоков, блок памяти констант, блок считывания информации, регистр, демультиплексор, два блока сравнения, блок элементов И, блок элементов ИЛИ, элемент ИЛИ, блок синхронизации и элемент И (авт.св. СССР N 1462344, G 06 F 15/16; опубл. 28.02.89, БИ N 8).

Недостатком указанного устройства является узкая область применения ввиду значительного числа внешних входов и выходов, требуемых для организации его взаимодействия с другими аналогичными устройствами в составе соответствующей коммуникационной сети.

Технической задачей, на решение которой направлено заявляемое изобретение, является расширение области применения устройства на основе минимизации числа внешних входов и выходов, требуемых для организации его взаимодействия с другими аналогичными устройствами (модулями) коммуникационной сети.

Техническая задача решается тем, что в модуль коммуникационной сети, содержащий с первого по девятый буферные запоминающие блоки, блок памяти констант, блок считывания информации, регистр, демультиплексор, первый и второй блоки сравнения, блок синхронизации, блок элементов И, блок элементов ИЛИ, первый элемент И, первый элемент ИЛИ, причем информационный и первый управляющий входы первого буферного запоминающего блока являются информационным входом и входом синхронизации модуля соответственно, первые управляющие выходы буферных запоминающих блоков с первого по девятый соединены с входом первого элемента ИЛИ, а также с информационными входами блока считывания информации с первого по девятый соответственно, выходы с первого по девятый которого подключены к вторым управляющим входам буферных запоминающих блоков с первого по девятый соответственно, информационные выходы которых подключены к входам блока элементов ИЛИ с первого по девятый соответственно, выход которого соединен с информационным входом регистра, первая и вторая группы выходов которого соединены с первыми входами первого и второго блоков сравнения соответственно, выходы равенства которых подключены к первому и второму входам первого элемента И соответственно, выход которого подключен к управляющему входу блока элементов И, информационный вход которого соединен с третьей группой выходов регистра, а выход является информационным выходом модуля, выход блока памяти констант соединен с вторыми входами первого и второго блоков сравнения, все выходы которых подключены к управляющему входу демультиплексора, информационный вход которого соединен с группами выходов регистра с первой по третью, второй выход блока синхронизации подключен к информационному входу блока элементов И, дополнительно введены дешифратор, триггер, первая и вторая группы блоков тристабильных элементов, группа элементов И, с первого по восьмой элементы И-НЕ, группа элементов НЕ, второй и третий элементы И, второй и третий элементы ИЛИ, элемент НЕ, причем вторые управляющие выходы буферных запоминающих блоков с первого по девятый подключены к входам второго элемента ИЛИ с первого по девятый соответственно, выход которого соединен с входом синхронизации регистра, выход первого элемента ИЛИ соединен с первым входом второго элемента И, выход которого подключен к входу синхронизации блока считывания информации, первый выход блока синхронизации подключен к второму входу второго элемента И, выход которого соединен с входом синхронизации триггера, инверсный выход которого соединен с третьим входом второго элемента И, все выходы первого и второго блоков сравнения подключены к информационному входу дешифратора, выходы с первого по восьмой которого соединены с первыми входами элементов И группы с первого по восьмой соответственно, вторые входы которых соединены с вторым выходом блока синхронизации, выходы демультиплексора с первого по восьмой подключены к информационным входам блоков тристабильных элементов первой группы с первого по восьмой соответственно, выходы которых соединены с информационными входами/выходами модуля с первого по восьмой соответственно, которые также подключены к информационным входам блоков тристабильных элементов второй группы с первого по восьмой соответственно, старшие m разрядов выходов которых (где m - разрядность сообщения) соединены с информационными входами буферных запоминающих блоков со второго по девятый соответственно, первые управляющие входы которых соединены с выходами элементов НЕ группы с первого по восьмой соответственно, второй выход блока синхронизации подключен к первому входу третьего элемента И и к входу элемента НЕ, выход которого соединен с информационными входами блоков тристабильных элементов первой группы с первого по восьмой, младшие ((m+1)-e) разряды выходов блоков тристабильных элементов второй группы с первого по восьмой соединены с входами элементов НЕ группы с первого по восьмой соответственно и с первыми входами элементов И-НЕ с первого по восьмой соответственно, выходы которых подключены к третьим входам элементов И группы с первого по восьмой соответственно, выходы которых подключены к входам третьего элемента ИЛИ с первого по восьмой соответственно, выход которого соединен с входом сброса триггера, информационный вход которого соединен с шиной логической единицы, выход первого элемента И подключен к второму входу третьего элемента И, выход которого соединен с девятым входом третьего элемента ИЛИ, выход которого соединен с входом сброса регистра, управляющие входы модуля с первого по восьмой подключены к вторым входам элементов И-НЕ с первого по восьмой соответственно, выходы которых соединены с управляющими входами блоков тристабильных элементов первой группы с первого по восьмой соответственно, с управляющими входами блоков тристабильных элементов второй группы с первого по восьмой соответственно и с управляющими выходами модуля с первого по восьмой соответственно.

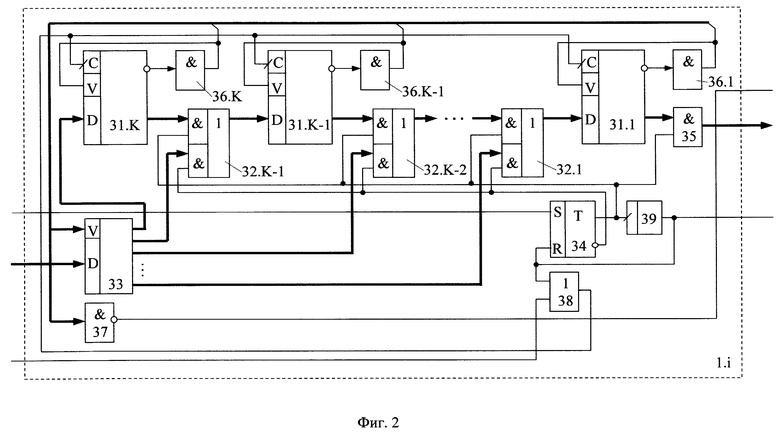

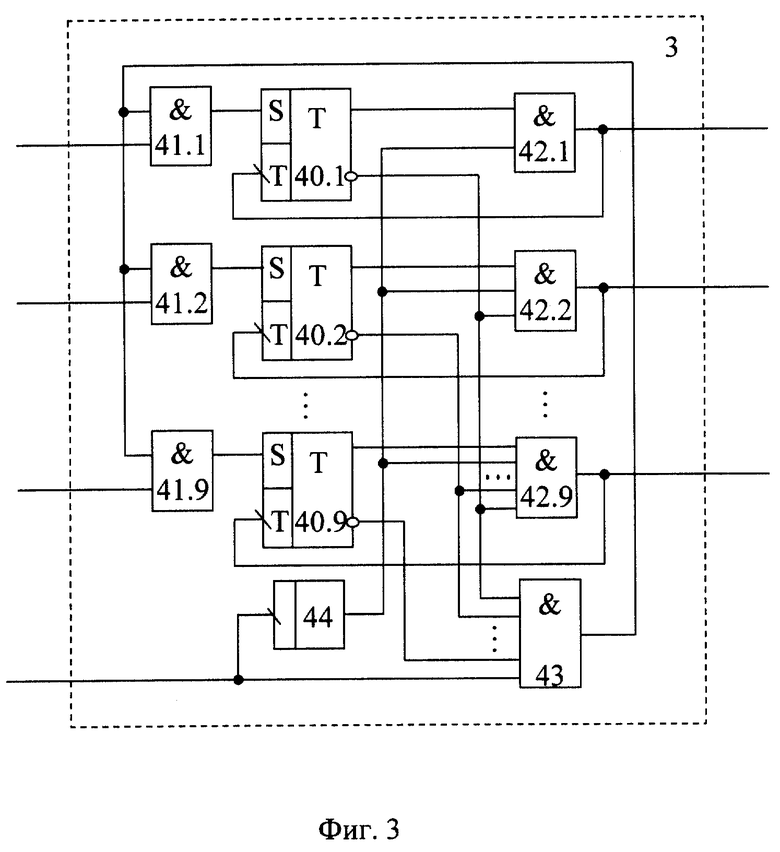

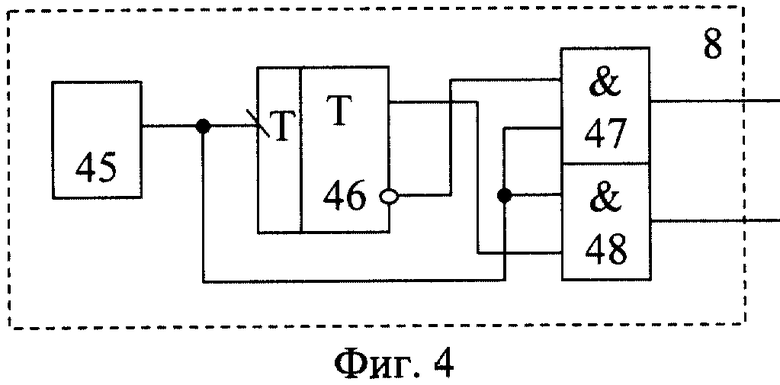

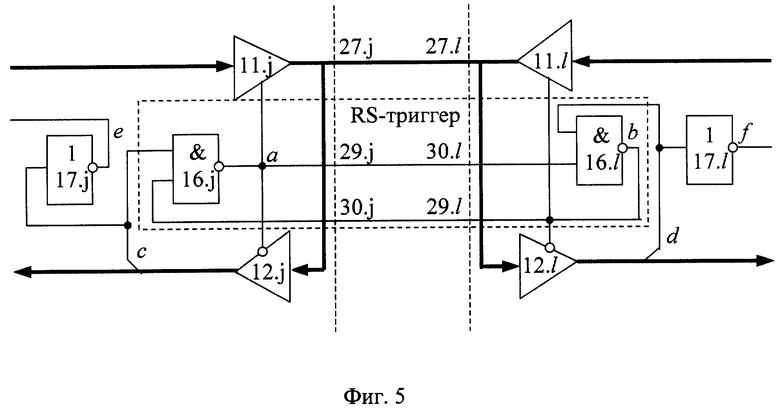

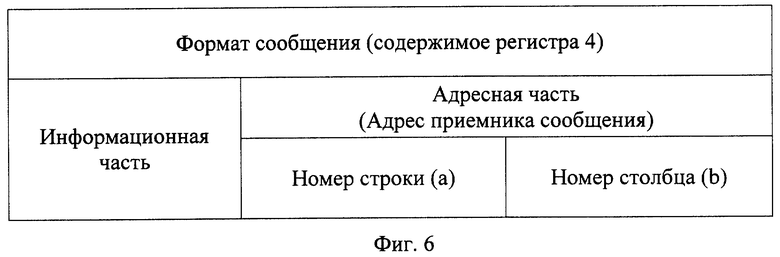

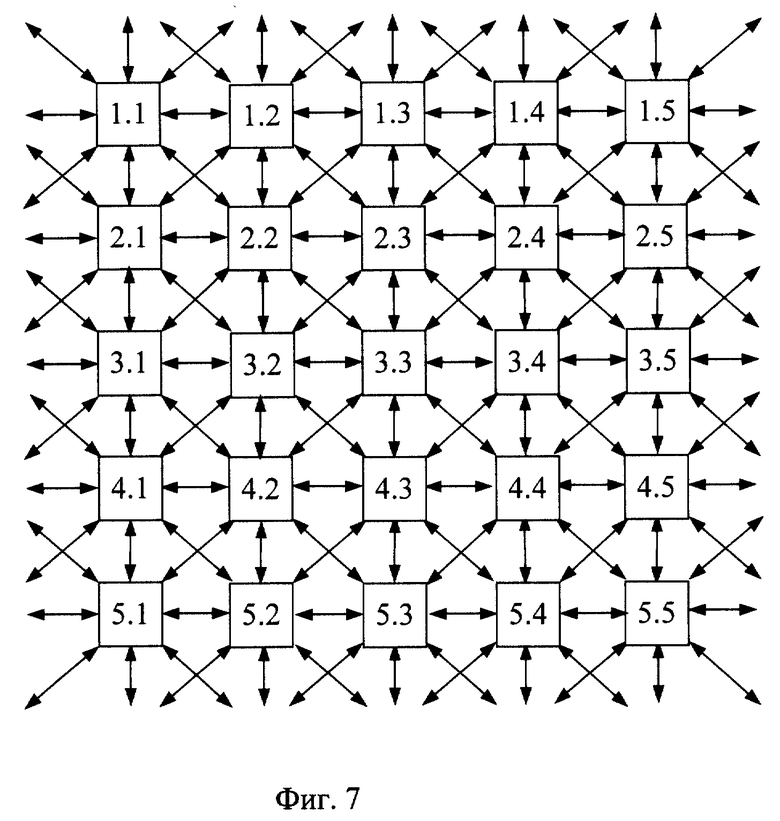

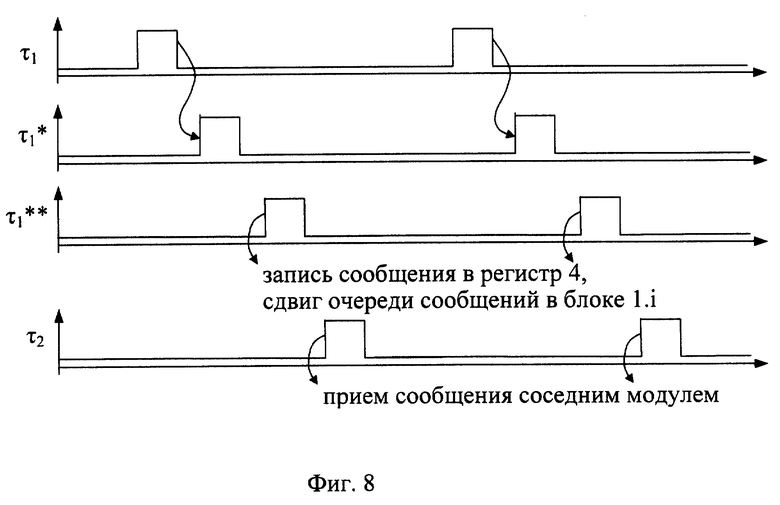

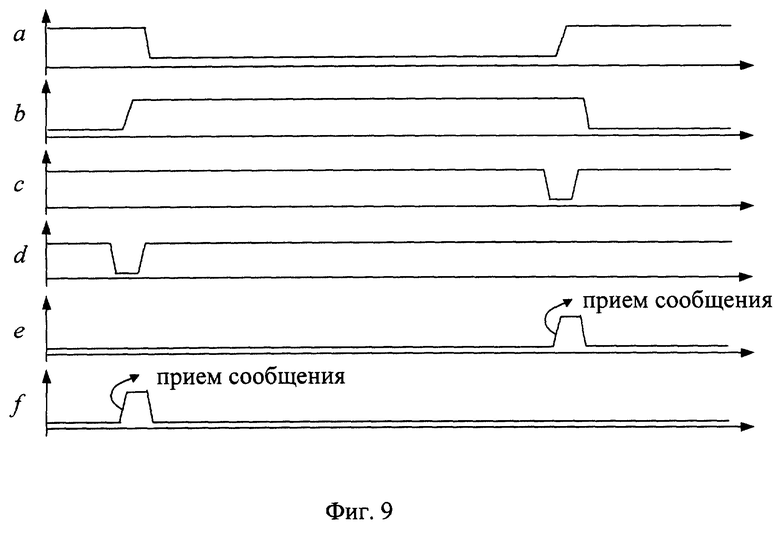

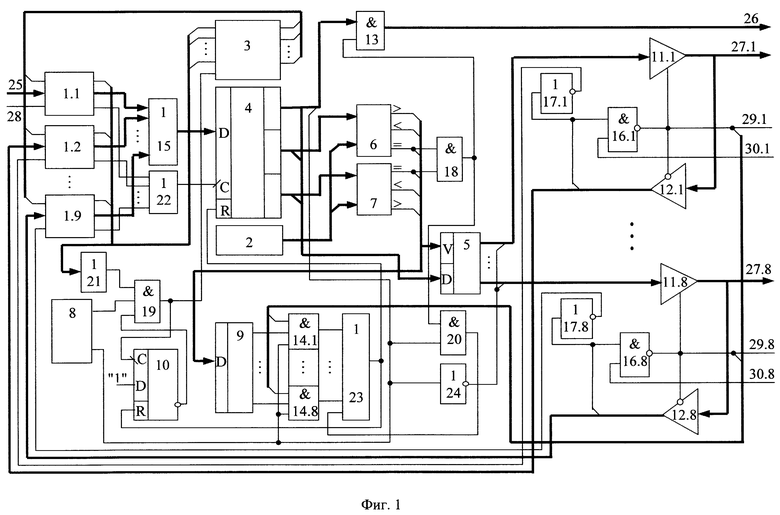

Сущность изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема модуля коммуникационной сети; на фиг. 2 представлена функциональная схема буферного запоминающего блока; на фиг. 3 показана функциональная схема блока считывания информации; на фиг. 4 приведена функциональная схема блока синхронизации; фиг. 5 поясняет принцип подключения соседних (смежных) модулей коммуникационной сети; на фиг. 6 дан формат сообщения; на фиг. 7 изображена структура коммуникационной сети на основе предлагаемого модуля; на фиг. 8 представлены временные диаграммы импульсов синхронизации модуля; на фиг. 9 приведены временные диаграммы сигналов управления взаимодействием смежных модулей коммуникационной сети.

Общие особенности изобретения состоят в следующем.

Предлагаемый модуль аналогично прототипу предназначен для функционирования в составе коммуникационной сети, включающей множество идентичных модулей, объединенных в регулярную (матричную) структуру (фиг. 7). Каждый модуль сети обслуживает соответствующее операционное устройство (например, вычислительный модуль в мультипроцессорной системе) и непосредственно связан с восемью другими модулями.

Взаимодействие модулей в сети осуществляется на основе транзитной передачи сообщений через другие модули. Сообщение включает информационную и адресную части (фиг. 6). Информационная часть содержит информацию, которая подлежит передаче модулю-приемнику сообщения. В адресной части фиксируется адрес (идентификатор) модуля-приемника сообщения, определяющий местоположение приемника в пределах структуры коммуникационной сети. Указанный адрес имеет вид a.b, где a и b - номера соответственно строки и столбца сети, содержащих модуль-приемник, "." - символ конкатенации.

Процесс передачи сообщения приемнику сводится к последовательности шагов, на каждом из которых сообщение обрабатывается соответствующим транзитным модулем. В ходе обработки осуществляется сопоставление содержимого адресной части сообщения (a.b) и адреса c.d текущего модуля (где c и d - номера соответственно строки и столбца сети, содержащих текущий модуль). В результате определяется направление выдачи сообщения - либо одному из смежных модулей ("вверх", "вниз", "влево", "вправо", "влево-вверх", "вправо-вверх", "влево-вниз", "вправо-вниз") для дальнейшей обработки (фиг. 7), либо операционному устройству, обслуживаемому текущим модулем (если данный модуль является приемником сообщения). В общем случае правило выбора направления выдачи сообщения имеет вид:

если c > a, то "вверх";

если c < a, то "вниз";

если c = a, то "стоп";

если d > b, то "влево";

если d < b, то "вправо";

если d = b, то "стоп".

Так, например, если c < a и d > b, то сообщение будет выдано "влево-вниз"; если c > a и d = b, то выдача осуществляется в направлении "вверх"; если c = a и d = b, то текущий модуль является приемником сообщения (передача сообщения завершена).

Ключевой особенностью заявляемого изобретения, обеспечивающей решение поставленной технической задачи, является применение двунаправленных каналов для взаимодействия пар смежных модулей. Каждый такой канал используется как для передачи, так и для приема сообщений за счет его временного мультиплексирования. Цикл использования канала разделяется на два такта. В первом из них канал настроен на передачу сообщений от первого модуля ко второму, во втором - на передачу сообщений от второго модуля к первому. Для управления настройкой канала используется асинхронный одноступенчатый RS-триггер, выполненный на элементах И-НЕ. Особенность подключения данного триггера при этом заключается в том, что его первый элемент И-НЕ конструктивно входит в первый модуль, а второй элемент И-НЕ - во второй модуль. Переключение триггера в противоположное состояние (и, следовательно, перенастройка канала) происходит по инициативе модуля, передающего сообщение, и обеспечивается непосредственно по импульсу, синхронизирующему передачу сообщения.

Принцип подключения смежных модулей коммуникационной сети иллюстрируется фиг. 5, где упомянутый выше RS-триггер (образованный элементами И-НЕ 16.j и 16. l) выделен пунктирной линией. Подробное описание процесса взаимодействия модулей сети при использовании заявляемого изобретения содержится ниже.

Применение двунаправленных каналов позволяет существенно сократить число внешних входов и выходов, требуемых для обеспечения межмодульного взаимодействия. При этом упрощается изготовление и комплексирование модулей при формировании коммуникационной сети. Особое значение минимизация числа внешних входов/выходов имеет в случае реализации модулей в виде отдельных СБИС, где указанные входы/выходы будут фактически внешними выводами на корпусе СБИС. В то же время число внешних выводов является одним из ключевых ограничений СБИС-технологии.

Количественная оценка преимуществ предлагаемого модуля перед прототипом дана в конце описания.

Модуль коммуникационной сети (фиг. 1) содержит буферные запоминающие блоки 1.1-1.9, блок 2 памяти констант, блок 3 считывания информации, регистр 4, демультиплексор 5, первый 6 и второй 7 блоки сравнения, блок 8 синхронизации, дешифратор 9, триггер 10, первую 11 группу блоков тристабильных элементов 11.1-11.8, вторую 12 группу блоков тристабильных элементов 12.1-12.8, блок элементов И 13, группу 14 элементов И 14.1-14.8, блок элементов ИЛИ 15, элементы И-НЕ 16.1-16.8, группу 17 элементов НЕ 17.1-17.8, первый 18, второй 19 и третий 20 элементы И, первый 21, второй 22 и третий 23 элементы ИЛИ, элемент НЕ 24, причем информационный и первый управляющий входы буферного запоминающего блока 1.1 являются информационным входом 25 и входом 28 синхронизации модуля соответственно, первые управляющие выходы буферных запоминающих блоков 1.1-1.9 соединены с входом элемента ИЛИ 21, а также с информационными входами блока 3 считывания информации с первого по девятый соответственно, выходы с первого по девятый которого подключены к вторым управляющим входам буферных запоминающих блоков 1.1-1.9 соответственно, информационные выходы которых подключены к входам блока элементов ИЛИ 15 с первого по девятый соответственно, выход которого соединен с информационным входом регистра 4, первая и вторая группы выходов которого соединены с первыми входами блоков 6 и 7 сравнения соответственно, выходы равенства которых подключены к первому и второму входам элемента И 18 соответственно, выход которого подключен к управляющему входу блока элементов И 13, информационный вход которого соединен с третьей группой выходов регистра 4, а выход является информационным выходом 26 модуля, выход блока 2 памяти констант соединен с вторыми входами блоков 6 и 7 сравнения, все выходы которых подключены к управляющему входу демультиплексора 5, информационный вход которого соединен с группами выходов регистра 4 с первой по третью, второй выход блока 8 синхронизации подключен к информационному входу блока элементов И 13, вторые управляющие выходы буферных запоминающих блоков 1.1-1.9 подключены к входам элемента ИЛИ 22 с первого по девятый соответственно, выход которого соединен с входом синхронизации регистра 4, выход элемента ИЛИ 21 соединен с первым входом элемента И 19, выход которого подключен к входу синхронизации блока 3 считывания информации, первый выход блока 8 синхронизации подключен к второму входу элемента И 19, выход которого соединен с входом синхронизации триггера 10, инверсный выход которого соединен с третьим входом элемента И 19, все выходы блоков 6 и 7 сравнения подключены к информационному входу дешифратора 9, выходы с первого по восьмой которого соединены с первыми входами элементов И 14.1-14.8 соответственно, вторые входы которых соединены с вторым выходом блока 8 синхронизации, выходы демультиплексора 5 с первого по восьмой подключены к информационным входам блоков 11.1-11.8 тристабильных элементов соответственно, выходы которых соединены с информационными входами/выходами 27.1-27.8 модуля соответственно, которые также подключены к информационным входам блоков 12.1-12.8 тристабильных элементов соответственно, старшие m разрядов выходов которых соединены с информационными входами буферных запоминающих блоков 1.2-1.9 соответственно, первые управляющие входы которых соединены с выходами элементов НЕ 17.1-17.8 соответственно, второй выход блока 8 синхронизации подключен к первому входу элемента И 20 и к входу элемента НЕ 24, выход которого соединен с информационными входами блоков 11.1-11.8 тристабильных элементов, младшие ((m+1)-e) разряды выходов блоков 12.1-12.8 тристабильных элементов соединены с входами элементов НЕ 17.1-17.8 соответственно и с первыми входами элементов И-НЕ 16.1-16.8 соответственно, выходы которых подключены к третьим входам элементов И 14.1-14.8 соответственно, выходы которых подключены к входам элемента ИЛИ 23 с первого по восьмой соответственно, выход которого соединен с входом сброса триггера 10, информационный вход которого соединен с шиной логической единицы, выход элемента И 18 подключен к второму входу элемента И 20, выход которого соединен с девятым входом элемента ИЛИ 23, выход которого соединен с входом сброса регистра 4, управляющие входы 30.1-30.8 модуля подключены к вторым входам элементов И-НЕ 16.1-16.8 соответственно, выходы которых соединены с управляющими входами блоков 11.1-11.8 тристабильных элементов соответственно, с управляющими входами блоков 12.1-12.8 тристабильных элементов соответственно и с управляющими выходами 29.1-29.8 модуля соответственно.

Назначение элементов и блоков модуля коммуникационной сети состоит в следующем.

Буферные запоминающие блоки 1.1, 1.2-1.9 служат для организации очередей сообщений, поступающих от операционного устройства данного модуля и восьми смежных модулей коммуникационной сети соответственно.

Блок 2 памяти констант предназначен для постоянного хранения адреса текущего модуля. Блок 2 не имеет входов и указанный адрес постоянно находится на его выходе.

Блок 3 считывания информации необходим для определения порядка опроса блоков 1.1-1.9 при считывании сообщений в регистр 4.

Регистр 4 служит для хранения считываемых из блоков 1.1-1.9 сообщений во время их обработки.

Демультиплексор 5 обеспечивает коммутацию сообщений в восемь межмодульных каналов к соседним модулям.

Блоки 6 и 7 сравнения предназначены для сопоставления адресной части сообщения, содержащейся в регистре 4, с адресом текущего модуля из блока 2.

Блок 8 синхронизации необходим для формирования двух сдвинутых друг относительно друга последовательностей импульсов синхронизации τ1 и τ2, синхронизирующих работу элементов модуля. Блок 8 не имеет каких-либо входов и генерация импульсов на его выходах происходит непрерывно с момента включения питания модуля.

Дешифратор 9 введен с целью преобразования кода с выходов блоков 6 и 7 сравнения, определяющего направление выдачи сообщения, в унитарный код номера соответствующего межмодульного канала.

Триггер 10 использован для управления блокировкой прохождения импульсов τ1 с блока 8 через элемент И 19.

Блоки 11.1-11.8 тристабильных элементов служат для блокировки выдачи сообщений на входы/выходы 27.1-27.8 модуля соответственно в случае их настройки на прием сообщений.

Блоки 12.1-12.8 тристабильных элементов предназначены для блокировки приема сообщений с входов/выходов 27.1-27.8 модуля соответственно в случае их настройки на передачу сообщений.

Блок элементов И 13 необходим для запрещения передачи информационной части сообщения из регистра 4 на выход 26 модуля в случае, если текущий модуль не является приемником сообщения.

Элементы И 14.1-14.8 требуются для блокировки прохождения импульсов τ2 на входы сброса регистра 4 и триггера 10 в случае настройки выбранного межмодульного канала на прием сообщений.

Блок элементов ИЛИ 15 предназначен для передачи сообщений с информационных выходов блоков 1.1-1.9 на информационный вход регистра 4.

Элементы И-НЕ 16.1-16.8 служат для управления передачей информации через блоки 11.1, 12.1, ..., 11.8, 12.8 соответственно и индикации текущей настройки соответствующих межмодульных каналов. Элементы И-НЕ {16.j} модуля в объединении с элементами И-НЕ {16.l} соответствующих смежных модулей образуют одноступенчатые RS-триггеры управления настройкой соответствующих межмодульных каналов (фиг. 5). Переключение указанных триггеров происходит по инвертированному импульсу.

Элементы НЕ 17.1-17.8 необходимы для инвертирования импульсов синхронизации, сопровождающих поступающие сообщения. Указанные импульсы передаются в инвертированном виде с тем, чтобы при их отсутствии на первых входах элементов И-НЕ 16.1-16.8 присутствовал единичный (пассивный) уровень сигнала.

Элемент И 18 предназначен для формирования сигнала, индицирующего совпадение адресной части обрабатываемого сообщения с адресом текущего модуля.

Элемент И 19 служит для блокировки прохождения импульсов τ1 с блока 8 синхронизации на входы синхронизации блока 3 и триггера 10.

Элемент И 20 введен с целью блокировки передачи импульсов τ2 с блока 8 синхронизации на входы сброса регистра 4 и триггера 10 при несовпадении адресной части сообщения с адресом текущего модуля.

Элемент ИЛИ 21 необходим для формирования сигнала, индицирующего наличие/отсутствие сообщений в блоках 1.1-1.9.

Элемент ИЛИ 22 требуется для передачи сигналов с вторых управляющих выходов блоков 1.1-1.9 на вход синхронизации регистра 4.

Элемент ИЛИ 23 предназначен для объединения сигналов с выходов элементов И 14.1-14.8, 20.

Элемент НЕ 24 используется с целью преобразования импульсов τ2 с блока 8 синхронизации в соответствующие инвертированные импульсы для сопровождения выдачи сообщений смежным модулям.

Назначение входов и выходов модуля коммуникационной сети состоит в следующем.

Информационный вход 25 модуля служит для приема сообщений от операционного устройства.

Информационный выход 26 модуля предназначен для выдачи информационной части сообщений операционному устройству.

Информационные входы/выходы 27.1- 27.8 модуля обеспечивают передачу и прием сообщений текущим модулем от соответствующих смежных модулей коммуникационной сети.

Вход 28 синхронизации модуля служит для приема импульсов, сопровождающих сообщения, проходящие на вход 25 модуля от операционного устройства.

Управляющие выходы 29.1-29.8 и управляющие входы 30.1-30.8 модуля предназначены для передачи/приема сигналов управления настройкой соответствующих межмодульных каналов и являются цепями обратных связей соответствующих триггеров управления настройкой каналов (фиг. 5).

Буферный запоминающий блок 1. i, i = 1, 2, ..., 9 (фиг. 2), включает регистры 31.1-31. K (где K - максимальная длина очереди сообщений), коммутаторы 32.1-32. K-1, демультиплексор 33, триггер 34, блок элементов И 35, элементы И 36.1-36.K, элемент И-НЕ 37, элемент ИЛИ 38, одновибратор 39, причем первый управляющий вход блока соединен с первым входом элемента ИЛИ 38, выход которого соединен с входами синхронизации регистров 31.1-31.K, инверсные выходы которых подключены к входам элементов И 36.1-36.K соответственно, выходы которых подключены к входам разрешения регистров 31.1-31.K соответственно, к управляющему входу демультиплексора 33 и к входу элемента И-НЕ 37, выход которого является первым управляющим выходом блока, второй управляющий вход которого соединен с входом установки триггера 34, прямой выход которого подключен к управляющему входу блока элементов И 35 и к входу одновибратора 39, выход которого соединен с вторым управляющим выходом блока, с вторым входом элемента ИЛИ 38 и с входом сброса триггера 34, инверсный и прямой выходы которого подключены соответственно к первым и вторым управляющим входам коммутаторов 32.1-32.K-1, информационный вход блока подключен к информационному входу демультиплексора 33, выходы с первого по (K-1)-й которого соединены с первыми информационными входами коммутаторов 32.1-32.K-1 соответственно, выходы которых соединены с информационными входами регистров 31.1-31. K-1 соответственно, K-й выход демультиплексора 33 подключен к информационному входу регистра 31.K, прямой выход регистра 31.1 соединен с информационным входом блока элементов И 35, выход которого является информационным выходом блока, прямые выходы регистров 31.2-31.K подключены к вторым информационным входам коммутаторов 32.1-32.K-1 соответственно.

Блок 3 считывания информации (фиг. 3) содержит триггеры 40.1-40.9, первую 41 группу элементов И 41.1-41.9, вторую 42 группу элементов И 42.1-42.9, элемент И 43, одновибратор 44, причем информационные входы блока с первого по девятый соединены с первыми входами элементов И 41.1-41.9 соответственно, выходы которых подключены к входам установки триггеров 40.1-40.9 соответственно, прямые выходы которых подключены к первым входам элементов И 42.1-42.9 соответственно, выходы которых соединены со счетными входами триггеров 40.1-40.9 соответственно, инверсные выходы которых подключены к входам элемента И 43 с первого по девятый соответственно, выход которого соединен с вторыми входами элементов И 41.1-41.9, вход синхронизации блока подключен к десятому входу элемента И 43 и к входу одновибратора 44, выход которого подключен к вторым входам элементов И 42.1-42.9, выходы которых соединены с выходами блока с первого по девятый соответственно, инверсный выход триггера 40.p (p = 1, 2, ..., 8) подключен к (p+2)-м входам элементов И 42.p+1-42.9.

Блок 8 синхронизации (фиг. 4) содержит генератор 45 импульсов, триггер 46, первый 47 и второй 48 элементы И, причем выход генератора 45 импульсов подключен к первым входам элементов И 47 и 48 и к счетному входу триггера 46, инверсный и прямой выходы которого соединены с вторыми входами элементов И 47 и 48 соответственно, выходы которых являются первым и вторым выходами блока соответственно.

Рассмотрим процесс функционирования предлагаемого модуля. Учитывая, что модуль предназначен для работы в составе коммуникационной сети (фиг. 7), его функционирование будем рассматривать во взаимосвязи с другими аналогичными модулями.

Первоначально все триггеры и регистры модуля и всех входящих в его состав блоков находятся в состоянии логического нуля, а в блоке 2 записан код адреса (c. d) модуля в пределах коммуникационной сети. Блок 8 синхронизации вырабатывает две непрерывные сдвинутые друг относительно друга последовательности импульсов синхронизации τ1 и τ2 (фиг. 8). Цепи начальной установки на фиг. 1-5 для упрощения условно не показаны.

Единичные коды с инверсных выходов регистров 31.1-31.K блока 1.i, i = 1, 2, . . . , 9 (фиг. 2) формируют единичные сигналы на выходах элементов И 36.1-36.K. Эти сигналы, в свою очередь, поступают на управляющий вход демультиплексора 33 и коммутируют его информационный вход с первым выходом. Кроме того, указанные сигналы обеспечивают нулевой уровень сигнала на выходе элемента И-НЕ 37 и разрешают запись информации в регистры 31.1-31.K. Нулевой сигнал с прямого выхода триггера 34 совместно с единичным сигналом с инверсного выхода триггера 34 коммутируют выходы коммутаторов 32.1-32.K-1 с соответствующими выходами демультиплексора 33. В то же время нулевой сигнал с прямого выхода триггера 34 запрещает передачу информации через блок элементов И 35 на информационный выход блока 1.i.

Нулевые сигналы с выходов элементов И-НЕ 37 блоков 1.1-1.9 формируют нулевой уровень сигнала на выходе элемента ИЛИ 21 (фиг. 1) и тем самым обеспечивают блокировку элемента И 19. Нулевые сигналы с прямых выходов триггеров 40.1-40.9 (фиг. 3) закрывают элементы И 42.1-42.9, а единичные сигналы с инверсных выходов указанных триггеров открывают элемент И 43.

В исходном состоянии сигналы на выходах элементов И-НЕ 16.1-16.8 (фиг. 1) могут иметь произвольное значение (нулевое или единичное). При этом, если на выходе элемента И-НЕ 16.j, j ∈ {1, ..., 8}, находится единичный сигнал, то на выходе элемента И-НЕ 16.l соответствующего смежного модуля (фиг. 1, 5) будет нулевой сигнал, и наоборот, поскольку эти элементы образуют единый RS-триггер управления настройкой соответствующего межмодульного канала.

Если на выходе элемента И-НЕ 16.j присутствует единичный сигнал, то блок 11. j открыт, а блок 12.j закрыт и его выход находится в высокоимпедансном состоянии. В результате первый вход элемента И-НЕ 16.j, вход элемента НЕ 17. j и информационный вход демультиплексора 33 (фиг. 2) блока 1.j+1 оказываются отключенными, что соответствует (для стандартных ТТЛ- и ЭСЛ-схем) подаче на них сигнала логической единицы. Единичный сигнал с выхода элемента И-НЕ 16.j (фиг. 1, 5) через выход 29.j модуля поступает на вход 30.l соответствующего смежного модуля, откуда подается на второй вход элемента И-НЕ 16.l. Учитывая, что на первом входе элемента И-НЕ 16.l смежного модуля находится единичный сигнал, проходящий с выхода элемента НЕ 24 текущего модуля через блок 11.j и затем через блок 12.l смежного модуля, на выходе элемента 16.l смежного модуля фиксируется нулевой сигнал. Этот сигнал подтверждает открытое состояние блока 12.l и закрывает блок 11.l, переводя его выход в высокоимпедансное состояние.

Если на выходе элемента И-НЕ 16.j текущего модуля находится нулевой сигнал, то блок 12.j будет открыт, а блок 11.j закрыт. В то же время на выходе элемента И-НЕ 16.l соответствующего смежного модуля будет единичный сигнал и, соответственно, блок 11.l данного модуля будет открыт, а блок 12.l закрыт. Таким образом, в первом случае текущий модуль будет настроен на передачу сообщений, а во втором - на прием сообщений от рассматриваемого смежного модуля.

Блок 8 синхронизации не имеет специальных управляющих входов и начинает формировать импульсы синхронизации сразу после включения питания (когда модуль находится в исходном состоянии). Импульсы τ1 с первого выхода блока 8 начинают поступать на элемент И 19 (фиг. 1), однако не вызывают никаких изменений ввиду блокировки данного элемента нулевым сигналом с выхода элемента ИЛИ 21. Импульсы τ2 со второго выхода блока 8 подаются на входы элементов И 14.1-14.8, 20, на информационный вход блока элементов И 13 и, проходя также через элемент НЕ 24, - на информационные входы блоков 11.1-11.8. Поскольку блок элементов И 13 и элемент И 20 закрыты нулевым сигналом с выхода элемента И 18, импульсы τ2 не проходят на их выходы. Прохождение импульсов τ2 через элементы И 14.1-14.8 никак не влияет на состояние модуля (если импульс τ2 проходит через элемент И 14.j, то он через элемент ИЛИ 23 передается на входы сброса регистра 4 и триггера 10 и подтверждает их нулевое состояние).

В то же время импульс 12, проходя через элемент НЕ 24, обеспечивает периодическую перенастройку межмодульных каналов, настроенных на передачу, на прием сообщений от смежных модулей. Такая перенастройка необходима для исключения тупиковой ситуации, когда смежный модуль должен передать сообщение текущему модулю, а соответствующий канал настроен на передачу сообщений от текущего модуля, которые в данный момент отсутствуют.

Процесс перенастройки канала протекает следующим образом.

Импульс τ2 инвертируется элементом НЕ 24 и (в виде инвертированного импульса) через открытый блок 11.j проходит на выход 27.j модуля (фиг. 1, 5). Далее указанный импульс поступает на вход 27.l смежного модуля и проходит через открытый блок 12.l на первый вход элемента И-HE 16.l и на вход элемента НЕ 17.l. В результате на выходе элемента 16.l возникает единичный уровень сигнала, а на выходе элемента 17.l образуется неинвертированный импульс. Единичный сигнал с элемента И-НЕ 16.l открывает блок 11.l и одновременно закрывает блок 12.l. Этот же сигнал возвращается на вход 30.j текущего модуля и поступает на второй вход элемента И-НЕ 16.j. Так как первый вход элемента 16.j отключен вследствие высокоимпедансного состояния выхода блока 12.j (что эквивалентно наличию единичного сигнала), на выходе элемента 16.j появляется нулевой сигнал. Этот сигнал открывает блок 12.j, закрывает блок 11.j и, возвращаясь на второй вход элемента 16.l смежного модуля, подтверждает единичный уровень сигнала на его выходе (происходит переключение RS-триггера, образованного элементом 16. j текущего и 16.l смежного модуля (фиг. 5)). Таким образом, текущий модуль настраивается на прием, а смежный модуль - на передачу сообщения по соответствующему каналу.

В ходе перенастройки на выходе элемента НЕ 17.l смежного модуля формируется импульс. При передаче сообщения (см. ниже) этот импульс обеспечивает прием сообщения в блок 1.l+1 смежного модуля, которое поступает через блок 12. l. При перенастройке на выходе блока 12.l сообщение отсутствует, на информационном входе блока 1.l+1 находится нулевой код и появление импульса на выходе элемента 17.l не влияет на состояние блока 1.l+1 и смежного модуля в целом.

Аналогичным образом осуществляется перенастройка других каналов.

Работа коммуникационной сети начинается в момент подачи на вход 25 некоторого модуля сообщения от обслуживаемого им операционного устройства. Процесс функционирования модуля может начаться как при поступлении сообщения на вход 25, так и при приеме первого сообщения с входа/выхода 27.j от одного из соседних модулей. Поступившее сообщение подается на информационный вход блока 1.1 (или 1.j+1) и записывается в данный блок импульсом синхронизации, приходящим на первый управляющий вход блока 1.1 (или 1.j+1). (Процесс записи сообщений в блоки 1.1-1.9 детально анализируется ниже). После записи сообщения в блок 1.1 (или 1.j+1) на первом управляющем выходе указанного блока появляется сигнал логической единицы, индицирующий наличие сообщений. Этот сигнал формирует единичный уровень сигнала на выходе элемента ИЛИ 21, который открывает элемент И 19. После открытия элемента И 19 модуль приступает к обработке поступающих сообщений.

Спустя определенное время в блоках 1.1-1.9 образуются очереди сообщений: в блоке 1.1 фиксируются сообщения, поступающие от операционного устройства, обслуживаемого данным модулем; в блоки 1.2-1.9 заносятся сообщения от смежных модулей, приходящие с входов/выходов 27.1-27.8 соответственно. В общем случае длина очереди сообщений в блоке 1.i, i ∈ {1, ..., 9}, может изменяться от 0 до K.

Запись очередного сообщения в блок 1.i, i ∈ {1, ..., 9}, происходит следующим образом.

Пусть в блоке 1.i находятся L сообщений, L = 1, ..., K-1. Тогда на инверсных выходах регистров 31.1-31.L (фиг. 2) присутствуют коды, отличные от единичных, а на инверсных выходах регистров 31.L+1-31.K установлены единичные коды (сообщения в регистрах 31.L+1-31.K отсутствуют). На выходах элементов И 36.1-36. L соответственно находятся нулевые сигналы, а на выходах элементов И 36.L+1-36.K присутствуют сигналы логической единицы. Сигналы с элементов И 36.1-36. K подаются на управляющий вход демультиплексора 33 и коммутируют его информационный вход с (L+1)-м выходом.

Сообщение с информационного входа блока 1.i проходит на (L+1)-й выход демультиплексора 33 и через открытый коммутатор 32.L+1 поступает на информационный вход регистра 31.L+1. Импульс синхронизации, сопровождающий сообщение, с первого управляющего входа блока 1.i подается на элемент ИЛИ 38, проходит через указанный элемент на входы синхронизации регистров 31.1-31.K и передним фронтом фиксирует сообщение в регистре 31.L+1. Воздействие рассматриваемого импульса на регистры 31.1-31.L, 31.L+2-31.K при этом никак не влияет ни их состояние, так как на входы разрешения регистров 31.1-31.L поступают нулевые (запрещающие) сигналы с выходов элементов И 36.1-36.L соответственно, а на информационных входах регистров 31.L+2-31.K находятся нулевые коды, проходящие с соответствующих выходов демультиплексора 33.

После записи сообщения в регистр 31.L+1 на выходе элемента И 36.L+1 образуется нулевой уровень сигнала. Сигналы с выходов элементов И 36.1- 36.K поступают на управляющий вход демультиплексора 33 и коммутируют его информационный вход с (L+2)-м выходом. Тем самым обеспечивается возможность записи следующего сообщения в регистр 31.L+2. Запись следующего сообщения производится аналогично описанному выше.

Если в момент поступления сообщения в блок 1.i все регистры 31.1-31.K находятся в нулевом состоянии (L = 0), то на выходах всех элементов И 36.1-36. K присутствуют сигналы логической единицы, информационный вход демультиплексора 33 скоммутирован с его первым выходом, а на выходе элемента И-НЕ 37 установлен нулевой уровень сигнала. В результате сообщение заносится в регистр 31.1. После этого на выходе элемента И 36.1 появляется нулевой сигнал, информационный вход демультиплексора 33 подключается к его второму выходу, а на выходе элемента И-НЕ 37 образуется единичный уровень сигнала, указывающий на наличие хотя бы одного сообщения в блоке 1.i.

Считывание сообщений из блоков 1.1-1.9 и их обработка осуществляются следующим образом.

Очередной импульс τ1 с первого выхода блока 8 синхронизации проходит через открытый элемент И 19 (фиг. 1). Далее указанный импульс подается на вход синхронизации триггера 10 и задним фронтом переключает его в единичное состояние. Нулевой сигнал, образующийся на инверсном выходе триггера 10, блокирует элемент И 19. (Блокировка элемента 19 необходима в том случае, когда сообщение не может быть выдано в требуемый канал ввиду его настройки на прием сообщения и должно быть сохранено до момента перенастройки указанного канала на передачу сообщения).

Одновременно импульс τ1 с выхода элемента И 19 поступает на вход синхронизации блока 3, где происходит определение порядка опроса блоков 1.1-1.9. Опрос блоков осуществляется циклами, начиная с блока 1.1 и заканчивая блоком 1.9. При этом аналогично прототипу опрашиваются только те блоки, в которых имеются сообщения.

В начале очередного цикла опроса триггеры 40.1-40.9 (фиг. 3) находятся в состоянии логического нуля и единичные сигналы с их инверсных выходов открывают элемент И 43. В данном случае импульс τ1 с входа синхронизации блока 3 проходит через элемент И 43 и подается на вторые входы элементов И 41.1-41.9. В то же время на первые входы элементов И 41.1-41.9 поступают сигналы с первых управляющих выходов блоков 1.1-1.9 соответственно (фиг. 1, 3). Если в блоке 1. k присутствуют сообщения, то на его первом управляющем выходе находится единичный сигнал, который открывает элемент И 41.k. Импульс τ1 через элемент 41.k передается на вход установки триггера 40.k и переключает его в единичное состояние. Аналогично происходит переключение других триггеров блока 3. В результате в триггерах 40.1-40.9 фиксируется код текущего состояния блоков 1.1-1.9 (состояние триггера 40.k нулевое, если в блоке 1.k нет сообщений, и единичное в противном случае). Сигналы с выходов триггеров 40.1-40.9 поступают на входы элементов И 42.1-42.9 и открывают элемент И 42. i с наименьшим номером i (остальные элементы И группы 42 при этом блокируются). Сигналы с инверсных выходов триггеров 40.1-40.9 закрывают элемент И 43.

В процессе реализации очередного цикла опроса блоков 1.1-1.9 некоторые триггеры 40.1-40.9 находятся в единичном состоянии и нулевые сигналы с их инверсных выходов закрывают элемент И 43. В данном случае импульс τ1 не проходит через элемент 43 и состояние триггеров 40.1-40.9 соответственно остается неизменным.

Одновременно с описанными выше процессами импульс τ1 с входа синхронизации блока 3 поступает на вход одновибратора 44. В результате по заднему фронту импульса τ1 на выходе одновибратора 44 появляется импульс τ

В то же самое время импульс τ

Импульс τ

В то же время переход сигнала из нуля в единицу на прямом выходе триггера 34 воздействует на одновибратор 39 и спустя определенное время задержки возбуждает на его выходе импульс τ

После сдвига очереди сообщений импульс τ

На этом процессы считывания сообщения и сдвига очереди сообщений в блоке 1.i завершаются.

После записи считанного сообщения в регистр 4 (фиг. 1) начинается обработка (анализ) адресной части сообщения с целью определения направления его выдачи. Для этого адресная часть сообщения (содержащая адрес a.b приемника сообщения) с первой и второй групп выходов регистра 4 поступает на первые входы блоков 6 и 7 сравнения и сопоставляется с адресом c.d текущего модуля, поступающим на вторые входы блоков 6 и 7 с выхода блока 2. В результате сопоставления на выходах блоков 6 и 7 формируется шестиразрядный код, определяющий необходимое направление выдачи сообщения (более детально правило выбора направления выдачи сообщений обсуждалось выше). Указанный код подается на управляющий вход демультиплексора 5, на информационный вход дешифратора 9; кроме того, третий и четвертый разряды данного кода с выходов равенства блоков 6 и 7 поступают на элемент И 18.

Если текущий модуль является приемником обрабатываемого сообщения (т.е. a.b = c.d), то на выходах равенства блоков 6 и 7 появляются единичные сигналы. Эти сигналы формируют единичный сигнал на выходе элемента И 18 и обеспечивают тем самым открытие элемента И 20 и блока элементов И 13. В результате информационная часть сообщения с третьей группы выходов регистра 4 проходит через блок элементов И 13 на выход 26 модуля и передается операционному устройству, обслуживаемому текущим модулем. В то же самое время код с выходов блоков 6 и 7, воздействуя на демультиплексор 5 и дешифратор 9, формирует на всех их выходах нулевые сигналы.

Если же текущий модуль не является приемником рассматриваемого сообщения (т.е. a.b ≠ c.d), то на выходе равенства хотя бы одного блока 6 или 7 устанавливается нулевой сигнал. На выходе элемента И 18 также образуется нулевой сигнал, который блокирует элемент И 20 и блок элементов И 13. В этом случае направление выдачи сообщения соответствует одному из восьми смежных модулей и определяется демультиплексором 5. Код с выходов блоков 6 и 7 коммутирует информационный вход демультиплексора 5 с одним из его выходов (например с k-м выходом) и сообщение с выходов регистра 4 через демультиплексор 5 передается на информационный вход блока 11.k. Если на выходе элемента И-НЕ 16.k при этом находится единичный сигнал (соответствующий межмодульный канал настроен на передачу сообщения), то сообщение проходит через открытый блок 11. k на вход/выход 27.k модуля и далее передается соседнему модулю. В противном случае (межмодульный канал настроен на прием сообщения) выдачи сообщения на вход/выход 27.k не происходит до перенастройки канала на передачу сообщений.

Одновременно код с выходов блоков 6 и 7 сравнения воздействует на дешифратор 9 и формирует на его k-м выходе единичный сигнал. Сигналы с выходов дешифратора 9 поступают на первые входы элементов И 14.1-14.8, на третьи входы которых подаются сигналы настройки межмодульных каналов с выходов элементов И-НЕ 16.1-16.8 соответственно. В результате элементы И группы 14, за исключением элемента 14. k, закрываются; состояние элемента 14.k при этом определяется текущей настройкой k-го межмодульного канала, которая, в свою очередь, задается сигналом с выхода элемента И-НЕ 16.k.

После завершения всех описанных выше процессов на втором выходе блока 8 появляется импульс синхронизации τ2/ (фиг. 8).

Если текущий модуль является приемником сообщения, то этот импульс проходит через открытые элемент И 20 и блок элементов И 13. С выхода блока элементов И 13 импульс τ2 через выход 26 модуля передается операционному устройству и передним фронтом синхронизирует прием информационной части сообщения. С выхода элемента И 20 импульс τ2 проходит через элемент ИЛИ 23 на входы сброса триггера 10 и регистра 4 и переводит их в нулевое состояние. Единичный сигнал с инверсного выхода триггера 10 вновь открывает элемент И 19, чем обеспечивается возможность считывания и обработки следующего сообщения.

В то же самое время импульс τ2 выполняет перенастройку всех каналов, настроенных на передачу сообщений, на прием сообщений от смежных модулей. Процесс перенастройки детально рассматривался выше и поэтому здесь не анализируется.

Если текущий модуль не является приемником сообщения, то импульс τ2 не проходит через элемент И 20 и блок элементов И 13 и дальнейший ход работы модуля определяется текущей настройкой k-го канала, т.е. уровнем сигнала на выходе элемента И-НЕ 16.k. В случае если на выходе элемента 16.k присутствует нулевой сигнал, то блок 11.k закрыт (передача сообщения запрещена ввиду настройки k-го канала на прием). Сигнал с элемента И-НЕ 16.k блокирует также и элемент И 14.k. В связи с этим импульс τ2 не проходит ни через элемент И 14. k, ни через блок 11.1 и, следовательно, не поступает в смежный модуль. Триггер 10 по-прежнему сохраняет единичное состояние и нулевой сигнал с его инверсного выхода запрещает прохождение следующего импульса τ1 через элемент И 19. Состояние регистра 4 также остается неизменным; обработка сообщения продолжается.

Если на выходе элемента 16.k установлен единичный сигнал, то блок 11.k оказывается открытым и сообщение с k-го выхода демультиплексора 5 поступает на вход/выход 27.k модуля, откуда передается на вход/выход 27.l соответствующего смежного модуля. Сигнал с выхода элемента 16.k открывает также и элемент И 14. k. Очередной импульс τ2 с блока 8 инвертируется элементом НЕ 24, после чего проходит через блок 11.k на вход/выход 27.k модуля, поступает на вход/выход 27.l смежного модуля и обеспечивает прием выданного сообщения. Этот же импульс наряду с обеспечением приема сообщения осуществляет перенастройку межмодульного канала для передачи сообщений от смежного модуля. Процесс перенастройки при этом протекает аналогично рассмотренному ранее, а прием сообщения смежным модулем происходит следующим образом.

Сообщение через блок 12.l смежного модуля (фиг. 1, 5) проходит на информационный вход блока 1.l+1 и далее (фиг. 2) через демультиплексор 33 и коммутатор 32.L+1 поступает на информационный вход регистра 31.L+1 (здесь L - текущая длина очереди сообщений в блоке 1.l+1). Импульс, сопровождающий сообщение, инвертируется элементом НЕ 17.l, после чего поступает на первый управляющий вход блока 1.l+1. В блоке 1.l+1 импульс подается на входы синхронизации регистров 31.1-31.K и фиксирует сообщение в регистре 31.L+1.

Временные диаграммы сигналов управления взаимодействием смежных модулей показаны на фиг. 9. Буквами a, ..., f на фиг. 9 обозначены цепи съема сигналов управления, отмеченные на фиг. 5.

В то же самое время в модуле, передающем сообщение, импульс τ2 с блока 8 проходит через элемент И 14.k (фиг. 1), через элемент ИЛИ 23 подается на входы сброса триггера 10 и регистра 4 и переключает их в нулевое состояние. Единичный сигнал, появляющийся на инверсном выходе триггера 10, снова открывает элемент И 19.

Кроме того, импульс τ2, проходя с выхода элемента НЕ 24 через открытые блоки группы 11, выполняет перенастройку соответствующих каналов на прием сообщения (перенастройка k-го канала, как описано выше, выполняется одновременно с передачей сообщения).

Работа предлагаемого модуля завершается после обработки последнего пришедшего сообщения и сдвига очереди сообщений в соответствующем буферном запоминающем блоке. В этом случае на первых управляющих выходах блоков 1.1-1.9 появляются сигналы логического нуля. Эти сигналы формируют нулевой сигнал на выходе элемента ИЛИ 21, который закрывает элемент И 19 и тем самым запрещает прохождение импульсов τ1 с блока 8 на входы синхронизации блока 3 и триггера 10. В то же время импульсы τ2 со второго выхода блока 8 продолжают проходить через элемент НЕ 24 и далее через открытые блоки группы 11 с целью периодической перенастройки соответствующих каналов на прием сообщений. Работа модуля может быть возобновлена с поступлением на вход 25 или на входы/выходы 27.1-27.8 модуля сообщения от операционного устройства или смежных модулей.

Оценим преимущества предлагаемого технического решения перед прототипом.

В прототипе для взаимодействия пары смежных модулей по входу и по выходу необходимо 2(m+1) линий связи, где m - разрядность сообщения (добавление единицы необходимо для учета линии, предназначенной для передачи импульсов, сопровождающих сообщения). Поскольку каждый модуль связан с восемью смежными модулями, общее число линий, требуемых для подключения модуля к смежным модулям, составляет Q1 = 16(m+1).

При использовании предлагаемого модуля для взаимодействия пары смежных модулей необходимо m+3 линии, m+1 линия из которых служит для приема и для выдачи сообщений, а две дополнительные линии обеспечивают передачу сигналов управления и фактически являются цепями обратных связей RS-триггера управления настройкой соответствующего канала (фиг. 5). Общее число линий для подключения модуля к соседним модулям составляет Q2 = 8(m+3). Значение m не может быть менее трех (m = 3 в предельном случае, когда адресная часть сообщения включает 2 разряда, а информационная часть - один разряд), поэтому Q2 значительно меньше Q1 при любых допустимых m. Так, при m = 11 Q1-Q2 = 80 линий, а если m = 17, то Q1-Q2 = 128 линий.

Использование одних и тех же линий для приема и для выдачи сообщений не снижает функциональных возможностей модуля (и коммуникационной сети в целом). Аналогично прототипу предлагаемый модуль позволяет строить коммуникационные сети с транзитной передачей сообщений по кратчайшему физическому пути между источниками и приемниками, при этом так же как и в прототипе при считывании сообщений исключается опрос буферных запоминающих блоков, не содержащих сообщений. Кроме того, при использовании заявляемого модуля сохраняется близкое к минимальному время передачи сообщения между смежными модулями. Выдача сообщения как и в прототипе осуществляется, как правило, за один период следования импульсов синхронизации: по импульсу τ1 происходит считывание сообщения и его обработка, по импульсу τ2 - выдача сообщения с перенастройкой каналов на прием сообщений. Если в момент появления импульса τ2 выдача сообщения невозможна из-за настройки требуемого канала на прием, то выдача сообщения производится за два периода следования импульсов синхронизации. Однако такая ситуация возможна лишь при некоторых соотношениях фаз и периодов следования импульсов синхронизации смежных модулей. Если указанные периоды примерно равны, то описанная ситуация маловероятна.

Таким образом, как следует из описания и приведенной выше оценки заявляемое изобретение позволяет существенно уменьшить число внешних входов и выходов, требуемых для организации взаимодействия модуля с другими модулями в составе коммуникационной сети, при этом сохраняется исходный уровень функциональных возможностей и быстродействия. Сокращение числа внешних входов и выходов способствует упрощению процессов изготовления и комплексирования модулей, в особенности при их реализации в виде СБИС. Тем самым достигается значительное расширение области целесообразного применения предлагаемого модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения коммутационных средств мультипроцессорных вычислительных и управляющих систем. Техническим результатом является расширение области применения устройства на основе минимизации числа внешних входов и выходов. Устройство содержит буферные запоминающие блоки, блок памяти констант, блок считывания информации, регистр, демультиплексор, блоки сравнения, блок синхронизации, блок элементов И, блок элементов ИЛИ, элементы И, элементы ИЛИ, дешифратор, триггер, группы блоков тристабильных элементов, группу элементов И, элементы И-НЕ, группу элементов НЕ, элемент НЕ. 3 з.п. ф-лы, 9 ил.

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Модуль матричного коммутатора | 1988 |

|

SU1575167A1 |

| Система коммутации устройств обработки информации | 1989 |

|

SU1798796A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Способ получения аминофенилэтаноламинов или их солей | 1974 |

|

SU533335A3 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПРОНИЦАЕМОСТИ ТКАНЫХ И НЕТКАНЫХ МАТЕРИАЛОВ ДЛЯ ИСПОЛЬЗОВАНИЯ В КАЧЕСТВЕ СРЕДСТВ ИНДИВИДУАЛЬНОЙ ЗАЩИТЫ ОТ БАКТЕРИАЛЬНОГО С РАЗНЫМ СТРОЕНИЕМ КЛЕТОЧНОЙ СТЕНКИ И ГРИБКОВОГО ЗАРАЖЕНИЯ ВОЗДУШНО-КАПЕЛЬНЫМ И КОНТАКТНО-БЫТОВЫМ ПУТЕМ | 2021 |

|

RU2770008C1 |

| US 3835896 A, 23.07.1974. | |||

Авторы

Даты

2001-05-10—Публикация

2000-07-10—Подача