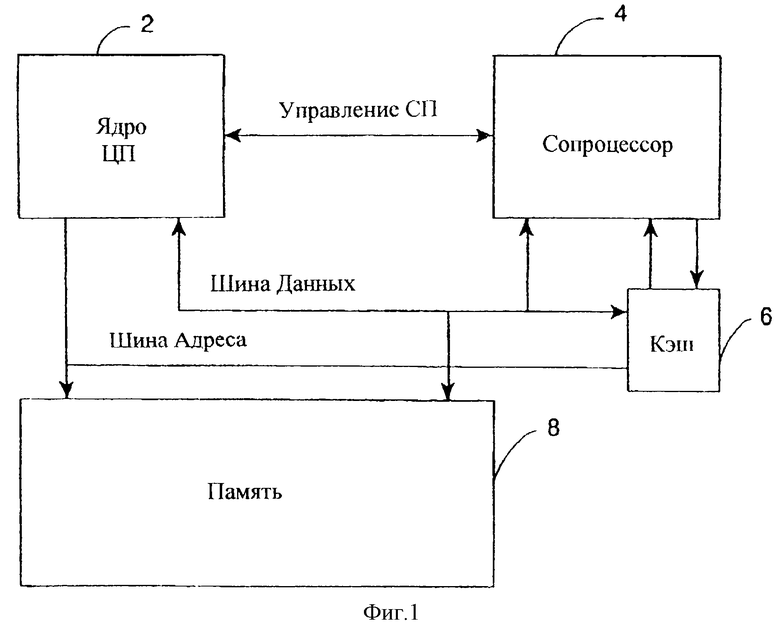

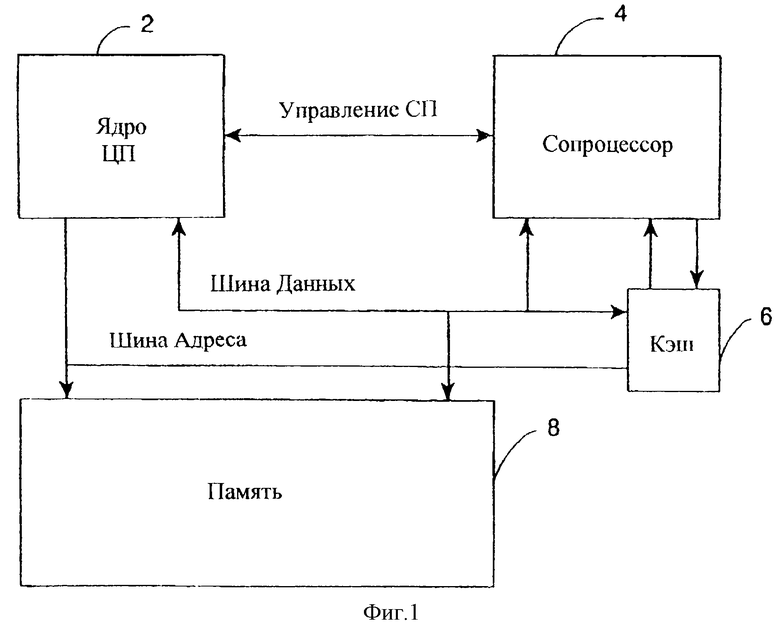

Изобретение относится к устройствам цифровой обработки сигнала. Техническим результатом является повышение эффективности операций смешанной системы, в которой микропроцессор используется для генерации адресов запоминающего устройства, а также снижение вероятности простоя одного из устройств, при котором одно из них должно ожидать окончания выполнения задания другим. Для этого в способе выполнения цифровой обработки сигнала блоком цифровой обработки сигналов выполняют арифметико-логические операции над словами данных одновременно и независимо от операций подачи и выборки, выполняемых микропроцессорным блоком, при этом, если блок цифровой обработки не способен принять слово данных, то микропроцессорный блок останавливают. Система, реализующая способ, содержит микропроцессорный блок, блок цифровой обработки сигнала. 2 с. и 31 з.п. ф-лы, 7 ил., 10 табл.

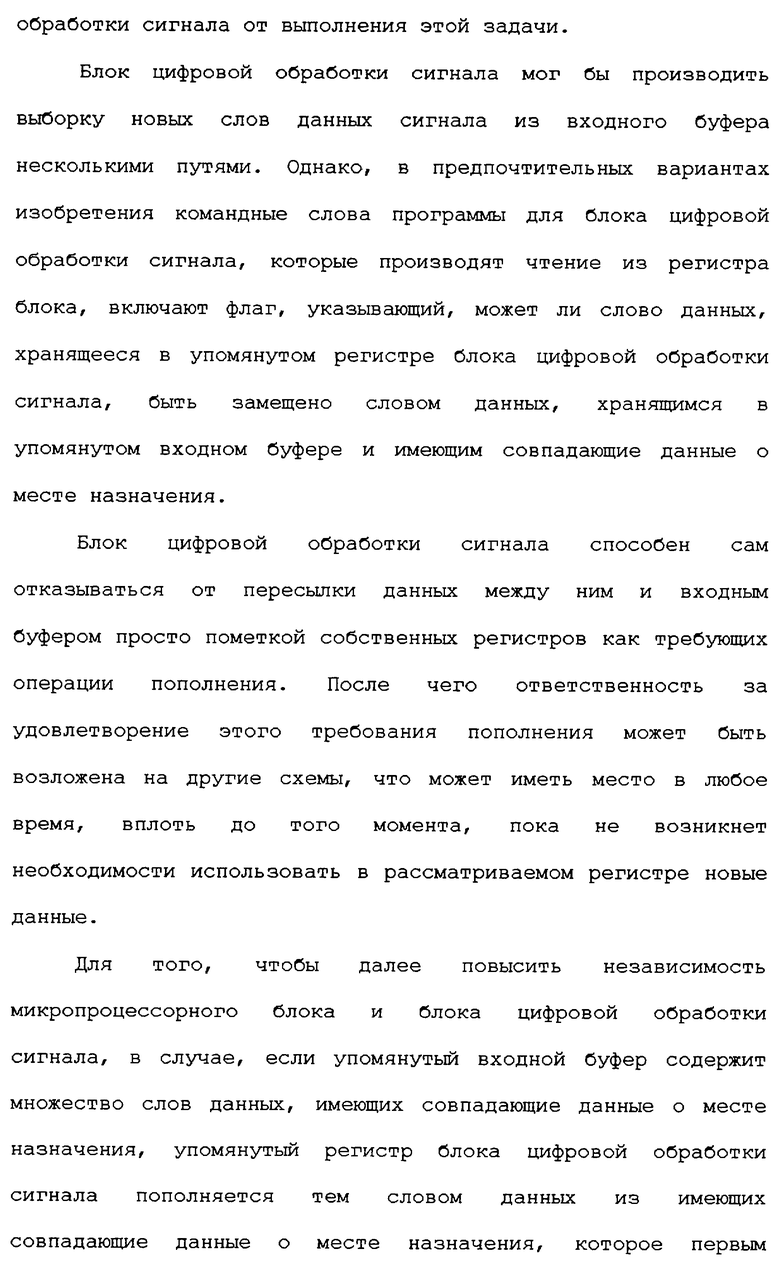

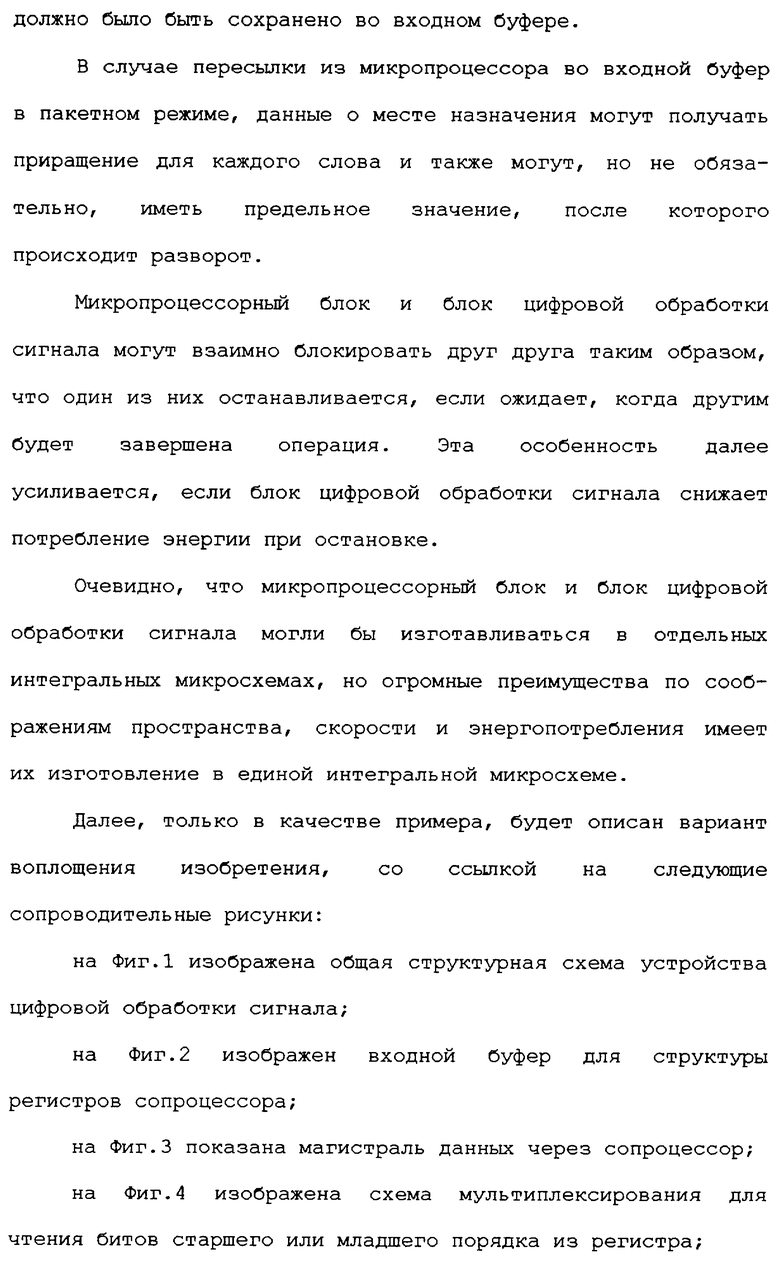

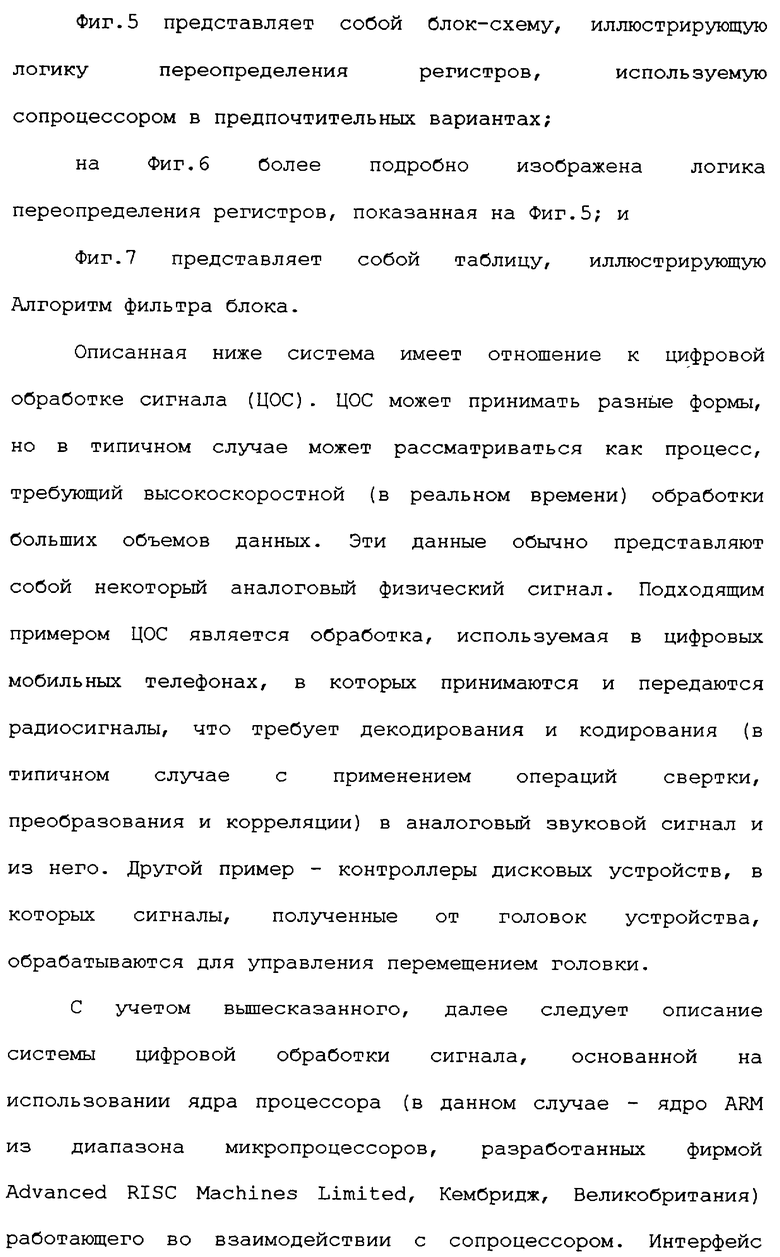

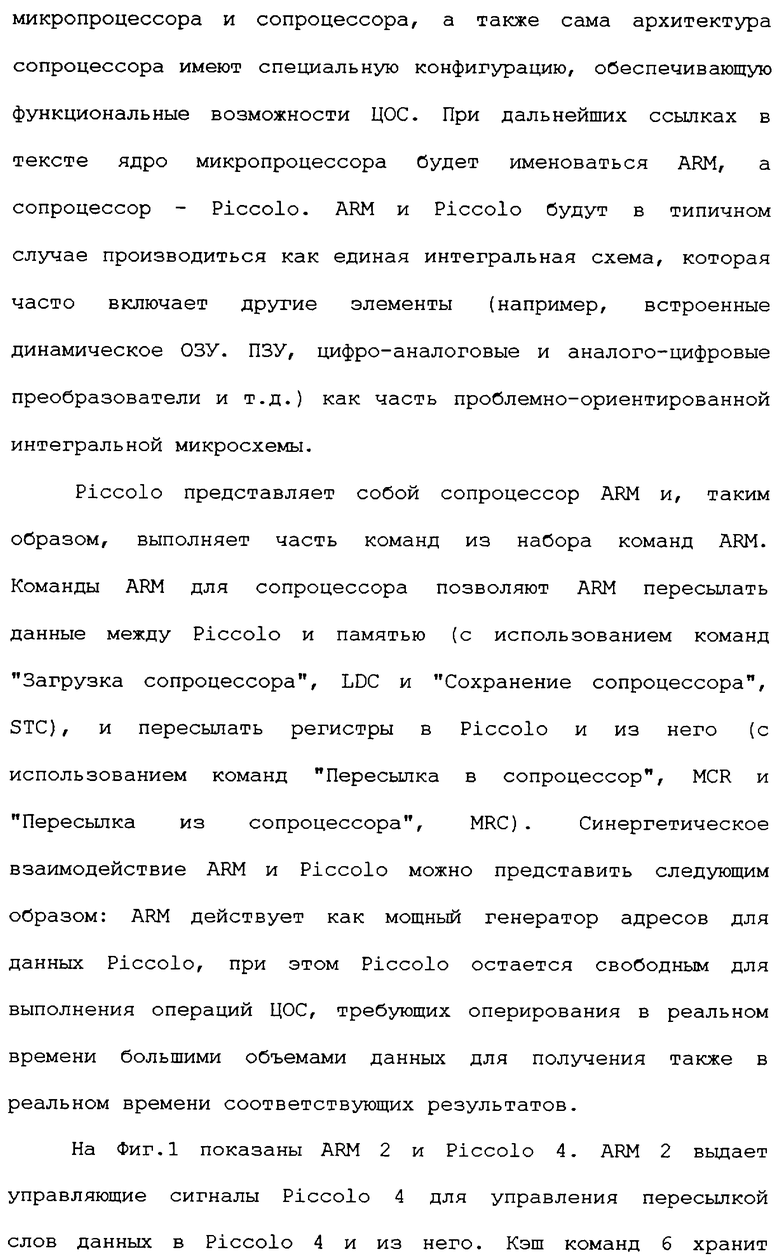

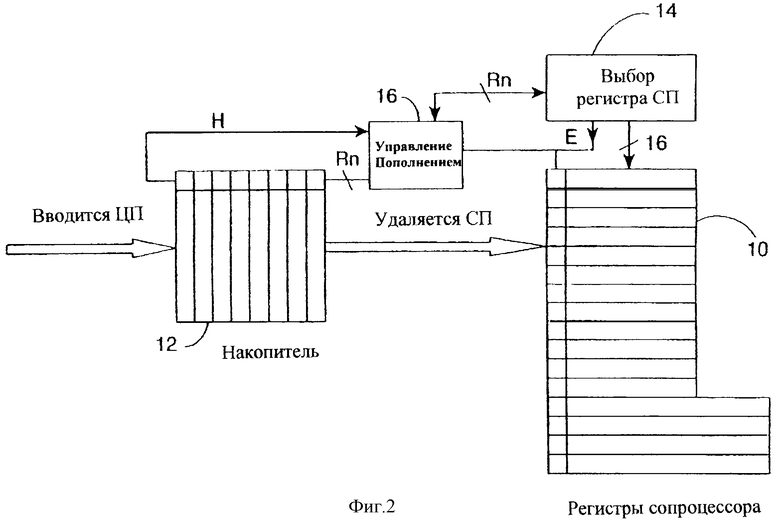

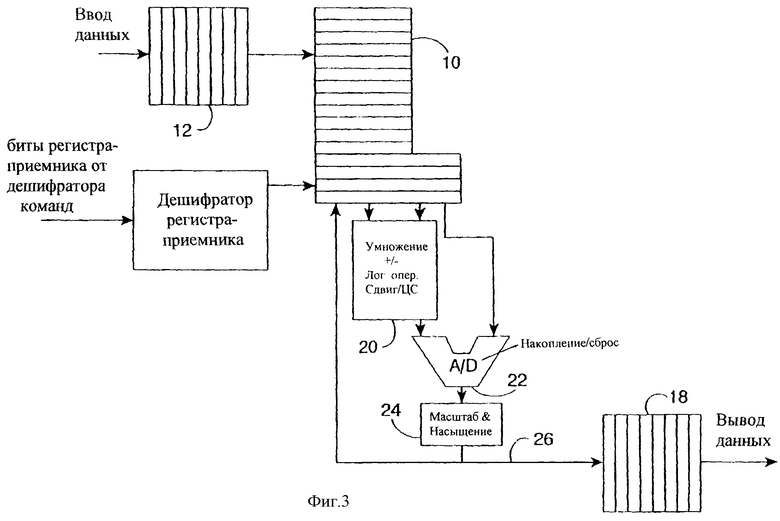

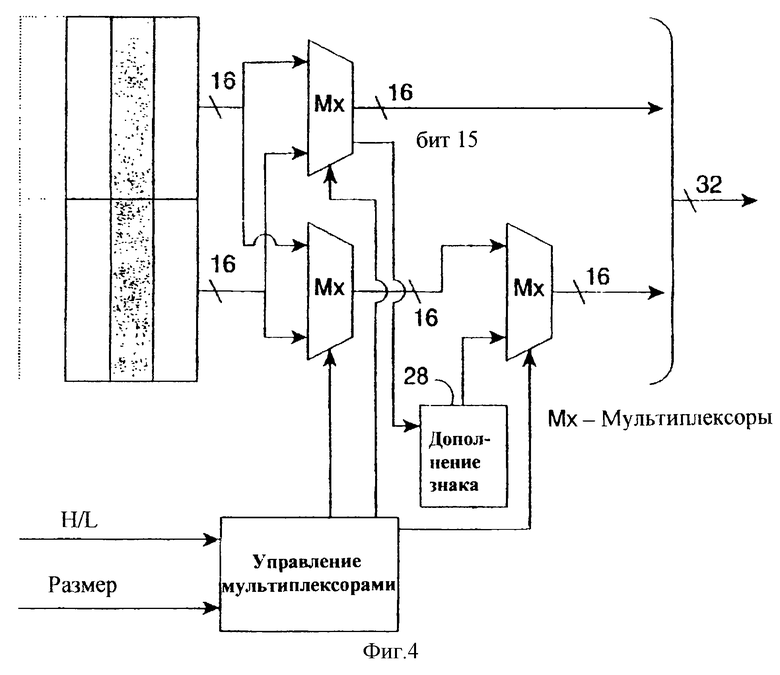

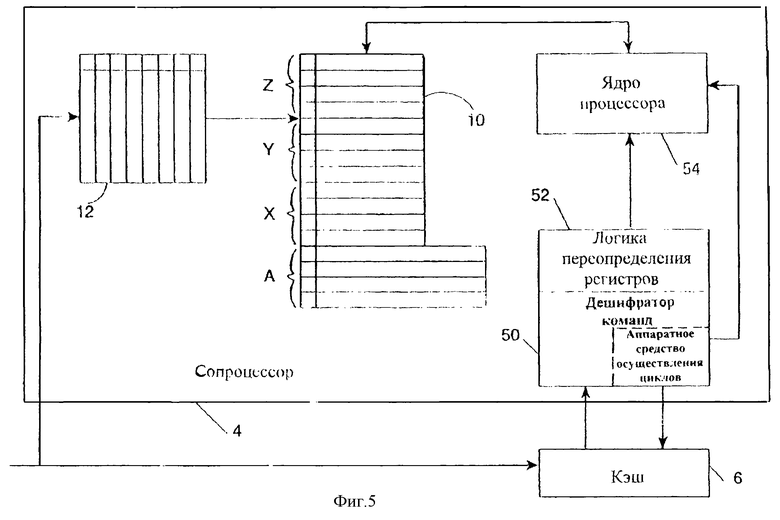

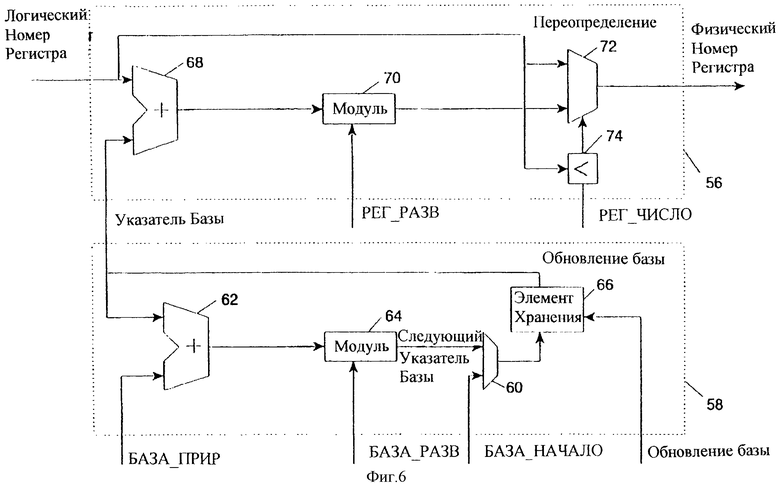

1. Способ выполнения цифровой обработки сигнала с использованием устройства цифровой обработки сигнала, применяемый к словам данных сигнала, хранящихся в устройстве (8) хранения данных, который содержит этапы генерации при работе микропроцессорного блока (2) под управлением командных слов программы для микропроцессорного блока, слов адреса для адресации ячеек хранения, хранящих упомянутые слова данных сигнала в упомянутом устройстве хранения данных, чтения, под управлением упомянутого микропроцессорного блока, упомянутых слов данных сигнала из упомянутых адресованных ячеек хранения, хранящих слова данных сигнала в устройстве хранения данных, подачи, под управлением микропроцессорного блока, слов данных сигнала в блок (4) цифровой обработки сигнала, работающий под управлением командных слов программы для блока цифровой обработки сигнала, выполнения, при работе упомянутого блока цифровой обработки сигнала под управлением командных слов программы для блока цифровой обработки сигнала, арифметико-логических операций, включающих в себя, по меньшей мере, одну из операции свертки, операции корреляции и операции преобразования над упомянутыми словами данных сигнала для генерации результирующих слов данных, и выборки, при работе упомянутого микропроцессорного блока под управлением командных слов программы для микропроцессорного блока, упомянутых результирующих слов данных из блока цифровой обработки сигнала, отличающийся тем, что блоком цифровой обработки сигнала выполняют упомянутые арифметико-логические операции над, по меньшей мере, одним или более словом данных сигнала одновременно и независимо от упомянутых операций подачи и выборки, выполняемых микропроцессорным блоком над одним или более словом данных сигнала, причем если упомянутый блок цифровой обработки сигнала не способен принять слово данных, поданное из упомянутого микропроцессорного блока, то упомянутый микропроцессорный блок останавливают.2. Способ по п.1, отличающийся тем, что упомянутый этап генерации дополнительно содержит этап генерации слов данных при работе упомянутого микропроцессорного блока, и упомянутый этап подачи дополнительно содержит этап подачи, под управлением упомянутого микропроцессорного блока, упомянутых слов данных в блок цифровой обработки сигнала, работающий под управлением командных слов программы для блока цифровой обработки сигнала.3. Способ по п.1, отличающийся тем, что содержит этапы генерации, под управлением упомянутого микропроцессорного блока, слов адреса для адресации ячеек хранения для хранения упомянутых результирующих слов данных в упомянутом устройстве хранения данных, и записи, под управлением упомянутого микропроцессорного блока, упомянутых результирующих слов данных в упомянутые адресованные ячейки хранения для хранения результирующих слов данных в упомянутом устройстве хранения данных.4. Способ по любому из пп.1, 2 или 3, отличающийся тем, что упомянутые слова данных сигнала представляют собой, по меньшей мере, один входной аналоговый сигнал.5. Способ по п.4, отличающийся тем, что упомянутый, по меньшей мере, один входной аналоговый сигнал является непрерывно изменяющимся входным сигналом в реальном времени.6. Способ по любому из предыдущих пунктов, отличающийся тем, что упомянутые результирующие слова данных представляют собой, по меньшей мере, один выходной аналоговый сигнал.7. Способ по п.6, отличающийся тем, что упомянутый, по меньшей мере, один выходной сигнал является непрерывно изменяющимся выходным сигналом в реальном времени.8. Устройство для выполнения цифровой обработки сигнала над словами данных сигнала, хранящимися в устройстве хранения данных, содержащее микропроцессорный блок, работающий под управлением командных слов программы для микропроцессорного блока, для генерации слов адреса для адресации ячеек хранения в упомянутом устройстве хранения данных и для управления пересылкой упомянутых слов данных сигнала между упомянутым устройством для выполнения цифровой обработки сигнала и упомянутым устройством хранения данных, и блок цифровой обработки сигнала, работающий под управлением командных слов программы для блока цифровой обработки сигнала для выполнения арифметико-логических операций, включающих в себя, по меньшей мере, одну из операции свертки, операции корреляции и операции преобразования над упомянутыми словами данных сигнала, извлеченных из устройства хранения данных микропроцессорным блоком, для создания результирующих слов данных, отличающееся тем, что упомянутые микропроцессорный блок и блок цифровой обработки сигнала работают одновременно и независимо, причем если упомянутый блок цифровой обработки сигнала не способен принять слово данных, поданное из упомянутого микропроцессорного блока, то микропроцессорный блок останавливается.9. Устройство по п.8, отличающееся тем, что упомянутые результирующие слова данных записываются в упомянутое устройство хранения данных упомянутым микропроцессорным блоком.10. Устройство по любому из пп.8 и 9, отличающееся тем, что упомянутые слова данных сигнала представляют собой, по меньшей мере, один входной аналоговый сигнал.11. Устройство по п.10, отличающееся тем, что упомянутый, по меньшей мере, один входной аналоговый сигнал является непрерывно изменяющимся входным сигналом в реальном времени.12. Устройство по любому из пп.8-11, отличающееся тем, что упомянутые результирующие слова данных представляют собой, по меньшей мере, один выходной аналоговый сигнал.13. Устройство по п.12, отличающееся тем, что упомянутый, по меньшей мере, один выходной сигнал является непрерывно изменяющимся выходным сигналом в реальном времени.14. Устройство по любому из пп.8-13, отличающееся тем, что микропроцессорный блок реагирует на командное слово множественной подачи, для подачи множества последовательно адресованных данных сигнала в упомянутый блок цифровой обработки сигнала.15. Устройство по любому из пп.8-14, отличающееся тем, что упомянутый блок цифровой обработки сигнала включает в себя многословный входной буфер (12).16. Устройство по любому из пп.8-15, отличающееся тем, что упомянутый микропроцессорный блок реагирует на командное слово множественной выборки для выборки множества последовательно адресованных результирующих слов данных из упомянутого блока цифровой обработки сигнала.17. Устройство по любому из пп.8-16, отличающееся тем, что упомянутый блок цифровой обработки сигнала включает в себя многословный выходной буфер (18).18. Устройство по любому из пп.8-17, отличающееся тем, что упомянутые устройство хранения данных и устройство цифровой обработки сигнала соединяет мультиплексированная шина данных и команд, служащая для пересылки слов данных сигнала, командных слов программы для микропроцессорного блока и командных слов программы для блока цифровой обработки сигнала в упомянутое устройство цифровой обработки сигнала.19. Устройство по любому из пп.8-18, отличающееся тем, что упомянутый блок цифровой обработки сигнала включает в себя банк регистров (10) блока цифровой обработки сигнала для хранения слов данных, над которыми должны быть выполнены арифметико-логические операции, причем упомянутые командные слова программы цифровой обработки сигнала включают в себя поля, задающие регистры.20. Устройство по любому из пп.15 и 19, отличающееся тем, что упомянутый входной буфер хранит данные о месте назначения, идентифицирующие регистр-приемник блока цифровой обработки сигнала для каждого слова данных, хранимых в упомянутом входном буфере.21. Устройство по п.20, отличающееся тем, что, по меньшей мере, одно командное слово программы для блока цифровой обработки сигнала, которое управляет блоком цифровой обработки сигнала для считывания, по меньшей мере, одного из регистров блока цифровой обработки сигнала, включает в себя флаг, указывающий, может ли слово данных, хранящееся в упомянутом регистре блока цифровой обработки сигнала, быть замещено словом данных, хранящимся в упомянутом входном буфере, имеющим совпадающие данные о месте назначения.22. Устройство по п.21, отличающееся тем, что в случае, если упомянутый входной буфер содержит множество слов данных, имеющих совпадающие данные о месте назначения, упомянутый регистр блока цифровой обработки сигнала пополняется тем словом данных из имеющих совпадающие данные о месте назначения, которое первым должно было быть сохранено во входном буфере.23. Устройство по любому из пп.14 и 20, отличающееся тем, что командное слово множественной подачи задает данные о месте назначения для первого слова данных, причем в результате исполнения командного слова множественной подачи упомянутые данные о месте назначения увеличиваются на приращение для каждого последующего слова данных, хранящегося во входном буфере.24. Устройство по п.23, отличающееся тем, что упомянутое командное слово множественной подачи также задает предельное значение для данных о месте назначения, причем упомянутые данные о месте назначения увеличиваются на приращение для каждого последующего слова данных до тех пор, пока не будет достигнуто упомянутое предельное значение, после чего, перед тем, как получить дальнейшее приращение, данные о месте назначения переустанавливаются в данные о месте назначения для упомянутого первого слова.25. Устройство по любому из пп.8-24, отличающееся тем, что микропроцессорный блок, работающий под управлением командных слов программы микропроцессорного блока, выбирает слова данных из упомянутого блока цифровой обработки сигнала, и если упомянутый блок цифровой обработки сигнала не способен подать слово данных, извлекаемое упомянутым микропроцессорным блоком, то микропроцессорный блок останавливается.26. Устройство по п.15, отличающееся тем, что если упомянутый блок цифровой обработки сигнала пытается считать слово данных, отсутствующее в упомянутом входном буфере, то блок цифровой обработки сигнала останавливается.27. Устройство по п.17, отличающееся тем, что если упомянутый блок цифровой обработки сигнала пытается записать слово данных в упомянутый выходной буфер, а упомянутый выходной буфер заполнен, то блок цифровой обработки сигнала останавливается.28. Устройство по любому из пп.26 и 27, отличающееся тем, что если упомянутый блок цифровой обработки сигнала останавливается, то упомянутый блок цифровой обработки сигнала входит в режим энергосбережения.29. Устройство по любому из пп.8-28, отличающееся тем, что содержит кэш-память блока цифровой обработки сигнала для хранения командных слов блока цифровой обработки сигнала.30. Устройство по п.29, отличающееся тем, что команды блока цифровой обработки сигнала могут быть предварительно выбраны в упомянутую кэш-память блока цифровой обработки сигнала в ответ на команду предварительной выборки.31. Устройство по п.20, отличающееся тем, что упомянутый блок цифровой обработки сигнала реагирует на команду, которая выполняет, по меньшей мере, одно из следующих действий: (i) помечает как пустые; и (ii) выводит содержимое множества регистров блока цифровой обработки сигнала.32. Устройство по любому из пп.8-31, отличающееся тем, что упомянутые микропроцессорный блок и блок цифровой обработки сигнала выполнены в виде единой интегральной микросхемы.33. Устройство по п.19, отличающееся тем, что упомянутое множество регистров блока цифровой обработки сигнала включает в себя, по меньшей мере, один регистр данных с разрядностью Х бит и, по меньшей мере, один регистр-аккумулятор с разрядностью Y бит, где Y больше, чем X.