Изобретение относится к вычислительной технике и, в частности, к структуре центрального процессора мультипрограммной мультипроцессорной вычислительной системы, в состав которого входит набор специализированных устройств обработки.

Известны центральные процессоры мультипрограммной мультипроцессорной вычислительной системы, содержащие процессор команд; процессор выполнения операций с фиксированной запятой, включающий набор регистров общего назначения; процессор выполнения операций с плавающей запятой, включающий набор регистров арифметики с плавающей запятой; устройство управления основной оперативной памятью и устройство управления основной расширенной памятью. Причем в процессорах выполнения операций содержатся буферные регистры операндов и магазины кодов операций, подключенные к выходу регистра команды процессора команд, регистры арифметики с плавающей запятой, буферы операндов и магазин кода операций арифметики с плавающей запятой подключены к исполнительным блокам процессора выполнения операций с плавающей запятой. Регистры общего назначения, буферы операндов и магазин кодов операций арифметики с фиксированной запятой подключены к исполнительному блоку процессора выполнения операций с фиксированной запятой. Регистры арифметики с плавающей запятой и исполнительный блок процессора выполнения операций с фиксированной запятой подключены к информационному буферу записи устройства управления основной оперативной памятью. Недостатком известного процессора является сложность структуры отдельных специализированных устройств. Путем определенных изменений структуры известного процессора может быть достигнута большая потенциальная производительность.

Предлагаемый центральный процессор отличается от известного тем, что он содержит в процессоре команд коммутирующую схему передачи команд на декодирование непосредственно из регистров буфера команд; схему быстрой предварительной проверки и схему точной проверки совпадения адресов ячеек памяти при подготовке операции запоминания с адресами команд, находящихся в буфере команд; схему записи команд непосредственно из информационного буфера записи устройства управления оперативной памятью при совпадении адреса ячейки памяти, в которую производится запись с адресом какой-либо команды, хранящейся в буфере команд процессора команд, одновременно с записью в ячейку памяти; раздельные шины передачи запросов на чтение и на запись от процессора

ных переходов, ускоряя работу вычислительной машины, и сохраняют содержимое регистров буфера команд, если перехода фактически нет.

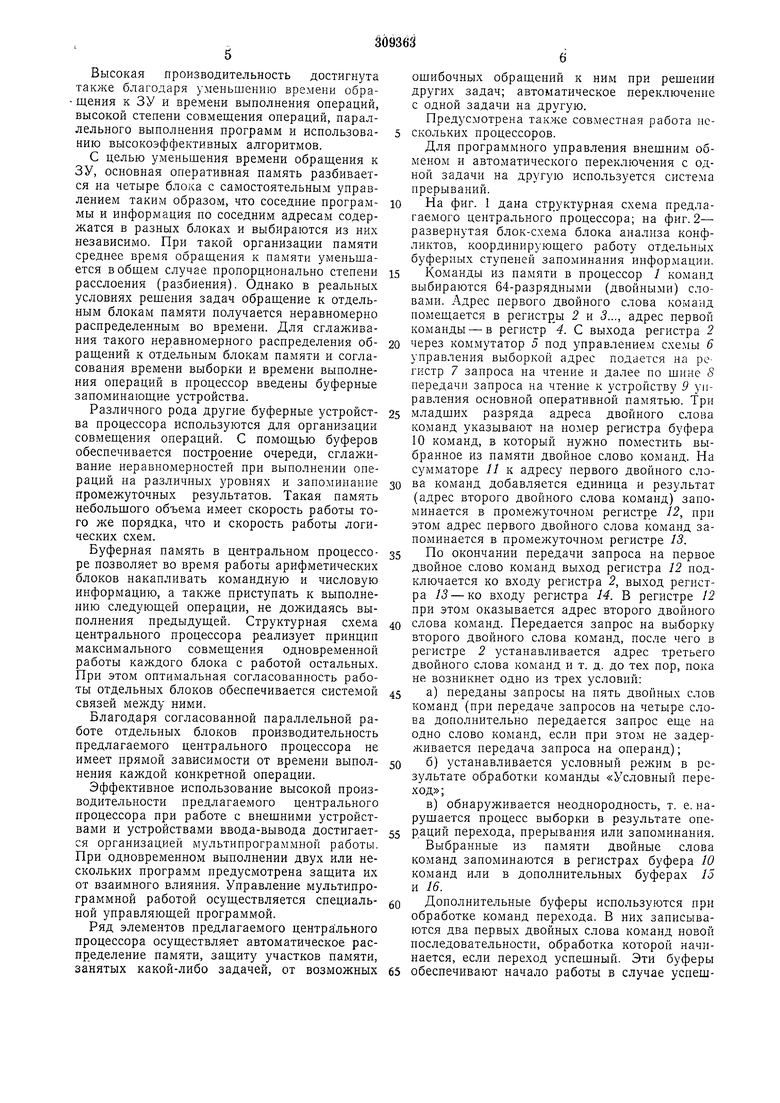

Первые 16 разрядов декодируемой команды и следующие 32 разряда из регистров буфера команд направляются на декодирование через коммутирующую схему 17 с помощью дешифратора 18.

К адресу декодируемой команды, записанному в регистре 4, на сумматоре 19 добавляется длина команды, а результат {адрес следующей команды) запоминается в разрядах 40- 63 регистра 20 слова состояния программы.

При переходе к декодированию следующей команды адрес из регистра 20 помещается в регистр 4. С помощью дешифратора 18 из регистров буфера команд подаются на декодирование первые 16 разрядов этой команды и следующие 32 разряда и т. д.

Команды декодируются в блоке 21 декодирования команд и помещаются в регистр 22 команды, из которого под управлением блока 23 анализа конфликтов направляются в процессор 24 выполнения операций с фиксированной запятой или процессор 25 выполнения операций с плавающей запятой в магазины кодов операций 26 и 27. Декодированные команды переходов и переключения состояния направляются блоком 21 в блок 28 выполнения команд переходов и переключения состояния, где они выполняются при участии блока 23 анализа конфликтов.

В блоке 29 модификации адреса процессора команд формируется адрес операнда и запрос в устройство управления оперативной памятью под управлением блока 23 анализа конфликтов. Запрос на выборку операнда подается через коммутатор 5 и регистр 7 запроса на чтение под управлением схемы 6. Сформированный в блоке 29 модификации адреса под управлением блока 23 анализа конфликтов запрос на запись подается в адресный буфер 30 записи в устройстве управления основной оперативной памятью по отдельной щине 31.

Если сформирован запрос на запись, то схема 32 быстрой проверки определяет предварительно, влияет ли операция запоминания на содержимое буфера 10 команд.

В случае определения такого влияния блокируется выборка команд и декодирование, включается схема 33 точной проверки, которая сравнивает адрес ячейки памяти, в которую будет производиться запоминание, с адресами в регистрах М и 3.

Регистр 3 отмечает адрес первого двойного слова команд, помещенного в буфер команд. Когда в результате увеличения адреса в регистре 2 происходит совпадение трех младших разрядов адреса двойного слова в этом регистре с тремя младщими разрядами адреса двойного слова в регистре 3 при передаче запроса в устройство управления основной оперативной памятью па выборку двойного слова

команд, единица добавляется не только к адресу в регистре 2, но и к адресу в регистре 3. Добавление единицы к адресу в регистре 3 производится на сумматоре 34, а результат запоминается в промежуточном регистре 35. По окончании передачи запроса выход регистра 35 подключается ко входу регистра 3. Совпадение трех младших разрядов адреса в регистрах 2 и 5 указывает на то, что буфер 10 комапд заполнен и при последующих выборках двойных слов команд происходит замена двойных слов команд, находящихся в этом буфере, начиная с первого.

Блокировка снимается, если результат точной проверки указывает на то, что запоминание пе влияет на содержимое буфера команд. Если же адрес ячейки памяти, в которой будет произведено заноминапие, совпадает с адресом какой-либо команды в буфере команд,

то блокировка пе снимается до тех пор, пока эта команда не будет заменена па новую. Как только информация для запоминания поступит в информационный буфер 36 записи, блокировка снимается. Такая замена производится

схемой 37.

Полный запрос в устройство управления основной оперативной памятью, кроме адреса ячейки памяти, содержит еще ключ защиты памяти, признак записи или признак чтения,

адрес регистра-приемника и маркер.

Четырехразрядный ключ защиты памяти служит для защиты определенных областей памяти от ошибочных засылок информации во время выполпения программы.

Для целей защиты оперативная память разделена на блоки по 256 двойных слов (2048 байтов). С каждым блоком связан пятиразрядный ключ памяти. Пятый разряд служит для защиты от выборки.

При обращении в память в устройстве 9 управления основной оперативной памятью производится сравпение четырехразрядного ключа защиты с четырьмя разрядами ключа памяти. Запись и чтепие разрешены, если при

этом происходит совпадение или, во всех разрядах ключа защиты пули. Если ключ защиты не пулевой и не совпадает с четырьмя разрядами ключа памяти, запись не разрещена. Чтепие разрешено, если при этом пятый разряд. ключа памяти нулевой и нет, если единица.

Ключ защиты хранится в регистре 20 слова состояния программы. Ключи памяти хранятся в блоке 38 памяти

ключей и поступают в устройство управления основной оперативной памятью по щине 39. Ключи памяти устанавливаются по команде «Установить ключ памяти и проверяются по команде «Прочитать ключ памяти блоком 28

выполнения команд переходов и переключения состояния.

Так как память оперирует со словами двойной длины, а команды - с информацией перемеппой длины (байт, полуслово, слово,

Высокая производительность достигнута акже благодаря уменьшению времени обраения к ЗУ и времени выполнения операций, ысокой степени совмещения операций, паралельного выполнения программ и использованию высокоэффективных алгоритмов.

С целью уменьшения времени обращения к У, основная оперативная память разбивается на четыре блока с самостоятельным управлением таким образом, что соседние программы и информация по соседним адресам содератся в разных блоках и выбираются из них независимо. При такой организации памяти среднее время обращения к памяти уменьшается в общем случае пропорционально степени расслоения (разбиения). Однако в реальных условиях решения задач обращение к отдельным блокам памяти получается неравномерно распределенным во времени. Для сглаживания такого неравномерного распределения обращений к отдельным блокам памяти и согласования времени выборки и времени выполнения операций в процессор введены буферные запоминающие устройства.

Различного рода другие буферные устройства процессора используются для организации совмещения операций, С помощью буферов обеспечивается постр оение очереди, сглаживание неравномерностей при выполнении операций на различных уровнях и запоминание промежуточных результатов. Такая память небольщого объема имеет скорость работы того же порядка, что и скорость работы логических схем.

Буферная память в центральном процессоре позволяет во время работы арифметических блоков накапливать командную и числовую информацию, а также приступать к выполнению следующей операции, не дожидаясь выполнения предыдущей. Структурная схема центрального процессора реализует принцип максимального совмещения одновременной работы каждого блока с работой остальных. При этом оптимальная согласованность работы отдельных блоков обеспечивается системой связей между ними.

Благодаря согласованной параллельной работе отдельных блоков производительность предлагаемого центрального процессора не имеет прямой зависимости от времени выполнения каждой конкретной операции.

Эффективное использование высокой производительности предлагаемого центрального процессора при работе с внешними устройствами и устройствами ввода-вывода достигается организацией мультипрограммной работы. При одновременном выполнении двух или нескольких программ предусмотрена защита их от взаимного влияния. Управление мультипрограммной работой осуществляется специальной управляющей программой.

Ряд элементов предлагаемого центрального процессора осуществляет автоматическое распределение памяти, защиту участков памяти, занятых какой-либо задачей, от возможных

ощибочных обращений к ним при рещении других задач; автоматическое переключение с одной задачи на другую.

Предусмотрена также совместная работа нескольких процессоров.

Для программного управления внещним обменом и автоматического переключения с одной задачи на другую используется систе.ма прерываний.

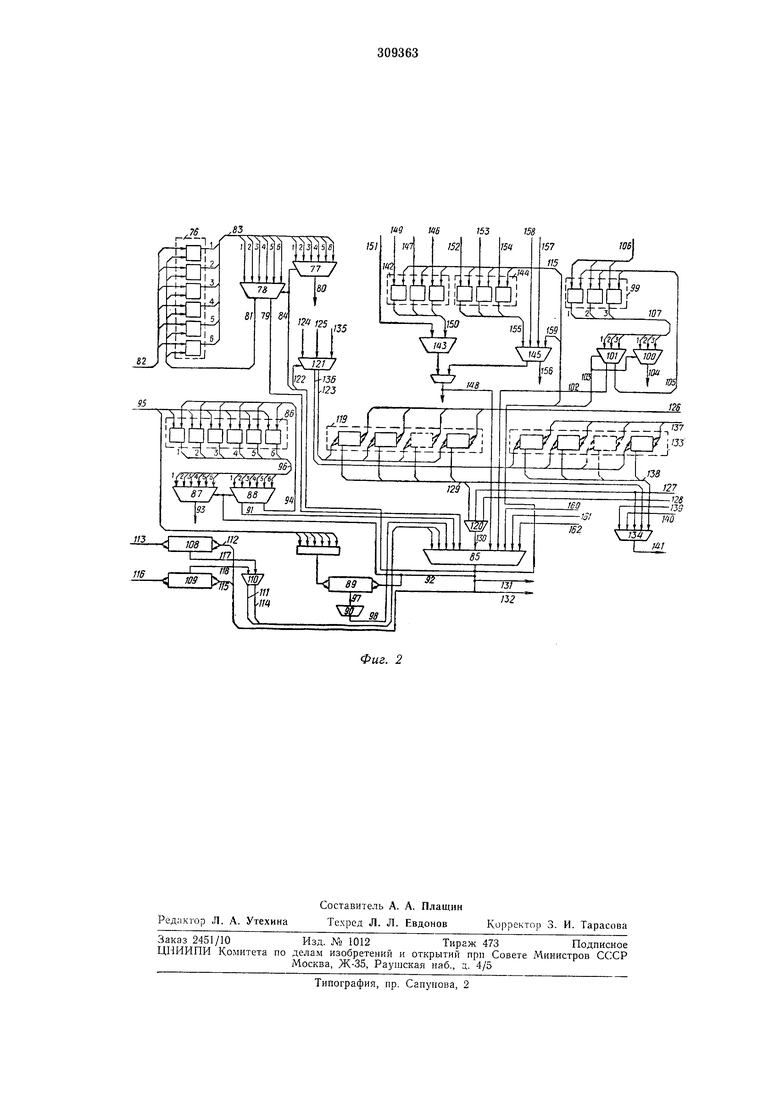

На фиг. 1 дана структурная схема предлагаемого центрального процессора; на фиг. 2- развернутая блок-схема блока анализа конфликтов, координирующего работу отдельных буферных ступеней запоминания информации. Команды из памяти в процессор 1 команд выбираются 64-разрядными (двойными) словами. Адрес первого двойного слова команд помещается в регистры 2 и 3..., адрес первой команды -в регистр 4. С выхода регистра 2 через коммутатор 5 под управлением схемы 6 управления выборкой адрес подается на регистр 7 запроса на чтение и далее по щине 6 передачи запроса на чтение к устройству 9 управления основной оперативной памятью. Три младших разряда адреса двойного слова команд указывают на номер регистра буфера 10 команд, в который нужно поместить выбранное из памяти двойное слово команд. На сумматоре И к адресу первого двойного слова команд добавляется единица и результат (адрес второго двойного слова команд) запоминается в промежуточном регистре 12, при этом адрес первого двойного слова команд запоминается в промежуточном регистре 13. По окончании передачи запроса на первое двойное слово команд выход регистра 12 подключается ко входу регистра 2, выход регистра 13 - ко входу регистра 14. В регистре 12 при этом оказывается адрес второго двойного слова команд. Передается запрос на выборку второго двойного слова команд, после чего в регистре 2 устанавливается адрес третьего двойного слова команд и т. д. до тех пор, пока не возникнет одно из трех условий: а) переданы запросы на пять двойных слов команд (при передаче запросов на четыре слова дополнительно передается запрос еще на одно слово команд, если при этом не задерживается передача запроса на операнд); б) устанавливается условный режим в результате обработки команды «Условный переход ;

в) обнаруживается неоднородность, т. е. нарушается процесс выборки в результате операций перехода, прерывания или запоминания. Выбранные из памяти двойные слова команд запоминаются в регистрах буфера 10 команд или в дополнительных буферах 15 и 16.

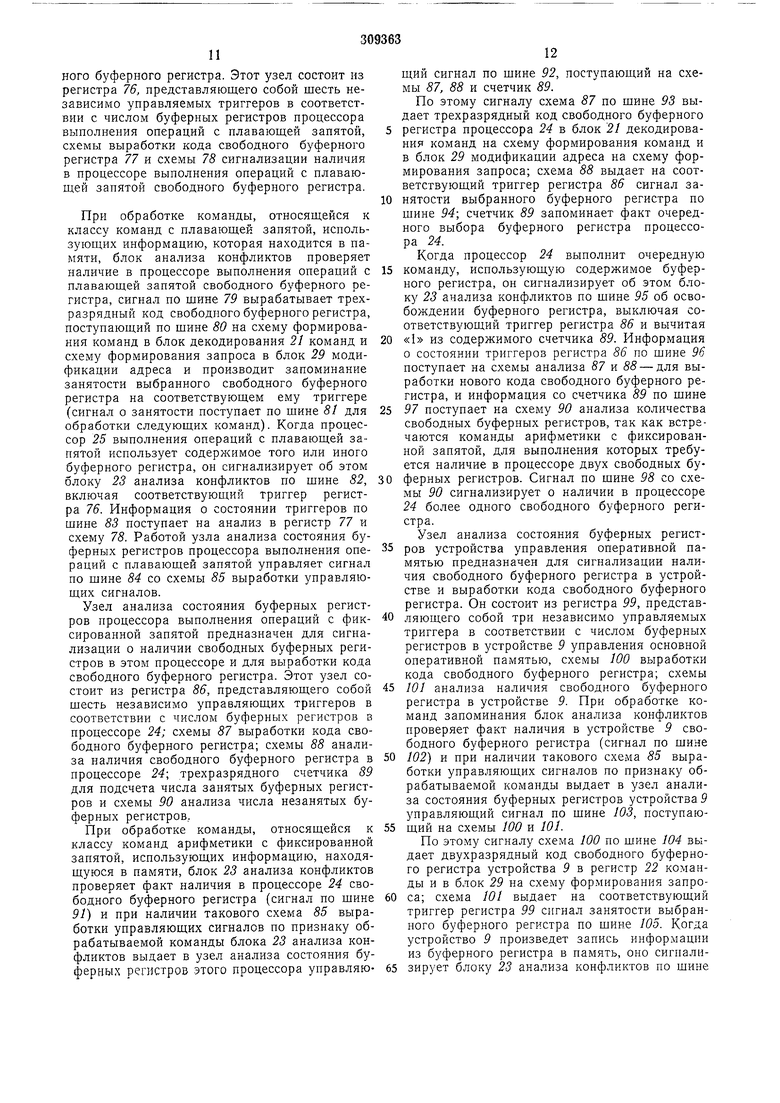

Дополнительные буферы используются при обработке команд перехода. В них записываются два первых двойных слова команд новой последовательности, обработка которой начинается, если переход успешный. Эти буферы обеспечивают начало работы в случае успешного буферного регистра. Этот узел состоит из регистра 76, представляющего собой шесть независимо управляемых триггеров в соответствии с числом буферных регистров процессора выполнения операций с плавающей запятой, схемы выработки кода свободного буферного регистра 77 и схемы 78 сигнализации наличия в процессоре выполнения операций с плавающей занятой свободного буферного регистра.

При обработке команды, относящейся к классу команд с плавающей запятой, иснользующих информацию, которая находится в памяти, блок анализа конфликтов проверяет наличие в процессоре выполнения операций с плавающей запятой свободного буферного регистра, сигнал по щине 79 вырабатывает трехразрядный код свободного буферного регистра, поступающий по щине 80 на схему формирования команд в блок декодирования 2/ команд и схему формирования запроса в блок 29 модификации адреса и производит запоминание занятости выбранного свободного буферного регистра на соответствующем ему триггере (сигнал о занятости поступает по щине 81 для обработки следующих команд). Когда процессор 25 выполнения операций с плавающей запятой использует содержимое того или иного буферного регистра, он сигнализирует об этом блоку 23 анализа конфликтов по щине 82, включая соответствующий триггер регистра 76. Информация о состоянии триггеров по щине 55 поступает на анализ в регистр 77 и схему 78. Работой узла анализа состояния буферных регистров процессора выполнения oneраций с плавающей запятой управляет сигнал по щине 84 со схемы S5 выработки управляющих сигналов.

Узел анализа состояния буферных регистров процессора выполнения операций с фиксированной запятой предназначен для сигнализации о наличии свободных буферных регистров в этом процессоре и для выработки кода свободного буферного регистра. Этот узел состоит из регистра 86, представляющего собой щесть независимо управляющих триггеров в соответствии с числом буферных регистров в процессоре 24; схемы 87 выработки кода свободного буферного регистра; схемы 88 анализа наличия свободного буферного регистра в процессоре 24 трехразрядного счетчика 89 для подсчета числа занятых буферных регистров и схемы 90 анализа числа незанятых буферных регистров.

При обработке команды, относящейся к классу команд арифметики с фиксированной занятой, использующих информацию, находящуюся в памяти, блок 23 анализа конфликтов проверяет факт наличия в процессоре 24 свободного буферного регистра (сигнал но щине 97) и при наличии такового схема 55 выработки управляющих сигналов по признаку обрабатываемой команды блока 23 анализа конфликтов выдает в узел анализа состояния буферных регистров этого процессора управляю12

щий сигнал по щине 92, поступающий на схемы 87, 88 и счетчик 89.

По этому сигналу схема 87 по щине 93 выдает трехразрядный код свободного буферного регистра процессора 24 в блок 21 декодирования команд на схему формирования команд и в блок 29 модификации адреса на схему формирования запроса; схема 88 выдает на соответствующий триггер регистра 86 сигнал занятости выбранного буферного регистра по щине 94; счетчик 89 запоминает факт очередного выбора буферного регистра процессора 24.

Когда процессор 24 выполнит очередную команду, использующую содержимое буферного регистра, он сигнализирует об этом блоку 23 анализа конфликтов по щине 95 об освобождении буферного регистра, выключая соответствующий триггер регистра 86 и вычитая «1 из содержимого счетчика 89. Информация о состоянии триггеров регистра 86 по щине 96 поступает на схемы анализа 87 и 88 - для выработки нового кода свободного буферного регистра, и информация со счетчика 89 по щине 97 поступает на схему 90 анализа количества свободных буферных регистров, так как встречаются команды арифметики с фиксированной запятой, для выполнения которых требуется наличие в процессоре двух свободных буферных регистров. Сигнал по щине 98 со схемы 90 сигнализирует о наличии в процессоре 24 более одного свободного буферного регистра.

Узел анализа состояния буферных регистров устройства управления оперативной памятью предназначен для сигнализации наличия свободного буферного регистра в устройстве и выработки кода свободного буферного регистра. Он состоит из регистра 99, представляющего собой три независимо управляемых триггера в соответствии с числом буферных регистров в устройстве 9 управления основной оперативной памятью, схемы 100 выработки кода свободного буферного регистра; схемы 101 анализа наличия свободного буферного регистра в устройстве 9. При обработке команд запоминания блок анализа конфликтов проверяет факт наличия в устройстве 9 свободного буферного регистра (сигнал по щине 102} и при наличии такового схема 55 выработки управляющих сигналов по признаку обрабатываемой команды выдает в узел анализа состояния буферных регистров устройства 9 управляющий сигнал по щине 103, поступающий на схемы 100 и 101.

По этому сигналу схема 100 по щине 104 выдает двухразрядный код свободного буферного регистра устройства 9 в регистр 22 команды и в блок 29 на схему формирования запроса; схема 101 выдает на соответствующий триггер регистра 99 сигнал занятости выбранного буферного регистра по щине 105. Когда устройство 9 произведет запись информации из буферного регистра в намять, оно сигнализирует блоку 23 анализа конфликтов по щине

ния требуемой информации и двойном слове необходимы особые признаки.

Место расположения требуемой информации указывается в запросе с помощью восьмиразрядного маркера (в соответствии с числом байтов в двойном слове).

Независимо от длины информации, которую необходимо записать в память, начало ее в регистрах информационного буфера 36 записи всегда совпадает со старшим разрядом.

Из буфера 36 информация поступает на схему 40 сдвига, которая подает информацию в шину 41 к блокам управления основной оперативной памяти и шину 42 к устройству управления расширенной оперативной памятью в соответствии с маркером соответствующего запроса на запись.

Информация, выбранная из памяти, приходит по шине 43 в соответствии с маркером в соответствующем запросе на чтение на входной регистр 44. Одновременно с информацией из памяти из устройства управления основной оперативной памятью по шине- 5 приходит адрес регистра-приемника, который помещается в регистр 46, и маркер по шине 47 в регистр 48. Схемой 49 сдвига информация сдвигается так, чтобы начало ее всегда совпадало со старшим разрядом регистра-приемника, и подается по шине 50 к регистр , определенному адресом регистра-приемника под управлением дешифратора 51 адреса регистра-приемника.

Кроме того, с регистра 44 информация подается на схему 52 контроля передачи.

Команды, оперирующие с информацией переменной длины, могут выполняться как программным, так и аппаратным методом. При использовании программного метода такие команды вызывают прерывание программы, по которому из памяти вызывается подпрограмма выполнения таких команд.

Для выполнения команд, оперирующих с информацией переменной длины, аппаратным методом предусматривается возможность подключения специализированного блока.

В этом случае прерывание программы не происходит, и код операции из блока 21 декодирования команд подается в специализированный блок по шине 53.

По шине 54 к блоку дешифрации команд подается сигнал о том, что специализированный блок подключен, по которому происходит блокировка прерывания при дешифрации команд, оперирующих с информацией переменной длины, и разрешение передачи кода операции этих команд.

Блок 55 прерываний обрабатывает прерывания программы при появлении внешних по отношению к системе сигналов, а также сигналов, поступающих из устройств ввода-вывода или возникающих в самом центральном процессоре.

Связь с другими центральными процессорами системы осуществляется по шинам 56 и 57 через блок 58 ввода-вывода.

Связь с каналами ввода-вывода по управлению осуществляется по шинам 59 и 60 через тот же блок 58, который участвует в обработке команд ввода-вывода и прямого управления.

Центральный процессор связан с блоками основной расширенной памяти через блок 61 управления основной оперативной памятью и устройство 62 управления основной расширенной памятью по адресной шине 63 и информационной шине 64.

Устройство 62 управления основной расширенной памятью связано с каналами вводавывода шиной 65.

По шине 66 от блока 61 управления основной оперативной памятью производится передача адреса при обращениях к блокам основной расширенной оперативной памяти.

Все команды с плавающей запятой выполняются в процессоре 25 выполнения операций с плавающей занятой, в который кроме магазина кодов операций 27 входят блок 67 сложения, в котором выполняются операции сложения (вычитания) с нормализацией результата

и без нормализации и сравнение; блок 6S умножения и деления, в котором выполняются операции умножения и деления; регистры 69 арифметики с плавающей запятой, предназначенные для временного хранения результатов операций с плавающей запятой; буфер 70 операндов арифметики с плавающей запятой, предназначенный для буферизации операндов, поступающих из оперативной памяти; дешифратор 71 кода операций.

Процессор 24 выполнения операций с фиксированной запятой предназначен для выполнения арифметических операций с фиксированной запятой и логических операций. Процессор 24, кроме магазина 26 кола операций.

содержит исполнительный блок 72, выполняющий арифметические и логические операции; буфер 75 операндов арифметики с фиксированной запятой, предназначенный для буферизации операндов, поступающих из оперативной

памяти; дешифратора 74 кода операций; регистры 75 общего назначения, предназначенные для временного хранения результатов операций с фиксированной запятой. Регистры общего назначения имеют непосредственную связь

с процессором / команд, который может обращаться к регистрам общего назначения, производить запись и чтение информации из этих регистров.

В некоторых случаях процессор 24 выполнения операций с фиксированной запятой может брать операнды из буфера 70 операндов арифметики с плавающей запятой, который связан с буфером 73 операндов арифметики с фиксированной запятой.

Узел анализа состояния буферных регистров процессора выполнения операций с плавающей запятой предназначен для сигнализации наличия в процессоре выполнения операций с плавающей запятой свободных буфер121. Наряду с функциями, описанными выше, схема 121 запоминает номера трех регистров общего назначения, содержимое которых будет использовано при выполнении команд процессором 24. Информация об этих регистрах поступает по шинам 135 и 124 из блока 21 и представляет собой четырехразрядные коды, содержащие номера регистров общего назначения 75. Схема 121 по сигналу по шине 136 производит запоминание номеров регистров общего назначения, содержимое которых будет использоваться при выполнении команд процессором 24. Запоминание производится на счетчиках 133, номера которых соответствуют номерам регистров общего назначения.

При выполнении процессором 24 команды, использующей содержимое регистра 75 общего назначения, этот процессор выдает в блок 23 анализа конфликтов на счетчик 133 по шине /57 сигнал, по которому этот счетчик производит вычитание «1 в соответствующем счетчике и перевод счетчика в нулевое состояние, означающее, что данный общий регистр свободен от использования его в командах с фиксированной запятой.

При обработке команд процессора, результатом выполнения которых является изменение информации регистра 75 общего назначения, необходимо следить за тем, чтобы информация заносилась только в тот регистр, который свободен от использования в командах процессора 24. Эту функцию выполняет схема 134 анализа занятости общих регистров для команд процессора. Схема 134 получает информацию о регистрах общего назначения, содержимое которых будет изменено в результате выполнения команд процессором 24 (шина 129); информацию о регистрах общего назначения, содержимое которых используется при выполнении команд процессором 24 (шина 138); информацию о регистре общего назначения, содерлшмое которого изменится в результате выполнения команды процессором 24, (шина 139) и признак команд процессора, изменяющих содержимое регистров общего назначения (шина 140).

Результат анализа со схемы,/54 в виде сигнала по шине 141 поступает в блок 29 и либо разрешает, либо запрещает запись информации в регистр 75 в результате выполнения команды процессором /.

Узел управления потоком команд предназначен для выявления конфликтных ситуаций, которые могут возникнуть при принятом параллельном способе обработки нескольких команд на разных уровнях. Он состоит из регистра 142, представляющего собой три независимо управляемых триггера, предназначенных для фиксации признаков, которые могут вызвать прерывание непрерывного потока обработки, обусловленное влиянием команд программы друг на друга; схемы 143 анализа межкомандных блокировок, регистра 144, представляющего собой три независимо управляемых регистра для фиксации признаков, которые могут вызвать прерывание непрерывного потока обработки команд, обусловленное влиянием условий, не относящихся к обрабатываемым командам; и схемы 145 анализа блокировок, не зависящих от обрабатываемых команд.

При обработке команд запоминания может возникнуть ситуация, когда результат выполнения очередной команды влияет на команду,

следующую за ней. В этом случае необходимо прекратить декодирование следующей команды, пока не закончится выполнение команды запоминания. При обработке команды запоминания блок анализа конфликтов заиоминает

эту команду на одном из триггеров регистра

142(сигнал по щине 146 из блока 21). Схема 32 быстрой проверки выдает на регистр 142 сигнал по шине 147, который сигнализирует о возможности такого влияния. Схема 143 в этом случае вырабатывает сигнал по шине 148, который поступает в блок 21 и блокирует подачу команд на дешифрацию и на схему для блокировки выработки управляюШ.ИХ сигналов.

После окончательного выявления влияния команды запоминания на команды, следующие за ней, схема 33 формирует сигнал по шине 149, который либо подтверждает действие сигнала по шине 147, либо отменяет его.

Информация с регистра 142 передается на схему анализа 143 по шине 150. Другой случай возникновения межкомандных блокировок происходит при обработке команд переходов. В этом случае необходимо прекращать выполнение очередных команд програ.ммы до выявления решения о переходе. Для этого схема

143получает из блока 21 сигнал признака команды перехода по шине 151.

При обработке команд программы возникают ситуации, когда приходится прекращать выполнение команд под влиянием условий, требующих перехода к обработке других программ или подпрограмм. К числу таких условий относятся поступление сигналов от блока

55 прерываний (сигнал по шпне 152), от таймера (сигнал по шине 153) или вмешательство оператора (сигнал по шипе 154). В любом из этих случаев схема 145 вырабатывает сигнал блокировки по шине 148 на основе анализа содержимого регистра 144, поступающего на схему 145 по шине /55. С другой стороны схема 145 сама вырабатывает сигнал прерывания, по шине 156 поступающий в блок 55 прерываний. Если этот блок принимает сигнал

на исполнение, он сообщает об этом блоку 23 анализа конфликтов посылкой сигнала по шине 152, а та, в свою очередь, производит прерывание обработки основного потока команд.

Причиной выработки сигнала прерывания по шине 156 схемой 145 является: отсутствие в системе оборудования для выполнения тех или иных команд (сигнал по шине /57), так как в этом случае они являются с помощью

13

106 об освобождении буферного регистра, сбрасывая соответствующий триггер регистра 99. Информация о состоянии триггеров регистра 99 по шине 107 поступает на схемы анализа 100 и 101 для выработки нового кода свободного буферного регистра устройства 9.

Узел анализа состояния магазинов кодов операций процессоров выполнения операций с фиксированной и плавающей запятой предназначен для сигнализации способности процессоров принимать команду на исполнение, т. е. того, что магазины команд процессоров имеют свободные регистры для приема команд. Он состоит из четырехразрядного счетчика 108, фиксирующего число команд, переданных в процессор 25; трехразрядного счетчика 109, фиксирующего число команд, поступивших в процессор 24, и схемы 110 анализа способности процессоров принять в магазин следующую очередную команду.

При обработке команды с плавающей запятой блок анализа конфликтов проверяет способность процессора 2.5 принять команду на исполнение по сигналу по шине 111 со схемы 110. При положительном ответе схема 85 блока 23 анализа конфликтов выдает в счетчик 108 сигнал по шине 112, по которому этот счетчик запоминает факт передачи команды в процессор 25. По окончании выполнения очередной команды процессор 25 выдает в блок 23 анализа конфликтов сигнал по щине 113 на счетчик 108, который сигнализирует об освобождении одного из восьми регистров магазина кодов операций. Аналогично при обработке команды с фиксированной запятой блок анализа конфликтов проверяет способность процессора 24 принять команду на исполнение по сигналу по ШЛне.114 схемы 110 и при положительном ответе схема 85 блока 23 анализа конфликтов выдает в счетчик 109 сигнал по шине 115, по которому этот счетчик запоминает факт передачи команды в процессор 24. По окончании выполнения очередной команды процессор 24 выдает в блок анализа конфликтов сигнал по шине 116 на счетчик 109, который сигнализирует об освобождении одного из шести регистров магазина кодов операций. Содержимое счетчиков 108 и 109 по шинам 117 и 118 поступает в схему 110 для следующего анализа.

Узел анализа занятости общих регистров для модификации адреса предназначен для управления поступлением информации в сумматор модификатора. Узел состоит из 16 трехразрядных счетчиков 119 в соответствии с числом регистров общего назначения, находящихся Б процессоре 24, схемы 120 анализа занятости регистров общего назначения и схемы 121 управления счетчиками занятости регистров общего назначения. При обработке команды, относящейся к классу команд арифметики с фиксированной запятой, в результате выполнения которой будет изменяться содержимое регистра общего назначения, схема 85 блока анализа конфликтов вырабатывает сигнал уп14

равления, по шине 122 поступающий на схему 121.

Схема 121 запоминает факт изменения содержимого регистра общего назначения путем выдачи сигнала по шине 123 на счетчик, номер которого соответствует номеру того регистра общего назначения, содержимое которого будет изменено в результате выполнения команды процессора 24. Для выработки сигналов

управления счетчиками 119 схема 121 получает с выходной ступени блока 21 по шине 124 четырехразрядный код номера общего регистра 75, содержимое которого будет изменено, и сигнал 125 - признак команд, изменяющих

содержимое регистров общего назначения.

При выполнении процессором 24 команды, в результате которой содержимое регистра общего назначения изменяется, процессор сигнализирует об этом блоку 23 анализа конфликтов, выдавая по шине 126 сигнал на счетчик с номером, соответствующим номеру регистра общего назначения, содержимое которого изменилось. По ЭТОМУ сигналу вычитается «1 из содержимого соответствующего счетчика,

и счетчик переходит в нулевое состояние. Это означает, что данный общий регистр свободен. При обработке команд, требующих модификации адреса содержимым общих регистров, прежде чем послать содержимое общих регистров в блок 29, необходимо убедиться, что общие регистры, содержимое которых будет использовано, свободны.

Эту функцию выполняет схема 120 анализа занятости общих регистров для модификации

адреса. По шинам 127 и 128 из блока 21 схема 120 получает номера регистров общего назначения, содержимое которых должно быть передано в блок 29, а по шине 129 - информацию о состоянии регистров общего назначения в

данный момент. В результате анализа схема 120 вырабатывает сигнал по шине 130, который поступает на схему 85 блока анализа конфликтов и содержит информацию, разрешающую или запрещающую передачу содержимого регистров общего назначения в блок 29 модификации адреса. При разрешении использования содержимого регистров общего назначения для модификации адреса схема 85 вырабатывает управляющие сигналы, поступающие

в блоки 21 и 29 по шинам 131 и 132.

Узел анализа занятости регистров общего назначения для процессора / команд предназначен для управления занесением информации в регистры общего назначения в результате выполнения команд этим процессором, изменяющих содержимое общих регистров. Он состоит из 16 трехразрядных счетчиков 133 в соответствии с числом регистров общего назначения; схемы 134 анализа занятости схемы

121 управления счетчиками занятости. При обработке команды, относящейся к классу команд арифметики с фиксированной запятой, схема 85 блока 23 анализа конфликтов вырабатывает, как было описано выше, сигнал упцу полуслова, слова и двойного слова при передаче информации от информационного буфера записи к блокам памяти и на границу двойного слова при передаче информации из блоков памяти в буфер операндов арифметики с плавающей запятой и буфер операндов арифметики с фиксированной запятой, он содержит шины передачи маркера выставки от схемы модификации адреса к адресному буферу записи, от регистра запроса на чтение кю блоку управления основной оперативной памятью и от блока управления основной оперативной памятью к процессору команд, причем меледу памятью и процессором команд включен дополнительный регистр сдвига со схемойis контроля правильности передачи, а между информационным буфером записи и памятью- схема сдвига. 4. Центральный процессор мультипрограммной мультипроцессорной вычислительной си-20 стемы по п. 1, отличающийся тем, что, с целью сокращения оборудования, в нем блок анализа конфликтов содержит узлы анализа состояния буферных регистров процессоров выполнения операций с фиксированной и пла-25 вающей запятой и устройства управления основной оперативной памятью, включающие входные регистры, схемы выработки кодов свободных буферных регистров и схемы анализа наличия свободных буферных регистров, связанных управляющими выходами с входными регистрами; узлы анализа состояния магазинов кодов операций процессоров выполнения операций с фиксированной и плавающей запятой, содержащие счетчики числа команд в исполнительных блоках и схему анализа наличия свободных ячеек в магазинах, связанную с выходами счетчиков узла, узел анализа занятости регистров общего назначения для блока модификации адреса, включающий набор счетчиков числа команд изменения содержимого любого регистра общего назначения, схему сигнализации освобождения регистров общего назначения, подключенную к модификатору, и схему управления счетчиками, узел анализа занятости регистров общего назначения для команд процессора, содержащий набор счетчиков со схемой управления и схему сигнализации освобождения регистров общего назначения при выполнении команд процессора, узел прерывания непрерывного потока команд, включающий схему анализа блокировок, не зависящих от обраб атываемых команд, и схему анализа блокировок, обусловленных влиянием команд друг на друга, и буферные регистры для запоминания условий, вызывающих блокировки, подключенные к соответствующим входам первой и второй схем узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСГСО | 1970 |

|

SU287123A1 |

| ПАШИНО-ТЕХНН'-'Р'^Н.АЯБИБЛИОТЕКА | 1971 |

|

SU301703A1 |

| ОБРАБОТКА ТРАНЗАКЦИЙ | 2013 |

|

RU2606878C2 |

65 S1 BJ 66

17

дящих к неправильному выполнению команд, например нарушение расположения информации в памяти в соответствии с граничными условиями (сигнал по шине 158 из блока 29) или нарушение специфических условий, налагаемых на информацию, содержащуюся в компонентах команды (сигнал по шине 159 со схемы 85). В двух последних случаях необходимо перейти к программе отыскания причины нарушения спецификаций.

Схема выработки управляющих сигналов 85 предназначена для управления работой всех перечисленных узлов блока 23 анализа конфликтов. Схема получает информацию о состоянии всех узлов блока 23 и на основании этого выдает совокупность управляющих сигналов. Помимо сигналов, перечисленных при описании узлов, схема 85 получает информацию из блока 29 о состоянии модификатора адреса Э (сигнал по шине 160) и из блока 21 признак обрабатываемой команды по щине 161; и формат обрабатываемой команды по шине 162. Для каждой обрабатываемой в данный момент команды схема 85 проверяет выполнение всех условий, при которых можно выполнить команду, и только в этом случае выдает совокупность управляющих сигналов на те или иные узлы. При невыполнении какого-либо условия схема 85 не выдает управляющих сигналов до тех нор, пока это условие не будет выполнено. Таким образом, схема 85 может приостановить обработку потока команд на время выполнения требуемых условий.

Предмет изобретения

18

буферу записи устройства управления основной оперативно; памятью, отличающийся тем, что, с целью упрощения структуры, сокращения оборудования и повышения быстродейстВИЯ, он содержит в процессоре команд коммутирующую схему передачи команд на декодирование непосредственно из регистров буфера команд, схему быстрой предварительной проверки и схему точной проверки совпадения

адресов ячеек памяти при подготовке операции запоминания с адресом команд, находящихся в буфере команд; схему записи команд непосредственно из информационного буфера записи устройства управления оперативной

памятью при совпадении адреса ячейки памяти, в которую производится запись, с адресом какой-либо команды, хранящейся в буфере команд процессора команд, одновременно с записью в ячейку памяти; раздельные щины передачи запросов на чтение и на запись от процессора команд к устройству управления основной оперативной памятью, причем коммутирующая схема связана с выходами регистров буфера команд, а ее выходы через схеv.y декодирования команд и схему модификации адреса подсоединены ко входам схем быстрой и точной проверки, выход которой подсоединен к схеме записи команд в буфер команд непосредственно из информационного

буфера записи, а также блок анализа конфликтов, связанный со схемами декодирования команд и со схема.ми анализа заполнения магазинов кодов онераций процессоров выполнения операций с фиксированной и плавающей

запятой, со схемой сигнализации освобождения регистров общего назначепия, схемой сигнализации доступности регистров информационного буфера записи устройства управления основной оперативной памятью

при передаче запроса на запись, схемой доступности буферов онерандов процессоров выполнения операций с фиксирова);ной и плавающей запятой, с регистрами арифметики с плавающей запятой и подключенный

управляющими выходами к коммутирующей схеме передачи команд на декодирование, схеме формирования команд для иснолнительных блоков, схеме модификации адреса, магазинам процессоров онераций с фиксированной и

плавающей занятой, схеме формирования запроса, к устройству управления основной оперативной памятью.

а выходы - с входными шинами подключаемого специализировапкого блока обработки.

Авторы

Даты

1971-01-01—Публикация