Изобретение относится к системам обработки данных. В частности, настоящее изобретение относится к системам обработки данных, осуществляющим арифметические операции, способным осуществлять арифметические операции с насыщением.

Многие алгоритмы цифровой обработки сигналов (ЦОС) предусматривают использование так называемой арифметики над Q15 и арифметики над Q31. Число в формате Q15 является обычным 16-разрядным целым числом двоичной арифметики дополнений, но рассматривается как представление этого целого числа, деленного на 215. Поскольку 16-разрядное целое число двоичной арифметики дополнений может представлять числа от -215 до +215-1, то Q15 может представлять числа от -1 до +(1-2-15).

Аналогично, число в формате Q31 является обычным 32-разрядным целым числом двоичной арифметики дополнений, рассматриваемым как частное от деления на 231, и способно представлять числа от -1 до +(1-2-31). Аналогично можно определить (N+1)-разрядные числа в формате QN для любого другого значения N.

Важной особенностью арифметик над Q15 и Q31 является то, что они являются "насыщающими". Если результат соответствующей операции бесконечной арифметики превышает максимальное положительное значение (+1-2-N), то насыщенный результат равен максимальному положительному значению; аналогично, если результат в бесконечной арифметике оказывается меньше -1, то насыщенный результат будет равен -1. Например, в арифметике над Q15, если А=0•8000 (представление -1) и В=0•С000 (представление -0.5), то в результате сложения А и В получится 0•8000 (представление -1), а не результат обычной 16-разрядной двоичной арифметики дополнений, равный 0•4000.

В алгоритмах ЦОС очень часто и с большим успехом применяют операцию "умножение с накоплением", т.е. перемножение двух операндов с последующим сложением с третьим операндом:

Результат = (А*В)+С.

Попытки создания подобных команд умножения с накоплением в арифметике с насыщением (иногда говорят с "ограничением") сталкиваются со значительными проблемами. Особую важность эти проблемы приобретают в случае арифметики над QN.

Чтобы команды различных типов можно было использовать как в варианте с насыщением, так и в варианте без насыщения, требуется достаточно много места под разряды кода операции. Кроме того, когда нужно обеспечить выполнение умножения в течение одного цикла, дополнительно накладываемые требования, связанные с насыщением, и соответствующие корректировки приводят к нежелательному ограничению тактовой частоты за счет команды умножения с насыщением, которая является наихудшим случаем.

В опубликованной британской патентной заявке GB-А2317465 раскрыт сопроцессор, который поддерживает команды умножения с удвоением, позволяющие полностью осуществлять операции умножения с накоплением в формате Q15 в пределах одной команды, например, dest=SAT (асc+SAT(2*scr1*scr2)) с возможностью масштабирования и dest = SAT(асc-SAT(2*scr1*scr2)) с возможностью масштабирования.

Одним аспектом настоящего изобретения является устройство обработки данных, содержащее дешифратор команд, выполненный с возможностью формирования сигналов управления обработкой в соответствии с командными словами обработки данных, и логику обработки, выполненную с возможностью проведения операций обработки данных над словами-операндами данных под управлением упомянутых сигналов управления обработкой, отличающееся тем, что упомянутый дешифратор команд выполнен с возможностью формирования управляющих сигналов для управления упомянутой логикой обработки в соответствии с первым командным словом, чтобы она выполняла операцию обработки данных над первым словом-операндом Р N-разрядных данных и вторым словом-операндом Q N-разрядных данных, формируя результирующее слово R N-разрядных данных, выражаемое в виде:

R=Sat(Fun(P)+Q),

где Sat(X) - функция, возвращающая насыщенное значение X; и

Fun(X) - функция, воздействующая на, по меньшей мере, те значения X, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига для формирования сдвинутого слова и насыщением упомянутого сдвинутого слова.

Изобретение опирается на тот факт, что создание особой команды, позволяющей удовлетворить требованиям, связанным с применением команды умножения с накоплением с насыщением, обеспечивает значительные преимущества. В частности, требования к тактированию для стандартной операции умножения за один цикл, которую желательно использовать, упрощаются за счет корректировок, производимых в связи с особенностями арифметики с насыщением, которая лучше согласуется с циклами, используемыми последующей командой, которая осуществляет операцию накопления. Новая команда также позволяет избавиться от необходимости задавать насыщающие версии нескольких команд умножения и таким образом уменьшить место, занимаемое разрядами кода операции, и другие издержки, необходимые для обеспечения арифметики с насыщением. Наконец, для реализации новой команды требуется лишь небольшой дополнительный объем аппаратного обеспечения по отношению к уже предусмотренному в системе в соответствии с другими аспектами арифметики с насыщением и без насыщения.

Очевидно, что для реализации новой команды можно использовать самые разнообразные аппаратные средства. Различные операции, необходимые для получения в качестве окончательного результата N-разрядного слова данных, можно группировать различными способами и выполнять посредством различных схемных блоков. Все эти разнообразные альтернативы, обеспечивающие получение результирующего N-разрядного слова данных с одним и тем же вышеприведенным окончательным значением с использованием одной команды, представляют собой варианты осуществления настоящего изобретения.

Помимо вышеописанной команды, предназначенной для использования в операциях умножения с накоплением с насыщением, можно аналогичным образом создать аналогичные команды, обеспечивающие операции умножения с декрементом с насыщением.

В командах, отвечающих изобретению, можно использовать сдвиг той или иной величины. Однако особенно полезно применять такой сдвиг, чтобы сдвинутое слово вдвое превосходило первое слово-операнд Р N-разрядных данных.

При осуществлении целочисленного умножения двух чисел в формате Q15 результат, полученный нормальным путем, представляет собой 32-разрядное число в формате "квази-Q30", которое можно рассматривать как элемент арифметики дополнений, сопоставляемый обычному 32-разрядному значению со знаком, деленному на 230, и таким образом представляющий число от -2 до +(2-2-30). Число в формате квази-Q30 можно также рассматривать как знаковое 32-разрядное число с фиксированной запятой с 30 двоичными разрядами. Однако в таких обстоятельствах для дальнейшей обработки требуется число в формате Q31. Чтобы решить эту проблему, можно после стандартной команды целочисленного умножения выполнить команду, отвечающую изобретению, и выполнить сдвиг на величину, обеспечивающую удвоение результата целочисленного умножения для перевода полученного значения из формата квази-Q30 в формат Q31, а затем перейти к операции насыщения и операции накопления или декремента. Таким образом, одну из проблематичных корректировок, необходимых для поддержки арифметики с насыщением, можно обеспечить путем корректировки результата целочисленного умножения, осуществляемой в рамках последующей команды, вместо того, чтобы ждать окончания цикла умножения.

Для осуществления насыщения можно использовать логические схемы самых разных видов. Однако согласно предпочтительным вариантам осуществления изобретения насыщение упомянутого сдвинутого слова предусматривает проверку наличия определенных характеристик упомянутого первого слова-операнда Р N-разрядных данных и в случае наличия таковых - замену упомянутого сдвинутого значения соответствующим граничным значением диапазона разрешенных значений.

Эта особенность основана на том, что в некоторых обстоятельствах для обеспечения насыщения можно проверять характеристики первого слова-операнда Р N-разрядных данных, поскольку возможности манипуляции, которой его надлежит подвергнуть, довольно ограничены и потому обстоятельства, при которых может возникнуть переполнение или антипереполнение (потеря значащих разрядов), что обуславливает необходимость в насыщении, можно проверять специально и таким образом снизить требования к аппаратному обеспечению в целом.

В частности, когда применение сдвига приводит к удвоению первого слова-операнда Р N-разрядных данных, существует весьма простой способ установления необходимости насыщения, заключающийся в сравнении двух старших разрядов первого слова-операнда Р N-разрядных данных.

По сравнению со сравнительно ограниченным диапазоном обстоятельств, возникающих в ходе выполнения команды Fun(X), при которых возможно переполнение или антипереполнение, при выполнении функции Sat(X) переполнение или антипереполнение может возникать в большем количестве случаев и потому предпочтительные варианты осуществления изобретения предусматривают, что Sat(X) в целях формирования упомянутого результирующего слова R N-разрядных данных предусматривает проверку, лежит ли Х вне диапазона разрешенных значений, и в случае обнаружения этого факта - замену Х соответствующим граничным значением упомянутого диапазона разрешенных значений.

Хотя новые команды, отвечающие настоящему изобретению, сами по себе обладают преимуществами, они, как было отмечено выше, особенно пригодны для вариантов осуществления, предусматривающих наличие умножителя для выполнения второго командного слова, которое формирует первое слово-операнд N-разрядных данных, перемножая третье слово-операнд A N/2-разрядных данных и четвертое слово-операнд В N/2-разрядных данных.

Команды, отвечающие изобретению, можно применять к операндам любого рода. Однако команда особенно полезна применительно к вариантам осуществления, согласно которым упомянутое первое слово-операнд Р N-разрядных данных, упомянутое второе слово-операнд Q N-разрядных данных и упомянутое результирующее слово R N-разрядных данных являются словами знаковых данных с фиксированной запятой, причем запятая находится непосредственно справа от позиции старшего разряда, так что -1≤Р≤+1, -1≤Q<+1 и -1≤R<+1 и область определения Sat(X) отвечают условию -1≤Х<+1.

Согласно рассмотренному выше для использования таких операндов в формате QN требуются операции корректировки и насыщения, которые могут эффективно обеспечиваться за счет выполнения команд, отвечающих изобретению, не оказывая чрезмерного воздействия на остальную систему обработки данных.

Наиболее часто используют те значения первого слова-операнда Р N-разрядных данных, которые можно получить умножением со знаком N/2-разрядного целого на N/2-разрядное целое. Однако предпочтительные варианты осуществления изобретения предусматривают расширение сферы применения Fun(X), допуская ее использование при осуществлении сдвига и насыщения всех возможных N-разрядных значений X.

Изобретение можно использовать в системах, в которых N принимает те или иные значения. Однако для осуществления операций ЦОС того типа, для которого изобретение особенно полезно, обычно требуются определенные значения N, например N=32.

Хотя очевидно, что изобретение можно реализовать в виде системы, содержащей дискретные компоненты, весьма предпочтительно, чтобы устройство обработки данных было реализовано на основе интегральных схем.

Другим аспектом настоящего изобретения является способ обработки данных в устройстве обработки данных, согласно которому в соответствии с командными словами обработки данных формируют сигналы управления обработкой и выполняют операции обработки данных над словами-операндами данных под управлением упомянутых сигналов управления обработкой; отличающийся тем, что в соответствии с первым командным словом формируют управляющие сигналы для управления логикой обработки, чтобы она выполняла операцию обработки данных над первым словом-операндом Р N-разрядных данных и вторым словом-операндом Q N-разрядных данных, чтобы сформировать результирующее слово R N-разрядных данных, выражаемое в виде:

R=Sat(Fun(Р)+Q),

где Sat(X) - функция, возвращающая насыщенное значение X; и

Fun(X) - функция, воздействующая на, по меньшей мере, те значения X, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

Предусмотрены также дополнительные аспекты способа, согласно которым команда выполняет операцию вычитания, а не сложения.

Ниже, исключительно в качестве примера, описан вариант осуществления изобретения со ссылками на прилагаемые чертежи, в которых:

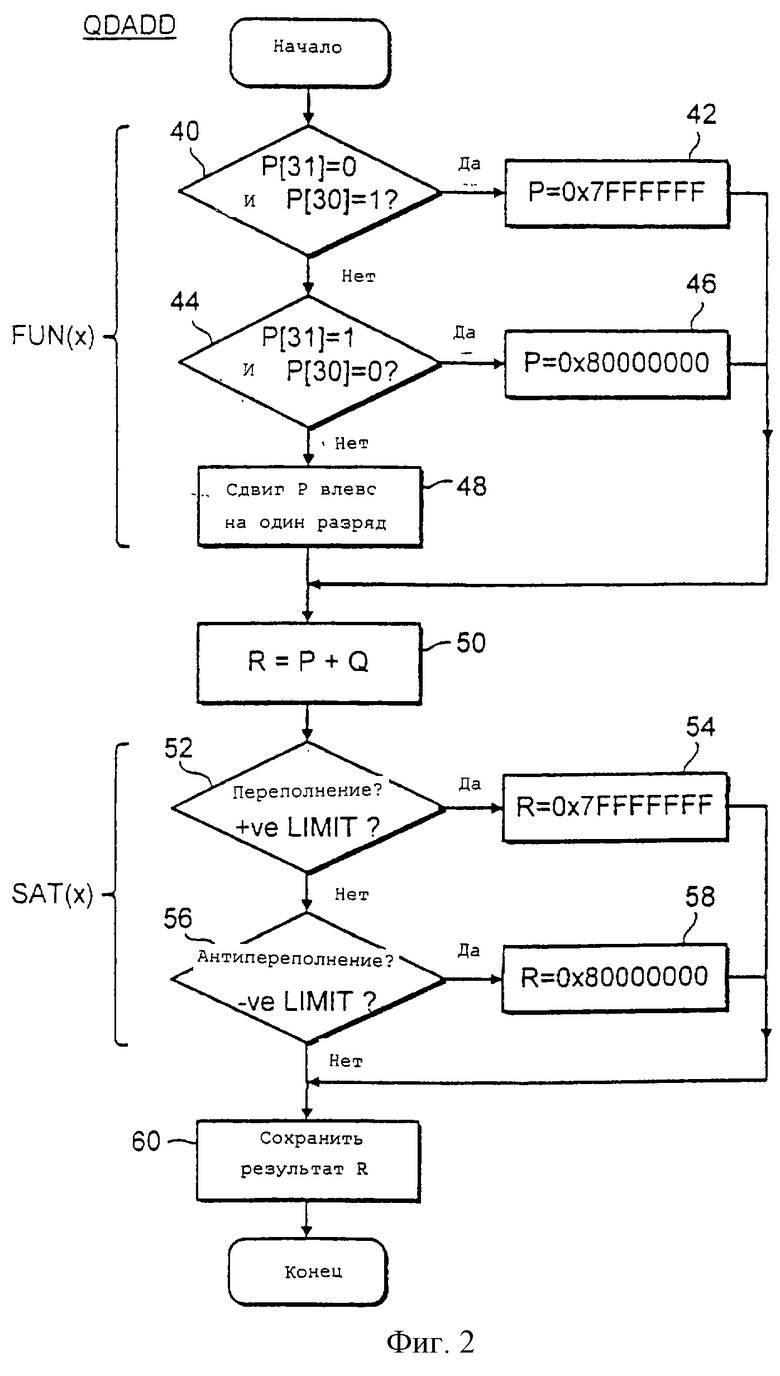

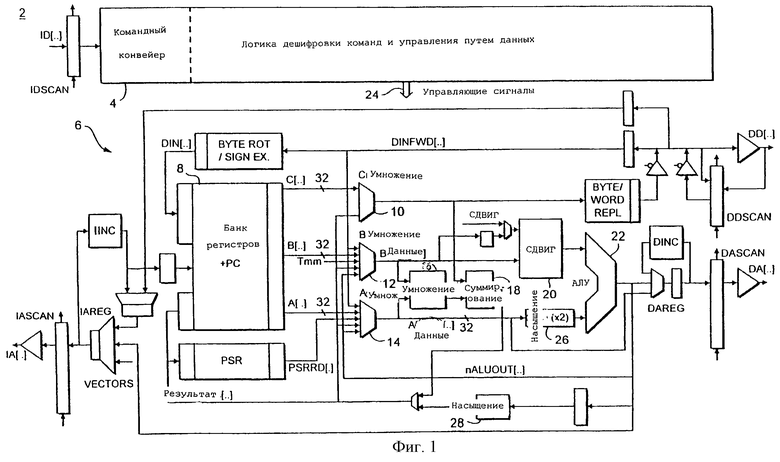

фиг. 1 - схема дешифратора команд и логики обработки в интегральной схеме; и

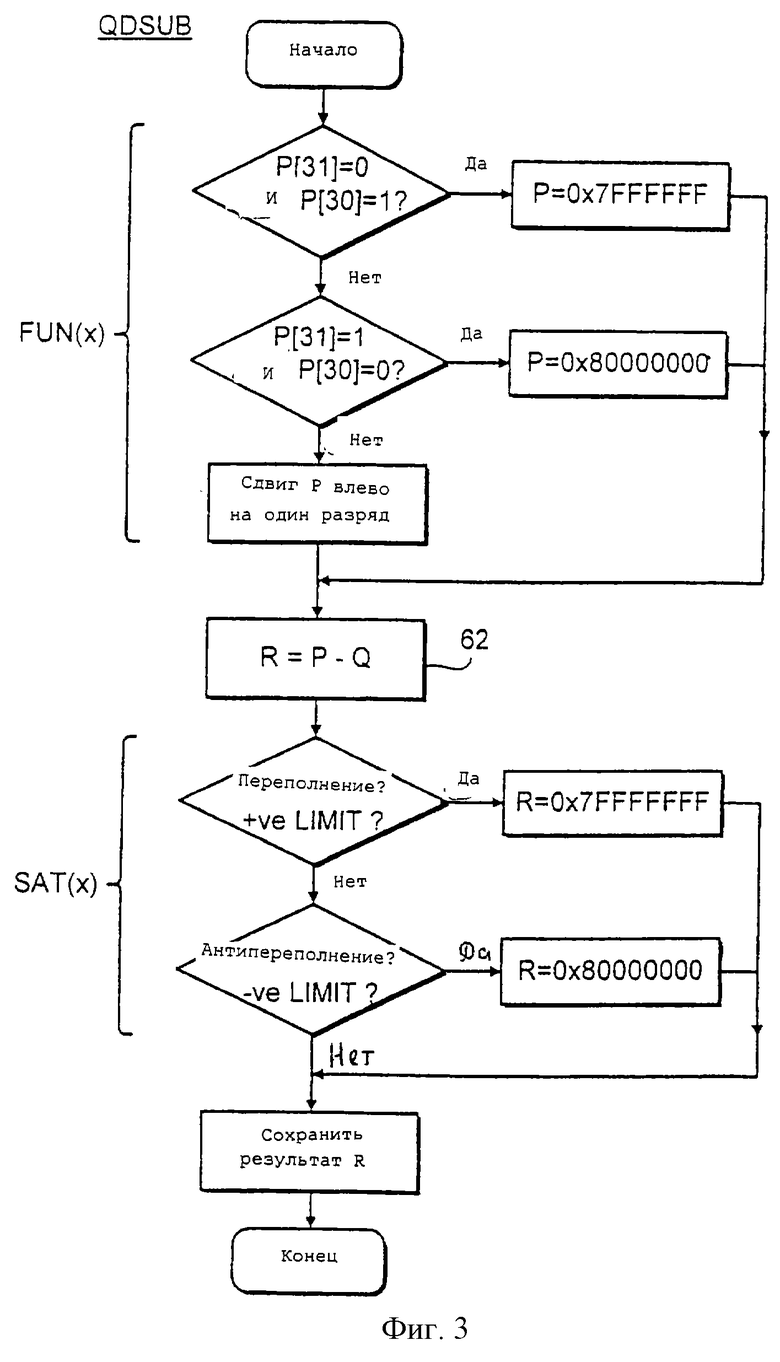

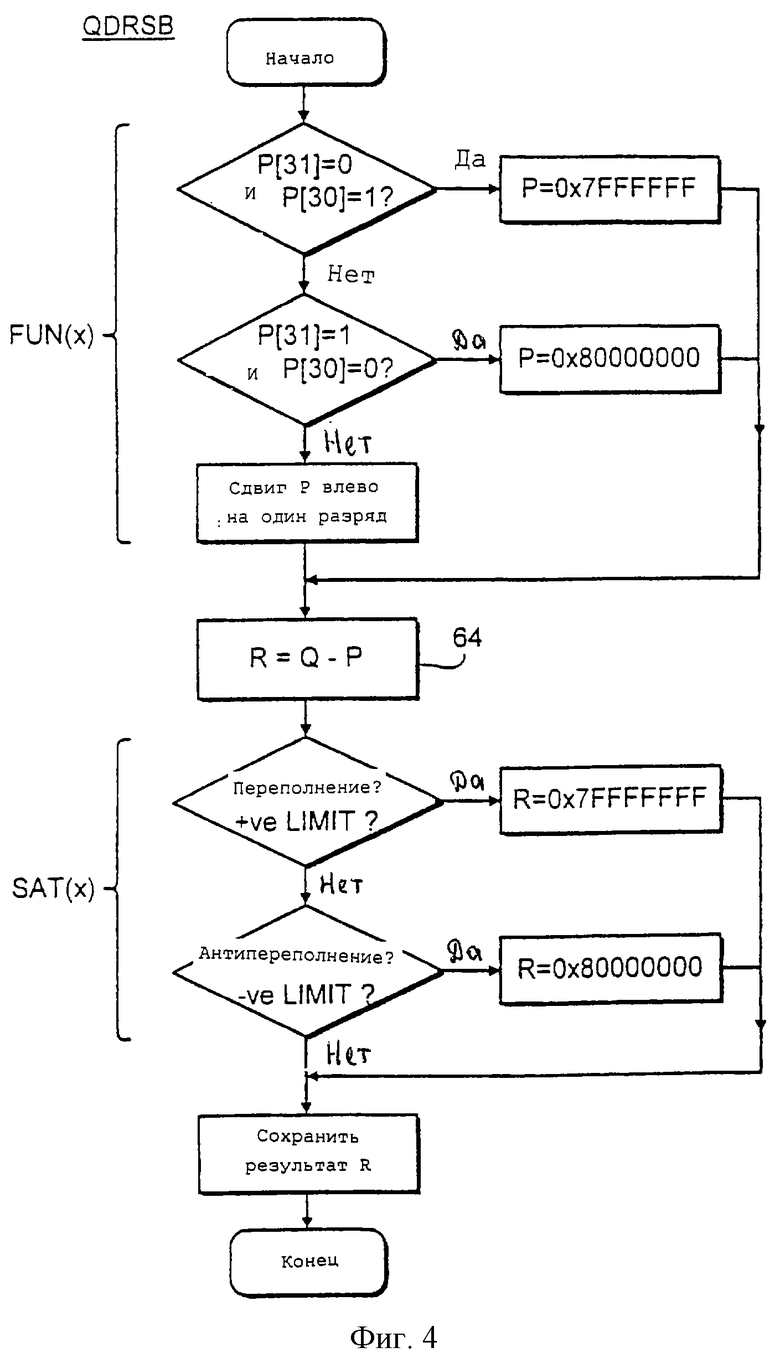

фиг. 2, 3 и 4 - блок-схемы, иллюстрирующие порядок выполнения команд, предусмотренных для поддержки арифметики с насыщением.

На фиг. 1 показана часть интегральной схемы 2 (аналогичная части микропроцессора ARM9TDMI, производимого ARM Limited, Кембридж, Великобритания), содержащая дешифратор 4 команд и логику 6 обработки. Логика 6 обработки образована большим количеством разнообразных отдельных функциональных элементов. В банке 8 регистров хранятся слова-операнды данных (P, Q), подлежащие манипулированию. Эти слова можно считывать из банка 8 регистров и подавать через мультиплексоры 10, 12, 14 на разные другие блоки обработки, входящие в состав логики 6 обработки. Целочисленный умножитель 16 предусмотрен для осуществления среди других функций целочисленного умножения со знаком. Сумматор 18 предусмотрен для осуществления операций умножения с накоплением без насыщения и для преобразования результата умножения из формата переноса с сохранением в формат дополнения до двойки. Предусмотрены также элемент сдвига 20 и арифметико-логическое устройство 22. Вышеупомянутые основные компоненты логики 6 обработки, в целом, известны. Управляющие сигналы дешифратора 4 команд подают на различные элементы логики 6 обработки для управления и согласования их работы. В частности, когда дешифратор команд дешифрует команды, выдаваемые им управляющие сигналы 24 переключают различные мультиплексоры, входящие в состав логики 6 обработки, для выбора нужного пути данных, а также активируют и настраивают различные блоки обработки, входящие в состав логики 6 обработки, для осуществления операции, заданной дешифрованной командой. Для простоты линии сигнализации, связывающие отдельные компоненты с дешифратором команд, на схеме не изображены.

В целях обеспечения дополнительных команд (QDADD, QDSUB и QDRSB) (команда сложения, команда вычитания и команда обращенного вычитания) для арифметики с насыщением предусмотрен блок 26 сдвига и насыщения, расположенный по ходу обработки выше арифметико-логического устройства 22, а также предусмотрен блок 28 полного насыщения, расположенный на пути обратной связи с банком 8 регистров, на следующем каскаде конвейерной обработки после того, на котором действует арифметико-логическое устройство 22. В ходе работы блок 26 сдвига и насыщения сначала проверяет тот факт, что два старших разряда поступившего на него 32-разрядного слова данных не равны друг другу. При выполнении этого условия сдвиг влево на один разряд приведет к переполнению или антипереполнению, если поступившее слово данных представляет слово в формате квази-Q30, которое подлежит преобразованию в слово в формате Q31 путем сдвига влево. Если два старших разряда равны '01', то блок 26 сдвига и насыщения выводит значение 0•7FFFFFFF, представляющее максимальное граничное значение диапазона разрешенных значений. Аналогично, если два старших разряда равны '10', то блок 26 сдвига и насыщения выводит значение 0•80000000, представляющее минимальное граничное значение диапазона разрешенных значений. Если не выполнено ни одно из этих условий, то блок 26 сдвига и насыщения осуществляет сдвиг влево поступившего значения двоичных данных на один разряд, что соответствует удвоению этого значения и таким образом преобразует представление квази-Q30, полученное целочисленным умножением числа в формате Q15 на число в формате Q15, в представление Q31, которое требуется для дальнейшей обработки (например, накопления) и насыщения.

Блок 26 сдвига и насыщения снабжен обходным маршрутом, что позволяет отключать его в соответствии с определенным управляющим сигналом 24, поступающим от дешифратора 4 команд, когда та или иная дешифрованная команда не требует этой операции. Блок 26 сдвига и насыщения размещается на шине А и эта шина обычно меньше ограничена по тактированию, чем шина В, поскольку шина В содержит элемент сдвига 20.

Соответственно, блок 26 сдвига и насыщения не вызывает никаких значительных дополнительных проблем, связанных с тактированием.

Блок 28 полного насыщения предусмотрен на пути обратной связи и используется после того, как арифметико-логическое устройство 22 произведет необходимую операцию сложения или вычитания. Блок 28 полного насыщения может действовать в соответствии с известными принципами для обнаружения переполнения или антипереполнения знакового результата, полученного на арифметико-логическом устройстве 22, и корректировки его до соответственно максимального или минимального граничного значения диапазона разрешенных значений. Подобно блоку 26 сдвига и насыщения блок 28 полного насыщения снабжен обходным маршрутом, что позволяет отключать его при наличии соответствующего управляющего сигнала 24, когда это насыщение не требуется. Поскольку блок 28 полного насыщения находится в каскаде конвейерной обработки, который обычно не влияет на выполнение команд сложения и вычитания, его работа не добавляет никаких проблем, связанных с тактированием. Однако он требует блокировки процессора в течение одного цикла, если результат команды насыщения сразу используется следующей командой. Этой блокировкой можно управлять наподобие того, как управляют блокировками, генерируемыми на многих микропроцессорах, когда значение, загруженное командой загрузки, сразу используется следующей командой.

В ходе работы в целом для того, чтобы выполнять умножение в формате Q15 совместно с операцией накопления в формате Q31, обработку осуществляют следующим образом. Сначала из банка 8 регистров считывают значения в формате Q15 на шину А и шину В и подают на вход одноциклового целочисленного умножителя 16. Результат в формате квази-Q30 направляют обратно в банк 8 регистров. На следующем цикле обработки выполняют одну из новых команд (например, команду QDADD), согласно которой результат умножения в формате квази-Q30 считывают на шину А, а накопленное значение в формате Q31 - на шину В. Затем значение в формате квази-Q30 подвергают сдвигу влево на один разряд или насыщению на блоке 26 сдвига и насыщения и подают его выходные данные на один вход арифметико-логического устройства 22. Значение в формате Q31 подают из шины В на другой вход арифметико-логического устройства 22, используя при этом соответствующие управляющие сигналы 24, в соответствии с которыми элемент сдвига 20 не осуществляет сдвиг на поступившем на него значении. Блок 26 сдвига и насыщения приводит значение из формата квази-Q30 к требуемому формату Q31, после чего скорректированное значение суммируется со значением в формате Q31, поступившее из шины В, на арифметико-логическом устройстве 22. Выходные данные арифметико-логического устройства 22 поступают на блок 28 полного насыщения, где подвергаются насыщению в формате Q31 при наличии флагов переполнения и антипереполнения и выполнении других стандартных условий в выходных данных арифметико-логического устройства 22, после чего направляются обратно на хранение в банк 8 регистров. Арифметико-логическое устройство 22 вместо того, чтобы выполнять сложение, может под управлением соответствующих управляющих сигналов 24 вычитать значение шины А из значения шины В в рамках команды QDRSB или вычитать значение шины В из значения шины А в рамках команды QDSUB. Настройку блока арифметической логики на осуществление операций вычитания посредством соответствующих управляющих сигналов 24, поступающих от дешифратора команд, можно реализовать разными стандартными способами.

Из вышесказанного следует, что операции, выполняемые в рамках команд QDADD, QDSUB и QDRSB, распределяются разными способами между различными функциональными блоками логики обработки. Специалистам в данной области понятно, что распределение этих операций между различными блоками можно осуществлять многими разными способами, но тем не менее получать один и тот же конечный результат.

На фиг. 2 показана блок-схема, иллюстрирующая этапы обработки, осуществляемые в рамках команды QDADD. На этапе 40 производится проверка, равны ли два старших разряда первого слова-операнда 32-разрядных данных '01'. Если это имеет место, то сдвиг влево на один разряд приведет к переполнению и соответственно на этапе 42 операнду присваивается максимальное разрешенное положительное значение (+1-2-31). Аналогично, на этапе 44 производится проверка, равны ли два старших разряда '10', в каковом случае сдвиг влево приведет к антипереполнению. При выполнении этого условия на этапе 46 операнду присваивается минимальное разрешенное значение -1.

Если не выполнено ни условие переполнения, ни условие антипереполнения, то на этапе 48 осуществляется сдвиг влево на один разряд первого слова-операнда 32-разрядных данных, т.е. преобразование из формата квази-Q30 в формат Q31, если это то, что представляет число. Операции, осуществляемые на этапах 40-48, соответствуют функциям, выполняемым блоком 26 сдвига и насыщения, и вышеописанной функции Fun(X).

На этапе 50 осуществляется сложение. Это сложение соответствует сложению, осуществляемому арифметико-логическим устройством 22, изображенным на фиг.1.

На этапах 52 и 54 производится обнаружение и устранение переполнения в насыщенном значении, полученном на этапе 50 сложения. Аналогично, выполнение этапов 56 и 58 устраняет антипереполнение. Если не обнаружено ни переполнения, ни антипереполнения, никакой корректировки не производится. На этапе 60 результат R команды QDADD поступает на хранение обратно в банк 8 регистров.

Операции, осуществляемые на этапах 52-58, соответствуют операциям, выполняемым блоком 28 полного насыщения, изображенным на фиг.1, и вышеописанной функции Sat(X).

На фиг. 3 показана аналогичная блок-схема, но применительно к команде QDSUB. В этой команде этап 50, обозначенный на фиг.2, заменен этапом 62, на котором второе слово-операнд Q 32-разрядных данных вычитают из сдвинутого и насыщенного первого слова-операнда Р.

Фиг. 4 аналогична фиг.3 за исключением того, что порядок вычитания, которое осуществляется на этапе 62, обозначенном на фиг.3, заменен обратным на этапе 64, обозначенном на фиг.4.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДРЕСАЦИЯ РЕГИСТРОВ В УСТРОЙСТВЕ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2193228C2 |

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НАБОРОВ КОМАНД | 1995 |

|

RU2137183C1 |

| ЦЕЛОЧИСЛЕННОЕ УМНОЖЕНИЕ ВЫСОКОГО ПОРЯДКА С ОКРУГЛЕНИЕМ И СДВИГОМ В АРХИТЕКТУРЕ С ОДНИМ ПОТОКОМ КОМАНД И МНОЖЕСТВОМ ПОТОКОВ ДАННЫХ | 2003 |

|

RU2263947C2 |

| ОТОБРАЖЕНИЕ С ПОМОЩЬЮ МУЛЬТИНАБОРОВ КОМАНД | 1995 |

|

RU2137184C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ОБЪЕДИНЕНИЯ ДАННЫХ СО СДВИГОМ ВПРАВО | 2002 |

|

RU2273044C2 |

| ФЛАГИ КОДА УСЛОВИЯ ДЛЯ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2181214C2 |

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179333C1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

Изобретение относится к системам обработки данных, которые осуществляют арифметические операции. Техническим результатом является упрощение тактирования операции умножения за один цикл, уменьшение объема памяти за счет исключения необходимости задания насыщающих версий нескольких команд умножения. Технический результат достигается за счет того, что устройство содержит средство логической обработки, дешифратор команд, который управляет средством логической обработки, которое выполняет операцию обработки данных над первым словом-операндом Р N-разрядных данных и вторым словом-операндом Q N-разрядных данных для формирования результирующего слова R N-разрядных данных. Способ включает в себя следующие операции: формируют сигналы управления обработкой, выполняют операции обработки данных над словами-операндами данных под управлением упомянутых сигналов управления, в соответствии с первым командным словом формируют управляющие сигналы для управления средством логической обработки, чтобы это средство выполняло операцию обработки данных над первым словом-операндом Р N-разрядных данных и вторым словом-операндом Q N-разрядных данных для формирования результирующего слова R N-разрядных данных. 6 с. и 9 з.п.ф-лы, 4 ил.

R=Sat(Fun(P)+Q),

где Sat (X) – функция, возвращающая насыщенное значение Х;

Fun (Х) - функция, воздействующая на, по меньшей мере, те значения Х, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

R=Sat(Fun(P)–Q),

где Sat (Х) – функция, возвращающая насыщенное значение Х;

Fun (Х) – функция, воздействующая на, по меньшей мере, те значения Х, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

R=Sat(Q–Fun(P)),

где Sat (Х) – функция, возвращающая насыщенное значение Х;

Fun (Х) - функция, воздействующая на, по меньшей мере, те значения Х, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

R=Sat(Fun(P)+Q),

где Sat(Х) – функция, возвращающая насыщенное значение Х;

Fun(Х) - функция, воздействующая на, по меньшей мере, те значения Х, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

R=Sat(Fun(P)–Q),

где Sat (Х) – функция, возвращающая насыщенное значение Х;

Fun(X) – функция, воздействующая на, по меньшей мере, те значения Х, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

R=Sat(Q–Fun(P)),

где Sat(X) – функция, возвращающая насыщенное значение Х;

Fun(Х) – функция, воздействующая на, по меньшей мере, те значения Х, которые могут быть получены умножением со знаком N/2-разрядного числа на N/2-разрядное число, и возвращающая значение, полученное сдвигом Х на некоторую величину сдвига, для формирования сдвинутого слова, и насыщением упомянутого сдвинутого слова.

| US 5652910 A, 29.07.1997 | |||

| САЛЬНИКОВЫЙ УЗЕЛ | 2005 |

|

RU2317465C2 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2047896C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

Авторы

Даты

2004-03-10—Публикация

1999-05-26—Подача