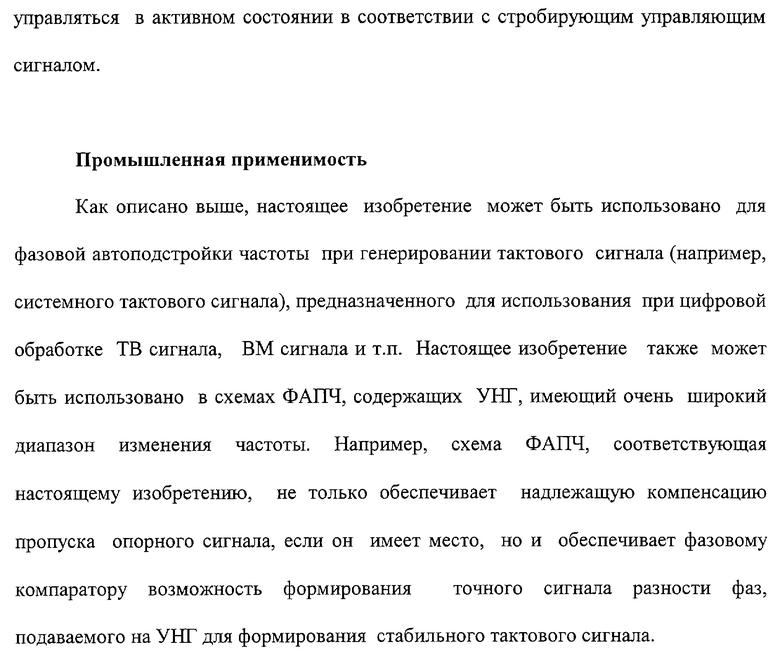

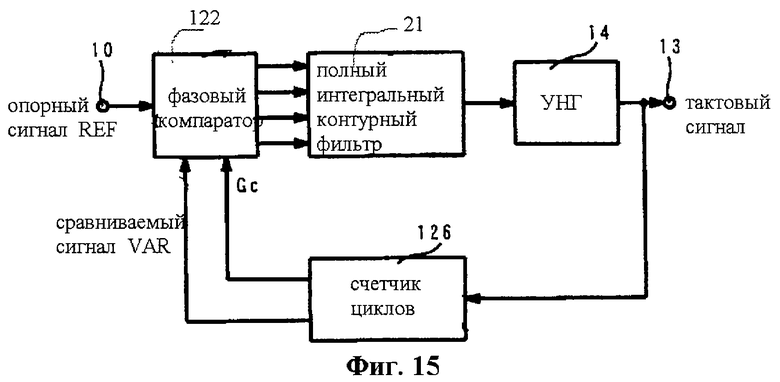

Изобретение относится к радиотехнике и может быть использовано для формирования тактового сигнала для цифровой обработки видеосигнала от станции телевизионного вещания. Схема ФАПЧ содержит фазовый компаратор, контурный фильтр, управляемый напряжением генератор и счетчик циклов, а также схему окна прогнозирования, которая вырабатывает сигнал HWIN для прогнозирования положений, где возникают сигналы REF, и схему компенсации пропусков, которая обнаруживает потери сигнала REF в сигнале HWIN и генерирует сигнал d.REFX для компенсации потери и сигнал d.VARX для компенсации разности фаз между сигналом сравнения VAR и d.REFX. Технический результат заключается в компенсации пропуска опорного сигнала при его наличии и формирование точного сигнала разности фаз, подаваемого на управляемый генератор для формирования стабильного тактового сигнала. 2 с. и 17 з.п. ф-лы, 20 ил.

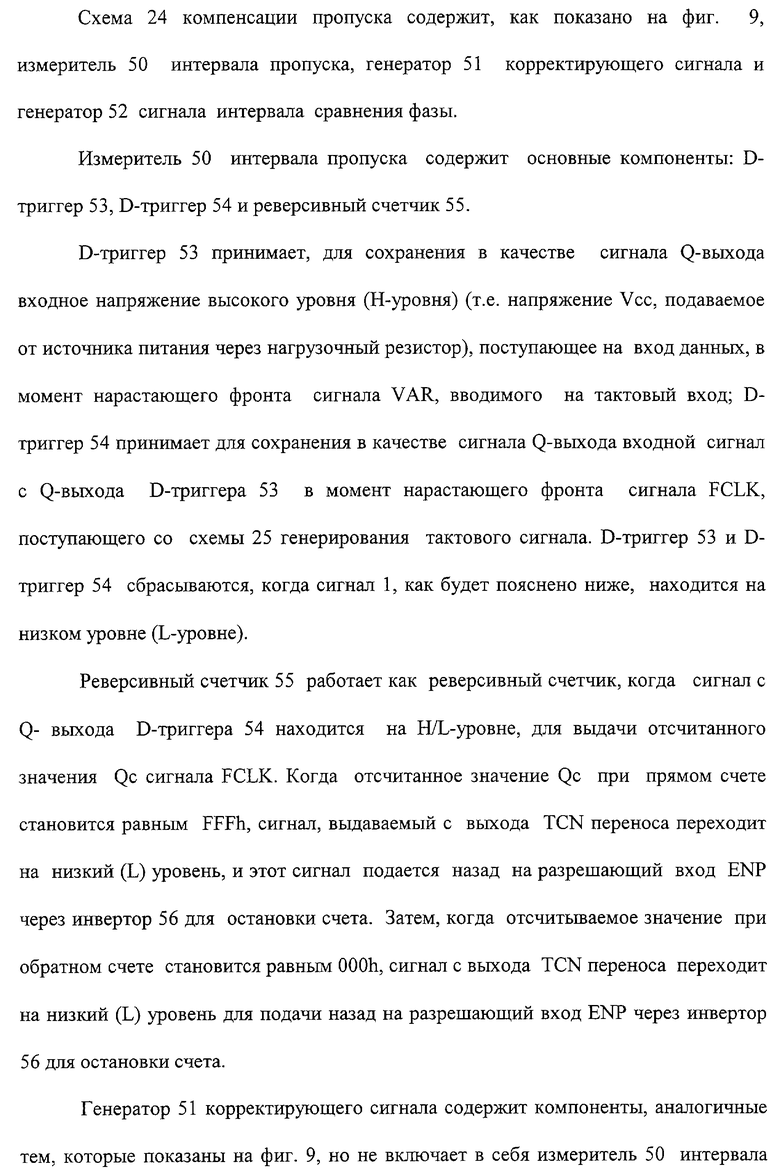

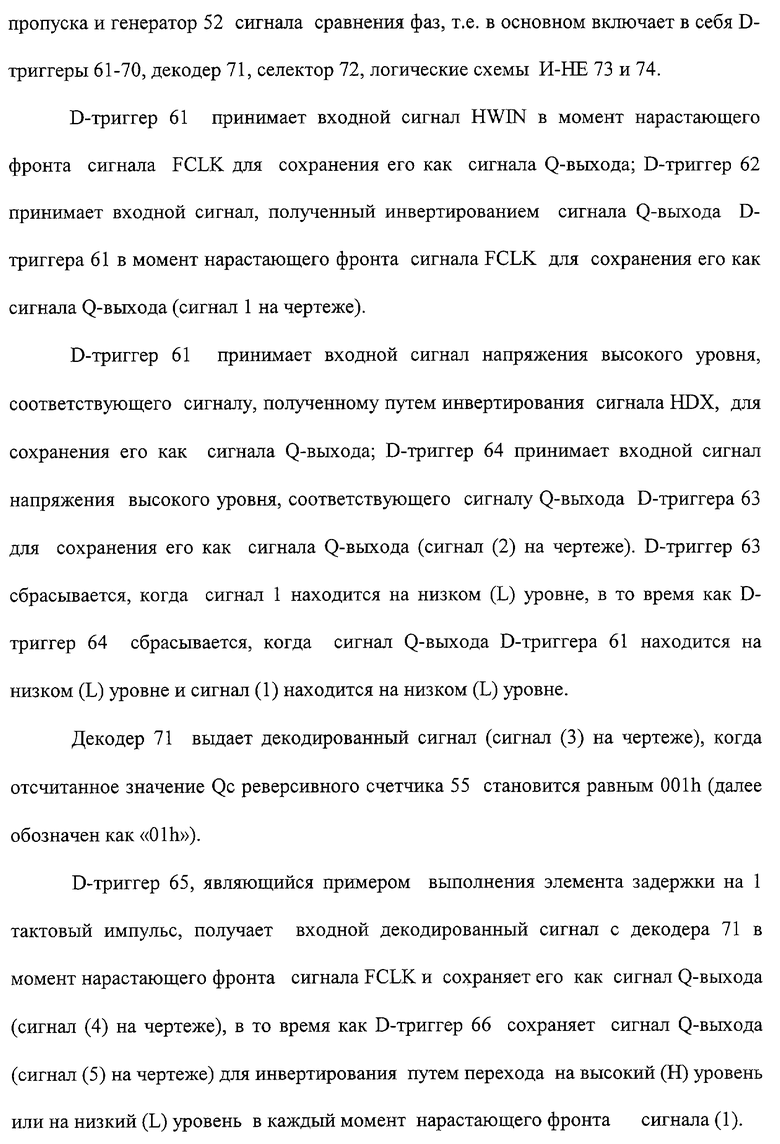

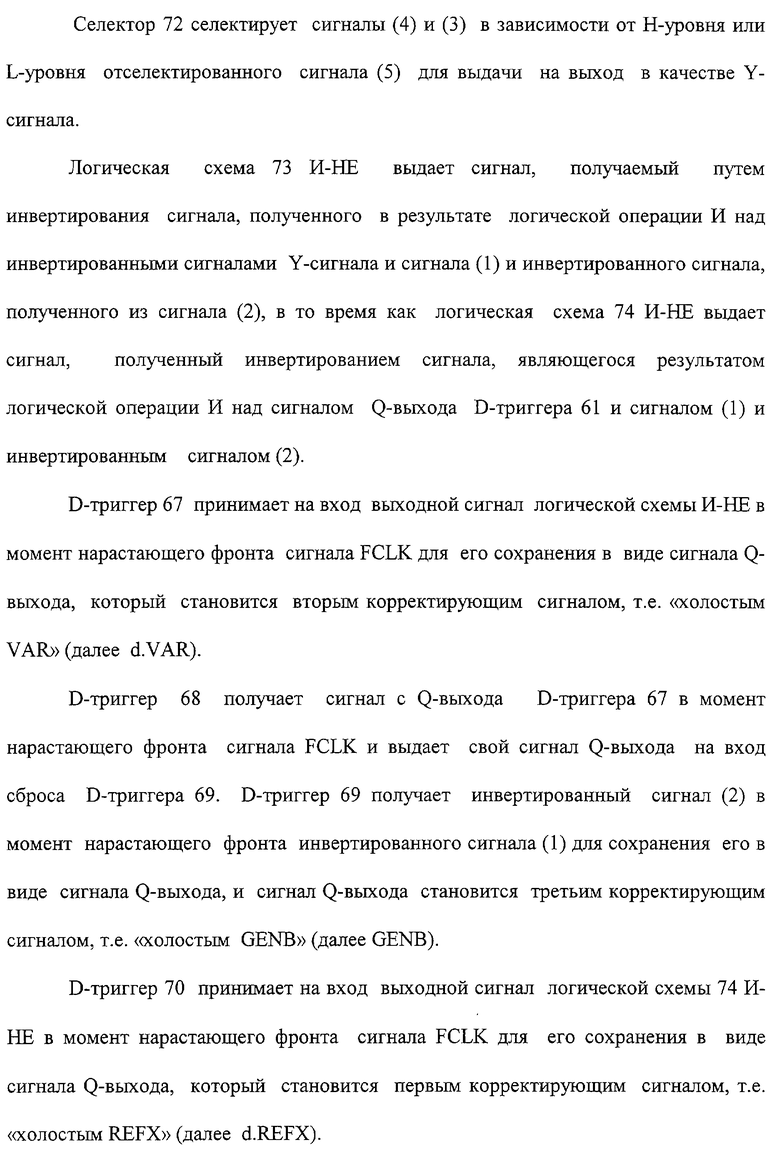

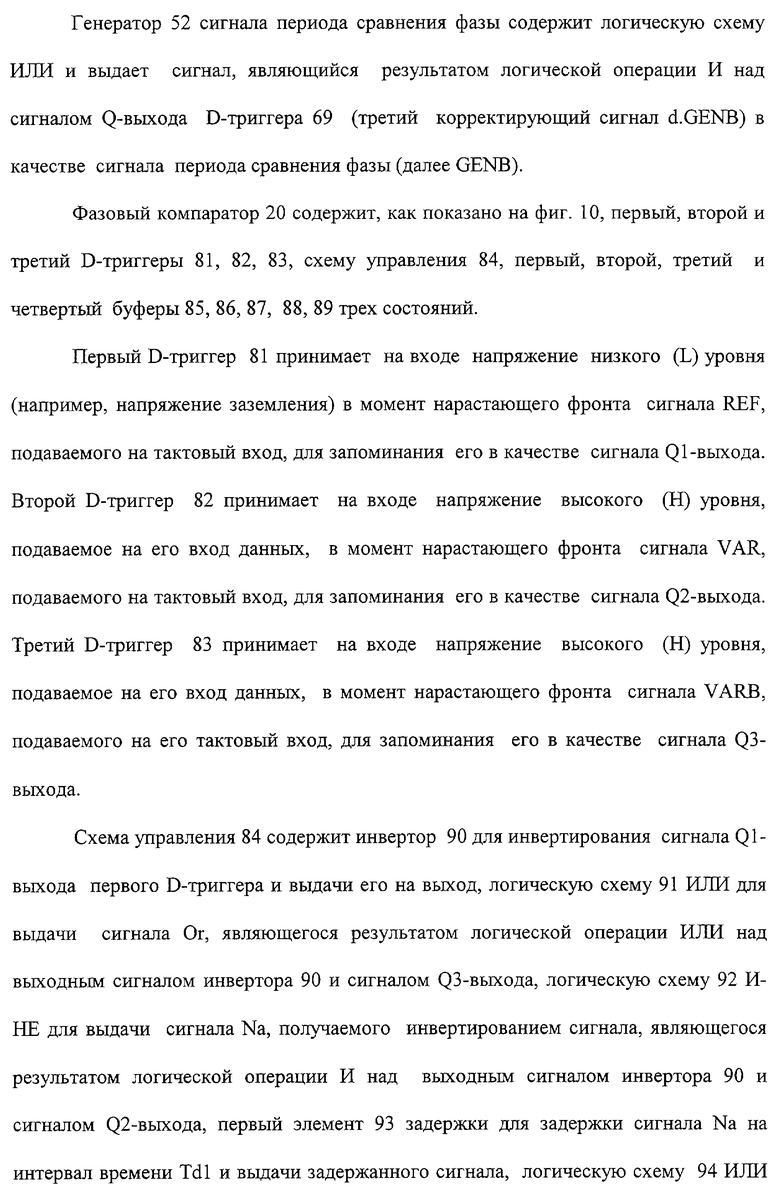

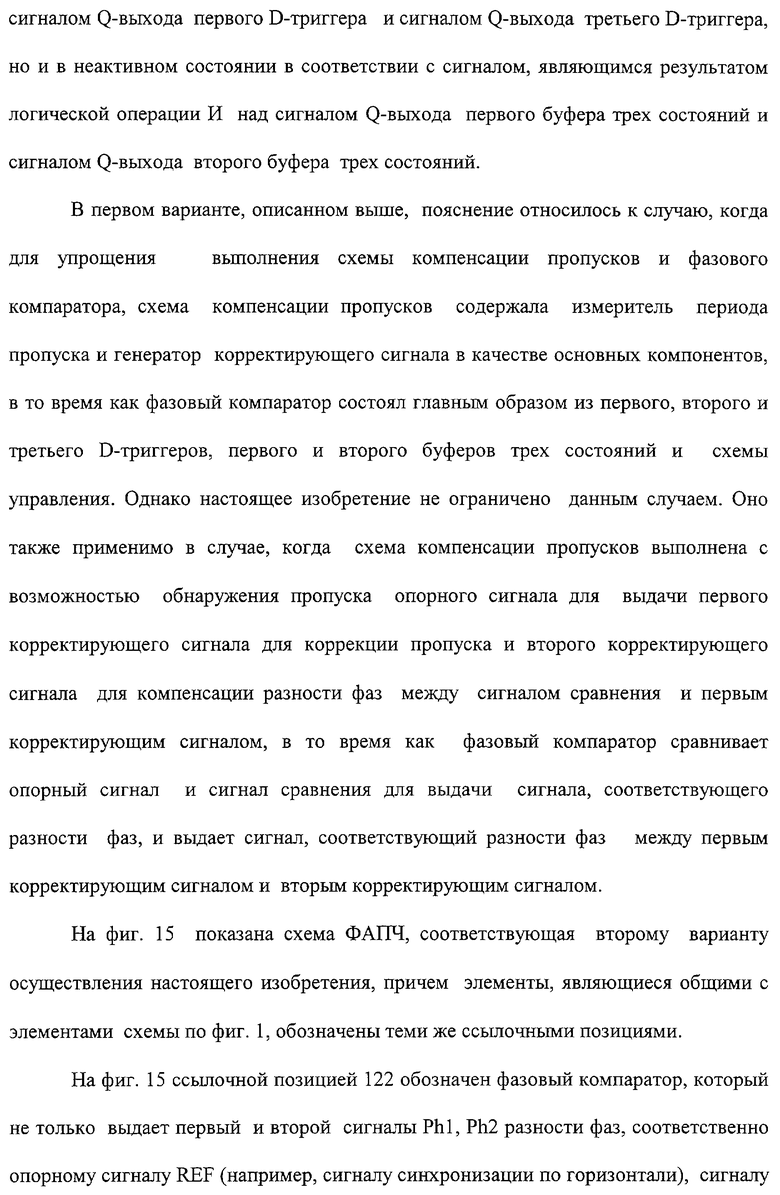

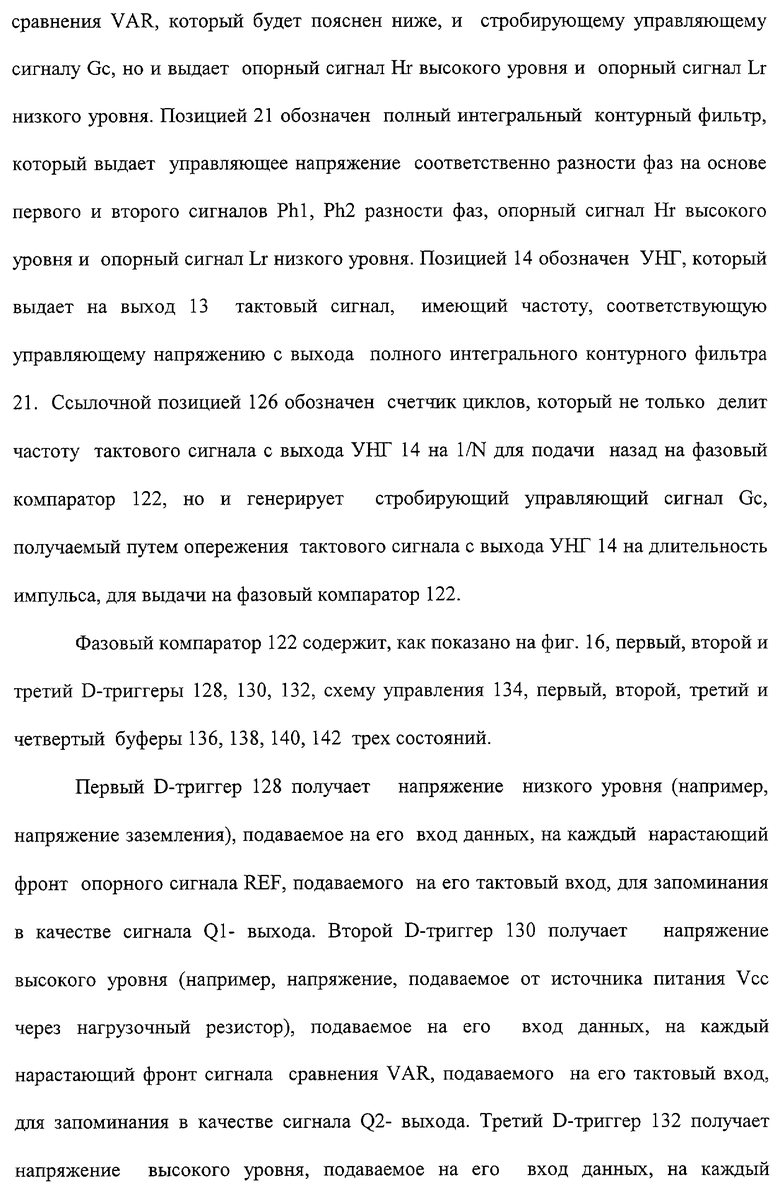

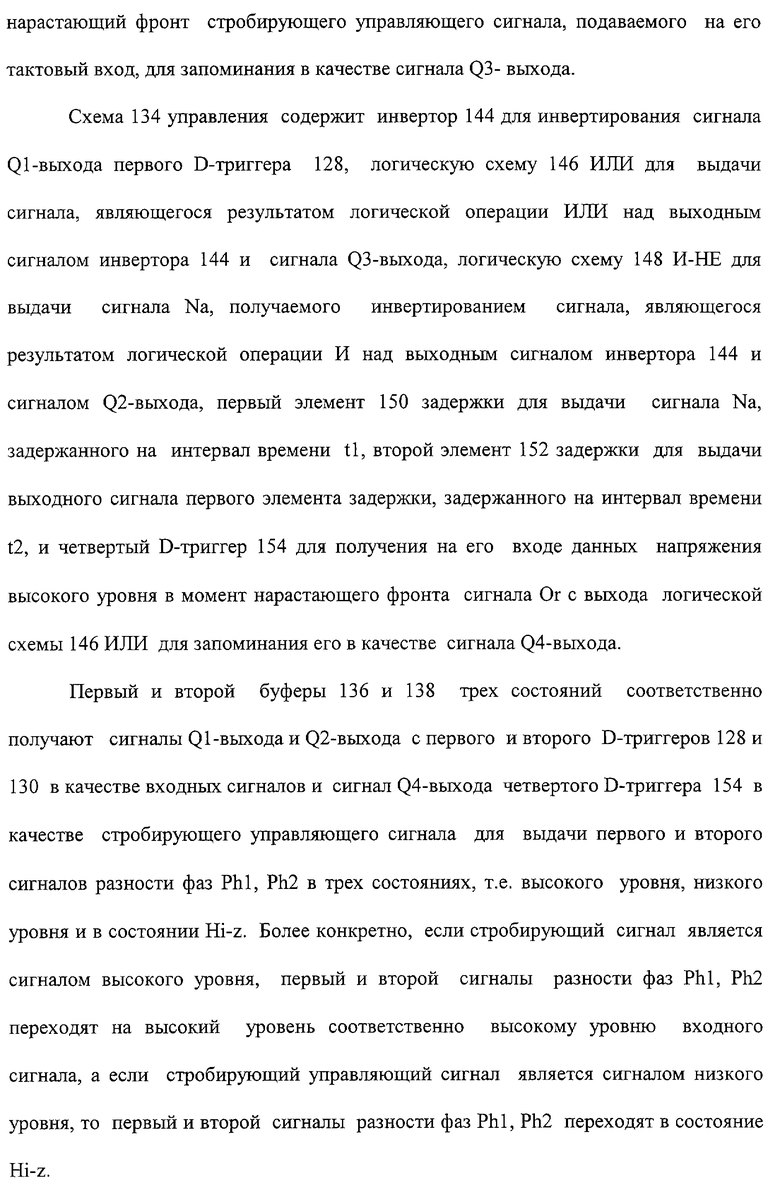

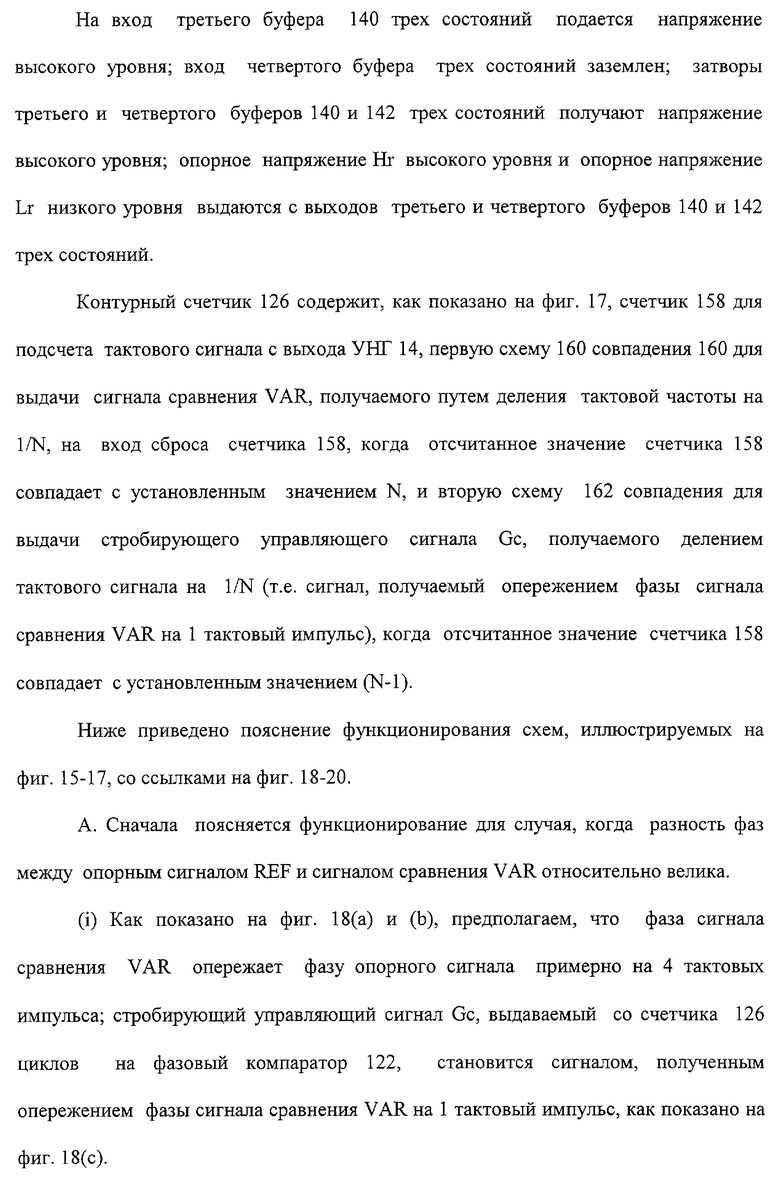

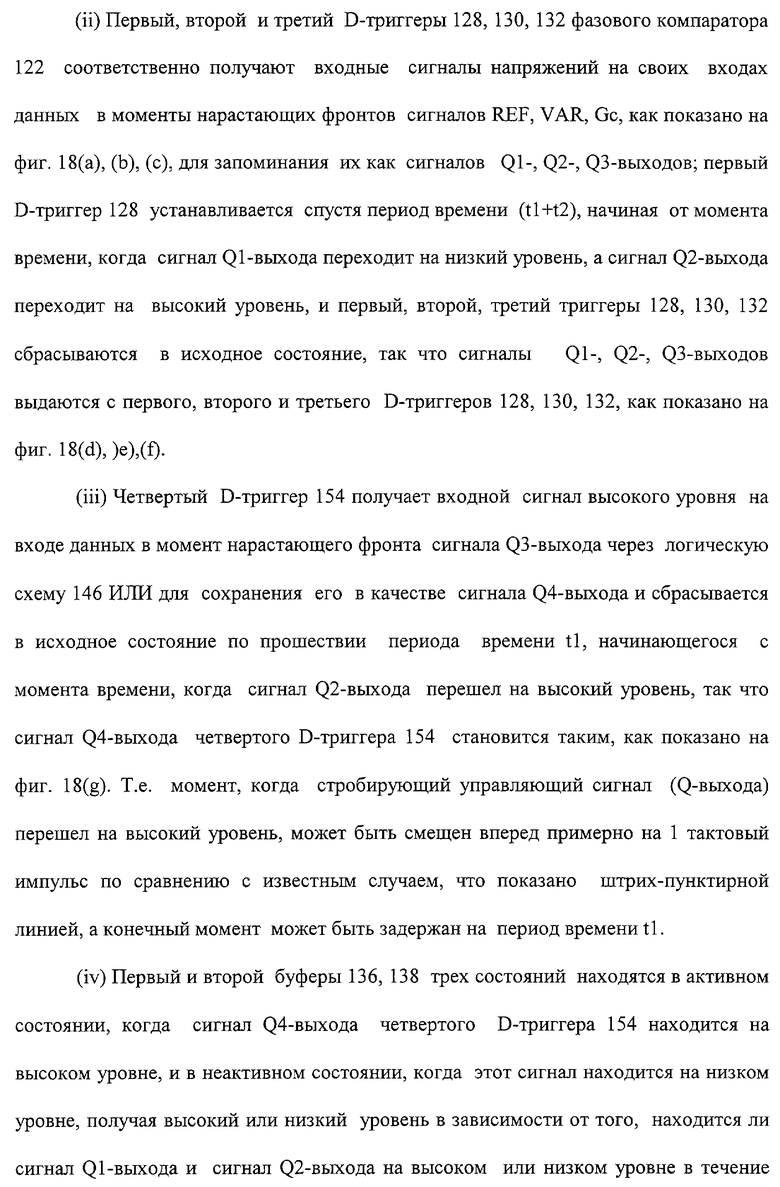

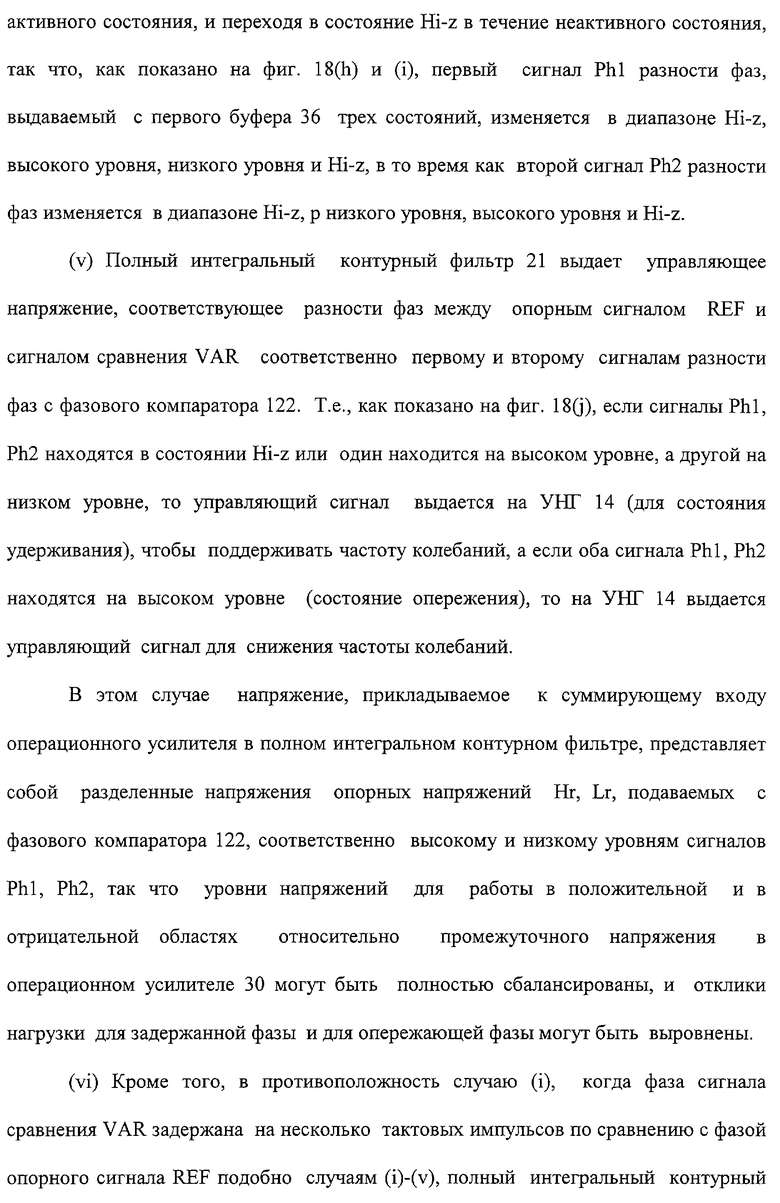

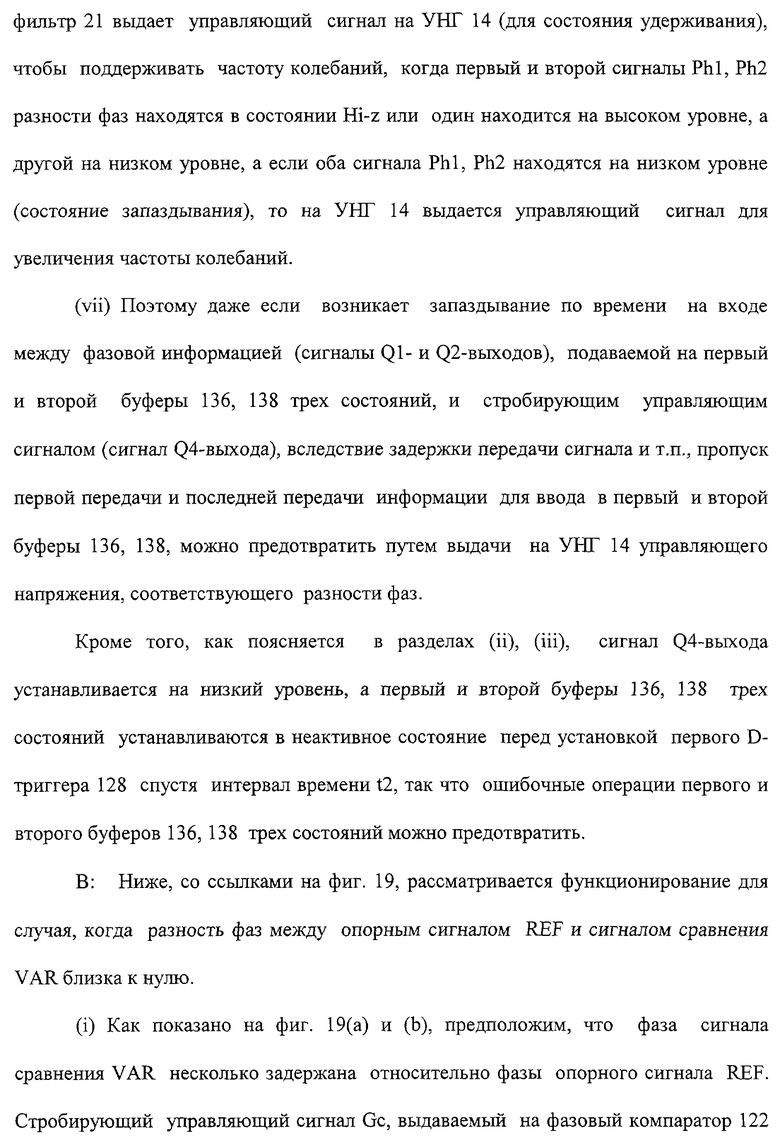

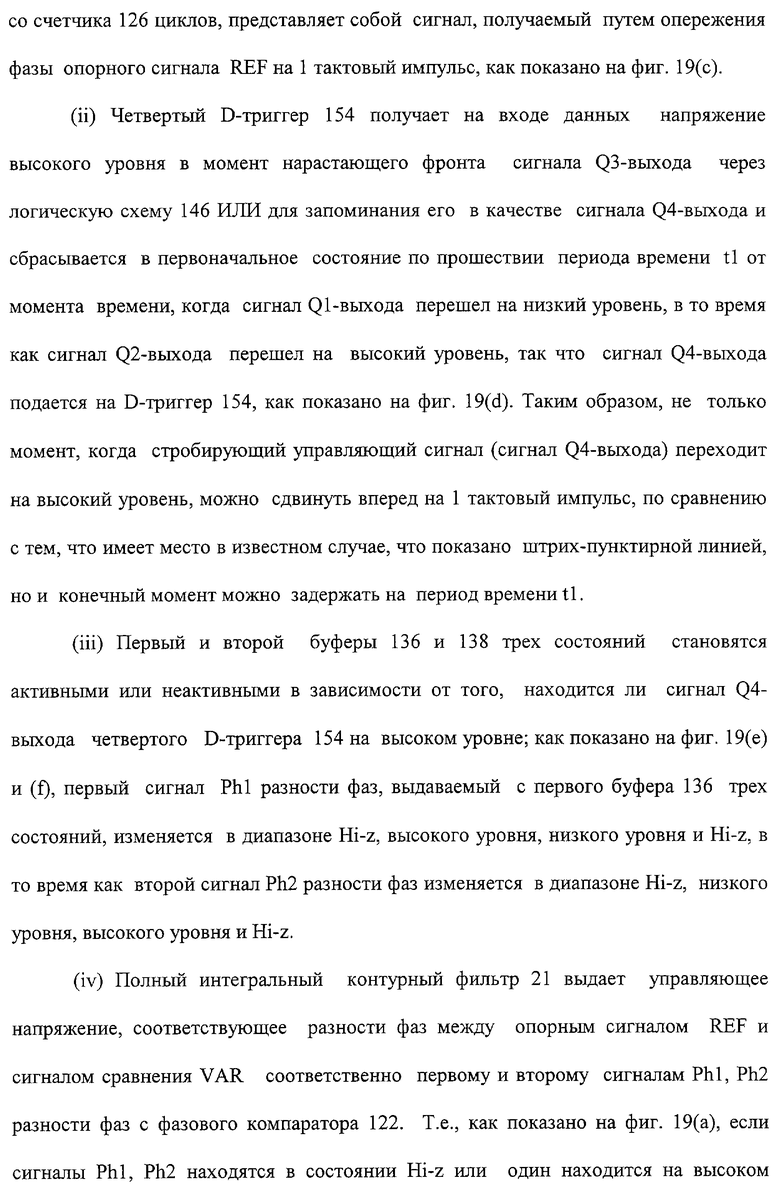

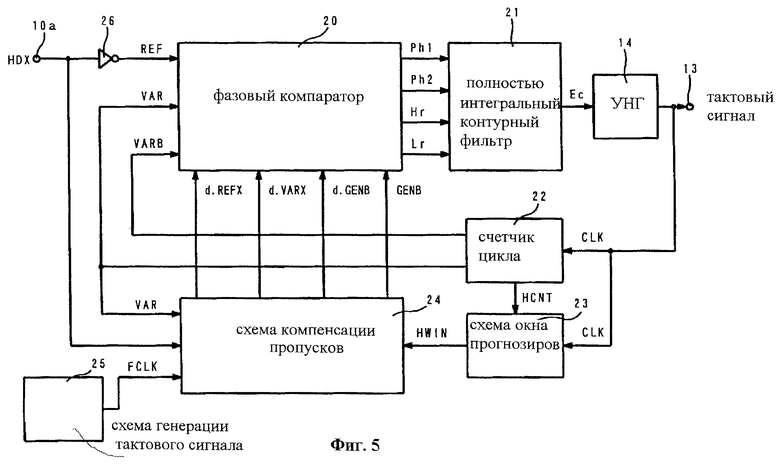

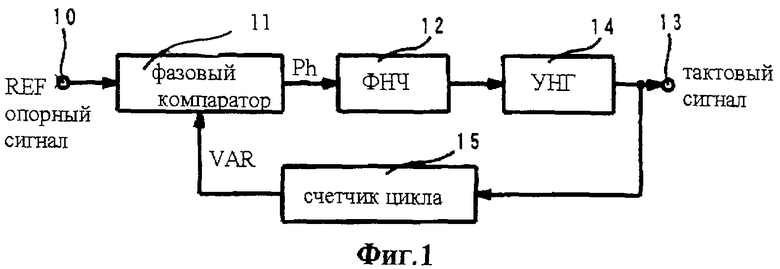

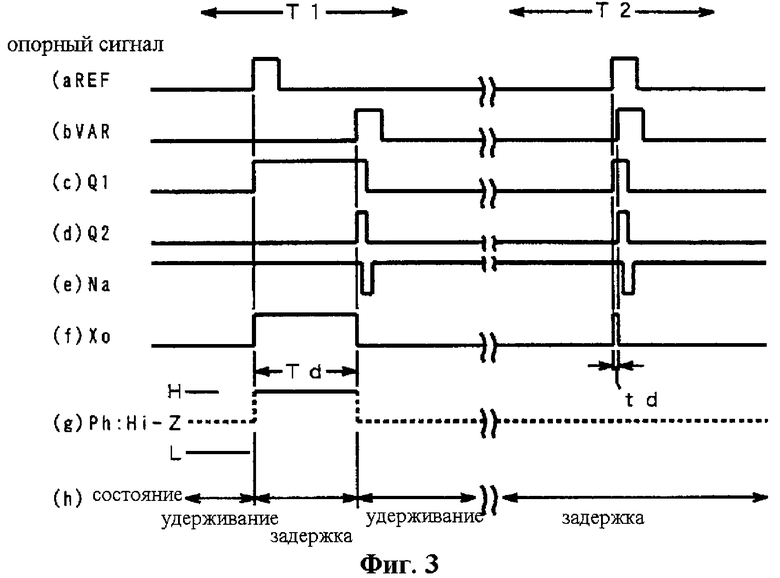

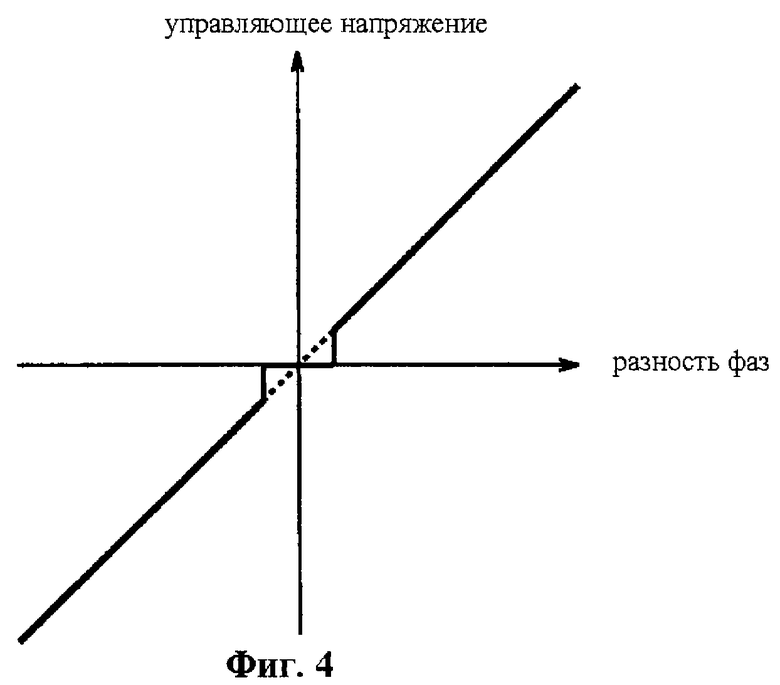

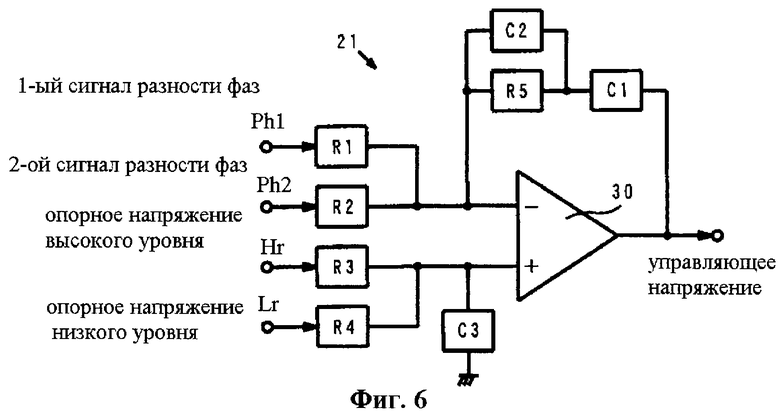

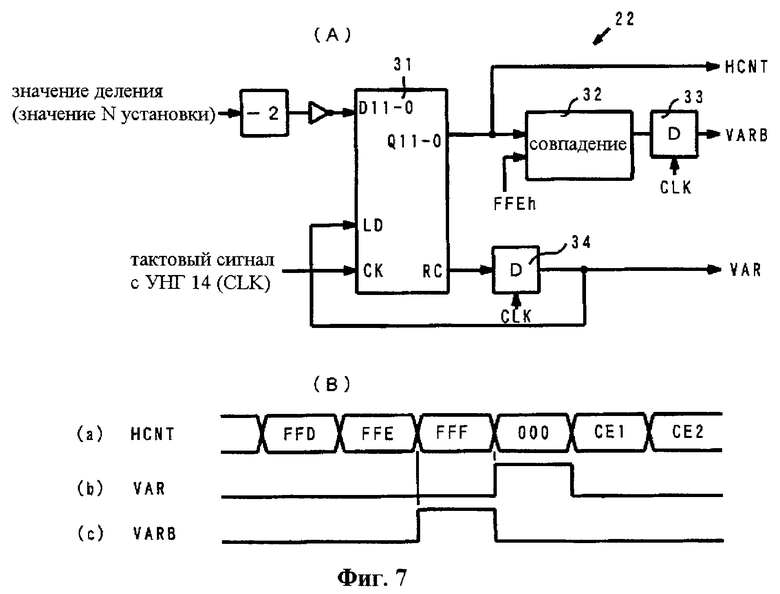

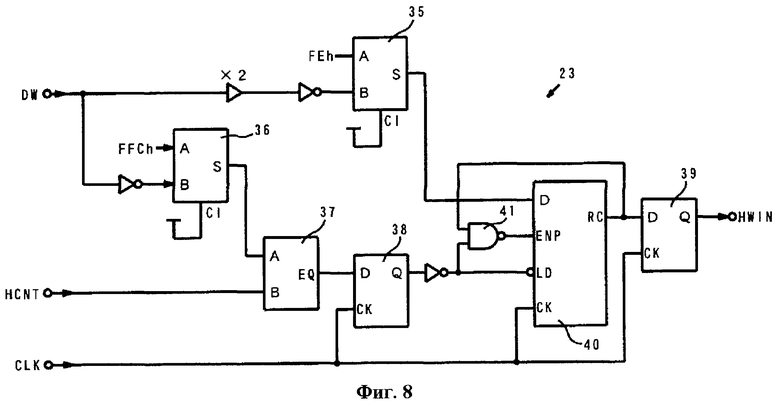

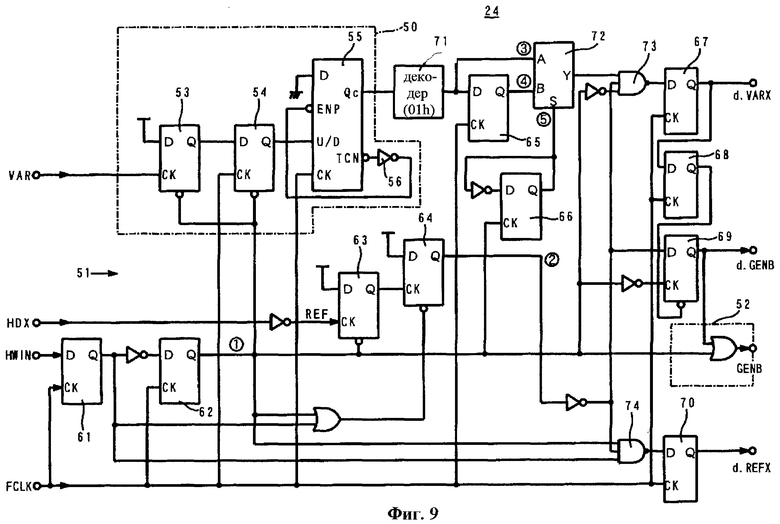

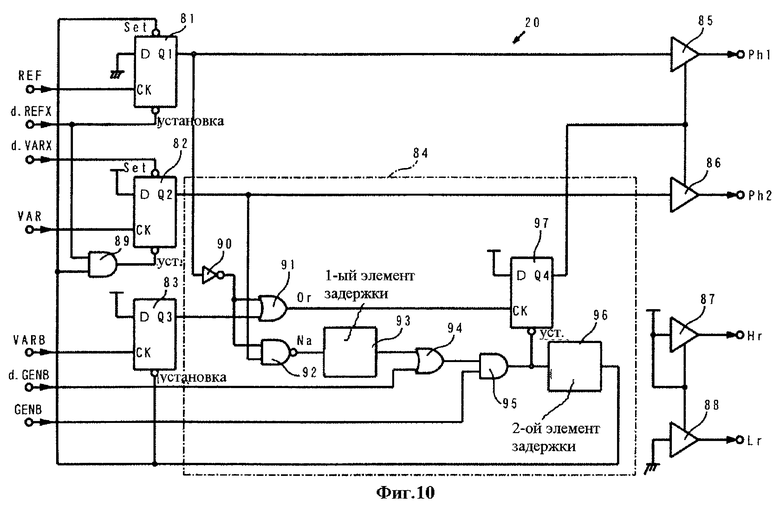

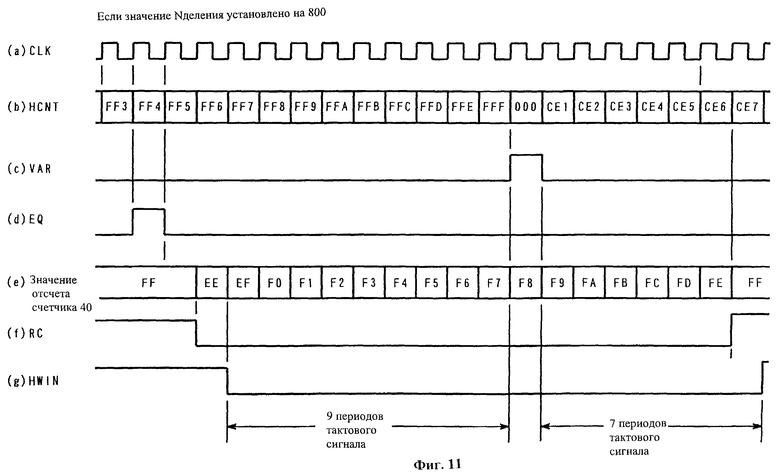

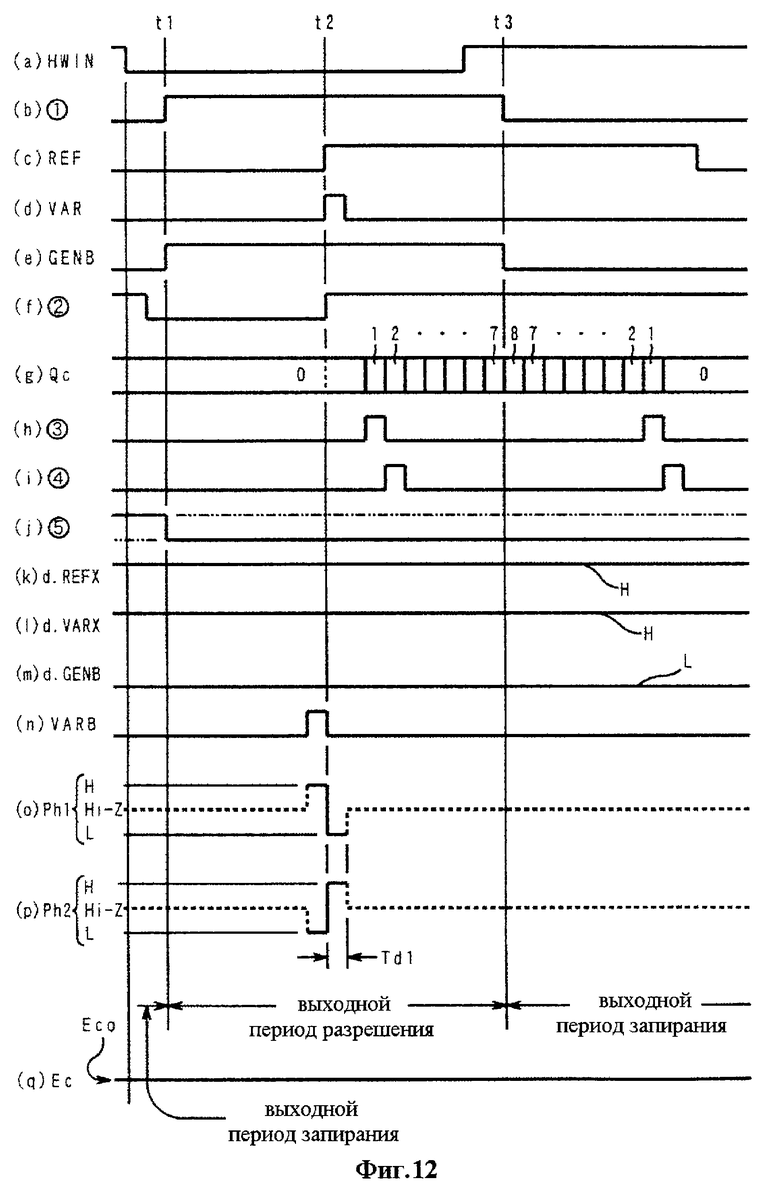

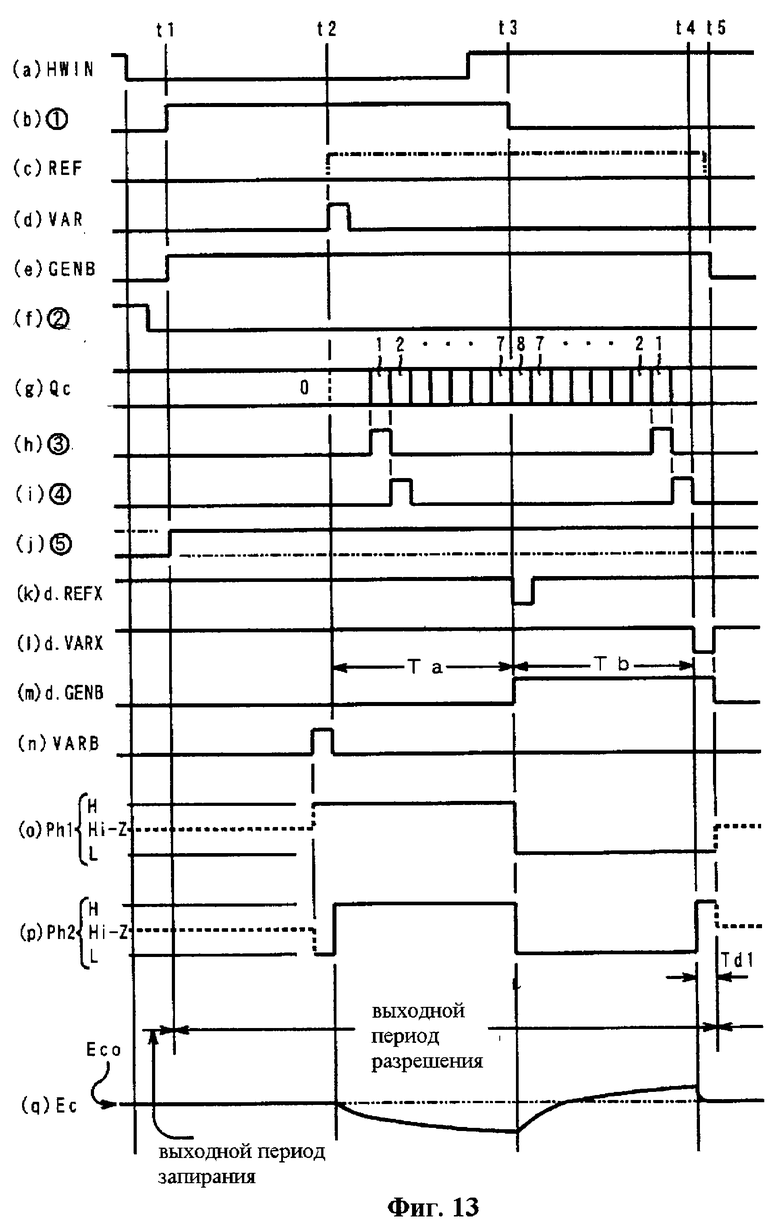

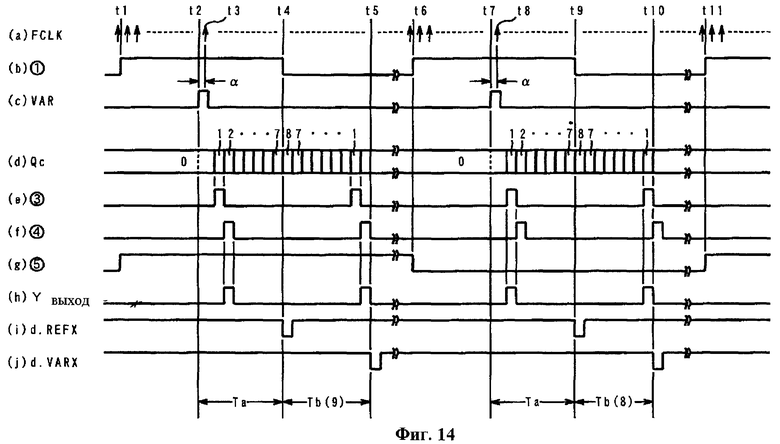

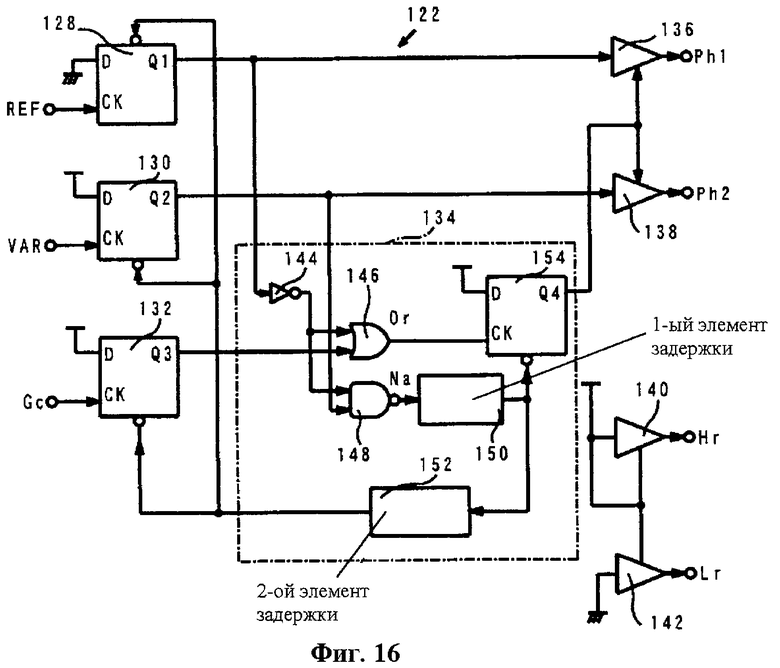

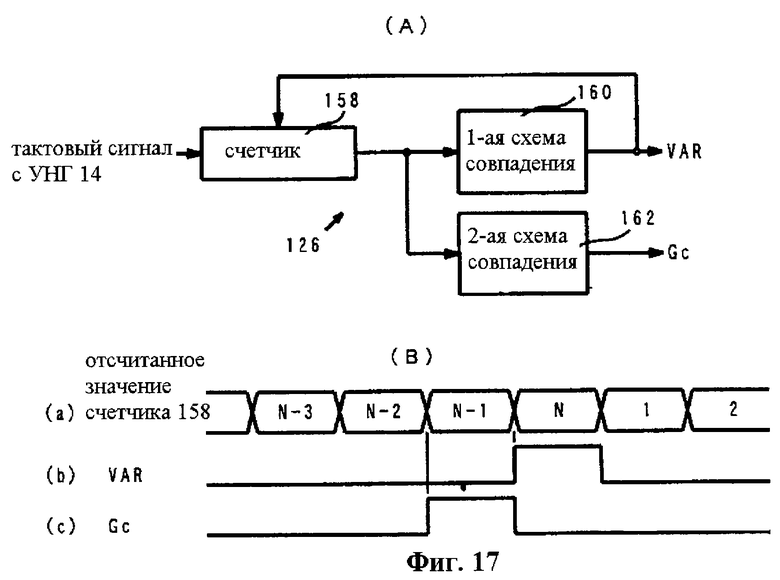

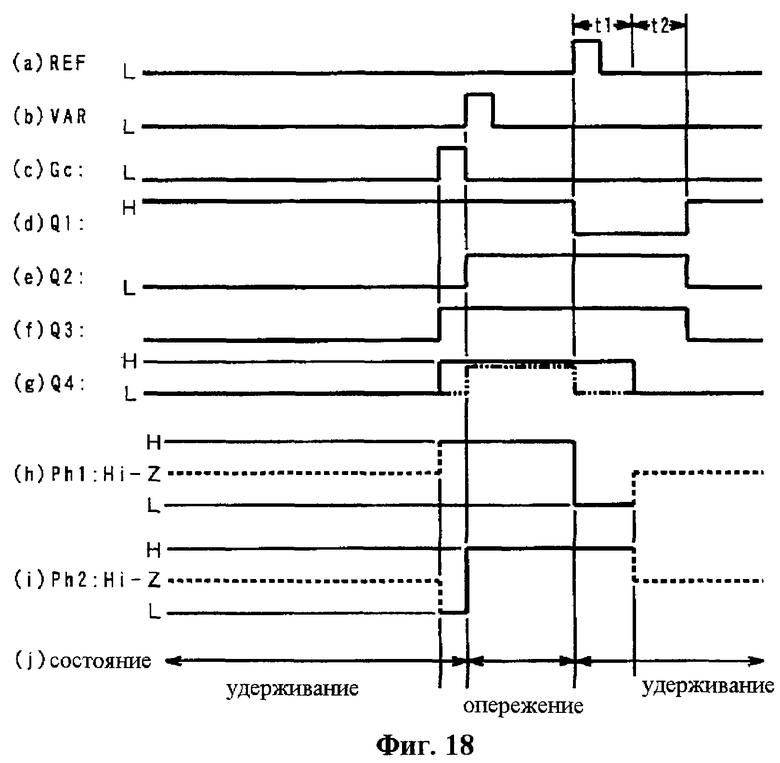

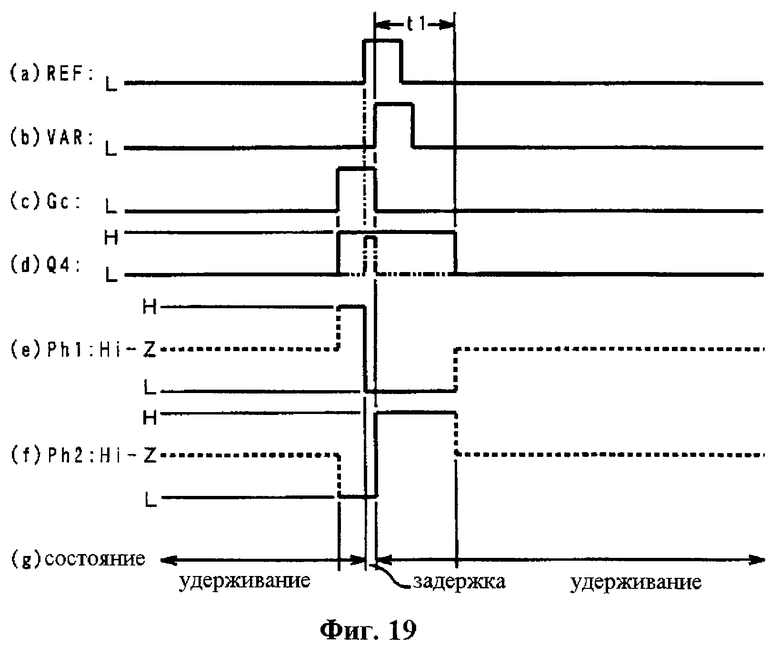

1. Схема фазовой автоподстройки частоты (ФАПЧ), содержащая фазовый компаратор для сравнения опорного сигнала и сигнала сравнения для выдачи сигнала, соответствующего разности фаз, контурный фильтр для выдачи управляющего сигнала, соответствующего сигналу с выхода фазового компаратора, управляемый напряжением генератор для выдачи на выход тактового сигнала, соответствующего управляющему напряжению с выхода контурного фильтра, и счетчик циклов для деления частоты тактового сигнала с выхода управляемого напряжением генератора на 1/N, где N - целое число, для подачи ее в качестве сигнала сравнения на фазовый компаратор, причем схема ФАПЧ дополнительно содержит схему окна прогнозирования для выдачи сигнала окна прогнозирования для прогнозирования момента формирования опорного сигнала и схему компенсации пропуска для обнаружения пропуска опорного сигнала в момент выдачи сигнала окна прогнозирования, а также выдачи первого корректирующего сигнала для компенсации пропуска и второго корректирующего сигнала для компенсации разности фаз между сигналом сравнения и первым корректирующим сигналом, при этом фазовый компаратор выдает не только сигнал, соответствующий разности фаз между сигналом сравнения и первым корректирующим сигналом, но и сигнал, соответствующий разности фаз между первым корректирующим сигналом и вторым корректирующим сигналом.2. Схема ФАПЧ по п.1, отличающаяся тем, что схема компенсации пропуска содержит главным образом измеритель интервала пропуска, предназначенный для измерения интервала пропуска опорного сигнала на основе сигнала окна прогнозирования и сигнала сравнения, и генератор корректирующих сигналов для выдачи первого и второго корректирующих сигналов на основе сигнала окна прогнозирования, опорного сигнала и измеренного значения измерителя интервала пропуска, при этом фазовый компаратор содержит первый D-триггер для приема опорного сигнала в качестве входного сигнала на его тактовом входе и напряжения низкого уровня в качестве входного сигнала на его входе данных, второй D-триггер для приема сигнала сравнения в качестве входного сигнала на его тактовом входе и напряжения высокого уровня в качестве входного сигнала на его входе данных, первый буфер трех состояний для приема сигнала Q-выхода первого D-триггера в качестве входного сигнала для выдачи первого сигнала разности фаз, второй буфер трех состояний для приема сигнала Q-выхода второго D-триггера в качестве входного сигнала для выдачи второго сигнала разности фаз, и схему управления, предназначенную не только для управления первым и вторым буферами трех состояний в активном состоянии в соответствии с инвертированным сигналом с Q-выхода первого D-триггера, но и для управления первым и вторым буферами трех состояний в неактивном состоянии в соответствии с инвертированным сигналом с логической схемы И, основанным на инвертированном сигнале с Q-выхода первого D-триггера и с Q-выхода второго D-триггера, причем первый D-триггер сбрасывается первым корректирующим сигналом, а второй D-триггер устанавливается вторым корректирующим сигналом.3. Схема ФАПЧ по п.2, отличающаяся тем, что измеритель интервала пропуска снабжен реверсивным счетчиком не только для счета тактовых импульсов с выхода схемы генерирования тактового сигнала, но и для прямого счета в соответствии с сигналом сравнения и обратного счета в соответствии с сигналом окна прогнозирования.4. Схема ФАПЧ по п.3, отличающаяся тем, что генератор сигналов коррекции содержит декодер для декодирования отсчитанного значения реверсивного счетчика, которое достигло установленного значения, элемент задержки на 1 тактовый импульс для задержки на 1 тактовый импульс выходного сигнала декодера по отношению к тактовому сигналу, выдаваемому со схемы генерирования тактового сигнала, и селектор для поочередного выбора сигнала с выхода декодера и сигнала с выхода элемента задержки на 1 тактовый импульс при каждой выдаче сигнала окна прогнозирования, при этом второй сигнал коррекции выдается соответственно выходному сигналу селектора, сигналу окна прогнозирования и опорному сигналу.5. Схема ФАПЧ по любому из пп.2-4, отличающаяся тем, что счетчик циклов содержит счетчик для приема первого установленного значения в качестве входного сигнала на его входе данных, отсчета тактовых импульсов с выхода управляемого напряжением генератора и задержки на 1 тактовый импульс выходного сигнала с выхода сквозного переноса для выдачи его в качестве сигнала сравнения и ввода его на вход нагрузки, схему совпадения для выдачи сигнала совпадения, когда отсчитанное значение счетчика совпадает со вторым установленным значением, и элемент задержки для формирования стробирующего управляющего сигнала путем задержки выходного сигнала схемы совпадения на 1 тактовый импульс, при этом фазовый компаратор снабжен третьим D-триггером для приема стробирующего управляющего сигнала в качестве входного сигнала на его тактовом входе и сигнала высокого уровня в качестве входного сигнала на его входе данных, причем схема управления управляет в активном состоянии первым и вторым буферами трех состояний в соответствии с сигналом, являющимся результатом логической операции ИЛИ над инвертированным сигналом с Q-выхода первого D-триггера и с Q-выхода третьего D-триггера.6. Схема ФАПЧ по любому из пп.2-4, отличающаяся тем, что схема управления содержит инвертор для инвертирования сигнала с Q-выхода первого D-триггера, четвертый D-триггер для приема выходного сигнала инвертора в качестве входного сигнала на его тактовом входе, напряжения высокого уровня в качестве входного сигнала на его входе данных и выдачи сигнала с Q-выхода в качестве стробирующего сигнала для первого и второго буферов трех состояний и логическую схему И-НЕ для инвертирования и выдачи на выходе сигнала, полученного в результате логической операции И над выходным сигналом инвертора и сигналом с Q-выхода второго D-триггера, и первый элемент задержки для задержки выходного сигнала логической схемы И-НЕ на установленный интервал времени Td1 для выдачи на вход сброса четвертого D-триггера.7. Схема ФАПЧ по п.5, отличающаяся тем, что схема управления содержит инвертор для инвертирования сигнала с Q-выхода первого D-триггера, логическую схему ИЛИ для выдачи сигнала, полученного в результате логической операции ИЛИ над выходным сигналом инвертора и сигналом с Q-выхода третьего D-триггера, четвертый D-триггер для приема выходного сигнала логической схемы ИЛИ в качестве входного сигнала на его тактовом входе, напряжения высокого уровня в качестве входного сигнала на его входе данных и выдачи сигнала с Q-выхода в качестве стробирующего сигнала для первого и второго буферов трех состояний, и логическую схему И-НЕ для инвертирования и выдачи на выходе сигнала, полученного в результате логической операции И над выходным сигналом инвертора и сигналом с Q-выхода второго D-триггера, и первый элемент задержки для задержки выходного сигнала логической схемы И-НЕ на установленный интервал времени Td1 для выдачи на вход сброса четвертого D-триггера.8. Схема ФАПЧ по п.6, отличающаяся тем, что схема управления содержит второй элемент задержки для задержки выходного сигнала первого элемента задержки на установленный интервал времени Td2 для выдачи на вход сброса первого D-триггера и для выдачи на вход сброса второго D-триггера через логическую схему И, причем первый корректирующий сигнал вводится на другой вход логической схемы И.9. Схема ФАПЧ по п.7, отличающаяся тем, что схема управления содержит второй элемент задержки для задержки выходного сигнала первого элемента задержки на установленный интервал времени Td2 для выдачи на вход установки первого D-триггера и на вход сброса второго D-триггера, причем первый корректирующий сигнал вводится на другой вход логической схемы И.10. Схема ФАПЧ по любому из пп.2-4, 7-9, отличающаяся тем, что контурный фильтр содержит полностью интегральный контурный фильтр с операционным усилителем, при этом первый сигнал разности фаз и второй сигнал разности фаз вводятся на один вход операционного усилителя, поделенные напряжения опорного напряжения высокого уровня и опорного напряжения низкого уровня вводятся на другой вход, а с выхода операционного усилителя выдается управляющее напряжение, подаваемое на управляемый напряжением генератор, при этом если первый сигнал разности фаз и второй сигнал разности фаз имеют высокий уровень или низкий уровень, то на управляемый напряжением генератор выдается управляющий сигнал для снижения или увеличения частоты колебаний, а если любой один из первого сигнала разности фаз и второго сигнала разности фаз имеет высокий уровень или низкий уровень или оба имеют высокий импеданс, то на управляемый напряжением генератор выдается управляющее напряжение для поддержания частоты колебаний.11. Схема ФАПЧ по п.5, отличающаяся тем, что контурный фильтр содержит полностью интегральный контурный фильтр с операционным усилителем, при этом полностью интегральный контурный фильтр выполнен так, что первый сигнал разности фаз и второй сигнал разности фаз вводятся на один вход, поделенные напряжения опорного напряжения высокого уровня и опорного напряжения низкого уровня вводятся на другой вход, а с выхода выдается управляющее напряжение, подаваемое на управляемый напряжением генератор, при этом, если первый сигнал разности фаз и второй сигнал разности фаз имеют высокий уровень или низкий уровень, то на управляемый напряжением генератор выдается управляющий сигнал для снижения или увеличения частоты колебаний, а если любой один из первого сигнала разности фаз и второго сигнала разности фаз имеет высокий уровень или низкий уровень или оба имеют высокий импеданс, то на управляемый напряжением генератор выдается управляющее напряжение для поддержания частоты колебаний.12. Схема ФАПЧ по п.6, отличающаяся тем, что контурный фильтр содержит полностью интегральный контурный фильтр с операционным усилителем, при этом полностью интегральный контурный фильтр выполнен таким образом, что первый сигнал разности фаз и второй сигнал разности фаз вводятся на один вход, поделенные напряжения опорного напряжения высокого уровня и опорного напряжения низкого уровня вводятся на другой вход, а с выхода выдается управляющее напряжение, подаваемое на управляемый напряжением генератор, при этом, если первый сигнал разности фаз и второй сигнал разности фаз имеют высокий уровень или низкий уровень, то на управляемый напряжение генератор выдается управляющий сигнал для снижения или увеличения частоты колебаний, а если любой один из первого сигнала разности фаз и второго сигнала разности фаз имеет высокий уровень или низкий уровень или оба имеют высокий импеданс, то на управляемый напряжением генератор выдается управляющее напряжение для поддержания частоты колебаний.13. Схема ФАПЧ, содержащая фазовый компаратор для сравнения опорного сигнала и сигнала сравнения для выдачи сигнала, соответствующего разности фаз, контурный фильтр для выдачи управляющего напряжения, соответствующего сигналу с выхода фазового компаратора, управляемый напряжением генератор для выдачи на выход тактового сигнала, соответствующего управляющему напряжению с выхода контурного фильтра, и счетчик циклов для деления частоты тактового сигнала с выхода управляемого напряжением генератора на 1/N, где N - целое число, для подачи ее в качестве сигнала сравнения на фазовый компаратор, причем схема ФАПЧ дополнительно содержит схему генерирования стробирующего управляющего сигнала, предназначенную для генерирования стробирующего управляющего сигнала, фаза которого опережает фазу сигнала сравнения на 1 тактовый импульс, и буфер трех состояний, которым снабжен фазовый компаратор и который может не только выдавать сигналы трех различных состояний, соответствующих разности фаз между опорным сигналом и сигналом сравнения, но и управляться в активном состоянии в соответствии со стробирующим управляющим сигналом.14. Схема ФАПЧ по п.13, отличающаяся тем, что фазовый компаратор содержит первый D-триггер для приема опорного тактового сигнала в качестве входного сигнала на его тактовом входе и напряжения низкого уровня в качестве входного сигнала на его входе данных, второй D-триггер для приема сигнала сравнения в качестве входного сигнала на его тактовом входе и напряжения высокого уровня в качестве входного сигнала на его входе данных, третий D-триггер для приема стробирующего управляющего сигнала в качестве входного сигнала на его тактовом входе и напряжения высокого уровня в качестве входного сигнала на его входе данных, первый буфер трех состояний для приема сигнала Q-выхода первого D-триггера в качестве входного сигнала для выдачи первого сигнала разности фаз (сигнала трех состояний), второй буфер трех состояний для приема сигнала Q-выхода первого D-триггера в качестве входного сигнала для выдачи второго сигнала разности фаз (сигнала трех состояний) и схему управления для управления первым и вторым буферами трех состояний в активном состоянии в соответствии с сигналом, являющимся результатом логической операции ИЛИ над инвертированным сигналом Q-выхода первого D-триггера и сигнала Q-выхода третьего D-триггера, а также для управления первым и вторым буферами трех состояний в неактивном состоянии в соответствии с сигналом, полученным инвертированием сигнала, являющегося результатом логической операции И над инвертированным сигналом Q-выхода первого D-триггера и сигналом Q-выхода второго D-триггера.15. Схема ФАПЧ по п.14, отличающаяся тем, что схема управления содержит инвертор для инвертирования сигнала с Q-выхода первого D-триггера, логическую схему ИЛИ для выдачи сигнала, являющегося результатом логической операции ИЛИ над выходным сигналом инвертора и сигналом с Q-выхода третьего D-триггера, четвертый D-триггер для приема выходного сигнала логической схемы ИЛИ в качестве входного сигнала на его тактовом входе, напряжения высокого уровня в качестве входного сигнала на его входе данных и выдачи сигнала с Q-выхода в качестве стробирующего управляющего сигнала на первый и второй буферы трех состояний, логическую схему И-НЕ для инвертирования на выходе сигнала, являющегося результатом логической операции И над выходным сигналом инвертора и сигналом с Q-выхода второго D-триггера, и первый элемент задержки для задержки выходного сигнала с логической схемы И-НЕ на установленное время t1 для выдачи на вход сброса четвертого D-триггера.16. Схема ФАПЧ по п.15, отличающаяся тем, что схема управления содержит второй элемент задержки для задержки выходного сигнала первого элемента задержки на установленное время t2 для выдачи на вход установки первого D-триггера и на входы сброса второго и третьего D-триггеров.17. Схема ФАПЧ по п.14, или 15, или 16, отличающаяся тем, что контурный фильтр содержит полностью интегральный контурный фильтр, включающий в себя операционный усилитель, при этом операционный усилитель принимает первый сигнал разности фаз и второй сигнал разности фаз в качестве входных сигналов на одном входе и разделенных напряжений опорного напряжения высокого уровня и опорного напряжения низкого уровня в качестве входных сигналов на другом входе и выдает управляющее напряжение на управляемый напряжением генератор, при этом когда первый и второй сигналы разности фаз находятся на высоком или на низком уровне, на управляемый напряжением генератор выдается управляющее напряжение для снижения или для увеличения частоты колебаний; когда один из первого и второго сигналов разности фаз находится на высоком уровне, а другой - на низком уровне или оба имеют высокий импеданс, то на управляемый напряжением генератор выдается управляющее напряжение для поддержания частоты колебаний.18. Схема ФАПЧ по п.13, или 14 или 15, или 16, отличающаяся тем, что счетчик циклов содержит счетчик для отсчета тактового сигнала, выданного с управляемого напряжением генератора, первую схему совпадения для выдачи сигнала сравнения, получаемого путем деления частоты тактового сигнала на 1/N, если отсчитанное значение счетчика совпадает с установленным значением N, и для выдачи сигнала сравнения на вход сброса счетчика и вторую схему совпадения для выдачи стробирующего управляющего сигнала, получаемого путем деления частоты тактового сигнала на N, если отсчитанное значение счетчика совпадает с установленным значением (N-1), причем счетчик циклов содержит схему генерации стробирующего управляющего сигнала.19. Схема ФАПЧ по п.17, отличающаяся тем, что счетчик циклов содержит счетчик для отсчета тактового сигнала, выданного с управляемого напряжением генератора, первую схему совпадения для выдачи сигнала сравнения, получаемого путем деления частоты тактового сигнала на 1/N, если отсчитанное значение счетчика совпадает с установленным значением N, и для выдачи сигнала сравнения на вход сброса счетчика и вторую схему совпадения для выдачи стробирующего управляющего сигнала, получаемого путем деления частоты тактового сигнала на 1/N, причем счетчик циклов содержит схему генерации стробирующего управляющего сигнала.

Приоритет по пунктам:

31.03.1998 по пп.13-19;10.11.1998 по пп.1-12.