Изобретения относятся к области радиотехники, в частности к способу и устройству частотно-временной синхронизации системы связи.

В системах связи каналы распространения сигнала между приемником и передатчиком данных являются многолучевыми и нестационарными. Эффективность систем связи во многом определяется способностью алгоритмов частотно-временной синхронизации обеспечить в многолучевых нестационарных каналах необходимую точность оценки временного положения сигнала и частотного рассогласования между частотой входного сигнала и частотой опорного генератора.

В последнее время большое развитие получили системы связи с OFDM (Orthogonal Frequency Division Multiplexing). OFDM сигнал представляет собой последовательность OFDM символов. Каждый такой символ состоит из двух частей - префикса и многочастотного информационного символа. Многочастотный информационный символ представляет собой сумму модулированных гармоник. Под префиксом понимают некоторую последовательность отсчетов сигнала, которая непосредственно предшествует каждому многочастотному информационному символу и представляет собой часть этого символа. Как правило, длительность префикса меньше длительности информационного символа. Наличие префикса при обработке сигнала позволяет уменьшить или полностью устранить межсимвольную интерференцию (IEEE Std 802.11а - 1999, Прокис Дж., Цифровая связь. Перевод с английского. М., Радио и связь, 2000 г., с.593) [1].

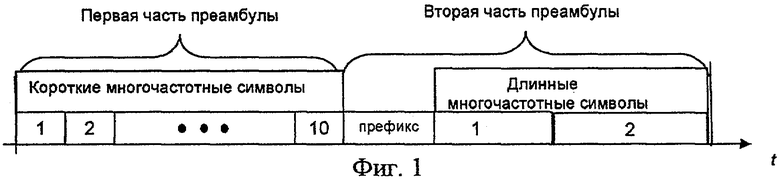

Для начальной частотно-временной синхронизации обычно используют специальный сигнал - преамбулу, который предшествует информационному сообщению. В системе связи IEEE 802.11а (см. Supplement to IEEE Standard for Information technology. Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications: High-speed Physical Layer in. the 5 GHZ Band)[2] преамбула и информационное сообщение представляют собой OFDM (Orthogonal Frequency Division Multiplexing) сигнал. Структура преамбулы показана на Фиг.1.

Преамбула состоит из двух частей.

Первая часть преамбулы включает десять коротких обучающих многочастотных символов и служит для предварительной ("грубой") оценки временного положения и частотной расстройки входного сигнала. Вторая часть преамбулы включает два длинных обучающих многочастотных символа и защитный интервал (префикс). Вторая часть преамбулы служит для точной окончательной оценки временного положения и частотной расстройки входного сигнала при начальной синхронизации.

Известен способ частотной и временной синхронизации, описанный в работе Tufvesson F., Faulkne M., Hoeher P., Edfors О., OFDM Time and Frequency Synchronization by Spread Spectrum Pilot Technique // 8th IEEE Communication Theory Mini Conference in conjunction to ICC'99,. - June 1999. - P.115-119 [3]. В данной статье предложен способ частотной и временной синхронизации для OFDM систем, который базируется на использовании непрерывной кодовой последовательности. Кодовая последовательность добавляется к OFDM информационному сигналу или используется отдельно как сигнал преамбулы. Этот способ временной и частотной синхронизации заключается в следующем.

Входной сигнал обрабатывают в нескольких фильтрах, согласованных с различными частями известной кодовой последовательности. Выходные сигналы согласованных фильтров используют для формирования комплексной решающей функции. Каждое слагаемое решающей функции представляет собой сумму попарных произведений откликов согласованных фильтров на соответствующие им соседние комплексно-сопряженные отклики согласованных фильтров.

Оценку временной задержки (положения) входного сигнала определяют по положению максимума квадрата модуля решающей функции. Оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала определяют по значению аргумента решающей функции в точке, соответствующей оценке временной задержки.

Описанный способ предполагает одноэтапную процедуру частотно-временной синхронизации. Вследствие этого при больших величинах возможного частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала при реализации способа необходимо использовать фильтры, согласованные с более короткими частями известной кодовой последовательности. Это приводит к ухудшению точности оценки временной задержки и частотной расстройки и является главным недостатком данного способа синхронизации.

Известен способ частотно-временной синхронизации, описанный в статье Schmidl Т.М., Сох D. С., Robust Frequency and Timing

В [4] предложен способ синхронизации параметров сигнала в OFDM (Orthogonal Frequency Division Multiplexing) системах, который основан на приеме преамбулы, состоящей из двух OFDM символов. В процессе синхронизации на первом этапе по первому символу определяют временное положение сигнала, а также осуществляют предварительную оценку частного рассогласования с точностью до n·π·Т, n=1, 2 ..., Т - длительность OFDM символа. Окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала осуществляют на втором этапе с использованием второго OFDM символа.

Первый OFDM символ состоит из двух идентичных частей, отличающихся при приеме фазовым сдвигом. Сначала формируют комплексную решающую функцию первого этапа как произведения выборок первой части символа на соответствующие комплексно-сопряженные выборки второй части символа. Оценку временной задержки входного сигнала определяют по положению максимума квадрата модуля решающей функции первого этапа. Предварительную оценку частотного сдвига между несущей входного сигнала и частотой опорного сигнала вычисляют по значению аргумента решающей функции первого этапа в точке, соответствующей оценке временной задержки.

Для определения окончательной оценки частотного рассогласования формируют решающую функцию второго этапа для всевозможных значений n, используя оба OFDM символа. Оценку параметра n определяют по положению максимума решающей функции второго этапа.

Недостатком описанного способа является невысокая точность оценки временного положения сигнала вследствие весьма широкой плоской вершины решающей функции первого этапа, ширина которой равна длительности префикса OFDM символа. Кроме того, недостатком является неполное использование ресурса преамбулы, а именно отказ от использования второго OFDM символа при оценке временного положения сигнала. Перечисленные недостатки приводят к низкой помехоустойчивости частотно-временной синхронизации системы связи.

В статье Chia-Sheng Peng, Chian-Himg Cho and К.A. Wen, Frame Synchronization and Digital AGC for OFDM Based WLAN Proceedings Vol.2 of European Wireless 2002, pp.835-839, Feb. 2002 [5] предлагается алгоритм временной синхронизации и AGC (Automatic Gain Control - автоматическая регулировка усиления) в системе связи IEEE 802.11а. В соответствии с предлагаемым в [5] алгоритмом начало фрейма и окончание первой части преамбулы определяют по пересечению порога следующей величиной

где s(n) - отсчеты принятого OFDM сигнала,

Ng=16.

Порог определяют на основе средней мощности сигнала, вычисленной в скользящем окне. После определения начала фрейма осуществляют AGC, используя модуль величины (1). После определения начала фрейма также выполняют символьную синхронизацию с помощью согласованного с коротким OFDM символом фильтра. Выходные отсчеты согласованного фильтра сравнивают с порогом. По окончании первой части преамбулы и превышению порога выходными отсчетами согласованного фильтра принимают решение о временной синхронизации.

Недостатком описанного способа синхронизации является отказ от некогерентной обработки при символьной (временной) синхронизации, что приводит к низкой помехоустойчивости временной синхронизации системы связи. Кроме того, в статье отсутствует описание процедуры частотной синхронизации.

В статье Н.Kobayashi, К.Mori, Т.Nagaosa. Proposal of Symbol Timing and Carrier Frequency Synchronization Method for Burst Mode OFDM Signal // IEICE Trans. Commun., Vol. E86-B, No.1, January 2003 [6] описан алгоритм частотно-временной синхронизации в OFDM системе связи, использующий сигнал преамбулы (аналогично представленной на Фиг.1).

В соответствии с описанным алгоритмом для осуществления временной синхронизации сначала формируют произведения комплексно-сопряженных отсчетов входного сигнала на комплексные отсчеты входного сигнала, задержанные на один отсчет. Полученные произведения подают на коррелятор, опорный сигнал которого представляет собой произведение известных временных отсчетов преамбулы на комплексно-сопряженные отсчеты преамбулы, задержанные на один отсчет. С выхода коррелятора сигнал поступает на вход пикового детектора, который определяет временное положение сигнала преамбулы по положению максимума выходного сигнала коррелятора. Оценку частотного рассогласования предлагается производить в два этапа. На первом этапе формируют предварительную оценку частотного рассогласования, а на втором - точную оценку частотного рассогласования. На первом этапе, используя оценку временного положения сигнала преамбулы, сначала формируют произведения отсчетов входного сигнала на комплексно-сопряженные отсчеты известного сигнала преамбулы. Предварительную оценку частотного рассогласования получают по результату преобразования Фурье полученного произведения. Далее корректируют входной сигнал в соответствии с полученной оценкой. На втором этапе сначала выполняют преобразование Фурье OFDM символов скорректированного входного сигнала. Затем находят произведения комплексно-сопряженных результатов преобразования первого символа на соответствующие результаты преобразования второго OFDM символа входного сигнала. Точную оценку частотного рассогласования получают по результату корреляции полученного произведения с опорным сигналом.

К недостаткам описанного способа частотно-временной синхронизации следует отнести отказ от когерентной обработки при временной синхронизации, отсутствие учета изменения уровня входного сигнала (в результате функционирования системы AGC). Перечисленные недостатки приводят к низкой помехоустойчивости частотно-временной синхронизации системы связи. К недостаткам также следует отнести большое время задержки вынесения решений, что требует усложнения аппаратуры (возникает необходимость в линиях задержки с большим объемом памяти).

Наиболее близким к заявляемому решению является способ частотно-временной синхронизации системы связи и алгоритм его реализации, приведенные в книге Nee R.Prasad R., OFDM for Wireless Multimedia Communication, London: «Artech House», 2000, Chapter 4. Synchronization. 4.6. Synchronization using Special Training Symbols, стр.86-88; Chapter 10. Applications of OFDM. 10.5.4 Training, стр.246-247 [7].

Этот способ частотно-временной синхронизации системы связи заключается в следующем:

входной сигнал фильтруют, усиливают, выполняют автоматическую регулировку усиления, вычисляя коэффициент усиления входного сигнала в зависимости от уровня мощности входного сигнала, переносят на видеочастоту, осуществляют его аналогово-цифровое преобразование и децимацию, формируя входной цифровой комплексный сигнал на видеочастоте;

частотно-временную синхронизацию осуществляют в два этапа:

на первом этапе определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего:

осуществляют согласованную с одним коротким многочастотным символом фильтрацию входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа;

вычисляют квадраты модулей комплексных откликов первого этапа, формируя решающую функцию первого этапа;

определяют временные положения локальных максимумов решающей функции первого этапа, превышающих заданный порог первого этапа H1;

запоминают комплексные отклики первого этапа, соответствующие локальным максимумам решающей функции первого этапа;

формируют предварительную оценку частотного сдвига по усредненной разности фаз комплексных откликов первого этапа, соответствующих локальным максимумам решающей функции первого этапа;

на втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей входного сигнала и частотой опорного сигнала, для чего:

корректируют фазу входного цифрового комплексного сигнала на интервале работы второго этапа с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала;

осуществляют согласованную с одним длинным многочастотным символом фильтрацию скорректированного входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа;

вычисляют квадраты модулей комплексных откликов второго этапа, формируя решающую функцию второго этапа;

сравнивают значения решающей функции второго этапа с заданным порогом второго этапа Н2, при непревышении порога полагают преамбулу необнаруженной;

при превышении порога второго этапа Н2 полагают преамбулу обнаруженной, тогда:

определяют оценку временного положения преамбулы по временному положению первого превышения порога второго этапа H2;

определяют временные положения локальных максимумов решающей функции второго этапа, превышающих заданный порог второго этапа Н2;

определяют дополнительную оценку частотного сдвига по разности фаз двух комплексных откликов второго этапа, соответствующих локальным максимумам решающей функции второго этапа;

определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига.

Автоматическую регулировку усиления выполняют путем изменения коэффициента усиления аналогового усилителя. Коэффициент усиления формируется по оценке уровня (мощности) принимаемого сигнала (описание прототипа п.10.4 стр.235).

Оценку временного положения преамбулы, а именно начала преамбулы, определяют равной разности временного положения первого превышения порога второго этапа Н2 и суммы длительностей первой части преамбулы и префикса.

Дополнительную оценку частотного сдвига определяют, например, как отношение разности фаз смежных комплексных откликов второго этапа к длительности длинного многочастотного символа.

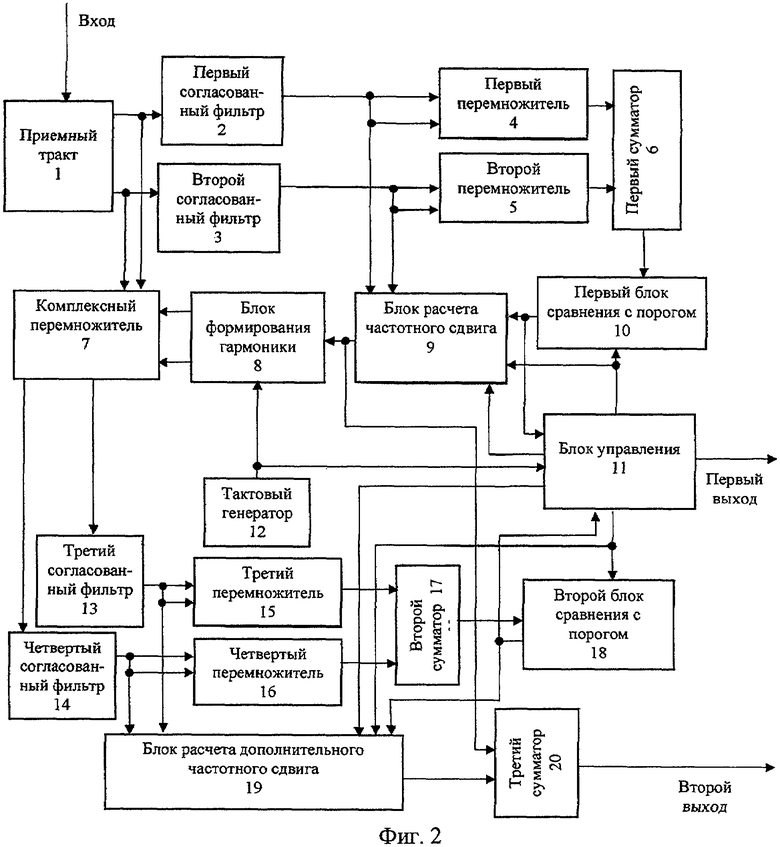

Заметим, что в упомянутом источнике информации структурная схема устройства частотно-временной синхронизации системы связи не приведена. Однако из описания алгоритма можно представить устройство, которое реализует способ-прототип. Устройство-прототип приведено на Фиг.2.

Устройство-прототип (Фиг.2) содержит приемный тракт 1, первый 2 и второй 3 согласованные фильтры, осуществляющие на первом этапе согласованную с одним коротким многочастотным символом фильтрацию сформированного входного цифрового комплексного сигнала и формирующие комплексные отклики первого этапа, первый 4 и второй 5 перемножители, первый сумматор 6, комплексный перемножитель 7, блок 8 формирования гармоники, блок 9 расчета частотного сдвига, первый блок 10 сравнения с порогом, блок 11 управления, тактовый генератор 12, третий 13 и четвертый 14 согласованные фильтры, осуществляющие на втором этапе согласованную с одним длинным многочастотным символом фильтрацию скорректированного входного цифрового комплексного сигнала и формирующие комплексные отклики второго этапа, третий 15 и четвертый 16 перемножители, второй сумматор 17, второй блок 18 сравнения с порогом, блок 19 расчета дополнительного частотного сдвига, третий сумматор 20, при этом вход приемного тракта 1 является входом устройства, первый выход приемного тракта 1 соединен с входом первого согласованного фильтра 2 и первым входом комплексного перемножителя 7, второй выход приемного тракта 1 соединен со входом второго согласованного фильтра 3 и вторым входом комплексного перемножителя 7, выход первого согласованного фильтра 2 соединен с первым и вторым входами первого перемножителя 4 и вторым входом блока 9 расчета частотного сдвига, выход второго согласованного фильтра 3 соединен с первым и вторым входами второго перемножителя 5 и третьим входом блока 9 расчета частотного сдвига, выходы первого 4 и второго 5 перемножителей соединены соответственно с первым и вторым входами первого сумматора 6, выход которого соединен с первым входом первого блока 10 сравнения с порогом, второй вход которого объединен с четвертым входом 9 блока расчета частотного сдвига и соединен с первым выходом блока 11 управления, выход первого блока 10 сравнения с порогом соединен с первым входом блока 9 расчета частотного сдвига и первым входом блока 11 управления, второй выход которого является первым выходом устройства, четвертый выход блока 11 управления соединен с пятым входом блока 9 расчета частотного сдвига, а третий выход - с первым входом блока 19 расчета дополнительного частотного сдвига, второй вход блока 11 управления объединен со вторым входом блока 8 формирования гармоники и соединен с выходом тактового генератора 12, первый вход блока 8 формирования гармоники объединен с первым входом третьего сумматора 20 и соединен с выходом блока 9 расчета частотного сдвига, первый и второй выходы блока 8 формирования гармоники соединены соответственно с третьим и четвертым входами комплексного перемножителя 7, первый и второй выходы которого соединены соответственно со входами третьего 13 и четвертого 14 согласованных фильтров, выход третьего согласованного фильтра 13 соединен с первым и вторым входами третьего перемножителя 15 и вторым входом блока 19 расчета дополнительного частотного сдвига, выход четвертого согласованного фильтра 14 соединен с первым и вторым входами четвертого перемножителя 16 и третьим входом блока 19 расчета дополнительного частотного сдвига, выходы третьего 15 и четвертого 16 перемножителей соединены соответственно с первым и вторым входами второго сумматора 17, выход которого соединен с первым входом второго блока 18 сравнения с порогом, второй вход которого объединен с четвертым входом блока 19 расчета дополнительного частотного сдвига и соединен с пятым выходом блока 11 управления, выход второго блока 18 сравнения с порогом соединен с третьим входом блока 11 управления и пятым входом блока 19 расчета дополнительного частотного сдвига, выход блока 19 расчета дополнительного частотного сдвига соединен со вторым входом третьего сумматора 20, выход которого является вторым выходом устройства.

Устройство частотно-временной синхронизации системы связи (Фиг.2) работает следующим образом.

На приемной стороне в приемном тракте 1 входной сигнал предварительно фильтруют, усиливают, переносят на видеочастоту, осуществляют его аналогово-цифровое преобразование, децимацию и т.д. В результате чего формируют входной цифровой комплексный сигнал на видеочастоте. Для частотно-временной синхронизации, которая состоит из двух этапов, используют сигнал преамбулы. При этом на первом этапе определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала. На втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала.

На первом этапе синфазную и квадратурную составляющие входного цифрового комплексного сигнала с первого и второго выходов приемного тракта 1 подают соответственно на входы первого 2 и второго 3 согласованных фильтров и на первый и второй входы комплексного перемножителя 7.

В согласованных фильтрах 2 и 3 на первом этапе осуществляют согласованную с одним коротким многочастотным символом фильтрацию соответственно синфазной и квадратурной компонент входного цифрового комплексного сигнала и формируют отклики для синфазной и квадратурной составляющих входного цифрового комплексного сигнала, которые поступают соответственно на первые и вторые входы перемножителей 4 и 5 и на второй и третий входы блока 9 расчета частотного сдвига. В перемножителях 4 и 5 вычисляют квадраты откликов для синфазной и квадратурной составляющих входного цифрового комплексного сигнала первого этапа, которые поступают на первый и второй входы первого сумматора 6. В первом сумматоре 6 путем суммирования соответствующих квадратов откликов синфазной и квадратурной составляющих входного цифрового комплексного сигнала вычисляют квадраты модулей комплексных откликов первого этапа, формируя решающую функцию первого этапа. Отклики первого этапа поступают с выхода первого сумматора 6 на первый вход первого блока 10 сравнения с порогом.

В первом блоке 10 сравнения с порогом последовательно сравнивают результаты суммирования с выхода первого сумматора 6 с порогом первого этапа H1. Результаты сравнения с выхода первого блока 10 сравнения с порогом поступают на первый вход блока 9 расчета частотного сдвига и на первый вход блока 11 управления.

На второй вход первого блока 10 сравнения с порогом и на четвертый вход блока 9 расчета частотного сдвига с первого выхода блока 11 управления подают сигнал управления, соответствующий окончанию временной области превышения значениями решающей функции первого этапа порога H1. По этому сигналу в первом блоке 10 сравнения с порогом осуществляют установку первоначального (исходного) значения порога первого этапа и в блоке 9 расчета частотного сдвига запоминают синфазные и квадратурные составляющие комплексных откликов первого этапа, соответствующие локальному максимуму решающей функции первого этапа (поступившие на второй и третий входы блока 9 с согласованных фильтров 2 и 3).

В блоке 9 расчета частотного сдвига по сигналу превышения порога первого этапа и по управляющему сигналу окончания временной области превышения значениями решающей функции первого этапа порога H1 определяют временные положения, соответствующие локальным максимумам решающей функции первого этапа.

По сигналу окончания приема первой части преамбулы, который поступает с четвертого выхода блока 11 управления на пятый вход блока 9 расчета частотного сдвига, в блоке 9 по синфазным и квадратурным составляющим комплексных откликов первого этапа, соответствующим локальным максимумам решающей функции первого этапа, определяют предварительную оценку частотного сдвига. Предварительную оценку частотного сдвига формируют, например, как отношение усредненной разности фаз комплексных откликов первого этапа, соответствующих локальным максимумам, к длительности короткого многочастотного символа. Усредненную разность фаз формируют, например, следующим образом. Для временных позиций локальных максимумов решающей функции первого этапа формируют сумму произведений пар текущих комплексных откликов и предыдущих комплексно-сопряженных откликов. Значение аргумента полученного комплексного числа равно усредненной разности фаз. При этом отношение усредненной разности фаз к длительности короткого многочастотного символа равно предварительной оценке частотного сдвига.

Оценку предварительного частотного сдвига подают с выхода блока 9 расчета частотного сдвига на первый вход блока 8 формирования гармоники и на первый вход третьего сумматора 20, и она соответствует значению предварительной оценки частотной расстройки. На второй вход блока 8 формирования гармоники и на второй вход блока 11 управления с выхода тактового генератора 12 подают сигнал тактовой частоты.

В блоке 8 формирования гармоники по предварительной оценке частотного сдвига и сигналу с тактового генератора 12 формируют комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временное положение текущих отсчетов, что соответствует стандартному экспоненциальному представлению комплексного множителя. Альтернативно, комплексный множитель может быть эквивалентно сформирован в виде синфазной и квадратурной компоненты. В этом случае синфазная часть комплексного множителя равна косинусу, а мнимая часть - синусу аргумента, который равен произведению предварительной оценки частотного сдвига на временное положение текущих отсчетов. Данное представление комплексного множителя легко реализуется в функциональном преобразователе на базе устройства памяти, в котором записаны значения соответствующих отсчетов функций синуса и косинуса.

Сформированные квадратурные составляющие комплексного множителя с первого и второго выходов блока 8 формирования гармоники подают соответственно на третий и четвертый входы комплексного перемножителя 7.

В комплексном перемножителе 7 корректируют фазу входного цифрового комплексного сигнала для второго этапа синхронизации с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, полученной на первом этапе. Для этого в комплексном перемножителе 7 осуществляют известную операцию умножения отсчетов входного цифрового комплексного сигнала на комплексный множитель.

Синфазную и квадратурную составляющие скорректированного входного цифрового комплексного сигнала с первого и второго выходов комплексного перемножителя 7 подают соответственно на входы третьего 13 и четвертого 14 согласованных фильтров.

В согласованных фильтрах 13 и 14 для синфазной и квадратурной составляющих входного скорректированного цифрового комплексного сигнала осуществляют фильтрацию, согласованную с одним длинным многочастотным символом, и формируют соответственно синфазные и квадратурные отклики второго этапа. Сформированные синфазные и квадратурные составляющие откликов второго этапа с выходов согласованных фильтров 13 и 14 подают соответственно на первый и второй входы третьего 15 (синфазного) и четвертого 16 (квадратурного) перемножителей и на второй и третий входы блока 19 расчета дополнительного частотного сдвига. В перемножителях 15 и 16 формируют соответственно квадраты синфазной и квадратурной составляющих откликов второго этапа, которые поступают на первый и второй вход второго сумматора 17, где путем их суммирования вычисляют квадраты модулей комплексных откликов второго этапа, получая решающую функцию второго этапа. Вычисленные квадраты модулей комплексных откликов второго этапа с выхода второго сумматора 17 подают на первый вход второго блока 18 сравнения с порогом.

Во втором блоке 18 сравнения с порогом сравнивают значения квадратов модулей комплексных откликов второго этапа с порогом второго этапа Н2. Результат сравнения с выхода второго блока 18 сравнения с порогом подают на третий вход блока 11 управления и на пятый вход блока 19 расчета дополнительного частотного сдвига.

При непревышении порога Н2 полагают преамбулу необнаруженной и продолжают процедуру частотно-временной синхронизации.

При превышении порога Н2 полагают преамбулу обнаруженной. При этом по сигналам превышения порога в блоке 11 управления определяют оценку временного положения преамбулы как временное положение первого превышения порога второго этапа Н2. Полученную оценку со второго выхода блока 11 управления подают на первый выход устройства.

Окончательную оценку временного положения преамбулы определяют равной разности временного положения первого превышения порога второго этапа Н2 и суммы длительностей первой части преамбулы и префикса.

С пятого выхода блока 11 управления на второй вход второго блока 18 сравнения с порогом и на четвертый вход блока 19 расчета дополнительного частотного сдвига подают сигнал окончания приема второй части преамбулы, равный, например, логической единице.

В блоке 19 расчета дополнительного частотного сдвига по сигналу превышения порога и по управляющему сигналу окончания временной области превышения значениями решающей функции порога второго этапа определяют временные положения, соответствующие локальным максимумам решающей функции второго этапа.

В блоке 19 расчета дополнительного частотного сдвига по сигналу окончания приема второй части преамбулы синфазные и квадратурные составляющие комплексных откликов второго этапа, соответствующие локальным максимумам решающей функции второго этапа, используют для определения дополнительного частотного сдвига.

Оценку выполняют, например, следующим образом. Формируют разность фаз двух комплексных откликов второго этапа, соответствующих локальным максимумам, как произведение комплексно-сопряженного отклика на последующий комплексный отклик. В результате аргумент полученного комплексного числа соответствует оценке дополнительного фазового сдвига. Дополнительную оценку частотного сдвига определяют, например, как отношение оценки дополнительного фазового сдвига к длительности длинного многочастотного символа. Дополнительную оценку частотного сдвига с выхода блока 19 подают на второй вход третьего сумматора 20. В третьем сумматоре 20 определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценок частотного сдвига. Полученную окончательную оценку с выхода третьего сумматора 20 подают на второй выход устройства.

К недостаткам способа-прототипа и устройства следует отнести отказ от предварительной оценки временного положения сигнала и, как следствие, от использования некогерентной обработки на первом этапе. Указанный недостаток обуславливает недостаточно высокую помехоустойчивость оценки временного положения и частотного рассогласования, особенно в условиях многолучевого распространения сигнала. Наличие префикса во второй части преамбулы может привести к возникновению аномальной ошибки при оценке временного положения на втором этапе.

Задача, которую решают предлагаемые изобретения, - это повышение помехоустойчивости частотно-временной синхронизации системы связи.

Эта задача решается тем, что в способе частотно-временной синхронизации системы связи, заключающемся в том, что

входной сигнал фильтруют, усиливают, выполняют автоматическую регулировку усиления, вычисляя коэффициент усиления входного сигнала в зависимости от уровня мощности входного сигнала, переносят на видеочастоту, осуществляют его аналогово-цифровое преобразование и децимацию, формируя входной цифровой комплексный сигнал на видеочастоте,

частотно-временную синхронизацию выполняют в два этапа:

на первом этапе определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего:

- осуществляют согласованную с одним коротким многочастотным символом фильтрацию входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа,

- вычисляют квадраты модулей комплексных откликов первого этапа,

- осуществляют сравнение с заданным порогом первого этапа,

- определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала,

на втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего:

- корректируют фазу входного цифрового комплексного сигнала на интервале работы второго этапа с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала,

- осуществляют согласованную с одним длинным многочастотным символом фильтрацию скорректированного по фазе входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа,

- вычисляют квадраты модулей комплексных откликов второго этапа,

- осуществляют сравнение с заданным порогом второго этапа, при непревышении порога полагают преамбулу необнаруженной,

- при превышении порога второго этапа полагают преамбулу обнаруженной, тогда определяют окончательную оценку временного положения преамбулы по временному положению первого превышения порога второго этапа,

- определяют оценку временного положения преамбулы по временному положению первого превышения порога второго этапа,

- определяют дополнительную оценку частотного сдвига по разности фаз комплексных откликов второго этапа,

определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига,

согласно изобретению:

при выполнении первого этапа частотно-временной синхронизации определяют предварительную оценку временного положения второй части преамбулы, для чего:

вычисляют коэффициент коррекции уровня мощности сформированного входного сигнала,

корректируют сформированный входной цифровой комплексный сигнал, используя вычисленный коэффициент коррекции уровня мощности сформированного входного сигнала,

формируя комплексные отклики первого этапа, осуществляют фильтрацию скорректированного входного цифрового комплексного сигнала,

запоминают комплексные отклики первого этапа,

вычисляют суммы N квадратов модулей комплексных откликов первого этапа, взятых с интервалом, равным длительности короткого многочастотного символа,

сравнивают полученные суммы с заданным порогом первого этапа, при превышении порога:

временное положение начала преамбулы, соответствующее полученной сумме, полагают текущим временным положением преамбулы,

формируют текущую оценку частотного сдвига по усредненной разности фаз смежных комплексных откликов первого этапа с n-го по (N-n+1)-й, соответствующих слагаемым суммирования, где n - целое число,  ,

,

порог первого этапа устанавливают равным полученной сумме,

если произошло хотя бы одно превышение порога первого этапа, а затем не происходит превышение порога первого этапа с момента времени последнего превышения порога в течение интервала, равного длительности короткого многочастотного символа, то

определяют предварительную оценку временного положения второй части преамбулы по текущему временному положению преамбулы,

предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала определяют как текущую оценку частотного сдвига,

порог первого этапа полагают равным первоначальному значению, а текущее временное положение преамбулы считают неопределенным;

на втором этапе осуществляют окончательную оценку временного положения преамбулы, для чего:

определяют априорный интервал временного положения второй части преамбулы по предварительной оценке временного положения второй части преамбулы,

квадраты модулей комплексных откликов второго этапа сравнивают с заданным порогом второго этапа на априорном интервале временного положения второй части преамбулы,

по временному положению первого превышения порога второго этапа оценку временного положения преамбулы определяют как окончательную,

находят комплексные спектры длинных многочастотных символов скорректированного по фазе входного цифрового комплексного сигнала, временные положения которых определяются по временному положению первого превышения порога второго этапа,

дополнительную оценку частотного сдвига определяют по усредненной разности фаз соответствующих элементов комплексных спектров длинных многочастотных символов.

Сформированный входной цифровой комплексный сигнал корректируют, например, путем умножения на отношение коэффициента усиления приемного тракта, при котором произошло первое превышение порога первого этапа, на текущий коэффициент усиления приемного тракта; если не произошло ни одного превышения порога первого этапа, то сформированный входной цифровой комплексный сигнал умножают на коэффициент, равный единице.

Текущую оценку частотного сдвига формируют, например, как отношение усредненной разности фаз комплексных откликов первого этапа к длительности короткого многочастотного символа.

Начало априорного интервала временного положения второй части преамбулы определяют, например, равным сумме предварительной оценки временного положения второй части преамбулы, длительности (N-2)-х коротких многочастотных символа и длительности префикса, где N - количество коротких многочастотных символов в преамбуле.

Окончание априорного интервала временного положения второй части преамбулы определяют, например, равным сумме предварительной оценки временного положения второй части преамбулы, длительности (N+2)-x коротких многочастотных символа и длительности префикса, где N - количество коротких многочастотных символов в преамбуле.

Фазу входного цифрового комплексного сигнала на интервале работы второго этапа корректируют, умножая отсчеты входного цифрового комплексного сигнала на комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временные положения отсчетов.

Дополнительную оценку частотного сдвига определяют, например, как отношение усредненной разности фаз соответствующих элементов комплексных спектров длинных многочастотных символов к длительности длинного многочастотного символа.

Окончательную оценку временного положения преамбулы, а именно начала преамбулы, определяют равной разности временного положения первого превышения порога второго этапа и суммы длительностей первой части преамбулы и префикса.

Поставленная задача решается также тем, что в устройство частотно-временной синхронизации системы связи, содержащее

приемный тракт, формирующий на выходах входной цифровой комплексный сигнал на видеочастоте, первый и второй согласованные фильтры, осуществляющие согласованную с одним коротким многочастотным символом фильтрацию соответственно синфазной и квадратурной компоненты сформированного входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа, первый и второй перемножители, первый сумматор, комплексный перемножитель, блок формирования гармоники, блок расчета частотного сдвига, блок сравнения с порогом, блок управления, тактовый генератор, формирующий на выходе сигнал тактовых импульсов, третий и четвертый согласованные фильтры, осуществляющие согласованную с одним длинным многочастотным символом фильтрацию скорректированного по фазе входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа, третий и четвертый перемножители, второй сумматор, блок расчета дополнительного частотного сдвига и третий сумматор, при этом вход приемного тракта является входом устройства, первый и второй выходы приемного тракта соединены соответственно с первым и вторым входами комплексного перемножителя, выходы первого и второго перемножителей соединены соответственно с первым и вторым входами первого сумматора, выход которого соединен с первым входом блока сравнения с порогом, второй вход которого соединен с первым выходом блока управления, выход блока сравнения с порогом соединен с первым входом блока расчета частотного сдвига, выход которого соединен с первым входом блока формирования гармоники и первым входом третьего сумматора, второй вход блока формирования гармоники соединен с выходом тактового генератора, первый и второй выходы блока формирования гармоники соединены соответственно с третьим и четвертым входами комплексного перемножителя, первый и второй выходы которого соединены соответственно со входами третьего и четвертого согласованных фильтров, выход третьего согласованного фильтра соединен с первым и вторым входами третьего перемножителя, выход четвертого согласованного фильтра соединен с первым и вторым входами четвертого перемножителя, выходы третьего и четвертого перемножителей соединены соответственно с первым и вторым входами второго сумматора, второй выход блока управления является первым выходом устройства, формирующего на этом выходе сигнал оценки временного положения преамбулы, третий выход блока управления соединен с первым входом блока расчета дополнительного частотного сдвига, выход которого соединен со вторым входом третьего сумматора, формирующего на выходе сигнал окончательной оценки частотного сдвига, выход третьего сумматора является вторым выходом устройства,

согласно изобретению дополнительно введены:

пятый и шестой перемножители для коррекции уровня мощности сформированного входного сигнала,

блок расчета коэффициента коррекции уровня мощности сформированного входного сигнала,

первая и вторая линии задержки,

(N-1) первых и (N-1) вторых перемножителей,

блок определения границ априорного интервала, формирующий на первом выходе сигнал непревышения порога первого этапа с момента времени последнего превышения порога в течение интервала, равного длительности короткого многочастотного символа, на втором выходе - сигнал начала априорного интервала временного положения второй части преамбулы, на третьем выходе - сигнал окончания априорного интервала временного положения второй части преамбулы,

ключ,

компаратор,

при этом первый выход приемного тракта соединен с первым входом пятого перемножителя, второй выход приемного тракта соединен с первым входом шестого перемножителя, третий выход приемного тракта соединен с первым входом блока расчета коэффициента коррекции уровня мощности сформированного входного сигнала, второй вход которого объединен с первым входом блока определения границ априорного интервала и соединен с выходом блока сравнения с порогом,

выход блока расчета коэффициента коррекции уровня мощности сформированного входного сигнала соединен со вторыми входами пятого и шестого перемножителей,

выход пятого перемножителя соединен со входом первого согласованного фильтра, осуществляющего фильтрацию скорректированного входного цифрового комплексного сигнала, выход первого согласованного фильтра соединен со входом первой линии задержки,

выход шестого перемножителя соединен со входом второго согласованного фильтра, выход которого соединен со входом второй линии задержки,

N выходов первой линии задержки соединены с соответствующими им N первыми и N вторыми входами соответствующих им N первых перемножителей и N вторыми входами блока расчета частотного сдвига, выходы (N-1) первых перемножителей соединены с (N-1) дополнительными первыми входами первого сумматора,

N выходов второй линии задержки соединены с соответствующими им N первыми и N вторыми входами соответствующих им N вторых перемножителей и N третьими входами блока расчета частотного сдвига, выходы (N-1) вторых перемножителей соединены с (N-1) дополнительными вторыми входами первого сумматора, формирующего на выходе сумму N квадратов модулей комплексных откликов первого этапа,

второй и третий входы блока расчета дополнительного частотного сдвига соединены соответственно с первым и вторым выходами комплексного перемножителя,

второй вход блока определения границ априорного интервала и четвертый вход блока расчета дополнительного частотного сдвига объединены и соединены с выходом тактового генератора,

первый вход блока управления и третий вход блока сравнения с порогом объединены и соединены с первым выходом блока определения границ априорного интервала, второй и третий выходы которого соединены соответственно со вторым и третьим входами блока управления, формирующего на первом выходе сигнал управления, определяющий момент окончания или повторного запуска выполнения первого этапа, на третьем - сигнал наличия хотя бы одного превышения порога второго этапа, на четвертом выходе - сигнал управления, определяющий временной интервал, когда текущая временная задержка находится внутри априорного интервала временного положения второй части преамбулы, четвертый выход блока управления соединен с первым входом ключа,

второй вход ключа соединен с выходом второго сумматора, а выход - со входом компаратора, выход которого соединен с четвертым входом блока управления, второй выход которого соединен с пятым входом блока расчета дополнительного частотного сдвига.

Заявляемые способ частотно-временной синхронизации системы связи и устройство для его осуществления имеют существенные отличия от наиболее близких аналогов, обнаруженных при поиске из известного уровня техники.

Эти отличия заключаются в следующем: оценку временного положения сигнала преамбулы осуществляют в два этапа, причем на первом этапе формируют решающую функцию с широким полезным откликом, что увеличивает вероятность захвата успешной предварительной оценки временного положения, на втором этапе формируют решающую функцию с узким полезным откликом, что позволяет получить точную оценку временного положения сигнала преамбулы. Оценку частотного сдвига формируют также в два этапа, причем качество этой оценки - высокое, поскольку базируется на качественной оценке временного положения.

Изобретения поясняются примерами выполнения и чертежами:

На Фиг.1 показана структура преамбулы OFDM (Orthogonal Frequency Division Multiplexing) сигнала.

На Фиг.2 приведена структурная схема устройства-прототипа.

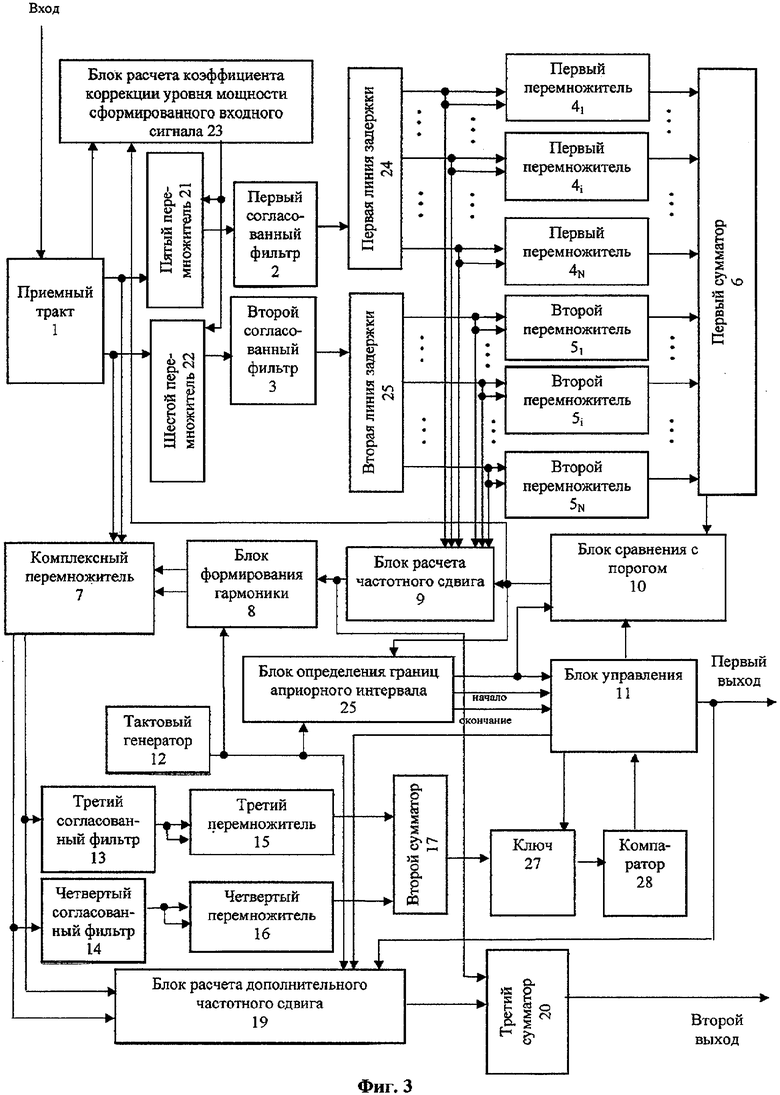

На Фиг.3 приведена структурная схема заявляемого устройства.

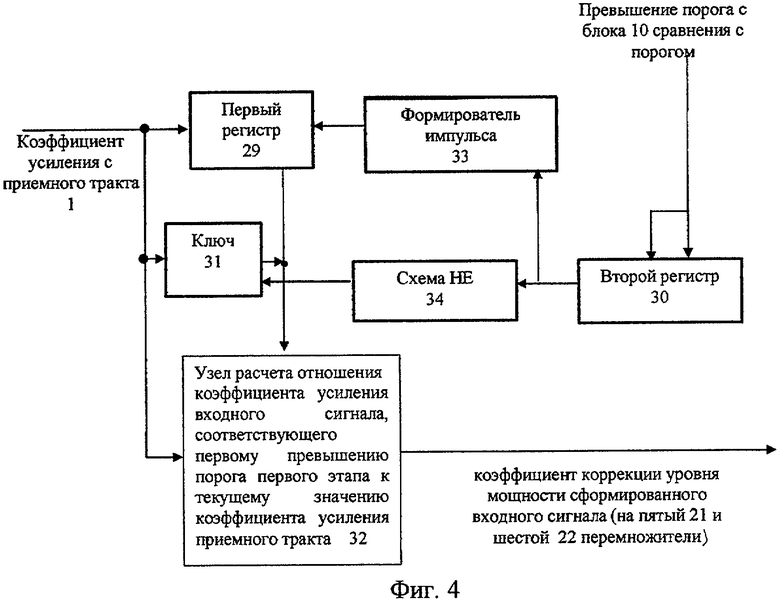

На Фиг.4 приведена структурная схема блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала.

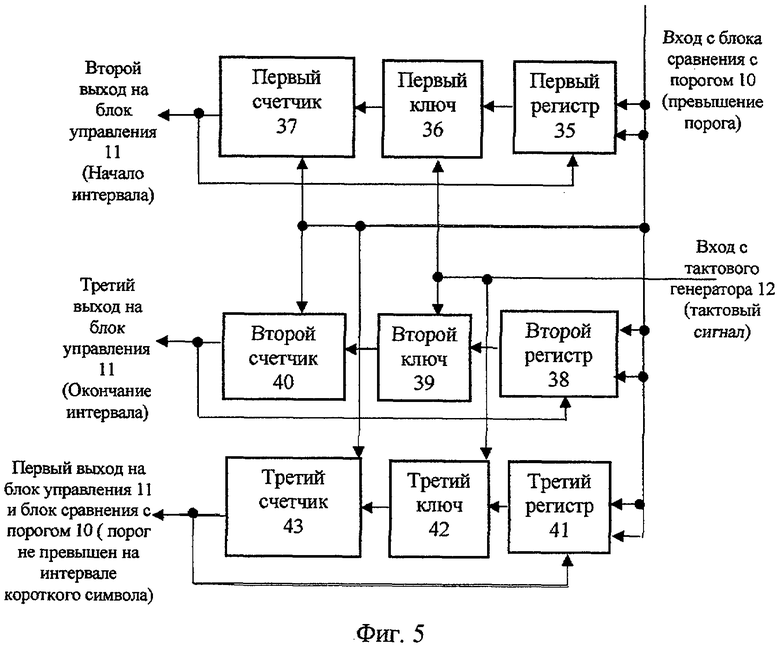

На Фиг.5 приведена структурная схема блока 25 определения границ априорного интервала,

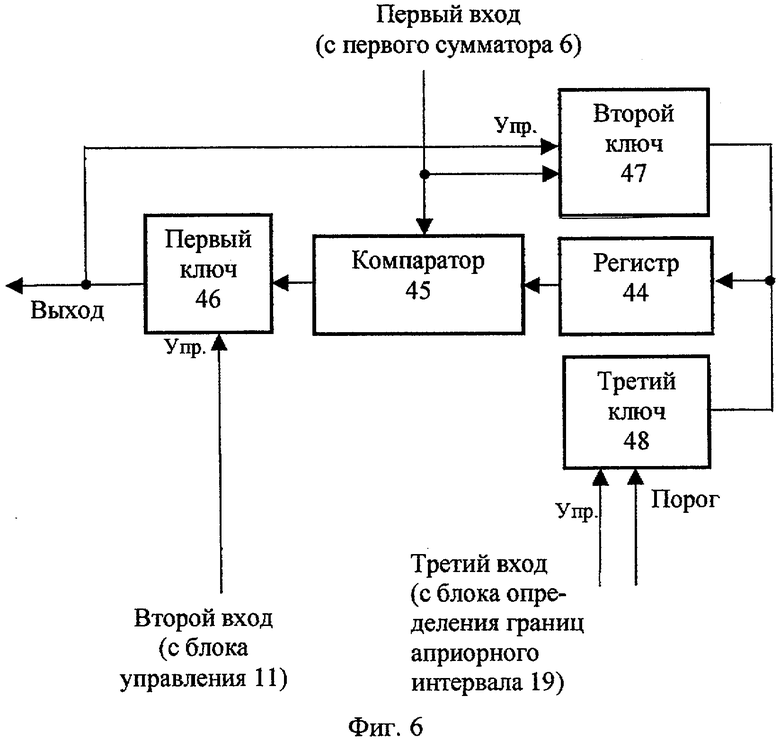

На Фиг.6 приведена структурная схема блока 10 сравнения с порогом.

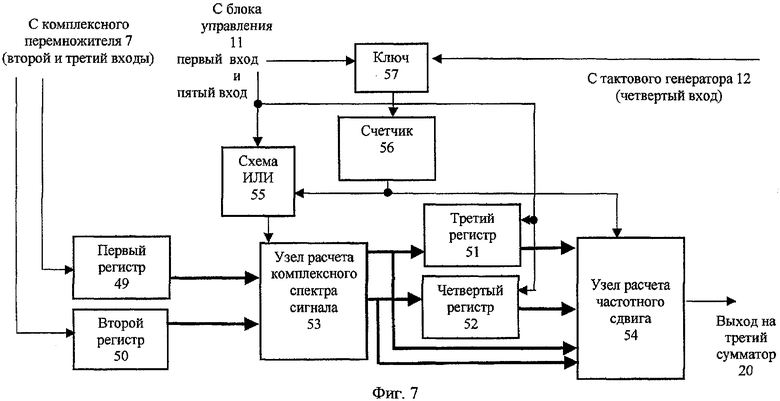

На Фиг.7 приведена структурная схема блока 19 расчета дополнительного частотного сдвига.

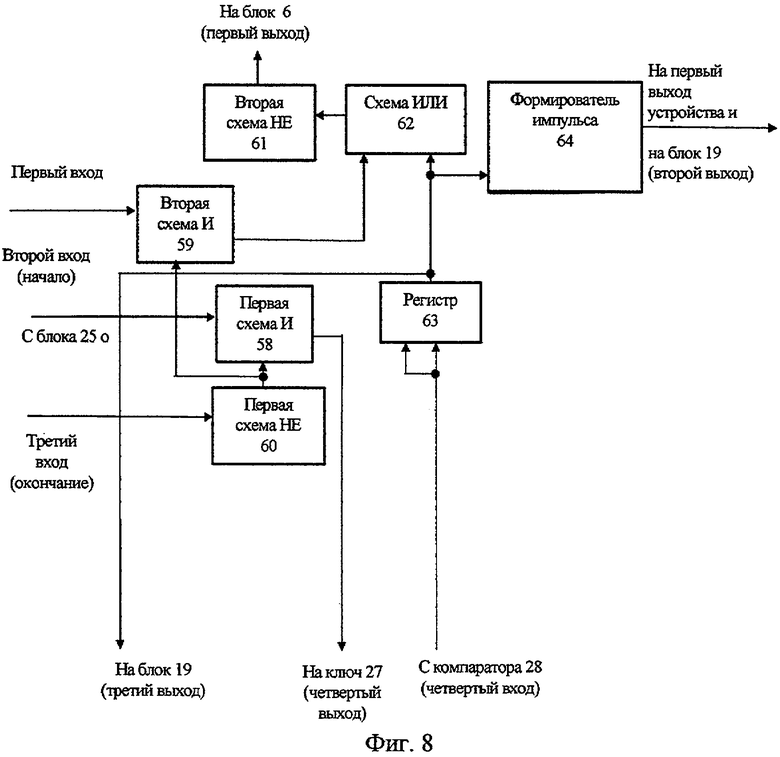

На Фиг.8 приведена структурная схема блока 11 управления.

Заявляемое устройство частотно-временной синхронизации (Фиг.3) содержит приемный тракт 1, первый 2 и второй 3 согласованные фильтры, первый 41 и второй 51 перемножители, первый сумматор 6, комплексный перемножитель 7, блок 8 формирования гармоники, блок 9 расчета частотного сдвига, блок 10 сравнения с порогом, блок 11 управления, тактовый генератор 12, третий 13 и четвертый 14 согласованные фильтры, третий 15 и четвертый 16 перемножители, второй сумматор 17, блок 19 расчета дополнительного частотного сдвига и третий сумматор 20, при этом вход приемного тракта 1 является входом устройства, первый и второй выходы приемного тракта 1 соединены соответственно с первым и вторым входами комплексного перемножителя 7, выходы первого 41 и второго 51 перемножителей соединены соответственно с первым и вторым входами первого сумматора 6, выход которого соединен с первым входом блока 10 сравнения с порогом, второй вход которого соединен с первым выходом блока 11 управления, выход блока 10 сравнения с порогом соединен с первым входом блока 9 расчета частотного сдвига, выход которого соединен с первым входом блока 8 формирования гармоники и первым входом третьего сумматора 20, второй вход блока 8 формирования гармоники соединен с выходом тактового генератора 12, первый и второй выходы блока 8 формирования гармоники соединены соответственно с третьим и четвертым входами комплексного перемножителя 7, первый и второй выходы которого соединены соответственно со входами третьего 13 и четвертого 14 согласованных фильтров, выход третьего согласованного фильтра 13 соединен с первым и вторым входами третьего перемножителя 15, выход четвертого согласованного фильтра 14 соединен с первым и вторым входами четвертого перемножителя 16, выходы третьего 15 и четвертого 16 перемножителей соединены соответственно с первым и вторым входами второго сумматора 17, второй выход блока 11 управления является первым выходом устройства, третий выход блока 11 управления соединен с первым входом блока 19 расчета дополнительного частотного сдвига, выход которого соединен со вторым входом третьего сумматора 20, выход третьего сумматора 20 является вторым выходом устройства, согласно изобретению дополнительно содержит: пятый 21 и шестой 22 перемножители, блок 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала, первая 24 и вторая 25 линии задержки, (N-1) первых 4i-4N и (N-1) вторых 5i-5N перемножителей, блок 25 определения границ априорного интервала, ключ 27 и компаратор 28, при этом первый выход приемного тракта 1 соединен с первым входом пятого перемножителя 21, второй выход приемного тракта 1 соединен с первым входом шестого перемножителя 22, третий выход приемного тракта 1 соединен с первым входом блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала, второй вход которого объединен с первым входом блока 25 определения границ априорного интервала и соединен с выходом блока 10 сравнения с порогом, выход блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала соединен с объединенными вторыми входами пятого 21 и шестого 22 перемножителей, выход пятого перемножителя 22 соединен со входом первого согласованного фильтра 2, выход которого соединен со входом первой линии задержки 24, выход шестого перемножителя 22 соединен со входом второго согласованного фильтра 3, выход которого соединен со входом второй линии задержки 25, N выходов первой линии задержки 24 соединены с соответствующими им N первыми и N вторыми входами соответствующих им N первых перемножителей 41-4N и N вторыми входами блока 9 расчета частотного сдвига, выходы (N-1) первых перемножителей соединены с (N-1) дополнительными первыми входами первого сумматора 6, N выходов второй линии задержки 25 соединены с соответствующими им N первыми и N вторыми входами соответствующих им N вторых перемножителей 51-5N и N третьими входами блока 9 расчета частотного сдвига, выходы (N-1) вторых перемножителей соединены с (N-1) дополнительными вторыми входами первого сумматора 6, второй и третий входы блока 19 расчета дополнительного частотного сдвига соединены соответственно с первым и вторым выходами комплексного перемножителя 7, второй вход блока 25 определения границ априорного интервала и четвертый вход блока 19 расчета дополнительного частотного сдвига объединены и соединены с выходом тактового генератора 12, первый вход блока 11 управления и третий вход блока 10 сравнения с порогом объединены и соединены с первым выходом блока 25 определения границ априорного интервала, второй и третий выходы которого соединены соответственно со вторым и третьим входами блока 11 управления, четвертый выход которого соединен с первым входом ключа 27, второй вход ключа 27 соединен с выходом второго сумматора 17, а выход - со входом компаратора 28, выход которого соединен с четвертым входом блока 11 управления, второй выход которого соединен с пятым входом блока 19 расчета дополнительного частотного сдвига.

Блок 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала (Фиг.4) содержит первый 29 и второй 30 регистры, ключ 31, узел расчета отношения коэффициента усиления входного сигнала, соответствующего первому превышению порога первого этапа, к текущему значению коэффициента усиления приемного тракта 32, формирователь 33 импульса и схему 34 "НЕ", при этом первые входы первого регистра 29, ключа 31 и вход узла 32 объединены, образуя первый вход блока 23, второй вход первого регистра 29 соединен с выходом формирователя 33 импульса, вход которого объединен с входом схемы 34 «НЕ» и соединен с выходом второго регистра 30, первый и второй входы которого объединены, образуя второй вход блока 23, выход схемы 34 «НЕ» соединен со вторым входом ключа 31, выходы ключа 31 и первого регистра 29 соединены со вторым входом узла 32 расчета отношения коэффициента усиления входного сигнала, соответствующего первому превышению порога первого этапа, к текущему значению коэффициента усиления приемного тракта, выход которого является выходом блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала.

Блок 25 определения границ априорного интервала (Фиг.5) содержит последовательно соединенные первый регистр 35, первый ключ 36 и первый счетчик 37, последовательно соединенные второй регистр 38, второй ключ 39 и второй счетчик 40, последовательно соединенные третий регистр 41, третий ключ 42 и третий счетчик 43, при этом первый и второй входы первого 35, второго 38 и третьего 41 регистров, вторые входы первого 37, второго 40 и третьего 43 счетчиков объединены, образуя первый вход блока 25, вторые входы первого ключа 36, второго ключа 39 и третьего ключа 42 объединены, образуя второй вход блока 25, выход первого счетчика 37 является вторым выходом блока 25 и соединен с третьим входом первого регистра 35, выход второго счетчика 40 является вторым выходом блока 25 и соединен с третьим входом второго регистра 38, выход третьего счетчика 43 является первым выходом блока 25 и соединен с третьим входом третьего регистра 41.

Блок 10 сравнения с порогом (Фиг.6) содержит последовательно соединенные регистр 44, компаратор 45 и первый ключ 46, второй ключ 47 и третий ключ 48, при этом второй вход компаратора 45 и первый вход второго ключа 47 объединены, образуя первый вход блока 10 сравнения с порогом, второй вход первого ключа 46 образует второй вход блока 10, вход третьего ключа 48 является третьим входом блока 10, выход первого ключа 46 является выходом блока 10 сравнения с порогом и соединен со вторым входом второго ключа 47, выходы ключей 47 и 48 соединены со входом регистра 44.

Блок 19 расчета дополнительного частотного сдвига (Фиг.7) содержит первый 49, второй 50, третий 51 и четвертый 52 регистры, узел 53 расчета комплексного спектра сигнала, узел 54 расчета частотного сдвига, схему 55 «ИЛИ», счетчик 56 и ключ 57, при этом входы регистров 49 и 50 образуют соответственно второй и третий входы блока 19 расчета дополнительного частотного сдвига, выходы регистров 49 и 50 соединены соответственно с первым и вторым входами узла 53 расчета комплексного спектра сигнала, третий вход которого соединен с выходом схемы 55 «ИЛИ», первый выход узла 53 соединен с первыми входами третьего регистра 51 и узла 54 расчета частотного сдвига, второй выход узла 53 соединен с первым входом четвертого регистра 52 и вторым входом узла 54 расчета частотного сдвига, третий и четвертый входы которого соединены соответственно с выходами регистров 51 и 52, выход узла 54 расчета частотного сдвига является выходом блока 19 расчета дополнительного частотного сдвига, пятый вход узла 54 расчета частотного сдвига и второй вход схемы 55 "ИЛИ" объединены и соединены с выходом счетчика 56, вход которого соединен с выходом ключа 57, первый и второй входы которого соответственно образуют четвертый и первый входы блока 19 расчета дополнительного частотного сдвига, вход схемы 55 «ИЛИ» является пятым входом блока 19.

Блок 11 управления (Фиг.8) содержит первую 58 и вторую 59 схемы «И», первую 60 и вторую 61 схемы «НЕ», схему 62 «ИЛИ», регистр 63 и формирователь 64 импульса, при этом первые входы первой схемы 58 «И» и второй схемы 59 «И» являются соответственно вторым и первым входами блока 11 управления, вход первой схемы 60 «НЕ» является третьим входом блока 11 управления, вторые входы первой 58 и второй 59 схем «И» объединены и соединены с выходом первой схемы 60 «НЕ», выход первой схемы 58 «И» является четвертым выходом блока 11 управления, выход второй схемы 59 «И» соединен с первым входом схемы 62 «ИЛИ», выход которой соединен со входом второй схемы 61 «НЕ», выход которой образует первый выход блока 11 управления, первый и второй входы регистра 63 образуют четвертый вход блока 11 управления, выход регистра 63 является третьим выходом блока 11 управления и соединен с объединенными вторым входом схемы 62 «ИЛИ» и входом формирователя 64 импульса, выход которого образует второй выход блока 11 управления и соответственно первый выход устройства.

Осуществляют заявляемый способ частотно-временной синхронизации системы связи следующим образом:

входной сигнал фильтруют, усиливают, выполняют автоматическую регулировку усиления, вычисляя коэффициент усиления входного сигнала в зависимости от уровня мощности входного сигнала, переносят на видеочастоту, осуществляют его аналогово-цифровое преобразование и децимацию, формируя входной цифровой комплексный сигнал на видеочастоте;

- частотно-временную синхронизацию выполняют в два этапа, при этом на первом этапе определяют предварительную оценку временного положения второй части преамбулы и предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего:

вычисляют коэффициент коррекции уровня мощности сформированного входного сигнала,

корректируют сформированный входной цифровой комплексный сигнал, используя вычисленный коэффициент коррекции уровня мощности сформированного входного сигнала,

осуществляют согласованную с одним коротким многочастотным символом фильтрацию скорректированного входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа,

запоминают комплексные отклики первого этапа,

вычисляют квадраты модулей комплексных откликов первого этапа,

вычисляют суммы N квадратов модулей комплексных откликов первого этапа, взятых с интервалом, равным длительности короткого многочастотного символа,

сравнивают полученные суммы с заданным порогом первого этапа, при превышении порога:

временное положение начала преамбулы, соответствующее полученной сумме, полагают текущим временным положением преамбулы,

формируют текущую оценку частотного сдвига по усредненной разности фаз смежных комплексных откликов первого этапа с n-го по (N-n+1)-ый, соответствующих слагаемым суммирования, где n - целое число,  ,

,

порог первого этапа устанавливают равным полученной сумме,

если произошло хотя бы одно превышение порога первого этапа, а затем не происходит превышение порога первого этапа с момента времени последнего превышения порога в течение интервала, равного длительности короткого многочастотного символа, то

определяют предварительную оценку временного положения второй части преамбулы по текущему временному положению преамбулы,

определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как текущую оценку частотного сдвига,

порог первого этапа полагают равным первоначальному значению, а текущее временное положение преамбулы считают неопределенным;

переходят ко второму этапу,

- на втором этапе осуществляют окончательную оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего:

определяют априорный интервал временного положения второй части преамбулы по предварительной оценке временного положения второй части преамбулы,

корректируют фазу входного цифрового комплексного сигнала на интервале работы второго этапа с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала,

осуществляют согласованную с одним длинным многочастотным символом фильтрацию скорректированного по фазе входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа,

вычисляют квадраты модулей комплексных откликов второго этапа,

сравнивают квадраты модулей комплексных откликов второго этапа с заданным порогом второго этапа на априорном интервале временного положения второй части преамбулы, при непревышении порога полагают преамбулу необнаруженной,

при превышении порога второго этапа полагают преамбулу обнаруженной, тогда

определяют окончательную оценку временного положения преамбулы по временному положению первого превышения порога второго этапа,

находят комплексные спектры длинных многочастотных символов скорректированного по фазе входного цифрового комплексного сигнала, временные положения которых определяются по временному положению первого превышения порога второго этапа,

определяют дополнительную оценку частотного сдвига по усредненной разности фаз соответствующих элементов комплексных спектров длинных многочастотных символов,

определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига.

Сформированный входной цифровой комплексный сигнал корректируют, например, путем умножения на отношение коэффициента усиления приемного тракта, при котором произошло первое превышение порога первого этапа, на текущий коэффициент усиления приемного тракта; если не произошло ни одного превышения порога первого этапа, то сформированный входной цифровой комплексный сигнал умножают на коэффициент, равный единице.

Текущую оценку частотного сдвига формируют, например, как отношение усредненной разности фаз комплексных откликов первого этапа к длительности короткого многочастотного символа.

Начало априорного интервала временного положения второй части преамбулы определяют, например, равным сумме предварительной оценки временного положения второй части преамбулы, длительности (N-1)-х коротких многочастотных символов и длительности префикса, где N - количество коротких многочастотных символов в преамбуле.

Окончание априорного интервала временного положения второй части преамбулы определяют, например, равным сумме предварительной оценки временного положения второй части преамбулы, длительности (N+2)-x коротких многочастотных символов и длительности префикса, где N - количество коротких многочастотных символов в преамбуле.

Фазу входного цифрового комплексного сигнала на интервале работы второго этапа корректируют, умножая отсчеты входного цифрового комплексного сигнала на комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временные положения отсчетов.

Дополнительную оценку частотного сдвига определяют, например, как отношение усредненной разности фаз соответствующих элементов комплексных спектров длинных многочастотных символов к длительности длинного многочастотного символа.

Окончательную оценку временного положения преамбулы, а именно начала преамбулы, определяют равной разности временного положения, соответствующего первому превышению порога второго этапа, и суммы длительностей первой части преамбулы и префикса.

Заявляемый способ реализуют на устройстве частотно-временной синхронизации системы связи, структурная схема которого приведена на Фиг.3.

Сигнал преамбулы используют для частотно-временной синхронизации, которая состоит из двух этапов. При этом на первом этапе определяют предварительную оценку временного положения второй части преамбулы и предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала. На втором этапе осуществляют окончательную оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала.

В приемном тракте 1 входной сигнал, который поступает на его вход, предварительно фильтруют, усиливают, выполняют автоматическую регулировку усиления, вычисляя коэффициент усиления входного сигнала в зависимости от уровня мощности входного сигнала, переносят на видеочастоту, осуществляют его аналогово-цифровое преобразование, децимацию и т.д. В результате чего формируют входной цифровой комплексный сигнал на видеочастоте.

Синфазная и квадратурная составляющие входного цифрового сигнала с первого и второго выхода приемного тракта 1 поступают соответственно на первый и второй входы комплексного перемножителя 7 и соответственно на первые входы пятого 21 и шестого 22 перемножителей.

Коэффициент усиления входного сигнала или величина, пропорциональная коэффициенту усиления, (которые изменяются в процессе приема сигнала под действием системы автоматической регулировки усиления) с третьего выхода приемного тракта 1 поступает на первый вход блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала, на второй вход которого поступает сигнал с выхода блока 10 сравнения с порогом.

Рассчитанный коэффициент коррекции уровня мощности сформированного входного сигнала с выхода блока 23 поступает на вторые входы пятого 21 и шестого 22 перемножителей.

С выхода пятого 21 и шестого 22 перемножителей скорректированные синфазная и квадратурная составляющие входного цифрового сигнала поступают на входы первого 2 и второго 3 согласованных фильтров.

В первом согласованном фильтре 2 осуществляют согласованную с одним коротким многочастотным символом фильтрацию синфазной компоненты входного сигнала. Во втором согласованном фильтре 3 осуществляют согласованную с одним коротким многочастотным символом фильтрацию квадратурной компоненты входного сигнала.

На выходах первого 2 и второго 3 согласованных фильтров формируют корреляционные отклики соответственно для синфазной и квадратурной составляющих входного цифрового комплексного сигнала, которые поступают соответственно на входы первой 24 и второй 25 линий задержки для синфазной и квадратурной составляющих сигнала.

В первой 24 и второй 25 линиях задержки запоминают (записывают) отклики соответственно для синфазной и квадратурной составляющих с дискретом, например, равным отношению длительности короткого многочастотного символа к количеству поднесущих на интервале длительности N коротких многочастотных символов. Каждая линия задержки соответственно для синфазной и квадратурной составляющих имеет N выходов.

В первых 41-4N и вторых 51-5N перемножителях вычисляют квадраты соответствующих откликов для синфазной и квадратурной составляющих первого этапа, которые поступают на соответствующие им первые и вторые входы первого сумматора 6.

В первом сумматоре 6 путем суммирования соответствующих квадратов синфазной и квадратурной составляющих откликов вычисляют сумму N квадратов модулей комплексных откликов первого этапа, взятых с интервалом, равным длительности короткого многочастотного символа, которые поступают на первый вход блока 10 сравнения с порогом. На второй вход блока 10 сравнения с порогом с первого выхода блока 11 управления подают сигнал управления, определяющий момент окончания или повторного запуска выполнения первого этапа. На третий вход блока 10 сравнения с порогом и первый вход блока 11 управления с первого выхода блока 25 определения границ априорного интервала подают сигнал непревышения порога первого этапа в течение длительности короткого многочастотного символа (после последнего превышения порога первого этапа), по которому осуществляют установку первоначального (исходного) значения порога первого этапа. Эта установка необходима для начала очередного цикла работы первого этапа синхронизации.

На второй вход блока 11 управления со второго выхода блока 25 определения границ априорного интервала подают сигнал начала априорного интервала временного положения второй части преамбулы.

В блоке 10 сравнения с порогом последовательно сравнивают результаты суммирования с выхода первого сумматора 6 с порогом первого этапа H1. Результаты сравнения с выхода блока 10 сравнения с порогом поступают на первый вход блока 25 определения границ априорного интервала, на первый вход блока 9 расчета частотного сдвига и на второй вход блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала.

При превышении порога первого этапа:

текущим временным положением преамбулы считают временное положение начала преамбулы, соответствующее результату суммирования;

в блоке 9 расчета частотного сдвига формируют текущую оценку частотного сдвига;

в блоке 25 определения границ априорного интервала определяют начало априорного интервала временного положения второй части преамбулы и окончание априорного интервала временного положения второй части преамбулы;

текущую оценку частотного сдвига формируют в блоке 9 расчета частотного сдвига по усредненной разности фаз комплексных откликов первого этапа, поступающих на вторые и третьи входы блока 9.

Усредненную разность фаз формируют, например, как сумму произведений комплексных откликов на комплексно-сопряженные соседние отклики. Причем (n-1) начальных и (n-1) последних корреляционных откликов не используют в формировании суммы. Значение аргумента полученного комплексного числа равно усредненной разности фаз. При этом отношение усредненной разности фаз к длительности короткого многочастотного символа равно оценке текущего частотного сдвига.

Оценка текущего частотного сдвига поступает с выхода блока 9 на первый вход блока 8 формирования гармоники и на первый вход третьего сумматора 20 и соответствует текущей предварительной («грубой») оценке частотной расстройки. На второй вход блока 8 формирования гармоники, на второй вход блока 25 определения границ априорного интервала и на четвертый вход блока 19 расчета дополнительного частотного сдвига с выхода тактового генератора 12 поступает сигнал тактовой частоты.

Начало априорного интервала временного положения второй части преамбулы определяют в блоке 25 определения границ априорного интервала, например, равным сумме предварительной оценки временного положения второй части преамбулы, соответствующего последнему превышению порога первого этапа (после которого не произошло ни одного превышения порога первого этапа в течение длительности короткого многочастотного символа), длительности (N-2)-х коротких многочастотных символов и длительности префикса. Начиная с момента начала априорного интервала временного положения второй части преамбулы сигнал, равный, например, логической единице, со второго выхода блока 25 определения границ априорного интервала поступает на второй вход блока 11 управления.

Окончание априорного интервала временного положения второй части преамбулы определяют в блоке 25 определения границ априорного интервала, например, равным сумме предварительной оценки временного положения второй части преамбулы, длительности (N+2)-x коротких многочастотных символов и длительности префикса. Сигнал окончания априорного интервала поступает с третьего выхода блока 25 определения границ априорного интервала на третий вход блока 11 управления.

После каждого превышения порога первого этапа его значение устанавливают в блоке 10 сравнения с порогом равным результату суммирования в первом сумматоре 6.

К моменту начала второго этапа в блоке 9 расчета частотного сдвига формируют предварительную оценку частотного сдвига между несущей входного сигнала и частотой опорного сигнала, которая равна последней текущей оценке частотного сдвига.

В блоке 8 формирования гармоники по предварительной оценке частотного сдвига и сигналу с тактового генератора 12 формируют комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временное положение текущих отсчетов. Квадратурные составляющие комплексного множителя с первого и второго выходов блока 8 формирования гармоники поступают соответственно на третий и четвертый входы комплексного перемножителя 7, в котором корректируют фазу входного цифрового комплексного сигнала на втором этапе. Для этого в комплексном перемножителе 7 осуществляют известную операцию умножения отсчетов входного цифрового комплексного сигнала на комплексный множитель.

В момент времени, соответствующий непревышению порога первого этапа, в течение длительности короткого символа (после последнего превышения порога первого этапа) в блоке 10 сравнения с порогом устанавливают порог первого этапа, равный первоначальному значению H1. С этого момента времени начинается второй этап, в течение которого осуществляют окончательную оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей входного сигнала и частотой опорного сигнала.

На интервале работы второго этапа в комплексном перемножителе 7 постоянно корректируют фазу входного цифрового комплексного сигнала с учетом предварительной оценки частотного сдвига между несущей входного сигнала и частотой опорного сигнала, полученной на первом этапе.

Синфазная и квадратурная составляющие входного цифрового комплексного сигнала, скорректированные по фазе, с первого и второго выходов комплексного перемножителя 7 поступают соответственно на входы третьего 13 и четвертого 14 согласованных фильтров и соответственно на второй и третий входы блока 19 расчета дополнительного частотного сдвига.

В третьем 13 и четвертом 14 согласованных фильтрах осуществляют согласованную фильтрацию с одним длинным многочастотным символом соответственно для синфазной и квадратурной составляющей входного скорректированного по фазе цифрового комплексного сигнала и формируют соответственно синфазные и квадратурные составляющие откликов второго этапа. Сформированные синфазные составляющие откликов второго этапа с выхода третьего согласованного фильтра 13 поступают на первые и вторые входы третьего перемножителя 15. Сформированные квадратурные составляющие откликов второго этапа с выхода четвертого согласованного фильтра 14 поступают на первый и второй входы четвертого перемножителя 16.

В третьем 15 и четвертом 16 перемножителях формируют соответственно квадраты синфазной и квадратурной составляющих откликов второго этапа, которые поступают соответственно на первый и второй вход второго сумматора 17, где путем их суммирования вычисляют квадраты модулей комплексных откликов второго этапа.

Вычисленные квадраты модулей комплексных откликов второго этапа с выхода второго сумматора 17 поступают на второй вход ключа 27. На первый вход ключа 27 с четвертого выхода блока 11 управления поступает сигнал управления, равный, например, логической единице, если текущая временная задержка находится внутри априорного интервала временного положения второй части преамбулы. С выхода ключа 27 квадраты модулей комплексных откликов второго этапа поступают на вход компаратора 28.

В компараторе 28 для временных задержек на априорном интервале временного положения второй части преамбулы сравнивают значения квадратов модулей комплексных откликов второго этапа с порогом второго этапа Н2. Результат сравнения с выхода компаратора 28 поступает на четвертый вход блока 11 управления.

При непревышении порога Н2 на априорном интервале временного положения второй части преамбулы полагают преамбулу необнаруженной, на первом выходе блока 11 управления формируют сигнал повторного запуска первого этапа, который поступает на второй вход блока 10 сравнения с порогом, и процедуру частотно-временной синхронизации повторяют, начиная с первого этапа.

При превышении порога Н2 (хотя бы однократном превышении) на априорном интервале временного положения второй части преамбулы преамбулу полагают обнаруженной. При этом по сигналам превышения порога в блоке 11 управления определяют окончательную оценку временного положения преамбулы как временное положение первого превышения порога второго этапа Н2. Полученная оценка со второго выхода блока 11 управления поступает на первый выход устройства и на пятый вход блока 19 расчета дополнительного частотного сдвига.

Окончательная оценка временного положения преамбулы (начало преамбулы) однозначно определяется временным положением первого превышения порога второго этапа Н2 и равна разности временного положения первого превышения порога второго этапа Н2 и суммы длительностей первой части преамбулы и префикса.

В блоке 19 расчета дополнительного частотного сдвига по управляющему сигналу наличия превышения порога второго этапа и по управляющему сигналу соответствующего временному положению первого превышения порога второго этапа, поступающим соответственно на его первый и пятый входы с третьего и второго выходов блока 11 управления, определяют временное положение, соответствующее длинным многочастотным символам. Момент времени первого превышения порога второго этапа соответствует окончанию первого многочастотного символа и началу второго многочастотного символа.

В блоке 19 расчета дополнительного частотного сдвига синфазные и квадратурные составляющие входного цифрового комплексного сигнала, скорректированные по фазе первого и второго длинных многочастотных символов, используют для определения дополнительной оценки частотного сдвига.

Оценка выполняется, например, следующим образом. Формируют комплексные спектры двух длинных многочастотных символов, затем находят усредненную разность фаз соответствующих элементов комплексных спектров как сумму произведений комплексно-сопряженных элементов первого символа на соответствующие комплексные элементы спектра второго символа. В результате аргумент полученного комплексного числа равен усредненной разности фаз и определяет оценку дополнительного фазового сдвига. Дополнительную оценку частотного сдвига определяют, например, как отношение усредненной разности фаз элементов комплексных спектров к длительности длинного многочастотного символа. Дополнительная оценка частотного сдвига с выхода блока 19 поступает на второй вход третьего сумматора 20.

В третьем сумматоре 20 определяют окончательную оценку частотного сдвига между несущей входного и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига. Полученная окончательная оценка с выхода третьего сумматора 20 поступает на второй выход устройства.

Для лучшего понимания реализации заявляемых способа частотно-временной синхронизации системы связи и устройства для его осуществления рассмотрим работу блока 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала, блока 10 сравнения с порогом, блока 25 определения границ априорного интервала, блока 19 расчета дополнительного частотного сдвига и блока 11 управления.

Блок 23 расчета коэффициента коррекции уровня мощности сформированного входного сигнала (Фиг.4) работает следующим образом.

На первый вход блока 23 поступает коэффициент усиления (или величина, пропорциональная ему) с выхода приемного тракта 1. С первого входа блока 23 сигнал поступает на объединенные первые входы первого регистра 29, ключа 31 и узла расчета отношения коэффициента усиления входного сигнала, соответствующего первому превышению порога первого этапа, к текущему значению коэффициента усиления приемного тракта 32.

Со второго входа блока 23 на первый сигнальный вход и на второй вход записи второго регистра 30 поступает сигнал результата сравнения с заданным порогом первого этапа H1, по которому при наличии хотя бы одного превышения во второй регистр 30 записывают сигнал, равный логической единице. Выход второго регистра 30 соединен с входом формирователя 33 импульса и входом схемы 34 "НЕ". По выходному сигналу со второго регистра 30 на выходе формирователя 33 импульса формируется сигнал в виде импульса, временное положение которого соответствует первому превышению порога первого этапа. По этому сигналу в первом регистре 29 запоминают значение коэффициента усиления приемного тракта. С выхода первого регистра 29 значение коэффициента усиления приемного тракта, соответствующее первому превышению порога первого этапа, поступает на вход узла 32 расчета отношения коэффициента усиления входного сигнала, соответствующего первому превышению порога первого этапа, к текущему значению коэффициента усиления приемного тракта. С выхода узла 32 рассчитанный коэффициент коррекции уровня мощности сформированного входного сигнала поступает на выход блока 23. Если не было превышения порога первого этапа, в узле 32 формируется отношение, равное единице, т.к. в этом случае ключ 31 замкнут (с выхода первого регистра 29 сигнал не поступает), и в узле 32 делимое и делитель равны.

Вариант выполнения блока 25 определения границ априорного интервала показан на Фиг.5. Блок 25 работает следующим образом.

В первом плече, содержащем первый регистр 35, первый ключ 36 и первый счетчик 37, формируют сигнал начала области априорного интервала второго этапа. Во втором плече, содержащем второй регистр 38, второй ключ 39 и второй счетчик 40, формируют сигнал окончания области априорного интервала второго этапа. Во третьем плече, содержащем третий регистр 41, третий ключ 42 и третий счетчик 43, формируют сигнал непревышения порога в течение интервала короткого символа (после последнего превышения порога первого этапа).