Изобретение относится к измерительной технике и может быть использовано в цифровых сетях электросвязи, построенных на волоконно-оптических линиях связи (ВОЛС) на базе систем передачи синхронной цифровой иерархии (СЦИ) и плезиохронной цифровой иерархии (ПЦИ) с целью определения временной задержки сигналов в линиях связи.

Как свидетельствует опыт практической эксплуатации ВОЛС большой протяженности, следствием изменения температуры окружающей среды - суточные, сезонные и годовые перепады, особенно линий связи с подвешенным кабелем на опорах контактной сети, является соответствующее изменение запаздывания в ВОЛС.

Изменение запаздывания в свою очередь искажает передаваемый эталонный временной сигнал. Отмеченное обстоятельство обуславливает необходимость постоянного измерения задержки сигналов на различных участках цифровой сети и использование этих данных при расчете и компенсации временных задержек в линиях связи.

Известны устройства определения расхождения фаз, содержащие генератор, фазовый дискриминатор, входную и выходную шины, делитель частоты с переменным коэффициентом деления, блок формирования зон добавления, блок формирования зон вычитания и блок управления коэффициентами деления с входной информационной шиной, информационные выходы которого соединены с информационными входами делителя частоты с переменным коэффициентом деления, вход которого соединен с выходом задающего генератора и первым входом фазового дискриминатора, второй вход которого соединен с первым выходом делителя частоты с переменным коэффициентом деления, второй выход которого соединен с выходной шиной и третьим входом фазового дискриминатора, четвертый вход которого соединен с входной шиной, а выходы его соединены с первыми входами блока формирования зон добавления и блока формирования зон вычитания, первые выходы которых соединены с входами вычитания и добавления блока управления коэффициентами деления, а вторые выходы перекрестно соединены с вторыми входами блока формирования зон добавления и блока формирования зон вычитания (RU 93057577 A, H 03 L 7/00, 27.01.1997). Однако точность определения данного устройства недостаточна.

Известно устройство “Цифровой фазовый дискриминатор” (ЦФД), содержащее входной коммутатор - объединитель опорного и измеряемого сигналов, два делителя частоты с переменным коэффициентом деления (ДПКД), на первый из которых подается сигнал с входного коммутатора, а на второй - дополнительный сигнал, релейно-фазовый детектор (РФД), блок управления режимами, вычитатель (SU 1569940 A1, H 03 L 7/00 07.06.1990).

Принцип действия этого устройства основан на изменении фазового угла между опорным и измеряемым сигналами при помощи дополнительного сигнала с учетом выполнения условия, чтобы частоты опорного и измеряемого сигналов были равны и изменения происходили в пределах периода измеряемых сигналов.

В качестве основного недостатка данного устройства следует отметить ограниченность его функциональных возможностей из-за узких пределов использования рабочей области детектирования.

К сожалению, использование в паре входного коммутатора опорного и измеряемого сигналов с ДПКД без принятия специальных мер по отдельному фазированию измеряемого сигнала с дополнительным сигналом не обеспечивает необходимых пределов детектирования для определения временной задержки с требуемой точностью.

Технический результат изобретения заключается в определении временной задержки при передаче сигналов по линиям связи, позволяющей обеспечить высокую точность измерения в широких временных пределах.

Поставленная цель достигается введением в состав рассмотренного ЦФД дополнительного делителя частоты с переменным коэффициентом деления (ДПКД) для подачи на него измеряемого сигнала и соответственно исключения входного коммутатора, а также введением второго релейно-фазового детектора (РФД) при соответствующем схемном соединении их с блоком управления, блоком установки фазы делителя и между собой.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием дополнительных элементов при соответствующем схемном решении. Таким образом, заявляемое техническое решение соответствует критерию изобретения “новизна”.

Сравнение заявляемого устройства с другими аналогичными техническими решениями показывает, что наличие в подобных устройствах ДПКД и РФД известно. Однако благодаря введению в состав устройства дополнительных ДПКД с РФД при соответствующем схемном соединении их между собой и с другими элементами устройства, с целью разделения опорного и измеряемого сигналов, в заявляемом устройстве появляются новые свойства, заключающиеся в расширении пределов использования рабочей области детектирования. Это позволяет сделать вывод о соответствии заявляемого технического решения критерию “изобретательский уровень”.

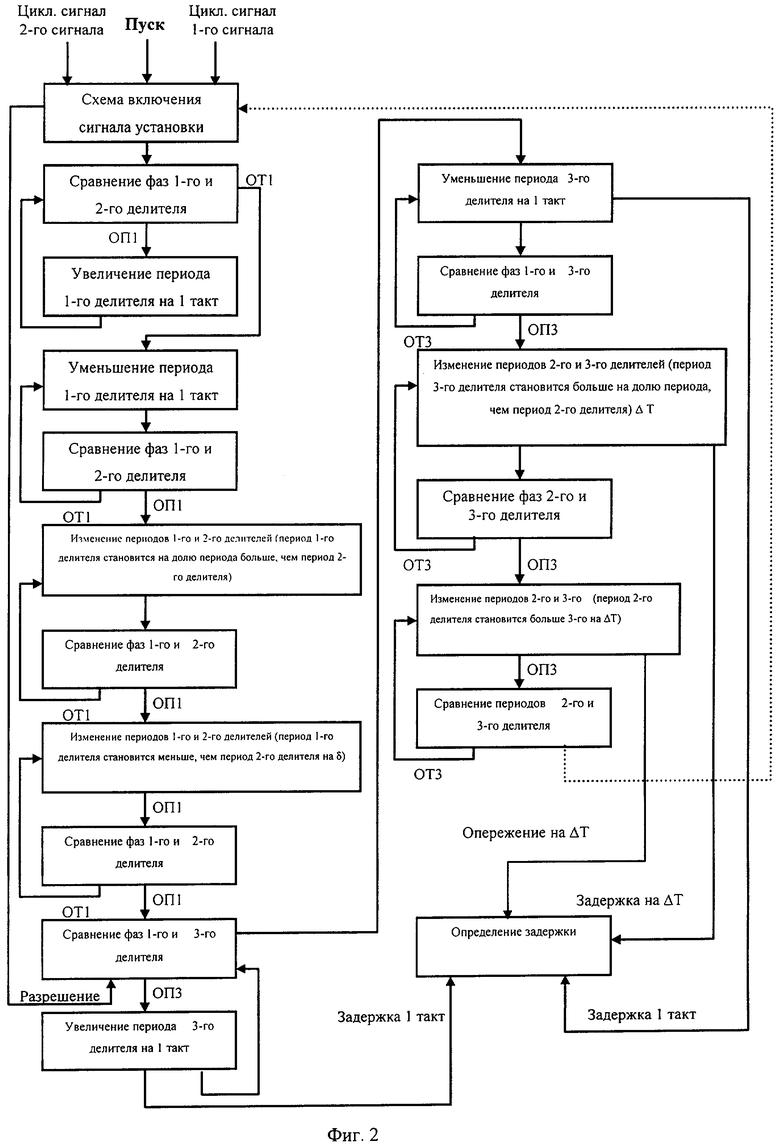

На фиг.1 приведена функциональная схема предлагаемого “Устройства определения временной задержки”, где обозначено:

1 - первый делитель частоты с переменньм коэффициентом деления;

2 - первый релейно-фазовый детектор;

3 - второй делитель частоты с переменным коэффициентом деления;

4 - третий делитель частоты с переменным коэффициентом деления;

5 - второй релейно-фазовый детектор;

6 - блок установки фазы делителя;

7 - блок управления режимами;

Uоп - опорный сигнал;

Uизм - измеряемый сигнал;

Uдоп - дополнительный сигнал;

Uфаз 1 - сигнал начального фазирования с ДПКД 1;

Uфаз 2 - сигнал начального фазирования с ДПКД 4;

На третий ДПКД 4 подается измеряемый сигнал, опорный сигнал подключается к первому ДПКД 1, а дополнительный - к второму ДПКД 3.

К первому РФД 2 подключаются выходы первого ДПКД 1 и второго ДПКД 3, а к второму РФД 5 - выходы второго ДПКД 3 и третьего ДПКД 4, выходы от первого РФД 2 и второго РФД 5 подключаются ко входам блока управления режимами 7, выходы которого подключаются к управляющим входам первого ДПКД 1 и третьего ДПКД 4 и к блоку установки фазы делителей 6, на вход которого подключены два сигнала фазирования, передаваемые с выхода к первому ДПКД 1 (Uфаз 1) и к третьему ДПКД 4 (Uфаз 2).

Работает заявляемое устройство определения временной задержки следующим образом.

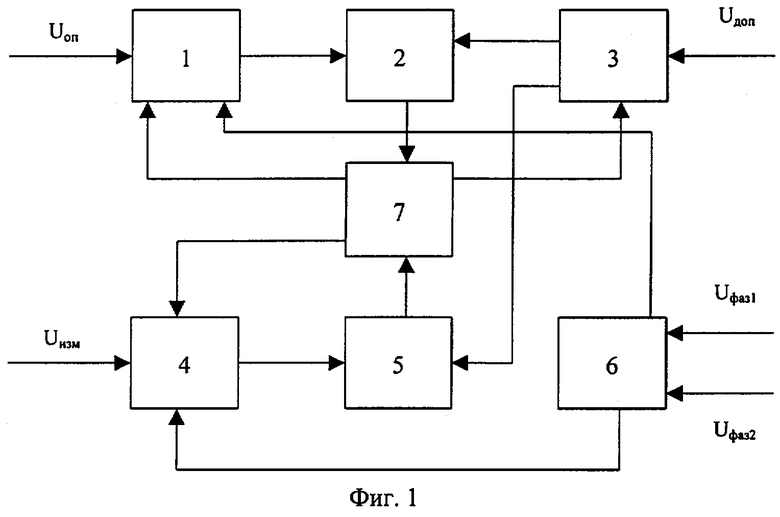

Устройство работает по алгоритму (фиг.2). В каждый момент времени взаимодействуют два из трех сигналов: Uоп и Uдоп, либо Uизм, поступающий на вход третьего ДПКД 4 и Uоп. Каждое из этих взаимодействий происходит последовательно в двух режимах деления ДПКД. Первый режим деления характеризуется коэффициентами деления первого ДПКД 1 и второго ДПКД 3, равными соответственно d01 и d03, а второй режим деления первого ДПКД 1 и третьего ДПКД 4 - соответственно d11 и d14. В процессе измерений происходят последовательно три раза по четыре состояния (фиг.2), характеризуемые взаимодействующими сигналами и режимом деления. Переход от одного состояния к другому происходит под воздействием изменения выходных сигналов первого РФД 2 и второго РФД 5. Опорный сигнал подают на вход первого ДПКД 1, измерение начинается со значащего момента дополнительного сигнала, который подается на вход второго ДПКД 3. Первым состоянием устройства является состояние отставания входного сигнала по команде блока 7 управления режимами и выдается первый режим деления. После того как первый РФД 2 и второй РФД 5 (по алгоритму на фиг.2 это происходит последовательно) после выдачи сигналов ОП дают команду ОТ, блок 7 управления режимами выдает на первый ДПКД 1, второй ДПКД 3 и третий ДПКД 4 сигналы изменения коэффициентов деления, первый РФД 2 и второй РФД 5 переходят во второй режим деления. Происходит уменьшение периода второго ДПКД 3 (третьего ДПКД4) на один такт. Когда первый РФД 2 (второй РФД 5) снова зафиксирует состояние опережения, значащие моменты дополнительного и опорного сигналов оказываются сфазированными с определенной точностью (период второго ДПКД 3 / третьего ДПКД 4 становится на долю периода больше, чем период первого ДПКД 1). После выполнения процессов сравнения фаз второго ДПКД 3, третьего ДПКД 4 и изменения коэффициентов третьего ДПКД 4 на один такт, а также сравнения второго ДПКД 3, третьего ДПКД 4 и изменения периодов этих делителей выполняется функция определения задержки. Результат определения временной задержки отражается в блоке управления режимами 7.

При соблюдении этого условия можно сделать вывод, что цель, поставленная перед предлагаемым изобретением, - определение временной задержки, при передаче сигналов времени и стандартных частот (СВСЧ) в ВОЛС с высокой точностью достигнута.

Несомненным достоинством предложенного устройства является простота его конструкции, обуславливающая его малую стоимость и высокую надежность в эксплуатации, что обеспечит его широкое практическое применение.

Предложенное устройство может найти применение при проведения непрерывного измерения задержек сигналов в линиях связи.

Технико-экономический эффект, обусловленный применением предложенного устройства, заключается в повышении стабильности получения СВСЧ и надежности функционирования системы распределения сигналов единого времени, а следовательно, и в повышении обеспечиваемого экономического эффекта от использования данного метода передачи СВСЧ по ВОЛС.

Количественная величина ожидаемого технико-экономического эффекта от использования предложенного устройства зависит от конкретного его исполнения и важности объектов, на которых оно будет реализовано - ее определение возможно только после реализации на конкретных объектах.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИЗМЕРЕНИЯ ЗАДЕРЖКИ СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ В КАНАЛАХ СВЯЗИ | 2011 |

|

RU2460209C1 |

| Способ определения отклонения частоты от номинального значения | 1986 |

|

SU1449923A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| УСТРОЙСТВО ЧАСТОТНО-ВРЕМЕННОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2341892C2 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Устройство фазовой автоподстройки частоты | 1986 |

|

SU1443173A1 |

| Способ определения отклонения частоты от номинального значения | 1989 |

|

SU1707561A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2011 |

|

RU2477920C1 |

| Синтезатор частот | 1982 |

|

SU1150764A1 |

Изобретение относится к измерительной технике, может быть использовано в цифровых сетях электросвязи, построенных на волоконно-оптических линиях связи (ВОЛС) на базе систем передачи синхронной цифровой иерархии и плезиохронной цифровой иерархии с целью определения временной задержки сигналов в линиях связи. Технический результат заключается в повышении точности измерения в широких временных пределах. Устройство содержит три делителя частоты с переменным коэффициентом деления (1), (3), (4), два релейно-фазовых детектора (2), (5), блок управления режимами (7), блок установки фазы делителей (6). 2 ил.

Устройство определения временной задержки, содержащее первый, второй и третий делители частоты с переменным коэффициентом деления, управляющие входы которых соединены с первыми выходами блока управления режимами, блок установки фазы делителя, на вход которого подключены два сигнала фазирования, выходы которого соединены соответственно с входами первого и третьего делителей частоты с переменным коэффициентом деления, выходы которых соединены с первыми входами соответственно первого и второго релейно-фазовых детекторов, выходы которых соединены со входами блока управления режимами, а выходы второго делителя частоты с переменным коэффициентом деления - со вторыми входами соответственно первого и второго релейно-фазовых детекторов, причем дополнительный сигнал подключен ко входу второго делителя частоты с переменным коэффициентом деления, измеряемый сигнал подключен ко входу третьего делителя частоты с переменным коэффициентом деления, а опорный сигнал подключен ко входу первого делителя частоты с переменным коэффициентом деления.

| Цифровой фазовый дискриминатор | 1987 |

|

SU1569940A1 |

| Фазовый дискриминатор | 1977 |

|

SU720680A1 |

| RU 2052894 C1, 20.01.1996 | |||

| RU 93057577 A, 27.01.1997 | |||

| US 4764980, 16.08.1988. | |||

Авторы

Даты

2004-11-20—Публикация

2002-05-18—Подача