2. Синтезатор по п. 1, о т л и чающийся тем, что преобразователь кодов содержит последовательно соединенные блок запоминания, блок вычисления промежуточного коэффициента деления и блок коммутации, при этом вторая группа входов блока коммутащ1и, вторая группа вхоДов блока вычисления промежуточного коэффициента деления и кодовые входы блока запоминания объединены и являются кодовыми входами преобразовате50764

ля кодов, выходы блока коммутации . являются кодовыми выходами преобразователя кодов, упрарляюи(ие входы блока коммутации, блока вычисления промежуточного коэффициента деления и блока запоминания являются соответ ственно первым, вторым и третьим управляющими входами преобразователя кодов, а информационн1.1й выход блока вычисления промежуточного коэффиплента деления является информационным в-ыходом преобразователя кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1681382A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частот | 1979 |

|

SU785943A1 |

1. СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные фазовый детектор, первый генератор стабильного тока, фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом деления, первый ключ и регистр сдвига, первый выход которого соединен с R входом RS-триггера, выход которого подключен к другому йходу первого ключа, второй генератор стабильного тока, вход и выход которого соединены соответственно с другим выходом фазового детектора и входом фильтра нижних частот, последовательно соединенные опорный генератор и делитель частоты с фиксированным коэффициентом деления, а также преобразователь ко- дов, кодовые входы которого подключены к соответствующим выходам датчика кода, установочные входы делителя частоты с переменным коэффициентом деления подключены к соответствующим кодовым выходам -преобразователя кодов, отличающийся тем, что, с целью повышения спектральной чистоты выходного сигнала и уменьшения времени перестройки, в него введены последовательно соединенные второй ключ и инвертор, третий ключ, а также первый и второй элементы И-ИЛИ, вьпсоды которых подключены к соответствующим входам фазового детектора, первый вход первого элемента И-ИЛИ, первый оход второго элемента И-ИЛИ и первый вход : третьего ключа объединены и подключены к выходу делителя частоты с фиксированным коэффициентом деления, второй вход первого элемента И-ИЛИ объединен с вторым входом второго элемента И-ИЛИ и подсоединен к выходу делителя частоты с переменным коэффициентом деления, первые управляющие входы первого и второго элементов И-ИЛИ под(Л ключены соответственно к выходу инс вертора и к выходу второго ключа, вторые управляющие входы первого и второго элементов И-ИЛИ соединены соответственно с выходом второго ключа и с выходом инвертора, первый и втосд рой входы второго ключа подключены соответственно к второму выходу регистра сдвига и к информационному sl выходу преобразователя кодов, первый О) управляющий вход которого объединен с D входом регистра сдвига и подключен к выходу R$-триггера, второй управляющий вход преобразователя кодов объединен с 5 входом R5 -триггера и подключен к установочному выходу датчика кода, третий управляющий вход преобразователя кодов объединен с входом обнуления регистра сдвига и подключен к выходу третьего ключа, второй вход которого объединен с входом обнуления делителя частоты с паременным коэффициентом деления и подключен к первому выходу регистра сдвига.

Изобретение относится к радиотехнике и может быть использовано для генерации сетки частот в широкополое ных радиопередающих и радиоприемных устройствах,

Известен синтезатор частот, содержаисий последовательно соединенные опорный генератор, первый делитель частоты с переменным коэффициентом деления, фазовый детектор, управляемый генератор, второй делитель частоты с переменным коэффициентом деления, датчик синхронизма, счетчик и преобразователь кодов, выход которого подключен к установочному входу второго делителя частоты с переменным коэффициентом деления, выход ко.торого также соединен с другим вхохом датчика синхронизма, а также датчик кода, выходы которого подключены к вторым входам счетчика и преобразователя кодов, вькод счетчика соединен с установочньгм входом первого делителя частоты с переменным коэффициентом деления Cll.

Однако спектральная чистота выходных колебаний такого синтезатора частот недостаточно высокая из-за необходимости расширения полосы пропускания фильтра нижних частот, входящего в состав фазового детектора, из-за изменения частоты сравнения в процессе перестройки по диапазону.

Наиболее близким к предлагаемому является синтезатор частот, содержащий последовательно соединенные фазевый детектор, первый генератор стабильного тока, фильтр нижних частот.

управляемый генератор, делитель частоты с переменным коэффициентом дешения, первый ключ и регистр сдвига, первый выход которого соединен с R входом RS-триггера, выход которого подключен к другому входу первого ключа, второй генератор стабильного тока, вход и выход которого соединены соответственно с другим выходом фазового детектора и входом фильтра нижних частот, последовательно соединенные опорный генератор и делитель частоты с фиксированным коэффициентом деления, а также преобразователь кодов, кодовые входы которого подключены к соответствующим выходам датчика кода, установочные входы делителя частоты с переменным коэффициентом деления подключены к соответствующим кодовым выходам преобразователя кодов Cz.

Однако быстродействие перестройки и спектральная чистота выходного сигнала этого синтезатора частот недостаточно высокие.

Цель изобретения - повышение спектральной чистоты выходного сигнала и уменьшение времени перестройки.

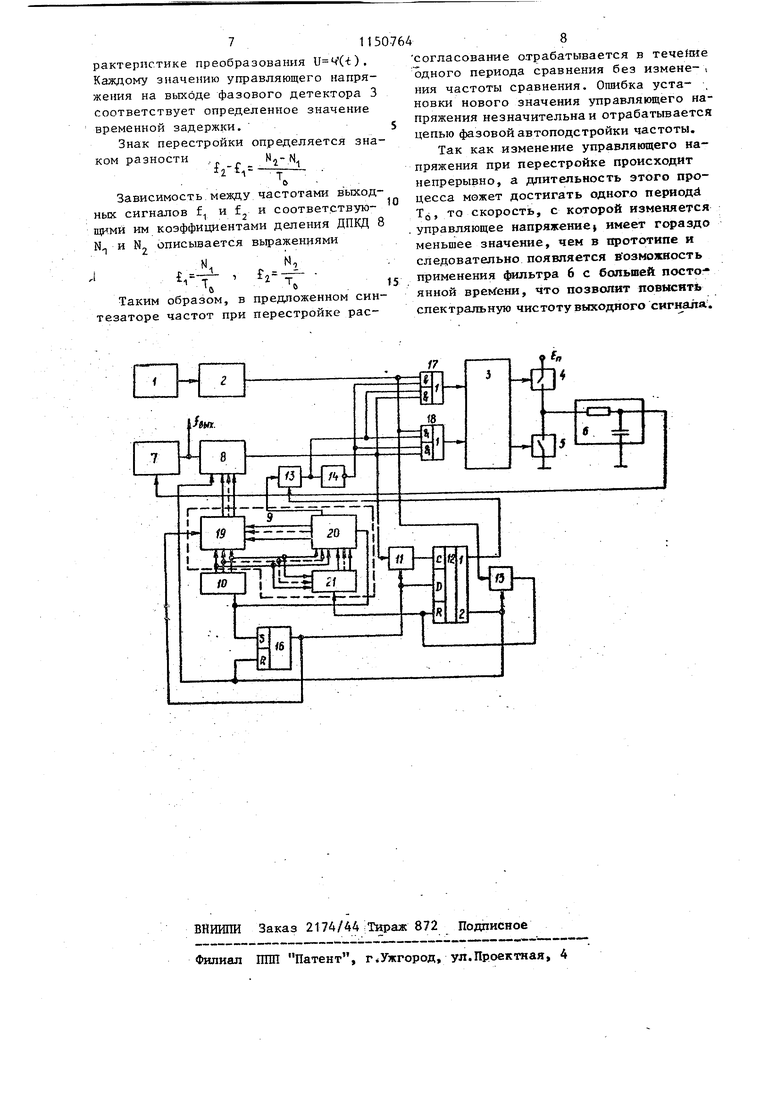

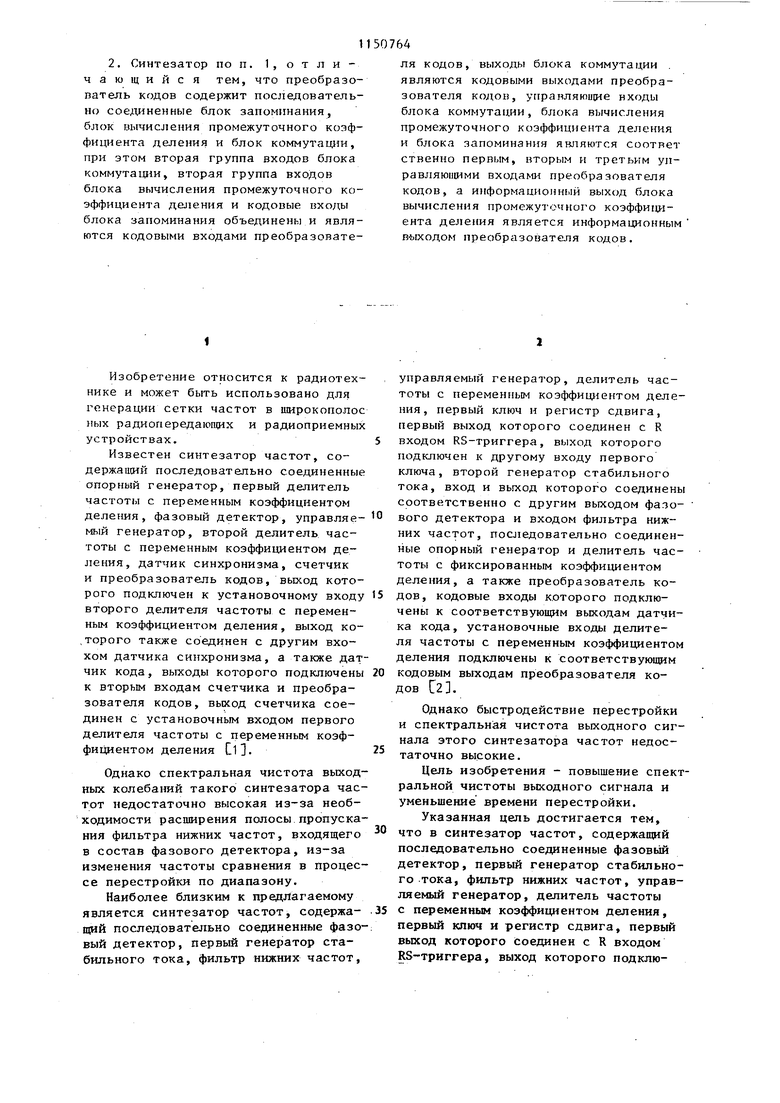

Указанная цель достигается тем, что в синтезатор частот, содержащий последовательно соединенные фазовЕлй детектор, первый генератор стабильного тока, фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом деления, первый ключ и регистр сдвига, первый выход которого Соединен с R входом RS-триггера, выход которого подключей к другому входу первого ключа, второй генератор стабильного тока, вход и выход которого соединены соот ветственно с другим выходом фазовог детектора н входом фильтра нижних ча тот, последовательно соединенные оп ный генератор и делитель частоты с фиксированным коэффициентом деления а также преобразователь кодов, кодо вые входы которого подключены к соо ветствующим выходам датчика кода, установочные входы делителя частоты с переменным коэффициентом деления подключены к соответствующим кодовым выходам преобразователя кодов, введе ны последовательно соединенные второй ключ и инвертор, третий ключ, а также первый и второй элементы И-ИЛИ выходы которых подключены к соответствуюи(им входам фазового детектора, первый вход первого элемента И-ИЛИ, первый вход второго элемента И-ИЛИ и первый вход- третьего ключа объединены и подключены к выходу делителя частоты с фиксированным коэффициенто деления, второй вход первого элемента И-ИЛИ объединен с вторым входом второго элемента И-ИЛИ и подсоединен к выходу делителя частоты с переменным коэффициентом деления, первые управляющие входы первого и второго элементов И-ИЛИ подключены соответственно к выходу инвертора и к выходу второго ключа, вторые управляющие входы первого и второго элементов И-ИЛИ соединены соответственно с выходом второго ключа и с выходом инвертора, первый и второй входы второ го ключа подключены соответственно к второму выходу регистра сдвига и к информационному выходу преобразовате ля кодов, первый управляющий вход которого объединен с D входом регист ра сдвига и подключен к выходу RSтриггера, второй управляющий вход преобразователя кодов объединен с S входом RS-триггера и подключен к установочному выходу датчика кода, третий управляющий вход преобразователя кодов объединен с входом обнуления регистра сдвига и подключен к выходу третьего ключа, второй вход которого объединен с входом обнуления делителя частоты с переменным коэффициентом деления и подключен к первому выходу регистра сдвига. Преобразователь кодов содержит последовательно соединенные блок за14 поминания, блок вычисления промежуточного коэффициента деления и блок коммутаций, при этом вторая группа входов блока коммутации, вторая группа входов блока вычисления промежуточного кoэффицlieнтa деления и кодовые входы блока запоминания объединены и являются кодовыми входами преобразователя кодов, выходы блока , коммутации являются кодовыми выходами преобразователя кодов, управляющие входы блока коммутации, блока вычисления промежуточного коэффициента деления и блока запоминания являются соответственно первым, вторым и третьим управляющими входами преобразователя кодов, а информационный выход блока вычисления промежуточного коэффициента деления является информационным выходом преобразователя кодов. На чертеже изображена структурная электрическая синтезатора частот. Синтезатор частот содержит опорный генератор 1, делитель частоты с фиксированным коэффициентом деления (ДФКД) 2, фазовый детектор 3, первый генератор стабильного гока 4, второй генератор стабильного тока 5, фильтр 6 нижних частот, управляемьй генератор 7, делитель частоты с переменным коэффициентом деления (ДПКД) 8, преобразователь кодов 9, датчик кода 10, первый ключ 11, регистр сдвига 12, второй ключ 13, инвертор 14, третий ключ 15 RS-триггер 16, первый элемент И-ИЛИ 17, второй элемент И-ИЛИ 18. Преобразователь кодов 9 содержит блок коммутации 19, блок вычисления 20 промежуточного коэффициента деления, блок запоминания 21. Синтезатор частот работает следующим образом. В исходном состоянии управляемый генератор 7 вьфабатывает сигнал с частотой f,, , заданный при помощи коэффициента деления N ДПКД 8 и за счет работы кольца фазовой автоподстройки. Последовательности импульсов на входах фазового детектора 3 имеют одинаковый период, повторения и нулевой фазовый сдвиг. На выходе фильтра 6 имеется постоянное управяющее напряжение. На управляющем входе блока коммутащ и.19 сигнал отсутствует и на установочные, входы ПКД 8 через блок коммутации 19 преобразователя кбдов 9.передается ббз изменения код частоты f с выходов датчика кода 10. Рдновреме но этот код частоты поступает на входы блока запоминания 21, с выходов которого та же информация поступает на первые входы блока вычисления 20. Переключение частоты выходных колебаний осуществляется следующим образом. После окончания набора нового зна чения частоты 2 установочном выходе датчика кода 10 появляется импульс установки и на кодовых выходах датчика кода 10 одновременно появляе ся информация о новом значении часто ты f , . Импульс установки включает блок вычисления 20 преобразователя к дов 9, который производит обработку кодов,поступающих на его входы, и на его информационном выходе знака перестройки устанавливается или уровень 0,,в зависимости от знака разности частот f. Одновременно импульс установки с выхода датчика кода 10 поступает На S вход RS-триг гера 16 и на его выходе устанавливается уровень 1, под действием кото рого на кодовых выходах преобразователя кодов 9 появляется код промежуточного коэффициента деления , сфопорциональньш разности между пред шествующим значением частоты f, , и новым значением fj ДПКД 8 продолжает делить с первоначальным коэффициентом N до окончания Ц11кла деления и появления на его выходе очередного импульса. В момент окончания цикла деления происходит установка коэффициента деления ДПКД 8 . Начинается промежуточный цикл деления, необходимый для того, чтобы импульсы с выходов ДФКД 2 и ДПКД 8 появились на входах фазового детектора 3 в последовательности и с задержкой, необходимыми для формирования фазовым детектором 3 нового значения управляющего напряжения, соответствующего установленному значению частоты fg. При ЭТОМ последовательность появления импульсов и время задержки определяются соответственно знаком и величиной расстройки. В зависимости от знака расстройки -при помощи второ го ключа 13, инвертора 14 и первого и второго.элементов 17 и 18 входы фазового детектора 3 подключаются или к выходам ДПКД 8 и ДФКД 2 ИЛИ наоборот - к вькодам ДФКД 2 и ДПКД 8 соответственно. Переключение входов фазового детектора 3 осу цествляется по сигналу 1 с второго выхода регистра сдвига 12 при окончании последнего цикла деления ДПКД 8 с первоначальным коэффициентом N. С появлением импульса на выходе ДПК/J 8 в промежуточном 1щкле деления на первом выходе регистра сдвига 12 появляется уровень 1, который блокирует ДПКД 8, а на втором выходе регистра сдвига 12 появляется уровень О. При этом на выходах преобразователя кодов 9 появляется код N2, соответствующий новому значению частоты fj . Очередной импульс с выхода ДФКД 2 поступает в зависимости от знака расстройки или на первый, или на второй входы фазового детектора 3 и одновременно на второй вход третьего ключа 15, на выходе которого появляется сигнал, с помощью которого происходит запись информации о новом значении частоты fj в блоке запоминания 21 преобразователя кодов 9. Одновременно с этим снимается блокировка с ДПКД 8 и начинается новый цикл деления с коэффициентом.деления N. Алгоритм работы преобразокодов 9 описывается выраженивателяем период частоты сравнения ; коэффициент деления ДПКД 8; эквивалентная крутизна управления управляемым генератором 7 (значения и и Uj определяются по хранимой в блоке вычисления 20 характеристике управления (U) управляемого генератора 7); ч . эквивалентная крутизна l4-iiJ характеристики преобразования фазового детектора 3. Значения t и t определяются по записанной в блоке вычисления 20 характерпстике преобразования (-t). Каждому значению управляющего напряжения на выходе фазового детектора 3 соответствует определенное значение временной задержки. Знак перестройки определяется зна ком разности . . . Зависимость между частотами выход ных сигналов f и f и соответствующими им коэффициентами деления ДПКД N и N описывается выражениями М. ; -ьи. Таким образом, в предложенном син тезаторе частот при перестройке рассогласование отрабатывается в одного периода сравнения без измене- ния частоты сравнения. Ошибка установки нового значения управляющего напряжения незначительна и отрабатывается цепью фазовой автоподстройки частоты. Так как изменение управляющего напряжения при перестройке происходит непрерывно, а дпительность этого процесса может достигать одного периодг1 TO, то скорость, с которой изменяется управляющее напряжение имеет гораздо меньшее значение, чем в прототипе и следовательно появляется возможность применения фильтра 6 с большей постоянной , что позволит повысить спектральную чистоту выходного сигнала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой синтезатор частоты | 1980 |

|

SU932623A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Синтезатор частот | 1981 |

|

SU987818A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-15—Публикация

1982-07-22—Подача