Изобретение относится к вычислительной технике и может быть использовано при создании больших интегральных схем (БИС), электрически программируемых и перепрограммируемых запоминающих устройств (ППЗУ, ЭРПЗУ) с энергонезависимым хранением информации.

Цель изобретения -упрощение накопителя и способа управления им при записи, считывании и стирании информации.

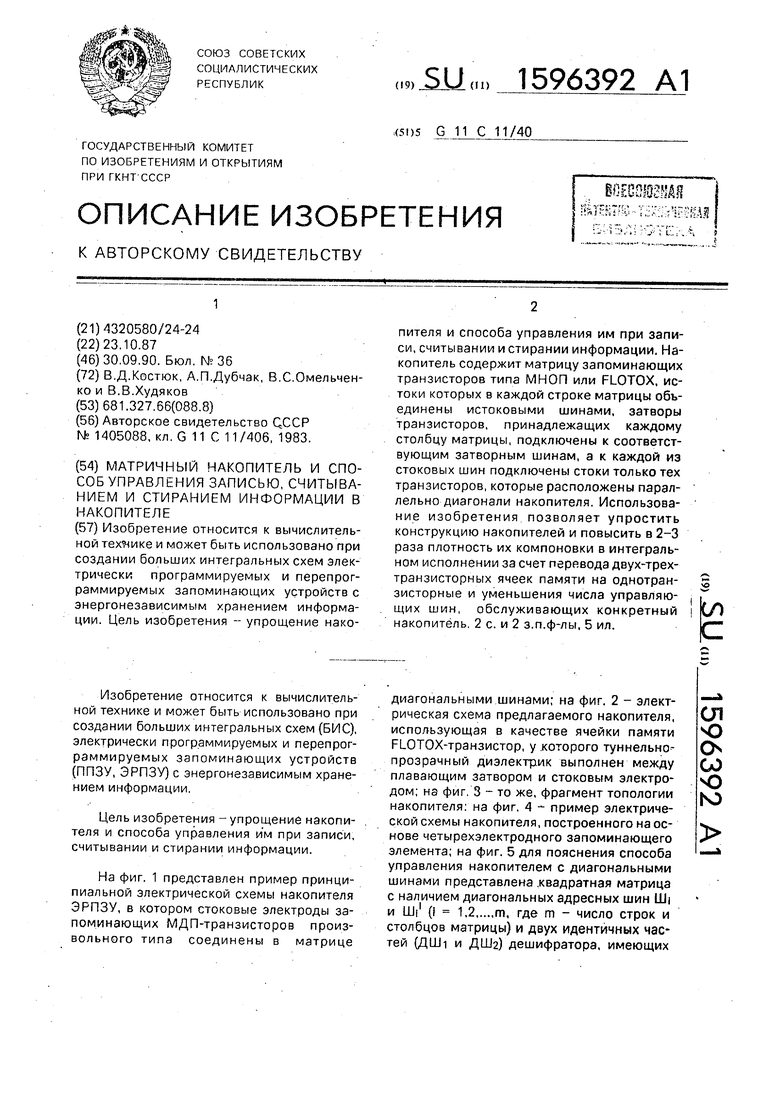

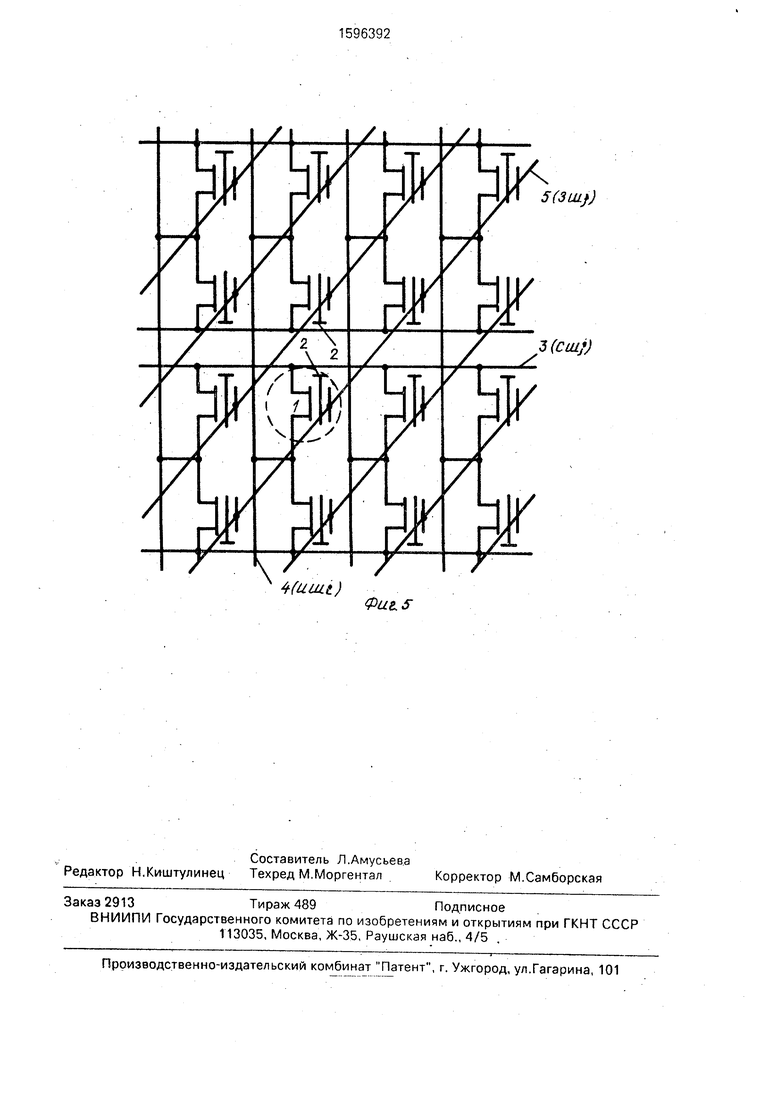

На фиг. 1 представлен пример принципиальной электрической схемы накопителя ЭРПЗУ, в котором стоковые электроды запоминающих МДП-транзисторов произвольного типа соединены в матрице

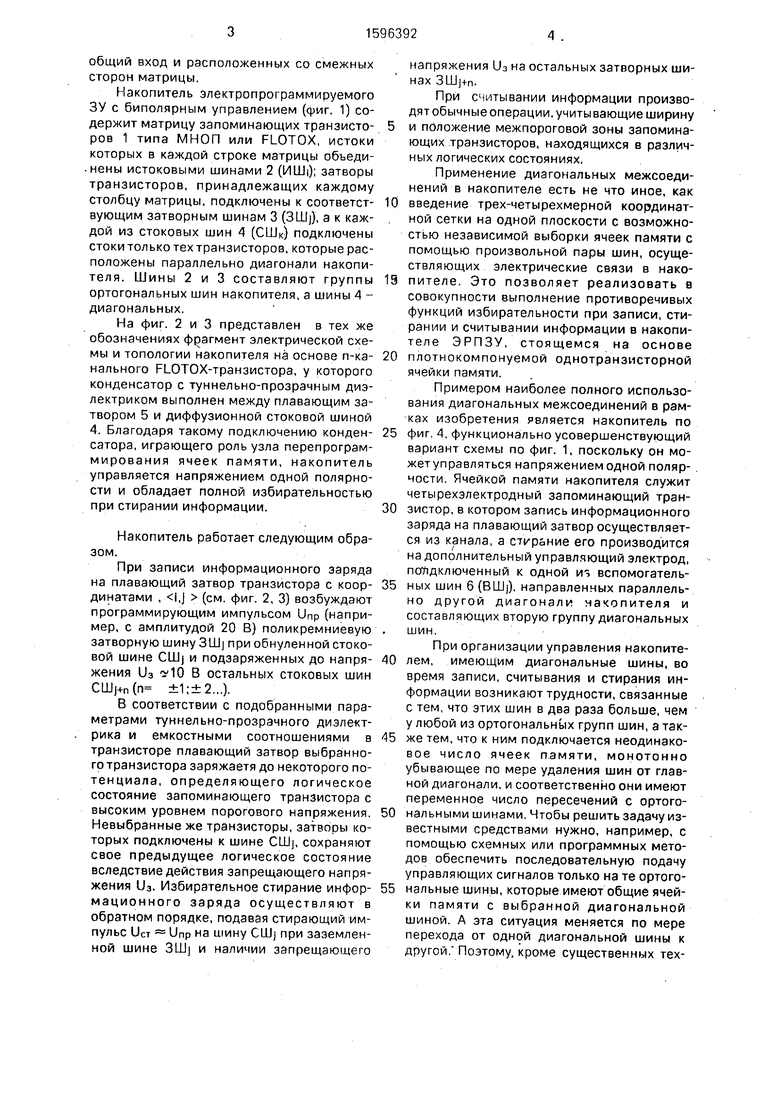

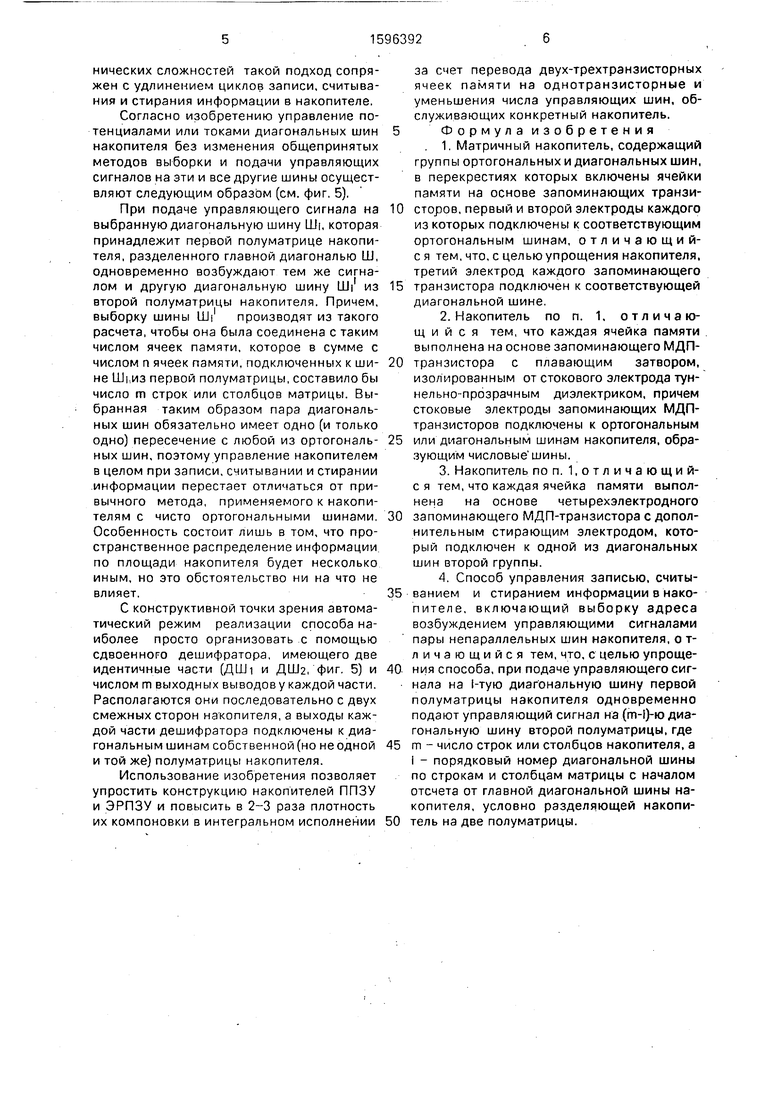

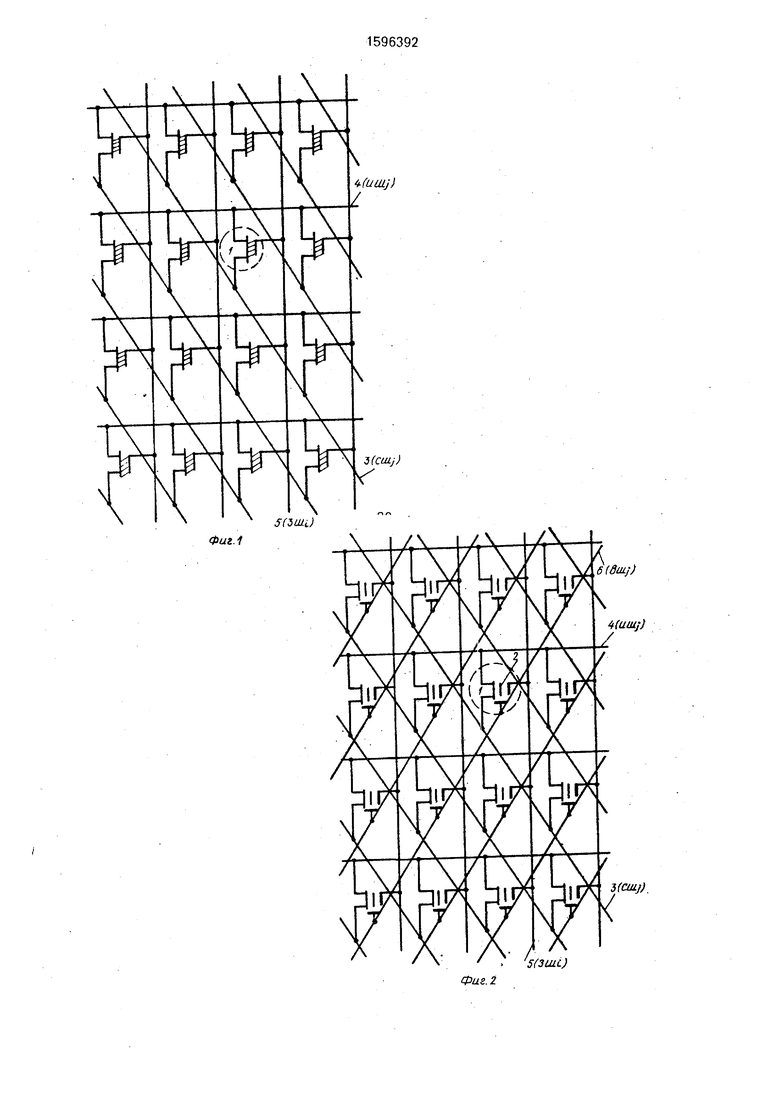

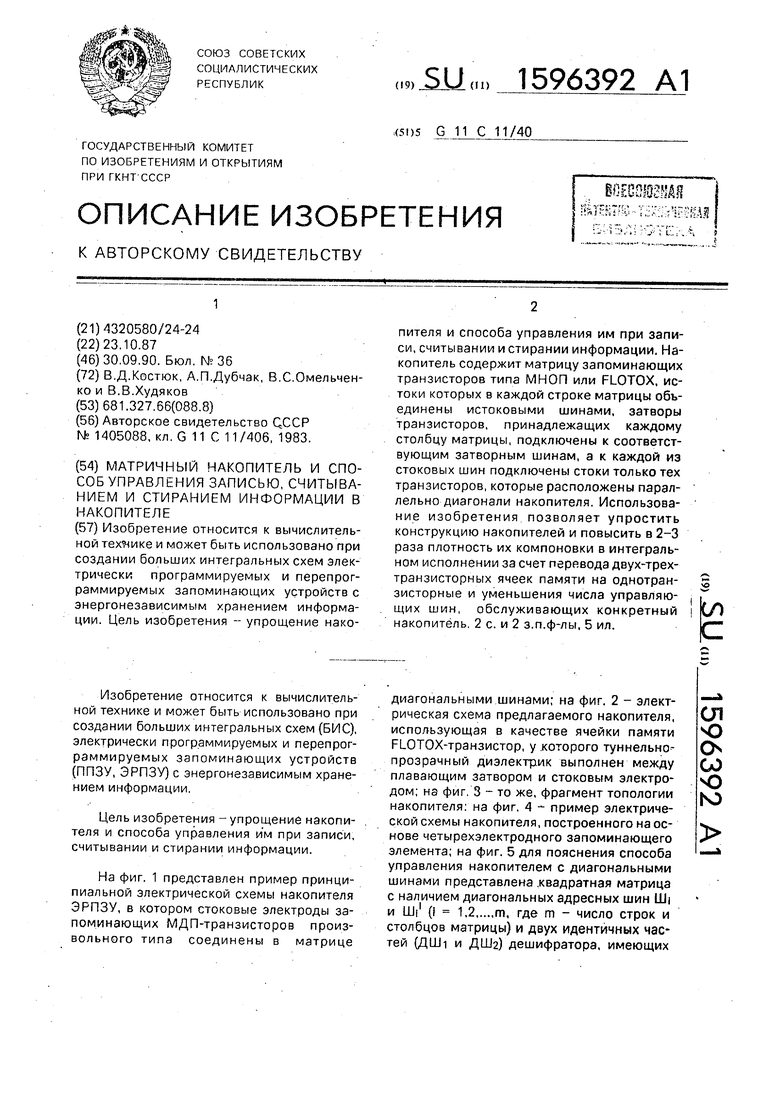

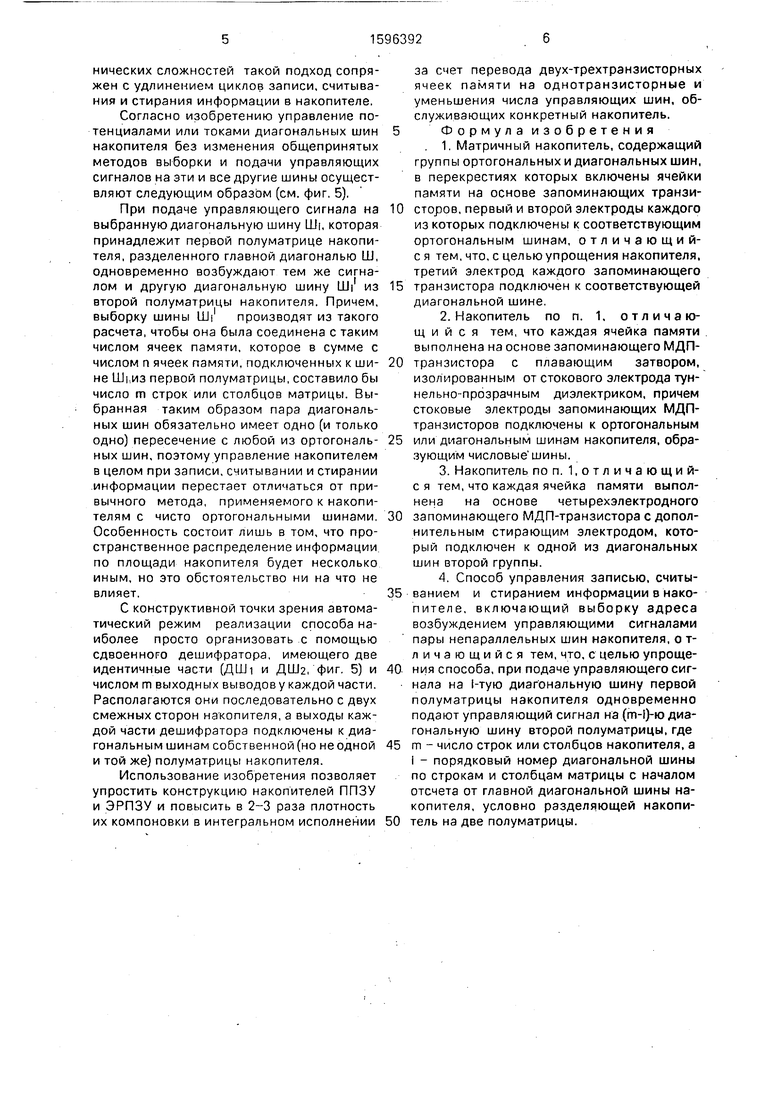

диагональными шинами: на фиг. 2 - электрическая схема предлагаемого накопителя, испояьзующая в качестве ячейки памяти FLOTOX-транзистор, у .которого туннельнопрозрачный диэлектрик выполнен между плавающим затвором и стоковым электродом; на фиг. 3 - то же, фрагмент топологии накопителя: на фиг. 4 - пример электрической схемы накопителя, построенного на основе четырехэлектродного запоминающего элемента; на фиг. 5 для пояснения способа управления накопителем с диагональными шинами представлена .квадратная матрица с наличием диагональных адресных шин Ш|

и Ш1 (i 1,2m, где m - число строк и

столбцов матрицы) и двух идентичных частей (ДШ1 и ДШа) дешифратора, имеющих

бщий вход и расположенных со смежных торон матрицы.

Накопитель электропрограммируемого У с биполярным управлением (фиг. 1) соержит матрицу запоминающих транзисторов 1 типа МНОП или FLOTOX, истоки которых в каждой строке матрицы объединены истоковыми шинами 2 (ИШ|); затворы транзисторов, принадлежащих каждому столбцу матрицы, подключены к соответствующим затворным шинам 3 (ЗШ), а к каждой из стоковых шин 4 (СШк) подключены стоки только тех транзисторов, которые расположены параллельно диагонали накопителя. Шины 2 и 3 составляют группы ортогональных шин накопителя, а шины 4 диагональных.

На фиг. 2 и 3 представлен в тех же обозначениях фрагмент электрической схемы и топологии накопителя на основе п-канального FLOTOX-транзистора, у которого конденсатор с туннельно-прозрачным диэлектриком выполнен между плавающим затвором 5 и диффузионной стоковой шиной 4. Благодаря такому подключению конденсатора, играющего роль узла перепрограммирования ячеек памяти, накопитель управляется напряжением одной полярности и обладает полной избирательностью при стирании информации.

Накопитель работает следующим образом.

При записи информационного заряда на плавающий затвор транзистора с координатами , i,j (см. фиг. 2, 3) возбуждают программирующим импульсом Unp (например, с амплитудой 20 В) поликремниевую затворную шину ЗШ при обнуленной стоковой шине СШ и подзаряженных до напряжения УЗ УЮ В остальных стоковых шин (п ±1;±2...).

В соответствии с подобранными параметрами туннельно-прозрачного диэлектрика и емкостными соотношениями в транзисторе плавающий затвор выбранного транзистора заряжаетя до некоторого потенциала, определяющего логическое состояние запоминающего транзистора с высоким уровнем порогового напряжения. Невыбранные же транзисторы, затворы которых подключены к шине СШ|, сохраняют свое предыдущее логическое состояние вследствие действия запрещающего напряжения УЗ. Избирательное стирание информационного заряда осуществляют в обратном порядке, подавая стирающий импульс UcT Unp на шину СШ при заземленной шине ЗШ| и наличии запрещающего

напряжения Уз на остальных затворных шиах .

При С11тывании информации произвоят обычные операции, учитывающие ширину

положение межпороговой зоны запоминающих транзисторов, находящихся в различных логических состояниях.

Применение диагональных межсоединений в накопителе есть не что иное, как

введение трех-четырехмерной координатной сетки на одной плоскости с возможностью независимой выборки ячеек памяти с помощью произвольной пары шин, осуществляющих электрические связи в накопителе. Это позволяет реализовать в совокупности выполнение противоречивых функций избирательности при записи, стирании и считывании информации в накопителе ЭРПЗУ, стоящемся на основе

плотнокомпонуемой однотранзисторной ячейки памяти.

Примером наиболее полного использования диагональных межсоединений в рамках изобретения является накопитель по

фиг. 4, функционально усовершенствующий вариант схемы по фиг. 1, поскольку он можетуправляться напряжением одной полярности. Ячейкой памяти накопителя служит четырехэлектродный запоминающий транзистор, в котором запись информационного заряда на плавающий затвор осуществляется из канала, а стирание его производится на дополнительный управляющий электрод, поЛдключенный к одной Иэ вспомогательных шин 6 (ВШ), направленных параллельно другой диагонали накопителя и составляющих вторую группу диагональных шин.

При организации управления накопителем, имеющим диагональные шины, во время записи, считывания и стирания информации возникают трудности, связанные с тем, что этих шин в два раза больше, чем у любой из ортогональнь1х групп шин, а также тем, что к ним подключается неодинаковое число ячеек памяти, монотонно убывающее по мере удаления шин от главной диагонали, и соответственно они имеют переменное число пересечений с ортогональными шинами. Чтобы решить задачу известными средствами нужно, например, с помощью схемных или программных методов обеспечить последовательную подачу управляющих сигналов только на те ортогональные шины, которые имеют общие ячейки памяти с выбранной диагональной шиной. А эта ситуация меняется по мере перехода от одной диагональной шины к другой. Поэтому, кроме существенных технических сложностей такой подход сопряжен с удлинением циклов записи, считывания и стирания информации в накопителе.

Согласно изобретению управление потенциалами или токами диагональных шин накопителя без изменения общепринятых методов выборки и подачи управляющих сигналов на эти и все другие шины осуществляют следующим образЬм (см. фиг. 5),

При подаче управляющего сигнала на выбранную диагональную шину Ш|, которая принадлежит первой полуматрице накопителя, разделенного главной диагональю Ш, одновременно возбуждают тем же сигналом и другую диагональную шину Ш/ из второй полуматрицы накопителя. Причем, выборку шины Ш| производят из такого расчета, чтобы она была соединена с таким числом ячеек памяти, которое в сумме с числом п ячеек памяти, подключенных к шине Шьиз первой полуматрицы, составило бы число m строк или столбцов матрицы. Выбранная таким образом пара диагональных шин обязательно имеет одно (и только одно) пересечение с любой из ортогональных шин, поэтому управление накопителем в целом при записи, считывании и стирании информации перестает отличаться от привычного метода, применяемого к накопителям с чисто ортогональными шинами. Особенность состоит лишь в том, что пространственное распределение информации по площади накопителя будет несколько иным, но это обстоятельство ни на что не влияет.

С конструктивной точки зрения автоматический режим реализации способа наиболее просто организовать с помощью сдвоенного дешифратора, имеющего две идентичные части (ДШт и ДШ2, фиг. 5) и числом m выходных выводов у каждой части. Располагаются они последовательно с двух смежных сторон накопителя, а выходы каждой части дешифратора подключены к диагональным шинам собственной (но не одной и той же) полуматрицы накопителя.

Использование изобретения позволяет упростить конструкцию накопителей ППЗУ и ЭРПЗУ и повысить в 2-3 раза плотность их компоновки в интегральном исполнении

за счет перевода двух-трехтранзисторных ячеек памяти на однотранзисторные и уменьшения числа управляющих шин, обслуживающих конкретный накопитель.

5Формула изобретения

, 1. Матричный накопитель, содержащий группы ортогональных и диагональных шин, в перекрестиях которых включены ячейки памяти на основе запоминающих транзисторов, первый и второй электроды каждого из которых подключены к соответствующим ортогональным шинам, отличающийс я тем, что, с целью упрощения накопителя. третий электрод каждого запоминающего

5 транзистора подключен к соответствующей диагональной шине.

2.Накопитель по п. 1. отличающийся тем, что каждая ячейка памяти . выполнена на основе запоминающего МДП0 транзистора с плавающим затвором, изолированным от стокового электрода туннельно-прозрачным диэлектриком, причем стоковые электроды запоминающих МДПтранзисторов подключены к ортогональным

5 или диагональным шинам накопителя, обра.зующим числовыешины.

3.Накопитель по п. 1,отличающийс я тем, что каждая ячейка памяти выполнена на основе четырехэлектродного

0 запоминающего МДП-транзистора с дополнительным стирающим электродом, который подключен к одной из диагональных шин второй группы.

4.Способ управления записью, считы5 ванием и стиранием информации в накопителе, включающий выборку адреса возбуждением управляющими сигналами пары непараллельных шин накопителя, о тличающийся тем, что, с целью упрощения способа, при подаче управляющего сигнала на 1-тую диагональную шину первой полуматрицы накопителя одновременно подают управляющий сигнал на (т-1)-ю диагональную шину второй полуматрицы, где

5 m - число строк или столбцов накопителя, а I - порядковый номер диагональной шины по строкам и столбцам матрицы с началом отсчета от главной диагональной шины накопителя, условно разделяющей накопи0 тель на две полуматрицы.

5(ЗШ.С)

3

/ V / / /

SI ;7e.-tL:-I. I 5i

7)Ш i

ui

LUi

9иг4

5(ЗШ.})

л

/Ъ(С1и})

Фие.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании больших интегральных схем электрически программируемых и перепрограммируемых запоминающих устройств с энергонезависимым хранением информации. Цель изобретения - упрощение накопителя и способа управления им при записи, считывании и стирании информации. Накопитель содержит матрицу запоминающих транзисторов типа МНОП или FLOTOX, истоки которых в каждой строке матрицы объединены истоковыми шинами, затворы транзисторов, принадлежащих каждому столбцу матрицы, подключены к соответствующим затворным шинам, а к каждой из стоковых шин подключены стоки только тех транзисторов, которые расположены параллельно диагонали накопителя. Использование изобретения позволит упростить конструкцию накопителей и повысить в 2-3 раза плотность их компоновки в интегральном исполнении за счет перевода двух-,трехтранзисторных ячеек памяти на однотранзисторные и уменьшения числа управляющих шин, обслуживающих конкретный накопитель. 2 с.п. ф-лы, 2 з.п. ф-лы, 5 ил.

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

Авторы

Даты

1990-09-30—Публикация

1987-10-23—Подача