Изобретение относится к технике цифровой связи, а именно к устройствам для синхронизации цифровых систем передачи информации с временным уплотнением цифровых потоков.

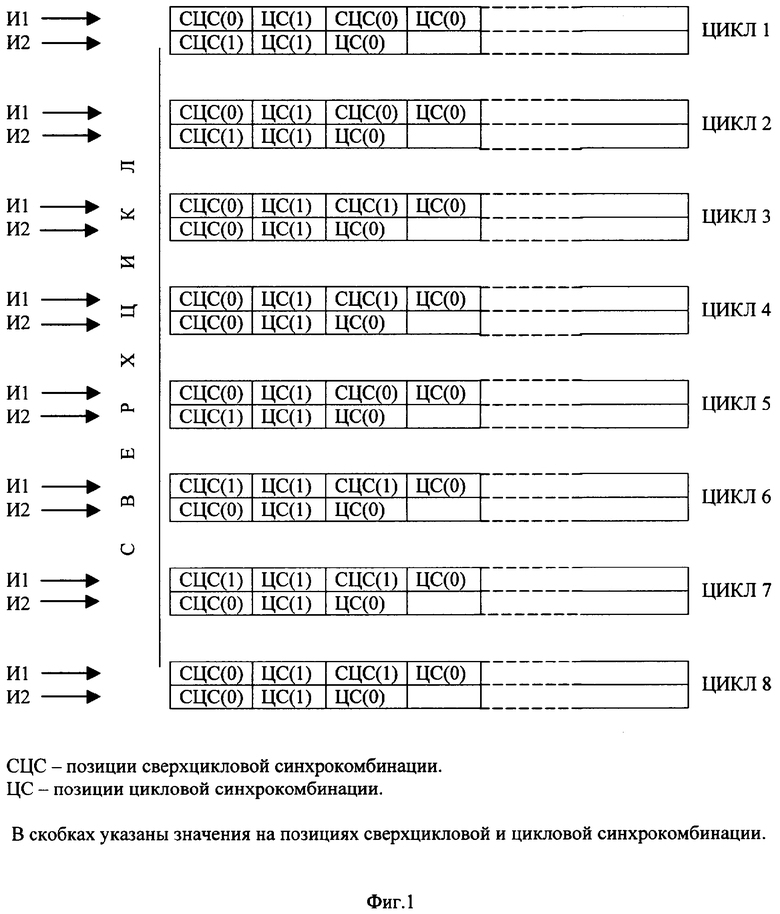

Известны цифровые передачи, структура которых состоит из сверхцикла, содержащего N циклов. В каждом цикле передаются биты цикловой и сверхцикловой синхрокомбинации. Сверхцикл организуется для определения момента начала скремблирования, а также для организации сигнальных и служебных каналов. Пример такой передачи приведен на фиг.1. Длина сверхцикла этих передач может достигать нескольких сот тысяч позиций.

Известны устройства для цикловой синхронизации [Патент РФ №2019046, кл. Н04L 7/08; Патент РФ №2136111, кл. Н04L 7/08; Левин Л. С., Плоткин М.А. Цифровые системы передачи информации. - Радио и связь, 1982, с.102 и 103, рис 4.4.], содержащие регистр сдвига, опознаватель циклового синхросигнала, анализатор совпадения синхросигнала, блок удержания и поиска синхронизма, генераторное оборудование.

Недостатком данных устройств является:

- невозможность одним и тем же устройством осуществить синхронизацию различных передач информации с асинхронным объединением цифровых потоков.

Известно устройство для цикловой синхронизации [Патент РФ №2187210, кл. Н04L 7/08], содержащее оперативное запоминающее устройство, устройство настройки и диагностики, устройства хранения критериев входа в синхронизм и выхода из синхронизма, дешифратор синхрокомбинации, фазирующее устройство, генераторное оборудование. Это устройство позволяет осуществлять синхронизацию различных цифровых передач информации с временным уплотнением и видом модуляции ФМ-2.

Недостатками данного устройства являются:

- невозможность синхронизации цифровых передач с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции;

- большое время поиска синхронизма при длинах сверхцикла цифровых передач до нескольких сотен бит, т.к. поиск синхронизма осуществляется последовательным методом.

Известно устройство для цикловой синхронизации [Патент РФ №2190304, кл. Н04L 7/08, Н04J 3/06], содержащее оперативное запоминающее устройство, регистр запоминания, дешифратор синхрокомбинации, распределитель, фазирующее устройство, генераторное оборудование, элементы И, ИЛИ, НЕ. Это устройство позволяет уменьшить время поиска синхронизма при равномерно распределенной синхрокомбинации в цикле (сверхцикле) за счет осуществления параллельного поиска.

Недостатками данного устройства являются:

- невозможность одним и тем же устройством осуществить синхронизацию цифровых передач с различными видами модуляции;

- невозможность осуществить синхронизацию при неравномерно распределенных позициях синхрокомбинации в цикле (сверхцикле).

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации [Патент РФ №2237374, кл. Н04L 7/08], содержащее оперативные запоминающие устройства, устройство настройки и диагностики, дешифратор синхрокомбинации, генераторное оборудование, фазирующее устройство, перестроитель сигналов, дешифратор, счетчик. Это устройство обеспечивает одним устройством цикловую синхронизацию большого класса цифровых передач с различными видами модуляции.

Недостатком данного устройства является:

- достаточно большое время поиска синхронизма при длинах сверхцикла цифровых передач до нескольких сотен бит, т.к. поиск синхронизма осуществляется последовательным методом.

Технической задачей изобретения является сокращение времени поиска синхронизма цифровых передач с различными видами модуляции, имеющих сверхцикловую структуру.

Указанная задача достигается тем, что в устройство для синхронизации, содержащее первое и второе оперативные запоминающие устройства (ОЗУ), блок настройки режима работы (блок настройки РР), дешифратор цикловой синхрокомбинации (дешифратор ЦСК), блок коммутации информационных сигналов (блок коммутации ИС), первый фазирующий блок, генераторное оборудование (ГО), причем тактовые входы дешифратора ЦСК, блока коммутации ИС и ГО соединены между собой и являются тактовым входом устройства, адресные выходы ГО соединены с соответствующими входами первого и второго ОЗУ и являются адресными выходами устройства для синхронизации, выход чтения, выход записи и первый и второй выходы выбора блока настройки РР соединены с соответствующими входами первого и второго ОЗУ, входы/выходы конца сверхцикла и конца цикла первого ОЗУ соединены с соответствующими входами/выходами блока настройки РР и являются выходами конца сверхцикла и конца цикла устройства для синхронизации, вход/выход конца синхрокомбинации первого ОЗУ соединен с соответствующими входами дешифратора ЦСК, блока коммутации ИС, первого фазирующего блока и входом/выходом блока настройки РР, входы/выходы позиций и значений цикловой синхрокомбинации первого ОЗУ соединены с соответствующими входами/выходами блока настройки РР и входами дешифратора ЦСК, выход отклика которого соединен с соответствующим входом первого фазирующего блока, выход нулевого состояния которого соединен с соответствующими входами блока коммутации ИС и ГО, входы тактов настройки и асинхронной установки в ноль которого соединены с соответствующими выходами блока настройки РР, выходы которого, определяющие количество информационных входов устройства для синхронизации соединены с соответствующими входами блока коммутации ИС, информационные входы которого являются информационными входами устройства для синхронизации, информационные входы дешифратора ЦСК соединены с соответствующими выходами блока коммутации ИС, выход конца перекоммутации которого подключен к соответствующему входу ГО, информационные входы/выходы, входы выбора режима, нового адреса, установки в ноль, записи, чтения, выбора настройки первого или второго ОЗУ, выбора настройки ОЗУ или регистров блока настройки РР являются соответствующими входами устройства для синхронизации, вход выбора режима ГО соединен с соответствующим входом устройства для синхронизации, согласно изобретению введены второй фазирующий блок, блок поиска сверхцикловой синхрокомбинации (блок поиска СЦСК) и блок поиска сверхцикловой синхронизации (блок поиска СЦС), причем входы/выходы позиций сверхцикловой синхрокомбинации второго ОЗУ соединены с разрешающими входами блока поиска СЦСК и входами/выходами блока настройки РР, выходы используемых разрядов регистров и значений сверхцикловой синхрокомбинации блока настройки РР соединены с соответствующими входами блока поиска СЦСК, информационные выходы блока коммутации ИС соединены с информационными входами блока поиска СЦСК, выход которого соединен с входом отклика второго фазирующего блока, вход конца синхрокомбинации которого соединен с соответствующим выходом блока поиска СЦС, выход наличия синхронизации первого фазирующего блока соединен с соответствующим входом блока поиска СЦС, выход наличия синхронизации второго фазирующего блока соединен с соответствующим входом блока поиска СЦС, выход которого является выходом наличия синхронизации устройства для синхронизации, выход нулевого состояния второго фазирующего блока соединен с соответствующим входом блока поиска СЦС, входы конца цикла и конца сверхцикла которого соединены с соответствующими выходами первого ОЗУ, выход синхронной установки в ноль блока поиска СЦС соединен с соответствующим входом ГО, тактовый вход блока поиска СЦСК является тактовым входом устройства.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: второго фазирующего блока, блока поиска сверхцикловой синхрокомбинации, блока поиска сверхцикловой синхронизации.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в устройство для синхронизации с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют сократить время поиска синхронизма цифровых передач, имеющих сверхцикловую структуру.

Таким образом, изобретение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи с временным уплотнением цифровых потоков.

Таким образом, изобретение соответствует критерию "промышленная применимость".

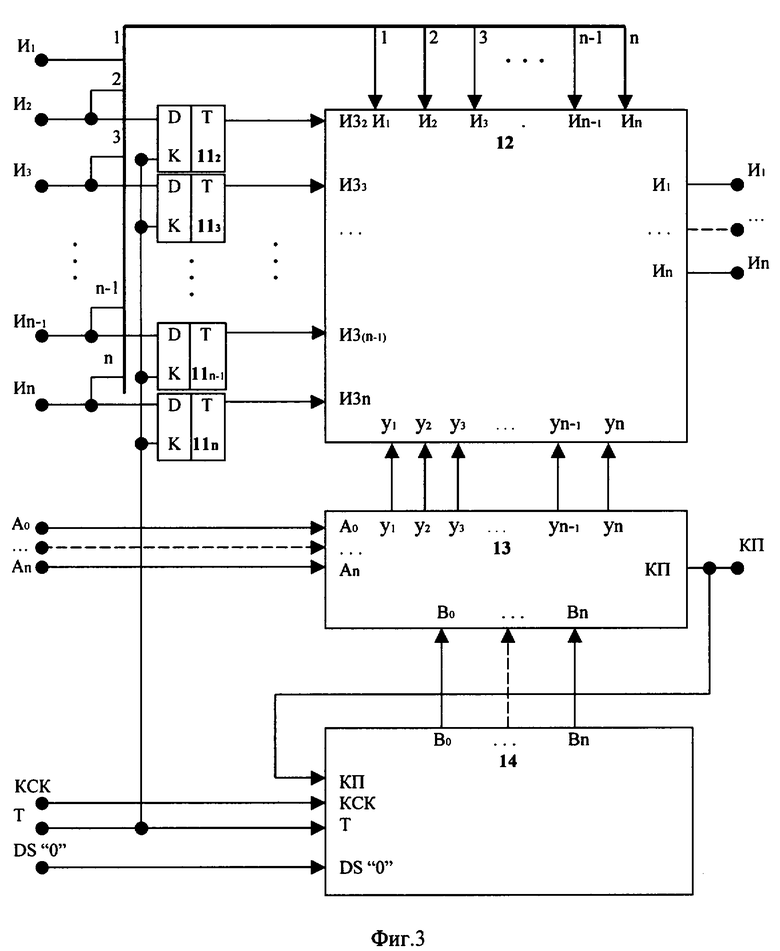

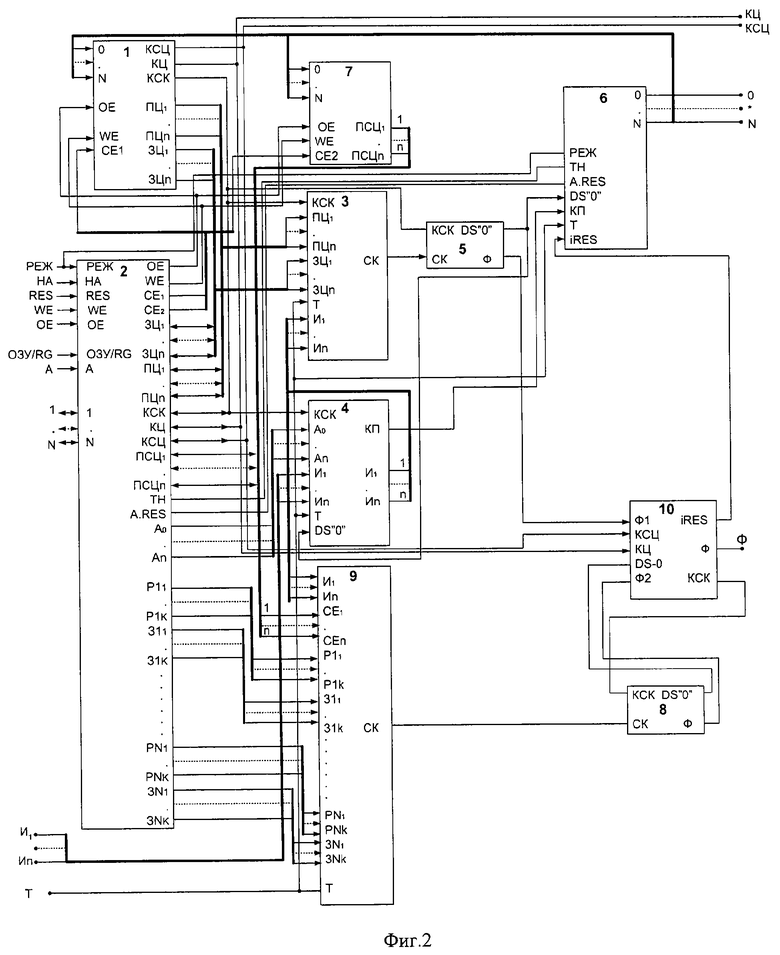

На фиг.1 представлен пример цифровой передачи со сверхцикловой структурой, на фиг.2 - структурная электрическая схема устройства для синхронизации, на фиг.3 - структурная электрическая схема блока коммутации информационных сигналов.

Устройство для синхронизации (фиг.2), содержит первое оперативное запоминающее устройство (ОЗУ) 1, блок настройки режима работы (блок настройки РР) 2, дешифратор цикловой синхрокомбинации (дешифратор ЦСК) 3, блок коммутации информационных сигналов (блок коммутации ИС) 4, первый фазирующий блок 5, генераторное оборудование (ГО) 6, второе ОЗУ 7, второй фазирующий блок 8, блок поиска сверхцикловой синхрокомбинации (блок поиска СЦСК) 9, блок поиска сверхциклового синхронизма (блок поиска СЦС) 10, причем тактовый вход (вход Т) устройства для синхронизации соединен с соответствующими входами дешифратора ЦСК 3, блока коммутации ИС 4, ГО 6, блока поиска СЦСК 9, адресные выходы (выходы 0, ..., N) ГО 6 соединены с соответствующими входами первого ОЗУ 1 и второго ОЗУ 7 и являются адресными выходами устройства для синхронизации, выход чтения (выход ОЕ) и выход записи (выход WE) блока настройки РР 2 соединены с соответствующими входами первого и второго ОЗУ, первый выход выбора (выход СЕ1) и второй выход выбора (выход СЕ2) блока настройки РР 2 соединены соответственно с входами выбора первого и второго ОЗУ, входы/выходы конца сверхцикла (вход/выход КСЦ) и конца цикла (вход/выход КЦ) первого ОЗУ 1 соединены с соответствующими входами/выходами блока настройки РР 2 и являются выходами конца сверхцикла и конца цикла устройства для синхронизации, вход/выход конца синхрокомбинации (вход/выход КСК) первого ОЗУ 1 соединен с соответствующими входами дешифратора ЦСК 3, блока коммутации ИС 4, первого фазирующего блока 5 и входом/выходом блока настройки РР 2, входы/выходы позиций (входы/выходы ПЦ1, ..., ПЦn) и значений (входы/выходы ЗЦ1, ..., ЗЦn) цикловой синхрокомбинации первого ОЗУ 1 соединены с соответствующими входами/выходами блока настройки РР 2 и входами дешифратора ЦСК 3, выход отклика (выход СК) которого соединен с соответствующим входом первого фазирующего блока 5, выход нулевого состояния (выход DS "0") которого соединен с соответствующими входами блока коммутации ИС 4 и ГО 6, входы тактов настройки (вход ТН) и асинхронной установки в ноль (вход A.RES) которого соединены с соответствующими выходами блока настройки РР 2, выходы которого, определяющие количество информационных входов устройства для синхронизации (выходы А0, ..., An) соединены с соответствующими входами блока коммутации ИС 4, информационные входы (входы И1, ..., Иn) которого являются информационными входами устройства для синхронизации, информационные входы (входы И1, ..., Иn) дешифратора ЦСК 3 соединены с соответствующими выходами блока коммутации ИС 4, выход конца перекоммутации (выход КП) которого подключен к соответствующему входу ГО 6, информационные входы/выходы (входы/выходы 1, ..., N), входы выбора режима (вход РЕЖ), нового адреса (вход НА), установки в ноль (вход RES), записи (вход WE), чтения (вход ОЕ), выбора настраиваемого ОЗУ (вход А), выбора настройки ОЗУ или регистра (вход ОЗУ/RG) блока настройки РР 2 являются соответствующими входами устройства для синхронизации, вход выбора режима (вход РЕЖ) ГО 6 соединен с соответствующим входом устройства для синхронизации, входы/выходы позиций сверхцикловой синхрокомбинации (входы/выходы ПСЦ1, ..., ПСЦn) второго ОЗУ 7 соединены с разрешающими входами (входы CE1...CEn) блока поиска СЦСК 9 и входами/выходами блока настройки РР 2, выходы используемых разрядов регистров (выходы P11, ..., P1k, ..., PN1, ..., PNk) и значений сверхцикловой синхрокомбинации (выходы З11, ..., З1k, ..., ЗN1, ..., ЗNk) блока настройки РР 2 соединены с соответствующими входами блока поиска СЦСК 9, информационные выходы (выходы И1, ..., Иn) блока коммутации ИС 4 соединены с соответствующими входами блока поиска СЦСК 9, выход которого (выход СК) соединен с соответствующим входом второго фазирующего блока 8, вход конца синхрокомбинации (вход КСК) которого соединен с соответствующим выходом блока поиска СЦС 10, выход наличия синхронизации (выход Ф) первого фазирующего блока 5 соединен с входом Ф1 блока поиска СЦС 10, выход наличия синхронизации (выход Ф) второго фазирующего блока 8 соединен с входом Ф2 блока поиска СЦС 10, выход которого является выходом наличия синхронизации (выход Ф) устройства для синхронизации, выход нулевого состояния (выход DS "0") второго фазирующего блока 8 соединен с соответствующим входом блока поиска СЦС 10, выходы КЦ и КСЦ первого ОЗУ 1 соединены с соответствующими входами блока поиска СЦС, вход синхронной установки в ноль (вход iRES) ГО 6 соединен с соответствующим выходом блока поиска СЦС 10.

Блок коммутации информационных сигналов (блок коммутации ИС) 4 (фиг.3) содержит триггеры 112, ..., 11n, коммутатор 12, дешифратор 13, счетчик 14, причем первый вход (вход И1) текущего значения информационного сигнала соединен с соответствующим входом коммутатора 12, от второго до n-го входов (входы И2, ..., Иn) текущих значений информационных сигналов соединены с соответствующими входами коммутатора 12 и соответственно с информационными входами (входы D) триггеров 112, ..., 11n, выходы которых соединены соответственно с входами ИЗ2, ..., ИЗn коммутатора 12, управляющие входы (входы У1, ..., Уn) коммутатора 12 соединены с соответствующими выходами дешифратора 13, информационные выходы (выходы И1, ..., Иn) коммутатора 22 являются соответствующими выходами блока коммутации ИС 4. Входы блока коммутации ИС 4, определяющие количество информационных входов устройства для синхронизации (входы А0, ..., An) соединены с соответствующими входами дешифратора 13, входы В0, ..., Вn которого соединены с соответствующими выходами разрядов счетчика 14, выход конца перекоммутации (выход КП) дешифратора 13 соединен с соответствующим входом счетчика 14 и является соответствующим выходом блока коммутации ИС 4, вход конца синхрокомбинации (вход КСК) блока коммутации ИС 4 соединен с соответствующим входом счетчика 14, тактовый вход (вход Т) блока коммутации ИС 4 соединен с тактовыми входами триггеров 112, ..., 11n и счетчика 14, вход DS "0" которого является соответствующим входом блока коммутации ИС 4.

Устройство для синхронизации работает следующим образом. Устройство для синхронизации имеет два режима работы. Первый - режим настройки и диагностики, второй - режим работы.

В первом режиме на входы блока настройки РР 2 поступают сигналы с контроллера, работающего совместно с персональной электронной вычислительной машиной (ПЭВМ). Режим настройки и диагностики разрешается сигналом Лог."0", который поступает на вход выбора режима (вход РЕЖ) блока настройки РР 2. Сигналом Лог."1", поступающим на вход выбора настройки оперативных запоминающих устройств или регистра (вход ОЗУ/RG) блока настройки РР 2, разрешается настройка оперативных запоминающих устройств (ОЗУ). Выбор настраиваемого ОЗУ осуществляется сигналом, поступающим на вход А блока настройки РР 2. При настройке первого ОЗУ 1 на его вход выбора (вход СЕ1) поступает сигнал Лог."0" с выхода СЕ1 блока настройки РР 2, разрешая работу первого ОЗУ 1. При записи информации в первое ОЗУ 1 с выхода чтения (выход ОЕ) блока настройки РР 2 на соответствующий вход первого ОЗУ 1 поступает сигнал Лог."1". На вход установки в ноль (вход A.RES) блока настройки РР 2 поступает импульсный сигнал положительной полярности, который с выхода RES блока настройки РР 2, поступая на соответствующий вход ГО 6, устанавливает его счетчик в нулевое состояние. Адресные 0, ..., N выходы счетчика ГО 6 соединены с соответствующими адресными входами первого 1 и второго 7 ОЗУ. Далее по сигналу записи, поступающему с выхода записи (выход WE) блока настройки РР 2 на соответствующий вход первого ОЗУ 1, в последнее по нулевому адресу осуществляется запись данных, поступающих с соответствующих входов/выходов блока настройки РР 2. После этого на вход нового адреса (вход НА) блока настройки РР 2 поступает сигнал, который, поступая с выхода тактов настройки (выход ТН) блока настройки РР 2 на соответствующий вход ГО 6, осуществляет смену адреса его счетчика и, следовательно, адреса первого ОЗУ 1.

Далее запись данных по новому адресу осуществляется также, как было описано ранее.

Для проверки правильности настройки первого ОЗУ 1 сигналом установки в ноль, поступившем с выхода A.RES блока настройки РР 2 на соответствующий вход ГО 6, его счетчик устанавливается в нулевое состояние. После этого сигналом Лог."1", поступившем на вход записи (вход WE) блока настройки РР 2 и далее с выхода WE блока настройки РР 2 на соответствующий вход первого ОЗУ 1, последнее переводится в режим чтения. Затем сигналом Лог."0", поступившем на вход чтения (вход ОЕ) блока настройки РР 2 и далее с выхода ОЕ этого блока на соответствующий вход первого ОЗУ 1, осуществляется считывание информации по нулевому адресу первого ОЗУ 1. При этом сигналы с выходов последнего поступают на соответствующие входы блока настройки РР 2 и далее в контроллер ПЭВМ для их сравнения с исходными. Затем по сигналу нового адреса осуществляется смена адреса первого ОЗУ 1 и считывание данных по новому адресу также, как было описано ранее.

Аналогично осуществляется настройка и проверяется правильность настройки второго ОЗУ 7. Номер настраиваемого ОЗУ задается сигналом, поступающим на вход А блока настройки РР 2.

После настройки и проверки правильности настройки первого 1 и второго 7 ОЗУ осуществляется настройка регистров запоминания блока настройки РР 2. Настройка регистров запоминания разрешается сигналом Лог."0", поступающим на ОЗУ/RG вход блока настройки РР 2. При этом порядок настройки и проверки ее правильности такой же, как для ОЗУ.

Перевод устройства для синхронизации в режим работы осуществляется сигналом Лог."1", поступающим на вход РЕЖ блока настройки РР 2. При этом сигналами выбора, поступающими с СЕ1 и СЕ2 выходов блока настройки РР 2 разрешается работа первого 1 и второго 7 ОЗУ, а сигналами Лог."0" и Лог."1", поступающими соответственно с выходов чтения ОЕ и записи WE блока настройки РР 2 на соответствующие входы первого 1 и второго 7 ОЗУ, последние переводятся в режим считывания данных. В режиме настройки на вход тактов счетчика позиций ГО 6 поступают такты настройки с выхода ТН блока настройки РР 2, а в режиме работы - с тактового входа Т устройства для синхронизации.

Работа устройства для синхронизации осуществляется следующим образом. На адресные входы (входы 0, ..., N) первого ОЗУ 1 и второго ОЗУ 7 поступают сигналы с соответствующих выходов ГО 6, при этом на соответствующих адресах на выходах ОЗУ 1 формируются сигналы конца сверхцикла (выход КСЦ), конца цикла (выход КЦ), конца синхрокомбинации (выход КСК), позиций (выходы ПЦ1, ..., ПЦn) и значений (выходы ЗЦ1, ..., ЗЦn) цикловой синхрокомбинации, а на выходах ПСЦ1, ..., ПСЦn ОЗУ 7 формируются сигналы позиций сверхцикловой синхрокомбинации. Первоначально осуществляется цикловая синхронизация, а затем, после ее нахождения, сверхцикловая синхронизация устройства. Цикловая синхронизация осуществляется следующим образом. Сигналы позиций, значений и конца цикловой синхрокомбинации с соответствующих выходов первого ОЗУ 1, информационные сигналы с соответствующих информационных выходов (выходы И1, ..., Иn) блока коммутации ИС 4, а также тактовые сигналы с тактового входа Т устройства для синхронизации поступают на соответствующие входы дешифратора ЦСК 3.

Дешифратор ЦСК 3 осуществляет сравнение значений информационных сигналов с заданными в первом ОЗУ 1 на позициях цикловой синхрокомбинации, также заданных в первом ОЗУ 1, и формирование результата сравнения на его выходе отклика (выходе СК). В случае положительного отклика на СК выходе дешифратора ЦСК 3 формируется сигнал Лог."1", а в случае отрицательного отклика - сигнал Лог."0". Сигнал отклика с СК выхода дешифратора ЦСК 3 и сигнал конца цикловой синхрокомбинации с КСК выхода первого ОЗУ 1 поступают на соответствующие входы первого фазирующего блока 5. До появления первого положительного отклика с СК выхода дешифратора ЦСК 3 первый фазирующий блок 5 находится в нулевом состоянии и сигналом Лог."1", поступающим с его выхода нулевого состояния (выход DS "0") на соответствующие входы блока коммутации ИС 4 и ГО 6, разрешается работа блока коммутации ИС 4 и удаление тактов в ГО 6. При отсутствии положительного отклика на выходе СК сигналом конца перекоммутации поступившем с выхода (выход КП) блока коммутации ИС 4 на соответствующий вход ГО 6, осуществляется удаление (пропуск) одного такта. Таким образом, изменяется фаза работы счетчика позиций ГО 6 по отношению к фазе цифровой передачи. В описанном режиме устройство для синхронизации работает до тех пор, пока не будет найдена первая цикловая синхрокомбинация. После поступления на соответствующие входы первого фазирующего блока 5 положительного отклика и конца цикловой синхрокомбинации реверсивный счетчик этого блока устанавливается в режим положительного счета и увеличивает свое состояние на единицу. При этом сигналом Лог."0", сформированном на DS "0" выходе первого фазирующего блока 5, запрещается удаление такта в ГО 6 и блока коммутации ИС 4. Таким образом, при наличии сигнала положительного отклика на СК входе первого фазирующего блока 5 реверсивный счетчик последнего увеличивает свое состояние на единицу, а при отсутствии положительного отклика - уменьшает на единицу. Когда разность количества сигналов положительного и отрицательного откликов достигает заданного в первом фазирующем блоке 5 значения, устройство для синхронизации переходит в режим цикловой синхронизации. В этом режиме устройство для синхронизации находится до тех пор, пока разность количества сигналов отрицательного и положительного откликов достигнет заданного в первом фазирующем блоке 5 значения. При этом первый фазирующий блок 5 устанавливается в нулевое состояние, и устройство для синхронизации переходит в режим поиска цикловой синхронизации, как было описано ранее.

Блок коммутации ИС 4 (фиг.3) предназначен для преобразования информационных сигналов, поступающих на его входы, таким образом, чтобы первый информационный сигнал в сверхцикле цифровой передачи находился на первом информационном выходе этого блока. Работа блока коммутации ИС 4 будет описана далее.

Пока не найдена цикловая синхронизация запрещена работа устройства для синхронизации по поиску сверхцикловой синхронизации сигналом Лог."0", поступающим с выхода Ф первого фазирующего блока 5 на вход Ф1 блока поиска СЦС. При этом на выходе КСК блока поиска СЦС 10 запрещено формирование сигнала, поступающего на вход КСК второго фазирующего блока 8, и последний находится в нулевом состоянии. При поиске цикловой синхронизации синхронная установка в ноль ГО 6 осуществляется сигналом с выхода КСЦ ОЗУ 1, поступающим через вход КСЦ и выход i.RES блока поиска СЦС на вход i.RES ГО 6.

После нахождения цикловой синхронизации разрешается поиск сверхцикловой синхронизации. При этом сигналами Лог."1", поступающими с выхода Ф первого фазирующего блока 5 на вход Ф1 блока поиска СЦС и с выхода DS "0" нулевого состояния второго фазирующего блока 8 на вход DS "0" блока поиска СЦС 10, разрешается прохождение сигнала с выхода КЦ ОЗУ 1 через вход КЦ и выход i.RES блока поиска СЦС 10 на вход i.RES синхронной установки в ноль ГО 6.

Поиск сверхцикловой синхронизации осуществляется следующим образом. Сигналы с выходов позиций сверхцикловой синхрокомбинации (выходы ПСЦ1, ..., ПСЦn) второго ОЗУ 7 поступают на разрешающие входы (входы CE1, ..., СЕn) блока поиска СЦСК 9. На информационные входы (входы И1, ..., Иn) блока поиска СЦСК 9 поступают сигналы с соответствующих информационных выходов (выходы И1, ..., Иn) блока коммутации ИС 4. Значение сверхцикловой синхрокомбинации для каждого информационного входа задается сигналами, поступающими с выходов З11, ..., З1k, ..., ЗN1, ..., ЗNk блока настройки РР 2 на соответствующие входы блока поиска СЦСК 9. Длина сверхцикловой синхрокомбинации, в позициях, для каждого информационного входа задается сигналами, поступающими с выходов P11, ..., P1k, ..., PN1, ..., PNk блока настройки РР 2 на соответствующие входы блока поиска СЦСК 9.

Практика показала, что оптимальным количеством позиций сверхцикловой синхрокомбинации на одном информационном входе при разных видах модуляции является 16 позиций. Если число позиций сверхцикловой синхрокомбинации на одном информационном входе превышает число 16, то во втором ОЗУ 7 задаются последние шестнадцать позиций сверхцикловой синхрокомбинации. Если число позиций сверхцикловой синхрокомбинации менее шестнадцати, то для недостающих позиций поступают сигналы Лог."0" с соответствующих выходов блока настройки РР 2.

При нахождении сверхцикловой синхрокомбинации на выходе СК блока поиска СЦСК 9 формируется сигнал положительного отклика. После поступления на вход СК второго фазирующего блока 8 первого положительного отклика и на вход КСК сигнала, поступающего при наличии цикловой синхронизации с выхода КЦ ОЗУ 1 через вход КЦ и выход КСК блока поиска СЦС 10, реверсивный счетчик второго фазирующего блока устанавливается в режим положительного счета и увеличивает свое состояние на единицу. При этом сигналом Лог."0" на выходе DS "0" второго фазирующего блока 8 запрещается прохождение сигнала с выхода КЦ ОЗУ 1 на выход КСК блока поиска СЦС 10 и разрешается прохождение на этот выход сигнала с выхода КСЦ ОЗУ 1. Этим же сигналом запрещается прохождение сигнала с выхода КЦ на вход i.RES блока поиска СЦС 10 и далее на вход i.RES ГО 6. Теперь на вход i.RES ГО 6 поступает сигнал с выхода КСЦ ОЗУ 1 через вход КСЦ и выход i.RES блока поиска СЦС 10.

Работа второго фазирующего блока 8 осуществляется так же, как работа первого фазирующего блока 5.

При переходе устройства в режим сверхцикловой синхронизации на выходе Ф второго фазирующего блока 8 появляется сигнал Лог."1", который поступает на вход Ф2 блока поиска СЦС 10. При этом, на выходе Ф этого блока появляется сигнал Лог."1", который указывает на наличие цикловой и сверхцикловой синхронизации устройства.

Блок коммутации ИС 4 (фиг.3) работает следующим образом. Сигналы с информационных входов (входы И1, ..., Иn) блока коммутации ИС 4 поступают на соответствующие входы коммутатора 12, а с входов И2, ..., Иn - на входы триггеров 112, ..., 11n. С выходов триггеров 112, ..., 11n задержанные на один такт информационные сигналы поступают на входы ИЗ2, ..., ИЗn коммутатора 12. Сигналы с входов блока коммутации ИС 4, определяющих количество информационных входов (входы А0, ..., An), поступают на соответствующие входы дешифратора 13. Сигналы с входов КСК, DS "0" и Т блока коммутации ИС 4 поступают на соответствующие входы счетчика 14. При поиске цикловой синхронизации работа счетчика 14 разрешена сигналом Лог."1", поступающим на его вход DS "0". При поступлении сигналов на входы КСК и Т счетчика 14, последний изменяет свое состояние на единицу. Установка в нулевое состояние счетчика 14 осуществляется сигналом, поступающим с выхода конца перекоммутации (выход КП) дешифратора 13 на вход КП счетчика 14. Дешифратор 13 осуществляет дешифрацию состояний счетчика 14. В соответствии с состоянием счетчика 14 на одном из управляющих выходов (выходы У1, ..., Уn) дешифратора появляется сигнал Лог."1", который, поступая на соответствующий управляющий вход коммутатора 12, определяет порядок перестроения информационных сигналов. Счетчик 14 изменяет свое состояние один раз за сверхцикл цифровой передачи. Полный цикл работы блока коммутации ИС 4 совершается за n сверхциклов, где n - количество информационных входов устройства для синхронизации.

Перекоммутация информационных сигналов осуществляется следующим образом. В нулевом состоянии счетчика 14 сигналом Лог."1", поступающим на вход У1 коммутатора 12, осуществляется коммутация текущих информационных сигналов с входов И1, ..., Иn коммутатора 12 на его выходы И1, ..., Иn. В первом состоянии счетчика 14 сигналом Лог."1", поступающим на вход У2 коммутатора 12, осуществляется коммутация задержанного на один такт (предыдущее значение) информационного сигнала с входа ИЗn коммутатора 12 на его выход И1, а текущих информационных значений - с входов И1, ..., Иn-1 соответственно на выходы И2, ..., Иn. Во втором состоянии счетчика 14 сигналом Лог."1", поступающим на вход У3 коммутатора 12, осуществляется коммутация предыдущих значений информационных сигналов с входов ИЗn-1 и ИЗn коммутатора 12 соответственно на его входы И1 и И2, а текущих значений - с входов И1, ..., Иn-2 соответственно на выходы И3, ..., Иn и т.д. В n-м состоянии счетчика 14 сигналом Лог."1", поступающим на вход Уn коммутатора 12, осуществляется коммутация предыдущих значений информационных сигналов с входов ИЗ2, ..., ИЗn коммутатора 12 соответственно на его входы И1, ..., Иn-1, а текущего значения - с входа И1 соответственно на выход Иn.

Если за цикл перекоммутации не будет обнаружена цикловая синхрокомбинация, то по сигналу конца перекоммутации, поступившему с КП выхода блока коммутации ИС 4 на КП вход ГО 6, в последнем осуществляется пропуск одного такта и цикл работы блока коммутации ИС 4 повторяется, как было описано ранее.

После нахождения первой цикловой синхрокомбинации сигналом Лог."0", поступающим на DS "0" вход блока коммутации ИС 4, дальнейшая работа последнего запрещается.

Для технической реализации устройства для синхронизации использованы статические оперативные запоминающие устройства (ОЗУ) импортного производства типа KM68257CJ-15 - фирмы SEC и программируемая пользователем логическая интегральная схема (ППЛИС) XC4020XLA - фирмы XILINX.

Предлагаемое изобретение позволяет сократить в n2 раз, по сравнению с прототипом, время поиска синхронизма цифровых передач с различными видами модуляции, имеющих сверхцикловую структуру за счет реализации метода последовательно - параллельного поиска синхронизации, при котором поиск цикловой синхронизации осуществляется последовательным методом, а сверхцикловой - параллельным методом, где n - количество циклов в сверхцикле цифровой передачи.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Устройство для передачи и приема информации с временным уплотнением каналов | 1977 |

|

SU660282A1 |

Изобретение относится к технике цифровой связи, а именно к устройствам для синхронизации цифровых систем передачи информации с временным уплотнением цифровых потоков. Сущность изобретения состоит в том, что в устройство для синхронизации, содержащее первое и второе ОЗУ, блок настройки режимов работы, дешифратор цикловой синхрокомбинации, блок коммутации информационных сигналов, первый фазирующий блок и генераторное оборудование, введены второй фазирующий блок, блок поиска сверхцикловой синхрокомбинации и блок поиска сверхцикловой синхронизации. Технический результат, достигаемый при осуществлении изобретения, состоит в сокращении времени поиска синхронизма цифровых передач с различными видами модуляции, имеющих сверхцикловую структуру. 3 ил.

Устройство для синхронизации, содержащее первое и второе оперативные запоминающие устройства (ОЗУ), блок настройки режима работы (РР), дешифратор цикловой синхрокомбинации (ЦСК), блок коммутации информационных сигналов (ИС), первый фазирующий блок, генераторное оборудование (ГО), причем тактовые входы дешифратора ЦСК, блока коммутации ИС и ГО соединены между собой и являются тактовым входом устройства, адресные выходы ГО соединены с соответствующими входами первого и второго ОЗУ и являются адресными выходами устройства, выход чтения, выход записи и первый и второй выходы выбора блока настройки РР соединены с соответствующими входами первого и второго ОЗУ, входы/выходы конца сверхцикла и конца цикла первого ОЗУ соединены с соответствующими входами/выходами блока настройки РР и являются выходами конца сверхцикла и конца цикла устройства, вход/выход конца синхрокомбинации первого ОЗУ соединен с соответствующими входами дешифратора ЦСК, блока коммутации ИС, первого фазирующего блока и входом/выходом блока настройки РР, входы/выходы позиций и значений цикловой синхрокомбинации первого ОЗУ соединены с соответствующими входами/выходами блока настройки РР и входами дешифратора ЦСК, выход отклика которого соединен с соответствующим входом первого фазирующего блока, выход нулевого состояния которого соединен с соответствующими входами блока коммутации ИС и ГО, входы тактов настройки и асинхронной установки в ноль которого соединены с соответствующими выходами блока настройки РР, выходы которого, определяющие количество информационных входов устройства, соединены с соответствующими входами блока коммутации ИС, информационные входы которого являются информационными входами устройства, информационные входы дешифратора ЦСК соединены с соответствующими выходами блока коммутации ИС, выход конца перекоммутации которого подключен к соответствующему входу ГО, информационные входы/выходы, входы выбора режима, нового адреса, установки в ноль, записи, чтения, выбора настройки первого и второго ОЗУ, выбора настройки ОЗУ или регистров блока настройки РР являются соответствующими входами устройства, вход выбора режима ГО соединен с соответствующим входом устройства, отличающееся тем, что введены второй фазирующий блок, блок поиска сверхцикловой синхрокомбинации (СЦСК) и блок поиска сверхцикловой синхронизации (СЦС), причем входы/выходы позиций сверхцикловой синхрокомбинации второго ОЗУ соединены с разрешающими входами блока поиска СЦСК и входами/выходами блока настройки РР, выходы используемых разрядов регистров и значений сверхцикловой синхрокомбинации блока настройки РР соединены с соответствующими входами блока поиска СЦСК, информационные выходы блока коммутации ИС соединены с информационными входами блока поиска СЦСК, выход которого соединен с входом отклика второго фазирующего блока, вход конца синхрокомбинации которого соединен с соответствующим выходом блока поиска СЦС, выход наличия синхронизации первого фазирующего блока соединен с соответствующим входом блока поиска СЦС, выход наличия синхронизации второго фазирующего блока соединен с соответствующим входом блока поиска СЦС, выход которого является выходом наличия синхронизации устройства, выход нулевого состояния второго фазирующего блока соединен с соответствующим входом блока поиска СЦС, входы конца цикла и конца сверхцикла которого соединены с соответствующими выходами первого ОЗУ, выход синхронной установки в ноль блока поиска СЦС соединен с соответствующим входом ГО, тактовый вход блока поиска СЦС является тактовым входом устройства.

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| US 6751235 A, 15.06.2004 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Холодильная установка | 1983 |

|

SU1150451A2 |

Авторы

Даты

2007-06-27—Публикация

2005-07-05—Подача