Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем с повышенной достоверностью выдаваемых данных.

Известно устройство для умножения (АС СССР №1024906, МКИ 6 G 06 F 7/49, заявлено 14.08.81, опубл. 23.06.83), содержащее регистры множителя и множимого, регистр результата, блок анализа знака, блок умножения, комбинационный сумматор и блок суммирования в избыточной системе счисления. Устройство обеспечивает выполнение операций в избыточной системе счисления.

Недостатком данного устройства является то, что в режиме функционирования не проводится проверка правильности выдаваемых данных, что, в свою очередь, не дает возможности повысить достоверность выдаваемых результатов.

Причины, препятствующие достижению требуемого технического результата, заключаются в отсутствии средств, обеспечивающих возможность проверки правильности выдаваемого кода данных.

Известно устройство для умножения чисел по модулю (патент РФ №2143723, МКИ 7 G 06 F 7/52, заявлено 29.07.98, опубл. 27.12.99), содержащее первый и второй преобразователи двоичного кода по первому внутреннему модулю, первый и второй преобразователи двоичного кода по второму внутреннему модулю, с первого по шестой блоки элементов И, табличный вычислитель, преобразователи унитарного кода по первому и второму модулям и сумматор по модулю. Устройство обеспечивает умножение чисел в системе остаточных классов по двум модулям.

Недостаток данного устройства заключаются в том, что не проводится проверка правильности выдаваемых данных, что, в свою очередь, не дает возможности повысить достоверность выдаваемых результатов.

Причины, препятствующие достижению требуемого технического результата, заключаются в отсутствии средств, обеспечивающих возможность проверки правильности выдаваемого кода данных.

Известно устройство для сложения в коде “М из N”, наиболее близкое к заявляемому, позволяющее получить код произведения чисел в коде “М из N” в виде частичного произведения и значения переносов (АС СССР №1015372, МКИ 6 G 06 F 7/49, заявлено 17.07.81, опубл. 30.04.83), содержащее регистры первого и второго операндов, блок контроля, матрицу сложения и матрицу умножения, причем первые и вторые группы выходов регистров операндов подключены к входам матрицы сложения, третьи группы выходов регистров операндов соединены соответственно с первыми и вторыми входами блока контроля, первый и второй выходы которого соединены с выходами сигнала ошибки устройства, выходы матрицы сложения соединены с выходами суммы устройства и первыми входами матрицы умножения, вторые входы которой соединены с третьими выходами блока контроля, выходы частичных произведений и выходы сигналов переносов матрицы умножения соединены с соответствующими выходами устройства. В приведенном в описании варианте реализации устройства представлено техническое решение для умножения в шестеричном коде “2 из 4”.

Первый недостаток данного устройства заключаются в том, что для получения окончательного значения произведения необходимо преобразование частичных произведений и сигналов переносов на дополнительном оборудовании.

Причины, препятствующие достижению требуемого технического результата, заключаются в том, что на выход устройства выдаются только частичные произведения и сигналы переносов.

Второй недостаток данного устройства заключается в том, что в нем проводится контроль кодов входных операндов, но отсутствует контроль полученного результата.

Причины, препятствующие достижению требуемого технического результата, заключаются в том, что в устройстве отсутствуют средства, обеспечивающие контроль результата операции умножения.

Задачей, на решение которой направлено предлагаемое техническое решение, является построение вычислительных систем с повышенной достоверностью получения результатов и равномерного распределения энергии в процессе работы, что особенно важно при реализации аппаратуры системы в виде СБИС.

Технический результат, достигаемый при осуществлении изобретения, заключается в повышении достоверности выдаваемого результата при обеспечении поразрядного контроля результата операции умножения чисел и равномерного распределения энергии по разрядам в процессе работы, что особенно важно при реализации аппаратуры системы в виде СБИС.

Существенные признаки, совпадающие у прототипа и заявленного устройства, следующие: матрица сложения в прототипе выполняет функции блока сумматоров в заявленном устройстве, матрица умножения в прототипе выполняет функции, аналогичные блоку частичных произведений в заявленном устройстве, блок контроля в прототипе выполняет функции, аналогичные блоку контроля в заявленном устройстве.

Заявляемый технический результат достигается тем, что в устройство для умножения чисел в коде “1 из 4”, содержащее блок частичных произведений, блок сумматоров и блок контроля, причем выходы блока контроля соединены с выходами признака ошибки устройства, введены регистр тетрадного сдвига и регистр результата в коде “1 из 4”, причем входы четверичных разрядов в коде “1 из 4” первого сомножителя устройства соединены с информационными входами соответствующих тетрад регистра тетрадного сдвига, выходы младшей тетрады которого соединены со входами первой группы блока частичных произведений, входы второй группы которого соединены со входами четверичных разрядов в коде “1 из 4” второго сомножителя устройства, выходы блока частичных произведений соединены со входами первой группы блока сумматоров, входы второй группы которого соединены с выходами группы старших четверичных разрядов регистра результата в коде “1 из 4”, выходы групп младших и старших четверичных разрядов которого соединены со входами блока контроля, выходы блока сумматоров соединены с информационными входами четверичных разрядов регистра результата в коде “1 из 4”, вход установки которого соединен со входом записи устройства и входом записи регистра тетрадного сдвига, вход тетрадного сдвига которого соединен со входом записи регистра результата в коде “1 из 4” и входом синхроимпульсов сдвига устройства, вход константы 0 в коде “1 из 4” которого соединен со входами константы 0 блока частичных произведений и блока сумматоров, при этом блок частичных произведений содержит n+1 узел частичных произведений в коде “1 из 4”, где n - количество четверичных разрядов сомножителей, входы четверичных разрядов в коде “1 из 4” первого и второго сомножителей с первого по n-й узлов частичных произведений в коде “1 из 4” соединены со входами соответствующих разрядов соответственно первой и второй групп блока частичных произведений, выходы которого соединены с выходами с первого по (n+1)-й узлов частичных произведений в коде “1 из 4”, входы четверичных разрядов в коде “1 из 4” первого и второго сомножителей (n+1)-го узла частичных произведений в коде “1 из 4” соединены со входом константы 0 блока частичных произведений, выходы первого и второго переносов i-го узла частичных произведений в коде “1 из 4”, где i=1,2,... ,n, соединены со входами соответственно первого и второго переносов (i+1)-гo узла частичных произведений в коде “1 из 4” блока частичных произведений, причем блок сумматоров содержит n+1 сумматор в коде “1 из 4”, входы четверичных разрядов в коде “1 из 4” первого слагаемого с первого по (n+1)-й сумматоров в коде “1 из 4” соединены со входами соответствующих разрядов первой группы блока сумматоров, выходы которого соединены с выходами с первого по (n+1)-й сумматоров в коде “1 из 4”, вход четверичного разряда второго слагаемого (n+1)-го сумматора в коде “1 из 4” соединен со входом константы 0 блока сумматоров, выход переноса i-го сумматора в коде “1 из 4”, где i=1,2,... ,n, соединен со входом переноса (i+1)-гo сумматора в коде “1 из 4”, входы четверичных разрядов второго слагаемого с первого по n-й сумматоров в коде “1 из 4” соединены со входами соответствующих разрядов второй группы блока сумматоров, при этом регистр результата в коде “1 из 4” содержит 2n тетрад четверичных разрядов, выходы и информационные входы с n-й по 2n-ю тетрад четверичных разрядов регистра результата в коде “1 из 4” соединены соответственно с выходами старшей группы четверичных разрядов и соответственно с первого по (n+1)-й информационными входами четверичных разрядов регистра результата в коде “1 из 4”, информационные входы с первой по (n-1)-ю тетрад четверичных разрядов регистра результата в коде “1 из 4” соединены с выходами четверичных разрядов соответственно со второй по n-ю тетрад четверичных разрядов регистра результата в коде “1 из 4”, при этом блок контроля содержит 2n узлов контроля кода “1 из 4”, входы и выходы которых подключены соответственно к соответствующим четверичным разрядам входов и выходов блока контроля.

Возможность проведения контроля данных основана на том, что четверичный код “1 из 4” имеет в составе всегда только одну единицу (все возможные комбинации этого кода 0001=0; 0010=1; 0100=2 и 1000=3) и, таким образом, из общего числа возможных ошибочных комбинаций для 4-разрядного слова, равного 15, количество неопознанных ошибок составит только 3. Таким образом, заявляемое устройство обеспечивает распознавание 80% ошибок.

Из возможных вариантов кодов “М из N” код “1 из 4” обладает наибольшей эффективностью. Во-первых, операция преобразования двоичного кода в код “М из N” и обратно, характерная для цифровых систем обработки, содержащих ряд подсистем, при М≠ 1 и N≠ 2m, где m=1, 2,... , требует анализа всей последовательности цифр двоичного кода, что приводит к очень большим затратам оборудования при реализации. Например, при построении такого преобразователя кода для 32-разрядного двоичного числа с использованием блока памяти потребуется от 5 до нескольких десятков мегабайт. Схемотехническая реализация таких преобразователей потребует оборудования, объем которого значительно превысит объем оборудования операционных устройств.

С другой стороны, для преобразования кода “1 из 2m” потребуется D/m (D - разрядность двоичного кода) дешифраторов для преобразования двоичного кода и столько же шифраторов для обратного преобразования. Это связано с тем, что преобразование осуществляется поразрядно. Например, для 32-разрядного двоичного кода преобразователь кода в “1 из 2”, “1 из 4”, “1 из 8” и т.д. потребует соответственно 32 одновходовых, 16 двухвходовых, 11 трехвходовых и т.д. дешифраторов и столько же шифраторов для обратного преобразования. Такое схемотехническое решение требует минимального количества оборудования и эффективно реализуется при построении систем на кристаллах СБИС или ПЛИС.

Во-вторых, реализация схемотехнических решений для кодов “1 из 2”, “1 из 4”, “1 из 8” и т.д. также обладает различной эффективностью. Это связано, с одной стороны, с различным количеством распознаваемых ошибок и, с другой стороны, с различным превышением объема требуемого оборудования для обработки по сравнению с двоичным кодом. Поэтому для оценки эффективности использования того или иного кода “1 из 2m” целесообразно рассмотреть величину отношения процента обнаруживаемых ошибок к величине превышения требуемого оборудования по отношению к двоичному коду.

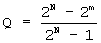

В общем случае количество комбинаций для кода “М из N” равно величине  , тогда количество необнаруживаемых ошибок составит

, тогда количество необнаруживаемых ошибок составит  -1 (одна верная комбинация). Количество всех возможных ошибочных кодов, очевидно, равно 2N-1. Тогда доля обнаруживаемых ошибок Q определяется соотношением

-1 (одна верная комбинация). Количество всех возможных ошибочных кодов, очевидно, равно 2N-1. Тогда доля обнаруживаемых ошибок Q определяется соотношением

.

.

Для кодов “1 из 2m” величина  =2m, тогда

=2m, тогда

.

.

Величина превышения требуемого оборудования К для кодов “1 из 2m”, очевидно, равна  .

.

Тогда эффективность использования кода “1 из 2m”

В табл.1 приведены расчетные данные для кодов “1 из 2m” при различных значениях m.

Из данных, приведенных в табл.1, видно, что наибольшей эффективностью обладает код “1 из 4”, имеющий максимальное значение показателя эффективности Е=0,40.

Кроме того, распределение энергии при вводе, хранении и выводе данных в коде “1 из 4” всегда одинаково по всем разрядам кода данных, т.к. структурно каждый четверичный разряд содержит строго один высокий и три низких потенциала. Это свойство особенно важно при создании устройств и систем на кристаллах СБИС.

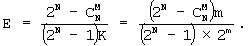

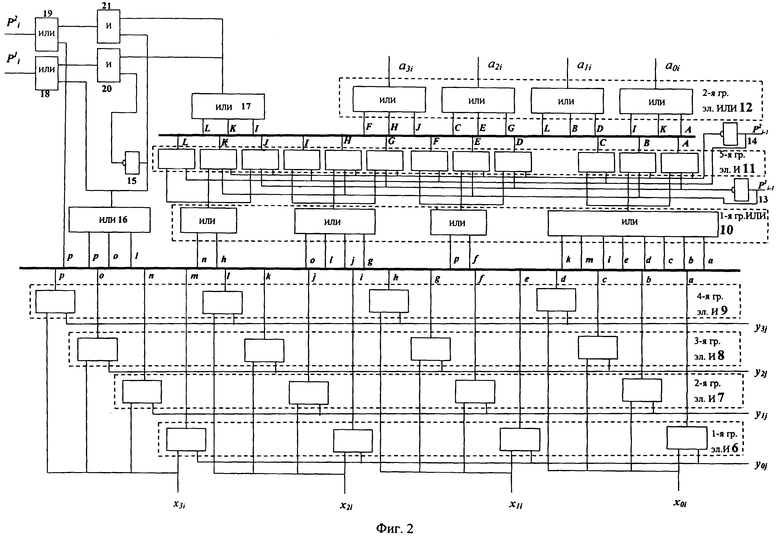

На фиг.1 представлена функциональная схема устройства для умножения чисел в коде “1 из 4”; на фиг.2 представлен вариант реализации узла частичного произведения в коде “1 из 4”; на фиг.3 показан вариант реализации сумматора в коде “1 из 4”; на фиг.4 приведены временные диаграммы управляющих сигналов.

Устройство для умножения чисел в коде “1 из 4” (фиг.1) содержит регистр тетрадного сдвига 1, блок частичных произведений 2, блок сумматоров 3, регистр результата в коде “1 из 4” 4, блок контроля 5, причем регистр тетрадного сдвига 1 осуществляет сдвиг в сторону младших разрядов потетрадно за один такт и содержит n тетрад четверичных разрядов в коде “1 из 4” 11-1n, где n - разрядность четверичного кода сомножителей, блок частичных произведений 2 содержит n+1 узел частичных произведений 21-2n+1, блок сумматоров 3 содержит n+1 сумматор в коде “1 из 4” 31-3n+1, регистр результата 4 в коде “1 из 4” содержит 2n тетрад четверичных разрядов в коде “1 из 4” 41-42n, блок контроля 5 содержит 2n узлов контроля кода “1 из 4” 51-52n.

Возможный вариант узла частичных произведений в коде “1 из 4” 2i (фиг.2) содержит с первой по четвертую группы элементов И 6-9, первую группу элементов ИЛИ 10, пятую группу элементов И 11, вторую группу элементов ИЛИ 12, с первого по третий элементы НЕ 13-15, с первого по четвертый элементы ИЛИ 16-19, первый и второй элементы И 20 и 21.

Возможный вариант сумматора в коде “1 из 4” 3i (фиг.3) содержит с первой по четвертую группы элементов И 22-25, первую группу элементов ИЛИ 26, пятую группу элементов И 27, вторую группу элементов ИЛИ 28, элемент НЕ 29 и элемент ИЛИ 30.

Устройство для умножения чисел в коде “1 из 4” работает следующим образом.

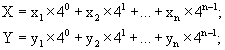

Числа Х и Y представляются в четверичной системе

n - количество четверичных разрядов.

Устройство работает по стандартному алгоритму:

где хi и уi представляются в коде “1 из 4”, суммирование частичных произведений проводится по соответствующим весам четверичных разрядов. В табл.2 даны коды преобразования входных значений в выходные при перемножении четверичных разрядов сомножителей в коде “1 из 4” и условия возникновения одного переноса П и двух переносов ПП в следующий четверичный разряд.

Очевидно, возникновение одного или двух переносов из предыдущего разряда не приводит к необходимости формирования дополнительного сигнала третьего переноса, т.к. максимальное значение кода частичного произведения при активном сигнале даже двух переносов из текущего разряда равно 0010 и, следовательно, даже два переноса из предыдущего разряда дадут результат 1000 без необходимости формирования дополнительного сигнала переноса.

В табл.3 даны коды преобразования входных значений в выходные при суммировании четверичных разрядов слагаемых в коде “1 из 4” и условия возникновения переноса П.

Очевидно, возникновение переноса из предыдущего разряда не приводит к необходимости формирования дополнительного сигнала переноса, т.к. максимальное значение кода суммы при активном сигнале переноса из текущего разряда 0100 и, следовательно, перенос из предыдущего разряда даст результат 1000 без переноса.

Устройство для умножения чисел в коде “1 из 4” работает следующим образом. Вначале на вход устройства подается импульс Запись (фиг.4), по заднему фронту которого обеспечивается запись операнда сомножителя Y в регистр 1 тетрадного сдвига и установка в ноль в коде “1 из 4” регистра 4 результата. Каждый из четверичных разрядов уi представлен кодом “1 из 4” y0iy1iy2iy3i и занимает i-ю тетраду регистра 1 тетрадного сдвига. Выход младшей тетрады регистра 1 соединен со входами всех узлов 2i частичных произведений в коде “1 из 4” блока 2 частичных произведений. На другие входы узлов 2i подаются четверичные разряды второго сомножителя в коде “1 из 4” x01X11Х21Х31 - X0nX1nX2nX3n, которые удерживаются в течение всего процесса вычислений. Для этой цели может быть использован внешний регистр (на фиг.1 не показан), запись в который может производиться тем же импульсом, что и в регистр 1 тетрадного сдвига. Узлы частичных произведений 2i блока 2 комбинационные, поэтому через время переходного процесса на выходе узлов частичных произведений 2i в соответствии с алгоритмом установится значение y1 ×40(x1 ×40 + x2 × 41 + ... + xn ×4n-1). Количество узлов частичных произведений 2i блока 2 на единицу больше, чем количество разрядов сомножителей n, т.к. возможна ситуация возникновения одного или двух переносов в (n+1)-й разряд. Аналогичная ситуация возникает с сумматорами 3i блока 3 сумматоров, которых также n+1.

Сумматоры 3i в коде “1 из 4” блока 3 сумматоров также комбинационные, на входы которых подаются соответствующие весам четверичных разрядов коды частичных произведений с соответствующих узлов 2i и значения нулей с установленного в ноль регистра 4 результата. На выходах сумматоров блока 3 через время переходного процесса будет установлено значение частичной суммы произведений y1 ×40(x1 ×40 + x2 ×41 + ... + xn ×4n-1), которое по переднему фронту синхроимпульса СИ (фиг.4) будет занесено в соответствующие разряды регистра результата 4. По заднему фронту этого же импульса осуществляется сдвиг на один четверичный разряд в регистре тетрадного сдвига. Таким образом, на входах первой группы блока 2 частичных произведений появится значение у2, на выходе блока 2 образуется код частичного произведения у2 ×41(x1 ×40 + x2 ×41 + ... + xn ×4n-1), который поразрядно складывается на сумматорах 3i со сдвинутым на один четверичный разряд в сторону младших разрядов кодом накопленной частичной суммы в регистре результата 4. Таким образом, на выходе блока сумматоров 3 образуется код очередной частичной суммы у2 ×41(x1 ×40 + x2 ×41 + ... + xn ×4n-1) + y1 ×40(x1 ×40 + x2 ×41 + ... + xn ×4n-1), который заносится в регистр 4 результата вторым импульсом СИ. При этом младший разряд частичной суммы у1 ×40 ×x1 ×40 без суммирования переписывается с выхода n-го четверичного разряда регистра 4 результата в (n-1)-й разряд. По заднему фронту второго импульса СИ осуществляется сдвиг на один четверичный разряд сомножителя Y в регистре 1 тетрадного сдвига.

В дальнейшем процесс вычисления циклически повторяется и после подачи n-го импульса СИ в регистре 4 результата образуется полная сумма частичных произведений Х × Y = yn ×4n-1(x1 ×40 + x2 ×41 + ... + xn ×4n-1) + yn-1 ×4n-2(x1 ×40 + x2 ×41 + ... + xn ×4n-1) + ... + y2 ×41(x1 ×40 + x2 ×41 + ... + xn ×4n-1) + y1 ×40(xl ×40 + x2 ×41 + ... + xn ×4n-1), которая находится в 2n четверичных разрядах z1-z2n в коде “1 из 4”. Выходы четверичных разрядов z1-z2n поступают на входы соответствующих узлов контроля кода “1 из 4” блока 5 контроля, и в случае появления несоответствия этому коду хотя бы в одном разряде zi на выход устройства будет выдан сигнал признака ошибки Ошi. Конструкция узлов контроля кода “1 из 4” известна (см. “Устройство для контроля кода “1 из n” патенты SU 1195451, МКИ 6 Н 03 М 7/22; SU 1683178, МКИ 6 Н 03 М 7/22).

Комбинационные узлы частичных произведений в коде “1 из 4” 3i (фиг.2) блока частичных произведений работают следующим образом. Каждая группа элементов И 6-9 содержит 4 элемента И, образуя матрицу 4× 4. На первые входы элементов И с первой по четвертую групп подаются бинарные составляющие четверичного разряда сомножителя у0iу1iу2iу3i, на вторые входы элементов И с первого по четвертый каждой группы подаются бинарные составляющие четверичного разряда сомножителя x0ix1ix2ix3i. На 16 выходах матрицы элементов И может, очевидно, возникнуть только одна “1”, остальные нули (любая другая комбинация, пройдя через логические элементы узла 2i и комбинационный сумматор 3i приведет к возникновению сигнала признака ошибки на одном из выходов блока контроля 5). Выходы элементов И групп 6-9 подключены ко входам четырех элементов ИЛИ первой группы 10 таким образом, что на их выходах реализуется необходимый результат частичного произведения в соответствии с табл.2. При этом на выходе элемента ИЛИ 16 и элемента ИЛИ 18 формируется сигнал признака первого переноса Р

Пятая группа элементов И 11 состоит из двенадцати элементов И и образует коммутатор, который управляется элементами НЕ 13 и 14, входы которых подключены ко входам первого и второго переносов из предыдущего четверичного разряда  и

и  . С помощью четырех элементов ИЛИ 12 второй группы формируется сдвиг кода с выходов элементов ИЛИ первой группы 10 в соответствии с уровнями сигналов

. С помощью четырех элементов ИЛИ 12 второй группы формируется сдвиг кода с выходов элементов ИЛИ первой группы 10 в соответствии с уровнями сигналов  и

и  . При этом, если оба сигнала переноса

. При этом, если оба сигнала переноса  и

и  пассивны, то код с выходов элементов ИЛИ первой группы 10 поступит на входы элементов ИЛИ второй группы 12 без сдвига и будет выдан на выход узла частичного произведения. Если активен сигнал

пассивны, то код с выходов элементов ИЛИ первой группы 10 поступит на входы элементов ИЛИ второй группы 12 без сдвига и будет выдан на выход узла частичного произведения. Если активен сигнал  , то будет произведен один сдвиг, если активны оба сигнала

, то будет произведен один сдвиг, если активны оба сигнала  и

и  (комбинация, когда активен только сигнал второго переноса не формируется), то осуществляется сдвиг на два разряда. Сдвиги осуществляются в кольцевом режиме и, при необходимости, на элементе ИЛИ 17 формируется сигнал переноса. При пассивном сигнале первого переноса на выходе элемента ИЛИ 16 открывается элемент И 20, а элемент И 21 закрыт. В этом случае при возникновении активного сигнала переноса на выходе элемента ИЛИ 17, на выходе элемента И 20 и выходе элемента ИЛИ 18 появится активный сигнал первого переноса в следующий разряд

(комбинация, когда активен только сигнал второго переноса не формируется), то осуществляется сдвиг на два разряда. Сдвиги осуществляются в кольцевом режиме и, при необходимости, на элементе ИЛИ 17 формируется сигнал переноса. При пассивном сигнале первого переноса на выходе элемента ИЛИ 16 открывается элемент И 20, а элемент И 21 закрыт. В этом случае при возникновении активного сигнала переноса на выходе элемента ИЛИ 17, на выходе элемента И 20 и выходе элемента ИЛИ 18 появится активный сигнал первого переноса в следующий разряд  . При активном сигнале первого переноса на выходе элемента ИЛИ 16 открывается элемент И 21, а элемент И 20 закрыт. Сигнал с выхода элемента ИЛИ 16, пройдя через элемент ИЛИ 18 сформирует сигнал первого переноса в следующий разряд

. При активном сигнале первого переноса на выходе элемента ИЛИ 16 открывается элемент И 21, а элемент И 20 закрыт. Сигнал с выхода элемента ИЛИ 16, пройдя через элемент ИЛИ 18 сформирует сигнал первого переноса в следующий разряд  . При возникновении активного сигнала переноса на выходе элемента ИЛИ 17, на выходе элемента И 21 и выходе элемента ИЛИ 19 появится активный сигнал второго переноса в следующий разряд

. При возникновении активного сигнала переноса на выходе элемента ИЛИ 17, на выходе элемента И 21 и выходе элемента ИЛИ 19 появится активный сигнал второго переноса в следующий разряд  . Наконец,, если в результате частичного произведения сформирован сигнал двух переносов, то активные сигналы поступают на входы элементов ИЛИ 18 и 19, формируя на выходе сигналы первого и второго переносов

. Наконец,, если в результате частичного произведения сформирован сигнал двух переносов, то активные сигналы поступают на входы элементов ИЛИ 18 и 19, формируя на выходе сигналы первого и второго переносов  и

и  , причем, как показано выше, на выходе элемента ИЛИ 17 не может возникнуть активного сигнала переноса при любых комбинациях сигналов переносов из предыдущего разряда

, причем, как показано выше, на выходе элемента ИЛИ 17 не может возникнуть активного сигнала переноса при любых комбинациях сигналов переносов из предыдущего разряда  и

и  .

.

Комбинационные сумматоры в коде “1 из 4” 3i блока сумматоров 3 работают аналогичным образом, но реализуют преобразование по табл.3. Каждая группа элементов И 22-25 содержит 4 элемента И, образуя матрицу 4× 4. На первые входы элементов И с первой по четвертую групп подаются бинарные составляющие четверичного разряда слагаемого а0i,а1iа2iа3i, на вторые входы элементов И с первого по четвертый каждой группы подаются бинарные составляющие четверичного разряда сомножителя b0ib1ib2ib3i. На 16 выходах матрицы элементов И может, очевидно, возникнуть только одна “1”, остальные нули (любая другая комбинация, пройдя через логические элементы сумматора 3i приведет к возникновению сигнала признака ошибки на одном из выходов блока контроля 5). Выходы элементов И групп 22-25 подключены ко входам четырех элементов ИЛИ первой группы 26 таким образом, что на их выходах реализуется необходимый результат частичного произведения в соответствии с табл.3. При этом на выходе элемента ИЛИ 30 формируется сигнал признака переноса Рi в следующий четверичный разряд.

Пятая группа элементов И 27 состоит из восьми элементов И и образует коммутатор, который управляется элементом НЕ 29, вход которого подключен ко входу переноса из предыдущего четверичного разряда Pi-1. С помощью четырех элементов ИЛИ 28 второй группы формируется сдвиг кода с выходов элементов ИЛИ первой группы 10 в соответствии с уровнем сигнала Pi-1. При этом, если сигнал переноса Pi-1 пассивен, то код с выходов элементов ИЛИ первой группы 26 поступит на входы элементов ИЛИ второй группы 28 без сдвига и будет выдан на выход сумматора. Если сигнал Pi-1 активен, то будет произведен один сдвиг. Сдвиг осуществляется в кольцевом режиме и, при необходимости, на элементе ИЛИ 30 формируется сигнал переноса.

Таким образом, предложенное устройство обеспечивает повышение достоверности результата умножения чисел за счет поразрядного контроля выполнения операции. При этом обеспечивается обнаружение 80% ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2467377C1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

Устройство для умножения чисел в коде “1 из 4” относится к вычислительной технике и может быть использовано для построения вычислительных систем с повышенной достоверностью получения результатов. Технический результат, достигаемый при осуществлении изобретения, заключается в повышении достоверности выдаваемого результата при обеспечении поразрядного контроля результата операции умножения чисел и равномерного распределения энергии по разрядам в процессе работы, что особенно важно при реализации аппаратуры системы в виде СБИС. Технический результат достигается за счет того, что в устройство, содержащее блок частичных произведений, блок сумматоров и блок контроля, введены регистр тетрадного сдвига и регистр результата в коде “1 из 4”, при этом блок частичных произведений содержит n+1 узел частичных произведений в коде “1 из 4”, где n - количество четверичных разрядов сомножителей, блок сумматоров содержит n+1 сумматор в коде “1 из 4”, регистр результата в коде “1 из 4” содержит 2n тетрад четверичных разрядов, блок контроля содержит 2n узлов контроля кода “1 из 4”. 4 ил.

Устройство для умножения чисел в коде “1 из 4”, содержащее блок частичных произведений, блок сумматоров и блок контроля, причем выходы блока контроля соединены с выходами признака ошибки устройства, отличающееся тем, что в него введены регистр тетрадного сдвига и регистр результата в коде “1 из 4”, причем входы четверичных разрядов в коде “1 из 4” первого сомножителя устройства соединены с информационными входами соответствующих тетрад регистра тетрадного сдвига, выходы младшей тетрады которого соединены со входами первой группы блока частичных произведений, входы второй группы которого соединены со входами четверичных разрядов в коде “1 из 4” второго сомножителя устройства, выходы блока частичных произведений соединены со входами первой группы блока сумматоров, входы второй группы которого соединены с выходами группы старших четверичных разрядов регистра результата в коде “1 из 4”, выходы групп младших и старших четверичных разрядов которого соединены со входами блока контроля, выходы блока сумматоров соединены с информационными входами четверичных разрядов регистра результата в коде “1 из 4”, вход установки которого соединен со входом записи устройства и входом записи регистра тетрадного сдвига, вход тетрадного сдвига которого соединен со входом записи регистра результата в коде “1 из 4” и входом синхроимпульсов сдвига устройства, вход константы 0 в коде “1 из 4” которого соединен со входами константы 0 блока частичных произведений и блока сумматоров, при этом блок частичных произведений содержит n+1 узел частичных произведений в коде “1 из 4”, где n - количество четверичных разрядов сомножителей, входы четверичных разрядов в коде “1 из 4” первого и второго сомножителей с первого по n-й узлов частичных произведений в коде “1 из 4” соединены со входами соответствующих разрядов соответственно первой и второй групп блока частичных произведений, выходы которого соединены с выходами с первого по (n+1)-й узлов частичных произведений в коде “1 из 4”, входы четверичных разрядов в коде “1 из 4” первого и второго сомножителей (n+1)-го узла частичных произведений в коде “1 из 4” соединены со входом константы 0 блока частичных произведений, выходы первого и второго переносов i-гo узла частичных произведений в коде “1 из 4”, где i=1,2,...,n, соединены со входами соответственно первого и второго переносов (i+1)-гo узла частичных произведений в коде “1 из 4” блока частичных произведений, причем блок сумматоров содержит n+1 сумматор в коде “1 из 4”, входы четверичных разрядов в коде “1 из 4” первого слагаемого с первого по (n+1)-й сумматоров в коде “1 из 4” соединены со входами соответствующих разрядов первой группы блока сумматоров, выходы которого соединены с выходами с первого по (n+1)-й сумматоров в коде “1 из 4”, вход четверичного разряда второго слагаемого (n+1)-го сумматора в коде “1 из 4” соединен со входом константы 0 блока сумматоров, выход переноса i-гo сумматора в коде “1 из 4”, где i=1,2,...,n, соединен со входом переноса (i+1)-гo сумматора в коде “1 из 4”, входы четверичных разрядов второго слагаемого с первого по n-й сумматоров в коде “1 из 4” соединены со входами соответствующих разрядов второй группы блока сумматоров, при этом регистр результата в коде “1 из 4” содержит 2n тетрад четверичных разрядов, выходы и информационные входы с n-й по 2n-ю тетрад четверичных разрядов регистра результата в коде “1 из 4” соединены соответственно с выходами старшей группы четверичных разрядов и соответственно с первого по (n+1)-й информационными входами четверичных разрядов регистра результата в коде “1 из 4”, информационные входы с первой по n-1)-ю тетрад четверичных разрядов регистра результата в коде “1 из 4” соединены с выходами четверичных разрядов соответственно со второй по n-ю тетрад четверичных разрядов регистра результата в коде “1 из 4”, при этом блок контроля содержит 2n узлов контроля кода “1 из 4”, входы и выходы которых подключены соответственно к соответствующим четверичным разрядам входов и выходов блока контроля.

| Устройство для сложения | 1981 |

|

SU1015372A2 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2143723C1 |

| Устройство контроля кода "1 из @ | 1984 |

|

SU1195451A1 |

| Шифратор позиционного кода | 1988 |

|

SU1683178A1 |

| JP 5257649 A, 10.08.1993. | |||

Авторы

Даты

2005-04-27—Публикация

2003-10-28—Подача