Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих вычислительных средств в системах с повышенной достоверностью обрабатываемых и выдаваемых данных.

Известно устройство умножения (патент RU на изобретение №2148270, заявлено 27.05.1998, опубликовано 27.04.2000, МПК G06F 7/49), содержащее регистр первого множимого, регистр второго множимого, два умножителя, регистр частных произведений, сумматор комбинационный, блок результата, распределитель тактовых импульсов (устройство управления).

Недостатками данного устройства умножения являются:

- в процессе получения произведения последовательно выполняются операции получения частичных произведений, суммирования и фиксации результата умножения, что влечет за собой большие временные затраты, соответствующие объемы аппаратуры и энергопотребление;

- отсутствие контроля в режиме функционирования, что снижает достоверность получаемой информации.

Известно устройство для умножения чисел (патент RU на изобретение №2021633, заявлено 10.07.1991, опубликовано 15.10.1994, МПК G06F 7/52), содержащее n одноразрядных узлов умножения (n - разрядность множимого), две группы по n буферных регистров, n комбинационных сумматоров первой группы, (n+1) комбинационных сумматоров второй группы, (n+1) регистров промежуточного результата, n триггеров переноса.

Данному устройству присущи все недостатки предыдущего.

Наиболее близким техническим решением (прототипом) по отношению к заявляемому является устройство для умножения чисел в коде «1 из 4» (патент RU на изобретение №2251144, заявлено 28.10.2003, опубликовано 27.04.2005, МПК G06F 7/52), содержащее регистр множимого, регистр тетрадного сдвига (регистр множителя), блок частичных произведений, блок сумматоров (сумматор), регистр результата и блок контроля (схему контроля «1-4»).

К недостатку данного устройства умножения, работающего с числами в коде «1 из 4», можно отнести необходимость выполнения операции формирования частичных произведений при получении конечного результата - произведения двух чисел, что приводит к определенным временным затратам, ограничивая тем самым быстродействие работы устройства умножения, увеличивает его объем и энергопотребление.

Задачей, на решение которой направлено предлагаемое техническое решение, является создание устройства умножения чисел в коде «1 из 4», в котором в процессе получения произведения двух чисел исключаются недостатки прототипа.

Целесообразность создания устройств, систем, работающих с числами, представленными в коде «1 из 4», достаточно обоснована, показана в материалах изобретений, на которые выданы патенты RU №2251143 МПК G06F 7/49, №2251144 МПК G06F 7/52 и др.

При представлении числа в коде «1 из 4» каждый из n четверичных разрядов числа имеет в своем составе только одну единицу, т.е. все возможные комбинации этого кода имеют вид: 0=0001, 1=0010, 2=0100, 3=1000.

Поэтому процедура получения частичного произведения сводится к умножению множимого на одно из этих значений.

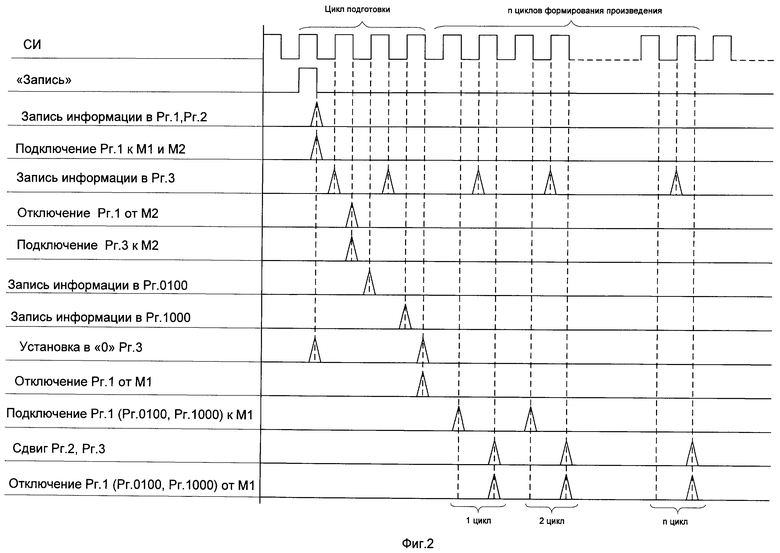

Указанный результат достигается тем, что в устройство умножения, содержащее регистр множимого, регистр множителя, сумматор, регистр результата и схему контроля «1-4», дополнительно введены устройство управления, регистр хранения результата умножения множимого на два, регистр хранения результата умножения множимого на три, и первая M1 и вторая М2 магистрали передачи данных, при этом

множимое по шинам X1÷Xn поступает на вход регистра множимого (Рг.1), множитель по шинам У1÷Уn поступает на вход регистра множителя (Рг.2), выход сигнала «Запись» поступает на первые входы регистра множимого, регистра множителя, регистра результата (Рг.3) и устройства управления, синхронизирующие импульсы поступают на второй вход устройства управления, в устройстве управления первый выход сигналов управления сопрягается со вторым входом регистра результата, второй выход - со вторым входом регистра множимого, третий выход - со вторым входом регистра множителя, четвертый выход - с первым входом регистра хранения результата умножения множимого на два (Рг.0100), пятый выход - с первым входом регистра хранения результата умножения множимого на три (Рг.1000), четыре выхода младшего четверичного разряда регистра множителя сопрягаются с четырьмя входами устройства управления, передача информации с регистров Рг.1, Рг.0100 и Рг.1000 на первую группу входов сумматора (См.) осуществляется по магистрали M1, передача информации с выхода регистра Рг.3 на вход регистров Рг.0100, Рг.1000, на внешнее устройство (ВУ) и на вторую группу входов сумматора осуществляется по магистрали М2, по этой же магистрали на вторую группу входов сумматора передается информация со второго выхода Рг.1, поразрядно с 1-го по n+1 выходы сумматора поступают на соответствующие входы Рг.3, с выходов которого (1÷n) информация поступает на соответствующие входы схемы контроля «1-4» (Сх.к «1-4»), Сх.к. «1-4» поразрядно (Ош.1÷Ош.n) выдает признаки ошибки во внешнее устройство.

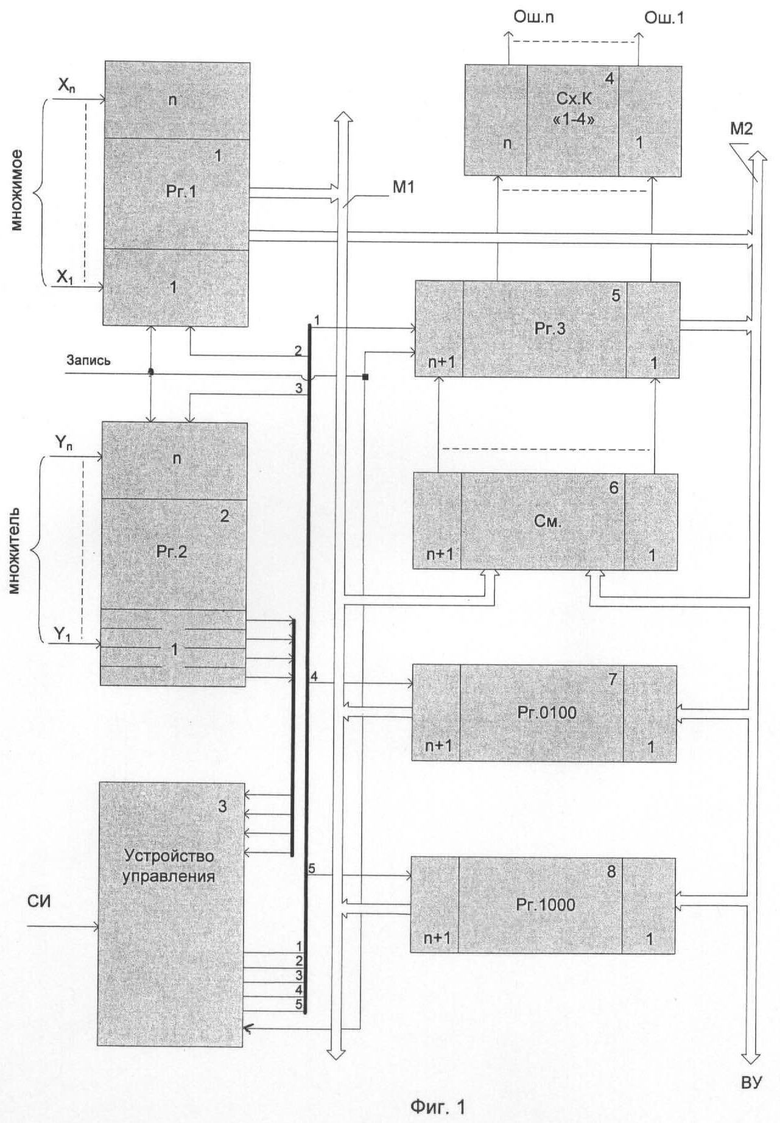

Сущность изобретения поясняется чертежом (Фиг.1), на котором изображена структурная схема устройства умножения и временной диаграммой (Фиг.2) его работы.

На Фиг.1 обозначены:

1 - регистр множимого (Рг.1);

2 - регистр множителя (Рг.2);

3 - устройство управления;

4 - схема контроля в коде «1 из 4» (сх.к. «1-4»);

5 - регистр результата (Рг.3);

6 - сумматор (См.);

7 - регистр хранения результата умножения множимого на два (Рг.0100);

8 - регистр хранения результата умножения множимого на три (Рг.1000);

M1 - магистраль передачи данных из Рг.1, Рг.0100, Рг.1000 в См.;

М2 - магистраль передачи данных из Рг.3 в См., Рг.0100, Рг.1000 и ВУ.

Предлагаемое устройство умножения работает следующим образом. На входе Рг.1 1 и Рг.2 2 устанавливаются данные соответственно множимого (по шинам X1÷Xn) и множителя (по шинам У1÷Уn).

По заднему фронту сигнала «Запись» осуществляется запись данных в Рг1 1, Рг2.2, устанавливается в «0» Рг3 5 и запускается работа устройства управления 3, которое подключает к магистрали M1 первый, а к магистрали М2 второй выходы Рг.1 1, т.е. подает на первый и второй входы сумматора 6 данные с указанного регистра. Сумматор 6 комбинационный, поэтому через время переходного процесса на его выходе установится код аналогичный удвоенному коду в регистре Рг.1 1. Передним фронтом синхроимпульса, следующего за импульсом «Запись», данные из сумматора 6 переписываются в Рг.3 5. Задним фронтом этого импульса Рг1 1 отключается от магистрали М2, а регистр Рг.3 5 к данной магистрали подключается. Передним фронтом второго (после импульса «Запись») синхроимпульса содержимое Рг 3 5 переписывается в Рг.0100 7, а задним фронтом этого синхроимпульса новое содержимое сумматора 6 (утроенное содержание Рг.1 1) переписывается в Рг.3 5.

Передним фронтом третьего (после импульса «Запись») синхроимпульса содержимое Рг.3 5 переписывается в Рг.1000 8. Задним фронтом этого импульса устанавливается в «0» Рг.3 5, а выход Рг.1 1 отключается от магистрали M1. Подготовительный цикл для получения произведения двух чисел завершен. Следует отметить, что Рг.3 5, сумматор 6, Рг.0100 7 и Рг.1000 8 имеют разрядность n+1, поскольку при выполнении операций сложения может возникнуть перенос.

Процесс получения произведения двух чисел состоит из n циклов, где n - количество разрядов множителя. Каждый из циклов начинается с анализа устройством управления 3 состояния младшего четверичного разряда регистра множителя Рг.2 2. Как было сказано выше, каждый из разрядов числа, представленного в коде «1 из 4», содержат только одну из комбинаций - 0001, 0010,0100 и 1000.

Максимально каждый из циклов получения произведения содержит следующие операции:

- анализ младшего разряда Рг.2 2;

- передача информации из Рг.1 1 (Рг.0100 7, Рг.1000 8) в См. 6;

- суммирование значений Рг.1 1 (Рг.0100 7, Рг.1000 8) и Рг.3 5;

- передача См. 6→Рг.3 5;

- сдвиг на один разряд в сторону младших разрядов Рг.2 2 и Рг.3 5.

Данный объем операций выполняется, когда в младшем разряде Рг.2 2 записано одно из значений 0010, 0100 и 1000, при этом: значение 0010 соответствует передаче информации из Рг.1 1;

- значение 0100 - из Рг.0100 7;

- значение 1000 - из Рг.1000 8.

В случае когда в младшем разряде Рг.2 2 записано значение 0001, цикл получения произведения сводится к выполнению двух операций: анализ состояния младшего разряда Рг.2 2;

- сдвиг в сторону младших разрядов Рг.2 2 и Рг.3 5.

Таким образом, предлагаемый способ и устройство умножения чисел в коде «1 из 4» позволяют создать устройство, в котором время цикла умножения не зависит от величины кода числа, а определяется только количеством операций суммирования, с достаточно высокой степенью достоверности функционирования, сравнительно низким объемом используемой элементной базы и энергопотреблением.

Представленные чертеж и описание устройства умножения, а также существующая элементная база дают возможность изготавливать его промышленным способом и, что особенно важно, в виде БИС.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| Устройство для умножения комплексных чисел | 1985 |

|

SU1283751A1 |

| Устройство для умножения | 1984 |

|

SU1254469A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| Устройство для умножения в избыточной системе счисления с запоминанием переноса | 1985 |

|

SU1252773A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

Изобретения относятся к вычислительной технике и могут быть использованы для построения вычислительных средств в системах обработки данных и управления. Техническим результатом является повышение быстродействия и достоверности обрабатываемой информации, снижение объемов используемой элементной базы и энергопотребления. Устройство содержит регистр множимого, регистр множителя, сумматор, регистр результата и схему контроля «1-4», устройство управления, регистр хранения результата умножения множимого на два, регистр хранения результата умножения множимого на три, две магистрали передачи даны. 2 н.п. ф-лы, 2 ил.

1. Способ умножения чисел в коде «1 из 4», заключающийся в приеме данных множимого и множителя, их хранении, получении результата умножения множимого на множитель, контроля и выдачи результатов умножения во внешние устройства, отличающийся тем, что, с целью сокращения времени выполнения процедуры умножения двух чисел в коде «1 из 4», из данной процедуры исключается операция получения частичных произведений, в подготовительном режиме, предшествующем процедуре получения произведения, формируется и запоминается удвоенное и утроенное значение множимого и по результату анализа содержания каждого четверичного разряда (0001, 0010, 0100, 1000) множителя осуществляется суммирование промежуточного значения произведения с одним из значений второго слагаемого - нулевым, равным значению множимого, удвоенному или утроенному значению множимого.

2. Устройство умножения чисел в коде «1 из 4», содержащее регистр множимого, регистр множителя, сумматор, регистр результата и схему контроля, отличающееся тем, что в него дополнительно введены устройство управления, регистр хранения результата умножения множимого на два, регистр хранения результата умножения множимого на три и первая и вторая магистрали передачи данных, при этом множимое по шинам X1÷Xn поступает на вход регистра множимого, множитель по шинам У1÷Уn поступает на вход регистра множителя, выход сигнала «Запись» поступает на первые входы регистра множимого регистра множителя, регистра результата и устройства управления, синхронизирующие импульсы поступают на второй вход устройства управления, в устройстве управления первый выход сигналов управления сопрягается со вторым входом регистра результата, второй выход - со вторым входом регистра множимого, третий выход - со вторым входом регистра множителя, четвертый выход - с первым входом регистра хранения результата умножения множимого на два, пятый выход - с первым входом регистра хранения результата умножения множимого на три, четыре выхода младшего четверичного разряда регистра множителя сопрягаются с четырьмя входами устройства управления, передача информации с регистра множимого, регистра хранения результата умножения множимого на два, регистра хранения результата умножения множимого на три на первую группу входов сумматора осуществляется по первой магистрали передачи данных, передача информации с выхода регистра результата на вход регистра хранения результата умножения множимого на два, регистра хранения результата умножения множимого на три, внешнего устройства и второй группы входов сумматора осуществляется по второй магистрали передачи данных, по этой же магистрали на вторую группу входов сумматора передается информация со второго выхода регистра множимого, поразрядные с 1-го по n+1 выходы сумматора поступают на соответствующие входы регистра результата, выходы с 1-го по n которого сопрягаются с соответствующими входами схемы контроля, схема контроля поразрядно (Ош.1÷Ош.n) выдает признаки ошибки во внешнее устройство.

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| US 2003105792 A1, 05.06.2003 | |||

| СРЕДСТВО ДЛЯ СНИЖЕНИЯ ТОКСИЧЕСКОГО ДЕЙСТВИЯ ГЕРБИЦИДА 2,4-ДИХЛОРФЕНОКСИУКСУСНОЙ КИСЛОТЫ НА ПОДСОЛНЕЧНИК | 2005 |

|

RU2284694C1 |

| US 5957999 A, 28.09.1999. | |||

Авторы

Даты

2012-11-20—Публикация

2011-04-19—Подача