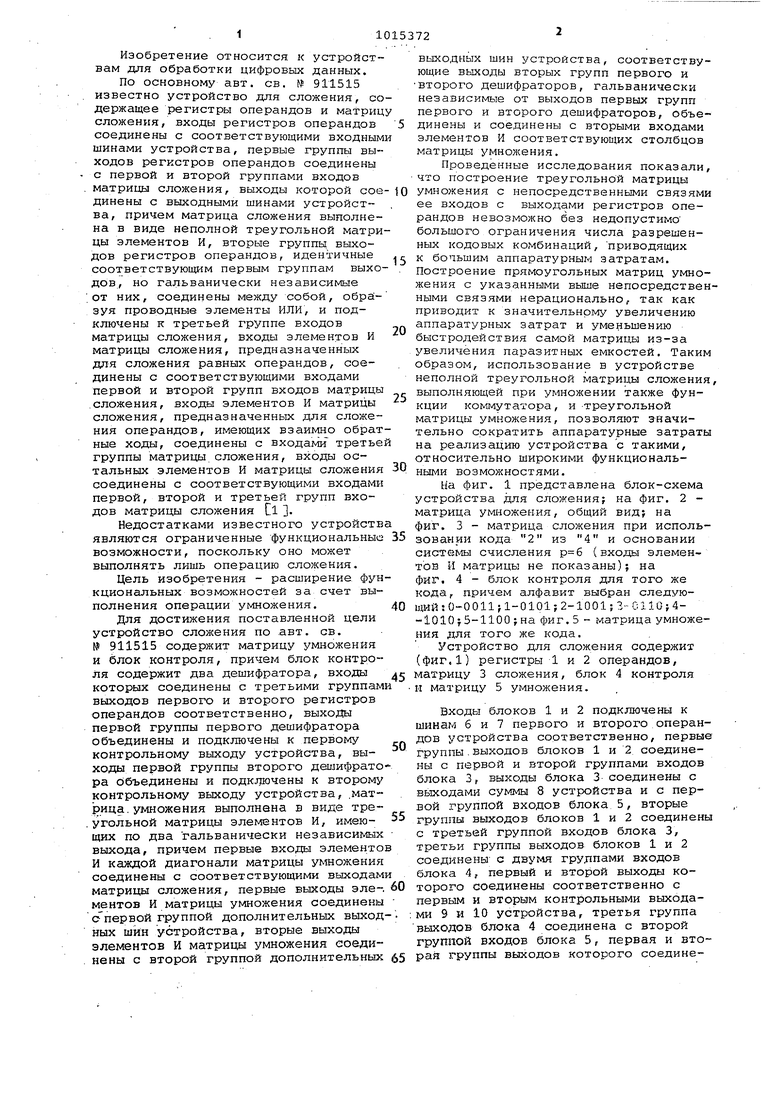

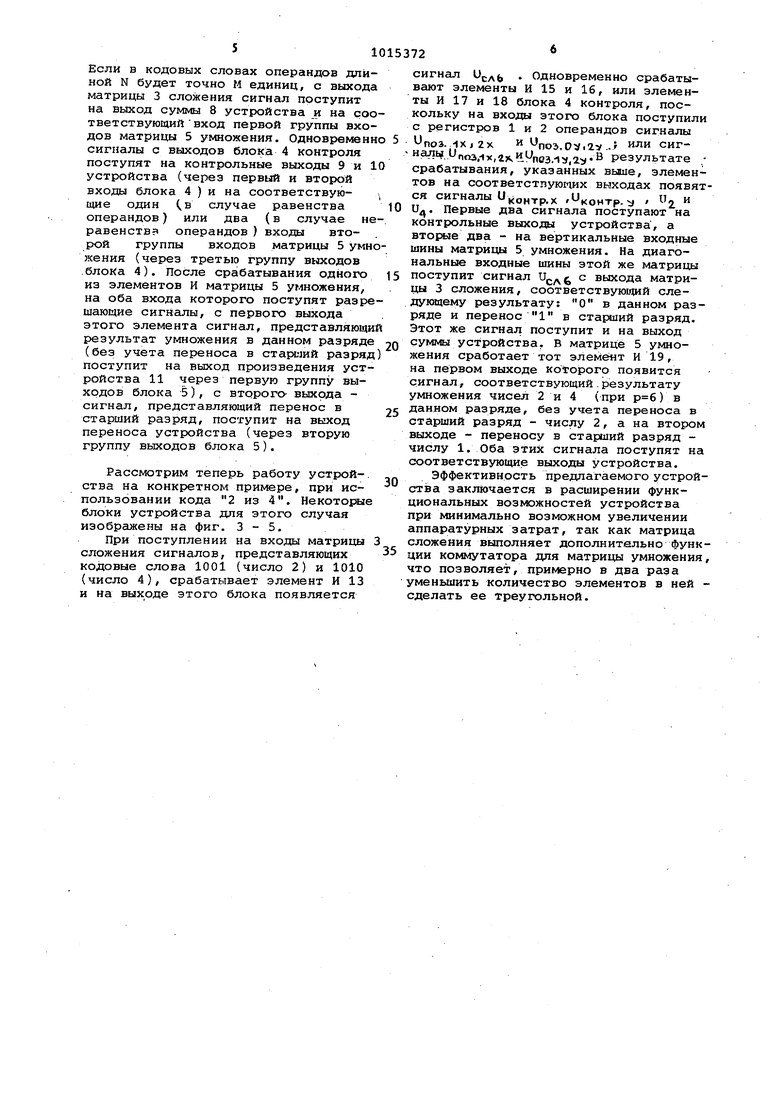

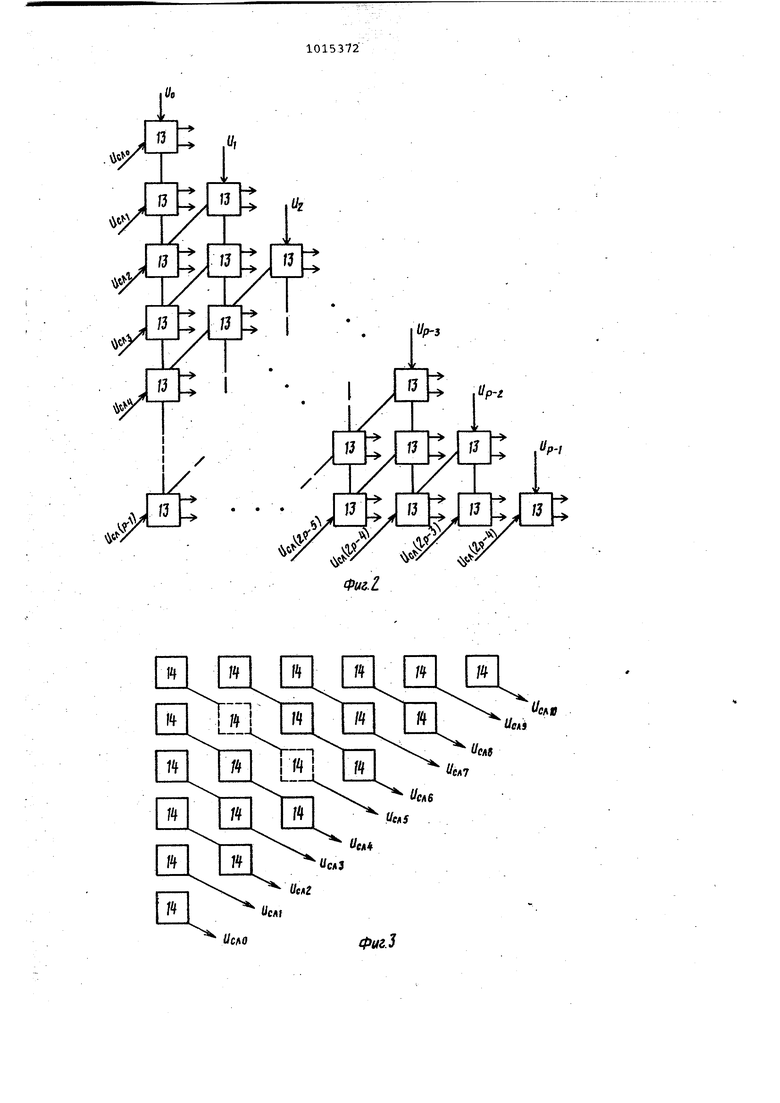

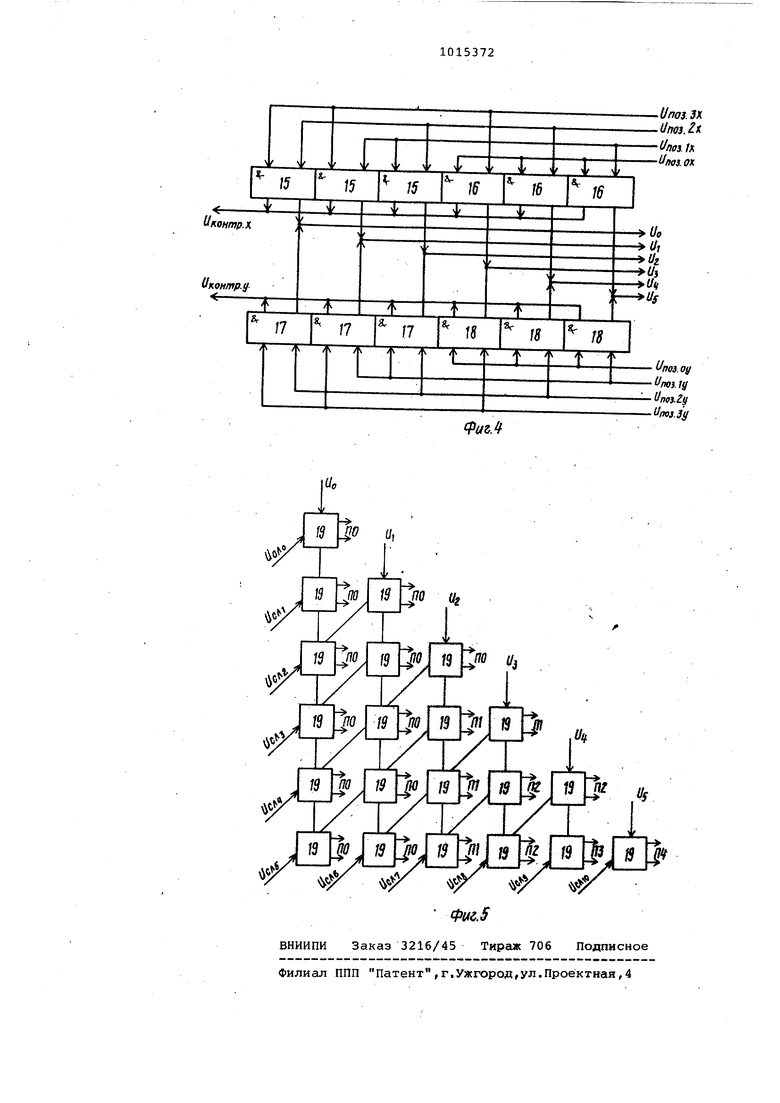

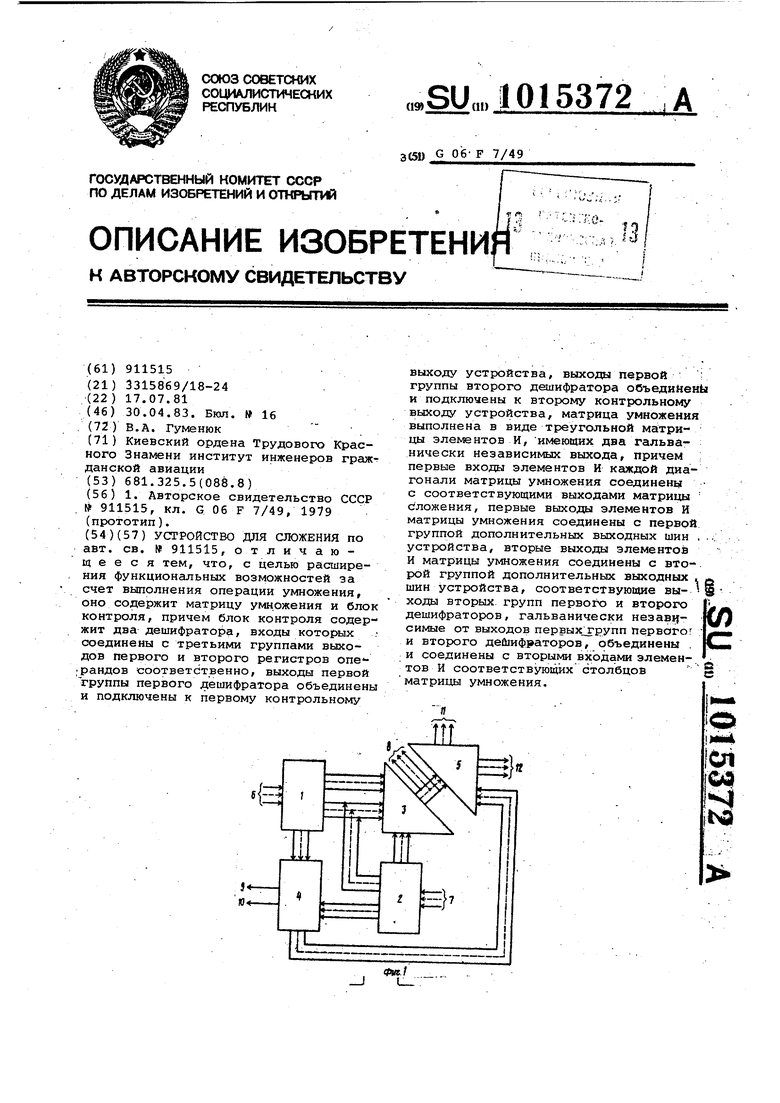

Изобретение относится к устройствам для обработки цифровых данных. По основному авт. св. № 911515 известно устройство для сложения, со держащее регистры операндов и матриц сложения, входы регистров операндов соединены с соответствующими входным шинами устройства, первые группы выходов регистров операндов соединены с первой и второй группами входов матрицы сложения, выходы которой сое динены с выходными шинами устройства, причем матрица сложения выполнена в виде неполной треугольной матри цы элементов И, вторые группы выходов регистров операндов, идентичные соответствующим первым группам выходов, но гальванически независимые от них, соединены между собой, обра;зуя проводные элементы ИЛИ, и подключены к третьей группе входов матрицы сложения, входы элементов И матрицы сложения, предназначенных для сложения равных операндов, соединены с соответствующими входами первой и второй групп входов матрицы .сложения, входы элементов И матрицы сложения, предназначенных для сложения операндов, имеющих взаимно обрат ные ходы, соединены с входами третье группы матрицы сложения, входы остальных элементов И матрицы сложения соединены с соответствующими входами первой, второй и третьей групп входов матрицы сложения Cl . Недостатками известного устройств являются ограниченные функциональные возможности, поскольку оно может выполнять лишь операцию сложения. Цель изобретения - расширение фун кциональных возможностей за счет выполнения операции умножения. Для достижения поставленной цели устройство сложения по авт. св. № 911515 содержит матрицу умножения и блок контроля, причем блок контроля содержит два дешифратора, входы которых соединены с третьими группам выходов первого и второго регистров операндов соответственно, выходы первой группы первого дешифратора объединены и подключены к первому контрольному выходу устройства, выходы первой группы второго деилифрато ра объединены и подк дачены к второму контрольному выходу устройства,.матрица, умножения выполнена в виде тре.угольной матрицы элементов И, имею вдих по два гальванически независимых выхода, причем первые входы элементо И каждой диагонали матрицы умножения соединены с соответствующими выходам матрицы сложения, первые выходы эле-. ментов И матрицы умножения соединены спер вой группой дополнительных выход ных шин устройства, вторые выходы элементов И матрицы умножения соединены с второй группой дополнительных выходных шин устройства, соответствующие выходы вторых групп первого и второго дешифраторов, гальванически независимые от выходов первых групп первого и второго дешифраторов, объединены и соединены с вторыми входами элементов И соответствующих столбцов матрицы умножения. Проведенные исследования показали, что построение треугольной матрицы умножения с непосредственными связями ее входов с выходами регистров операндов невозможно без недопустимо большого ограничения числа разрешенных кодовых комбинаций, приводящих к бопьшим аппаратурным затратам. Построение прямоугольных матриц умножения с указанными выше непосредственными связями нерационально, так как приводит к значительному увеличению аппаратурных затрат и уменьшению быстродействия самой матрицы из-за увеличения паразитных емкостей. Таким образом, использование в устройстве неполной треугольной матрицы сложения, выполняющей при умножении также функции коммутатора, и -треугольной матрицы умножения, позволяют значительно сократить аппаратурные затраты на реализацию устройства с такими, относительно широкими функциональными возможностями. На фиг. 1 представлена блок-схема устройства для сложения; на фиг. 2 матрица умножения, общий вид; на фиг. 3 - матрица сложения при использовании кода 2 из 4 и основании системы счисления (входы элементов И матрицы не показаны); на фйг. 4 - блок контроля для того же кода, причем алфавит выбран следующий 0-0011;1-0101;2-1001;3 0110;4 1010 ;5-1100 ; на фиг. 5 - матрица умножения для того же кода. Устройство для сложения содержит (фигЛ) регистры 1 и 2 операндов, матрицу 3 сложения, блок 4 контроля и матрицу 5 умножения. Входы блоков 1 и 2 подключены к шинам б и 7 первого и второго.операндов устройства со.ответственно, первые группы,выходов блоков 1 и 2. соединены с первой и второй группами входов блока 3, выходы блока 3- соединены с выходами суммы 8 устройства и с первой группой входов блока 5, вторые группы выходов блоков 1 и 2 соединены с третьей группой входов блока 3, третьи группы выходов блоков 1 и 2 соединены с двумя грудпами входов блока 4, первый и второй выходы которого соединены соответственно с первым и вторым контрольными выходами 9 и 10 устройства, третья группа выходов блока 4 соединена с второй группой входов блока 5, первая и вторая группы выходов которого соединены G выходами произведения и переноса 11 и 12 устройства соответственно. Блоки 1 и 2 устройства представляют собой группы из N триггеров каж дый. Триггер, входящий в состав этого блока, имеет два идентичных, но гапь ванически независимых единичных выхода и один нулевой выход. Первые единичные выходы триггеров образуют первую группу выходов блока,вторые единичные выходы - вторую группу выходов блокаИ ну;левые выходы - третью группу выходов блока. Блок 3 устройства представляет собой неполную треугольную матрицу элементов И, каждый из-которых имеет по 2м входов. Входы элементов И матрицы 3 сложения, пердназначенных для сложения равных операндов, соединены с. соответствующими входами первой и второй групп входов матрицы 3 сложения, входы элементов И матрицы 3 ело жения, предназначенных для сложения операндов, имеющих взаимно обратные коды соединены с входами третьей группы входов матрицы 3 сложения, входы остальных элементов И матрицы соединены с соответствующими входами первой, второй и третьей групп . входов этой матрицы. Выходы элементов И этой матриц, котфрые соответствуют одинаковым результатам сложения с учетом переноса в старший разряд, соединены с соответствующими выходами матрицы 3 сложения. Блок 4 устройства построен по ме контроля для кода М из N (полный дешифратор), на входы элементов И блока подаются обратные коды операндов. Блок 4 состоит из двух групп элементов И, по р элементов в Кс1ждой Такой элемент имеет N-M входов и два идентичных, но гальванически независимых выхода (реализован может быть, например, с помощью двух многоэмитте ных транзисторов). Первые выходы элементов И одной группы соединены с соответствующим вьаходом (первым или вторым) блока 4. Аналогичное соедине ние имеет другая группа элементов И блока 4. Вторые выходы элементов И обеих групп, соответствующих равным операндам соединены (попарно) с соответствующими выходами третьей групп выходов блока 4. На фиг. 4 представлена схема блока 4 для кода 2 из 4 основания системы счисления и (как указывалось вьлие) следу1рщего алфавита: 0-0011} 1-0101; 2-1001 3-0110f 4-1010; 5-1100, где 0-й разряд кодового слова - крайний справа. На фиг. 4 обозначены: и и сигналы на первом и второ КО HTP«j JillII выходах блока ,-j и «поз.та сигналы на входах первой и второй групп входов блока 4, где О i i- N-1 и- - сигналы на выходах третьей груп вькодов блока 4, где О ;С j р-1. Блок 5 устройства представляет собой (фиг. 2) треугольную матрицу элементов И. Каждый из этих элементов имеет по два входа и по два идентичных, но гальванически независимых выхода. Общее количество элементов И матрицы-умножения равно р(р+1)/2. Первые входы элементов И матрицы умножения соединены с соответствующими входами первой группы входов данного блока, вторые вхрды элементов И матрицы умножения соединены с соответствующими входами второй группы входов блока 5. Первые выходы элементов И матрицы умножения, представляющих одинаковые результаты умножения в данном разряде (без учета переноса), соединены с соответствующими выхода,ми первой группы выходов данного блока, вторые выходы элементов И матрицы умножения, идентичные соответствующим первым выходам, но гальванически независимые от них, представляющих одинаковые переносы в старщий разряд, соеди 9е ы соответствующими выходами вторфй группы выходов данного блока. На фиг. 2 обозначены: cA.i сигна)1ы с выходов матрицы 3 сложе 1ия, где О ii 2р-2; Ui - сигналы «: выходов блока 4 контроля , гд О . j р-1. На фиг 5 приеден пример построения матрицы 5 умн&ожения для кода 2 из 4 и основания системы счисления , отдельно вынесен элемент И матрицы умножения. На фиг. 5 используются следующие условные обозначения: ПХ-сигналы переноса в старший разряд, где 0$Х4р-2; в квадратных скобках приведены значения результатов умножения в данном разряде (без учета переноса в старший разряд). Устройство, работает следующим образом. Операнды коде М из N поступают на регистры 1 и 2 операндов. С первых двух групп выходов регистров 1 и 2 операндов прямые коды операндов поступают на входы, матрицы 3 сложения, а с третьей группы выходов регистров 1 и 2 операндов обратные коды операндов поступгиот на входы блока 4 контроля. Появление нескомпенсиро.ванной ошибки - приводит или к появлению сигналов на .выходах, сразу нескольких элементов И матрица 3 слохсения, или к отсутсткию сигналов на их выходах. В первом случае, отсутствуют сигнал контроля на выходе блока 4 контроля (на нервом выХояе, на втором выходе; или на обоих выходах одновременно) и разрецакадийоигнал на трет| ей груп- пе выходов этого блока. Такимобразом, неправил1ьный результат сложения в этом случае может быть затем/заблокигрован. Сигналы на выходах матрицы 5 умножения отсутствуют в обоих случаях. Если в кодовых словах операндов длиной N будет точно М единиц, с выхода матрицы 3 сложения сигнал поступит на выход суммы 8 устройства и на соо тветствующий вход первой группы входов матрицы 5 умножения. Одновременн сигналы с выходов блока 4 контроля поступят на контрольные выходы 9 и 1 устройства (через первый и второй входы блока 4 ) и на соответствующие один (,в случае равенства операндов) или два (в случае не равенств операндов ) входы второй группы входов матрицы 5 умно жения (через третью группу выходов блока 4). После срабатывания одного из элементов И матрицы 5 умножения, на оба входа которого поступят разре шающие сигналы, с первого выхода этого элемента сигнал, представляющи результат умножения в данном разряде (без учета переноса в старишй разряд поступит на выход произведения устройства 11 через первую группу выходов блока 5), с второго- выхода сигнал, представляющий перенос в старший разряд, поступит на выход переноса устройства (через вторую группу выходов блока 5). Рассмотрим теперь работу устрюй-. ства на конкретном примере, при использовании кода 2 из 4. Некоторые блоки устройства для этого случая изображены на фиг. 3-5. При поступлении на входы матрицы сложения сигналов, представляющих кодовые слова 1001 (число 2) и 1010 (число 4), срабатывает элемент И 13 и на выходе этого блока появляется сигнал , . Одновременно срабатывают элементы И 15 и 16, или элементы И 17 и 18 блока 4 контроля, поскольку на входы этого блока поступили с регистров 1 и 2 операндов сигналы Jnoa. XJ2x поъ,оу,гу.. сигналь ,4N Ll-no3.i;,2y результате срабатывания, указанных выше, элементов на соответстпующих выходах появятся сигналы .р.х . / О, и и. Первые два сигнала поступают на контрольные выходы устройства, а BTOjxsie два - на вертикальные входные шины матрицы 5 умножения. На диагональные входные шины этой же матрицы поступит сигнал и.д с выхода матрицы 3 сложения, соответствующий следу кяцему результату: О в данном разряде и перенос 1 в старший разряд. Этот же сигнал поступит и на выход суммы устройства. В матрице 5 умножения сработает тот элеМе-нт И 19, на первом выходе которого появится сигнал, соответствующий.результату умножения чисел 2 и 4 (при ) в данном разряде, без учета переноса в старший разряд - числу 2, а на втором выходе - переносу в старший разряд числу 1. Оба этих сигнала поступят на соответствующие выходы устройства. Эффективность предлагаемого устройства заключается в расширении функциональных возможностей устройства при минимально возможном увеличении аппаратурных затрат, так как матрица сложения выполняет дополнительно функции коммутатора для матрицы умножения, что позволяет, примерно в два раза уменьшить количество элементов в ней сделать ее треугольной.

t/c/to

Фиг.З

ч 1 f f t

J5

и контр. X

Иконтр-у

«,

/7

l/fJO}.3X

i/fto).2x

и поз. IK Uao3. OK

I

I

«,

/6

/(

W

15

-(/1 -(/}

ж

i:

«f

и

IS

J8

L

. Oj/

). ly - wj.#

-lJfio3.3jf

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1980 |

|

SU1008731A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Сумматор в коде "М" из "N | 1981 |

|

SU983706A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Сумматор в коде М из N | 1980 |

|

SU955037A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ по авт. св. № 911515, от л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения операции умножения, оно содержит матрицу умн.ожения и бло контроля, причем блок контроля содер жит два дешифратора, входы которялх соединены с третьими группами выходов первого и второго регистров опе ;рандов соответственно, выходы первой группы первого дешифратора объединен и подключены к первому контрольному выходу устройства, выходы первой группы второго дешифратора объедийенЬ и подключены к второму контрольному выходу устройства, матрица умножения выполнена в виде треугольной матрицы элементов И, имеющих два гальванически независимых выхода, причем ; первые входы элементов И каждой диагонали матрицы умножения соединены с соответствующими выходами матрицы сложения, первые выходы элементов И матрицы умножения соединены с первой группой дополнительных выходных шин , . устройства, вторые выходы элементоза И матрицы умножения соединены с вто-. рой группой дополнительных выходных . . шин устройства, соответствующие выходы вторых, групп первого и второго дешифраторов, гальванически незавцсимые от выходов первых групп первого г и второго дешифраторов, объединены . и соединены с вторыми входами элементов И соответствующих столбцов матрицы умножения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сложения | 1979 |

|

SU911515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-30—Публикация

1981-07-17—Подача